# **Programmable Logic in the 21<sup>st</sup> Century** Where are we and Where are we going?

**Steve Trimberger, Xilinx Fellow**

# **Key Messages**

### Still Pushing IC Manufacturing Technology

- Programmable logic has been successful because of effective use of Moore's Law

- Integrated circuit manufacturing doesn't give us all we need

- More than Moore: 3D, circuits for power, rad-hard, integration

### Xilinx 7-Series is Pretty Impressive

- Capacity, power, I/O bandwidth, processor integration, ADC

- Xilinx targets its major markets: communications, computing, image processing, automotive, industrial control

### Power: its Importance Continues to Grow

- FPGAs still give the best ops/watt

### Design Effort

- Improved devices, architecture and software

# **Introducing Xilinx**

#### Worldwide leader in programmable solutions

- Founded in 1984

- \$2.31B in revenues in 2010

- ~3,000 employees worldwide

- 20,000 customers worldwide

- Pioneer of the fabless semiconductor model

- Inventor of the FPGA

- 50% PLD market segment share\*

- Worldwide presence, with headquarters in San Jose, CA; Dublin, Ireland and Singapore

1997 1998 1999 2000 2001 2002 2003 2004 2005 2006 2007 2008 2009 2010 2011 \* According to market analyst firm iSuppli Corp . Source: <u>http://www.xilinx.com/company/about.htm</u>

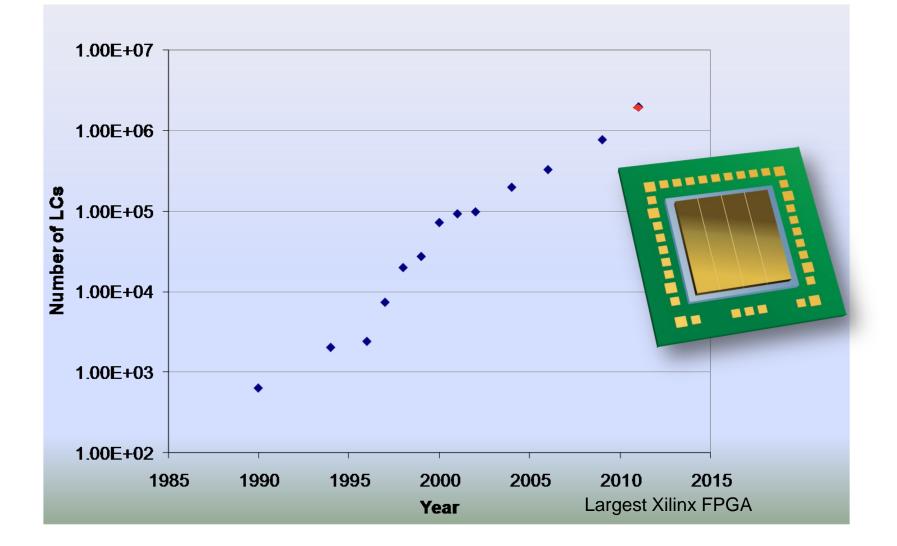

### **FPGA Capacity Trends**

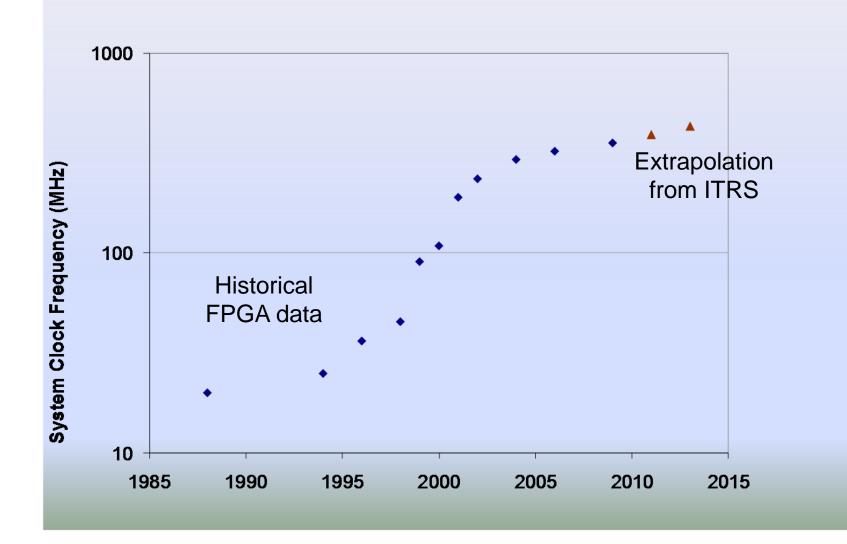

### **FPGA Performance Trends**

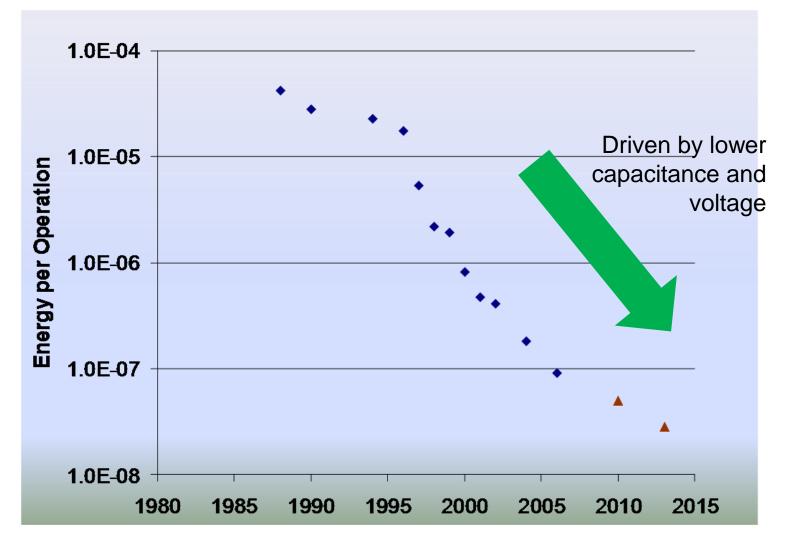

### FPGA Energy Trends (W / LC MHz)

### Pause

# Solving Next Generation Design Challenges For All Market Segments

| Next Gen W<br>Communicat                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                         | ations                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Computing<br>ARTIX <sup>7</sup>                                                                                                                                                                                                                              | KINTEX.                                                                                                                                                                                                                                                                 | Consumer<br>VIRTEX.7                                                                                                                                                                                                      |

| Lowest Power<br>and Cost                                                                                                                                                                                                                                     | Industry's Best<br>Price-Performance                                                                                                                                                                                                                                    | Industry's Highest System<br>Performance and Capacity                                                                                                                                                                     |

| <ul> <li>Portable/handheld ultrasound</li> <li>3D cameras &amp; camcorders</li> <li>D-SLR still cameras</li> <li>Software defined radio</li> <li>3DTV</li> <li>Portable eReaders</li> <li>Automotive Infotainment</li> <li>Multifunction printers</li> </ul> | <ul> <li>Wireless LTE infrastructure</li> <li>10G PON OLT line card</li> <li>LED backlit &amp; 3D video displays</li> <li>Video-over-IP bridge</li> <li>Cellular radio</li> <li>Medical &amp; Avionics imaging</li> <li>Set top boxes</li> <li>Motor control</li> </ul> | <ul> <li>400G &amp; 100G line cards</li> <li>300G Interlaken bridge</li> <li>Terabit switch fabric</li> <li>100G OTN</li> <li>MUXPONDER</li> <li>RADAR</li> <li>ASIC emulation</li> <li>Test &amp; Measurement</li> </ul> |

| Aerospace<br>& Defense<br>Measurement                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                         | dical ging Audio Video Broadcast                                                                                                                                                                                          |

# **Major Universal Market Challenges**

#### Market Challenges

- Lower <u>Power</u>

- Meeting Legislation and Regulations

### Higher <u>Performance</u>

System Capacity and Capability

#### Improved <u>Productivity</u>

Reduce Capital and Operating Expenses (OPEX, CAPEX)

#### Market Segments Affected

Flat Panel/TV, Central Office, Server Farms, Portable Medica Portable and Wired Consumer

Wired Infrastructure, 400G Networks, Wireless, Broadcast, Defense

Wireless, Wired, High Performance Computing

#1 problem from over 300 top customers' surveyed: Higher System Performance Impacted by Power Budget Limitations

# **Xilinx 7 Series Highlights**

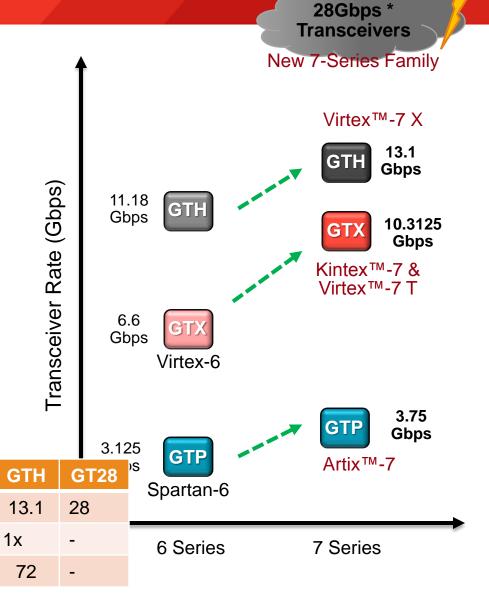

#### • 7 Series silicon devices

- 28 nm Technology, TSMC HPL process

- 50% reduction in power over 40 nm devices

#### 3 FPGA Fabrics

- Artix = Low cost, low power FPGA ("1W FPGA")

- Kintex = Density & performance FPGA ("Market Sweet spot")

- Virtex = Highest density and performance FPGA

("More than Moore")

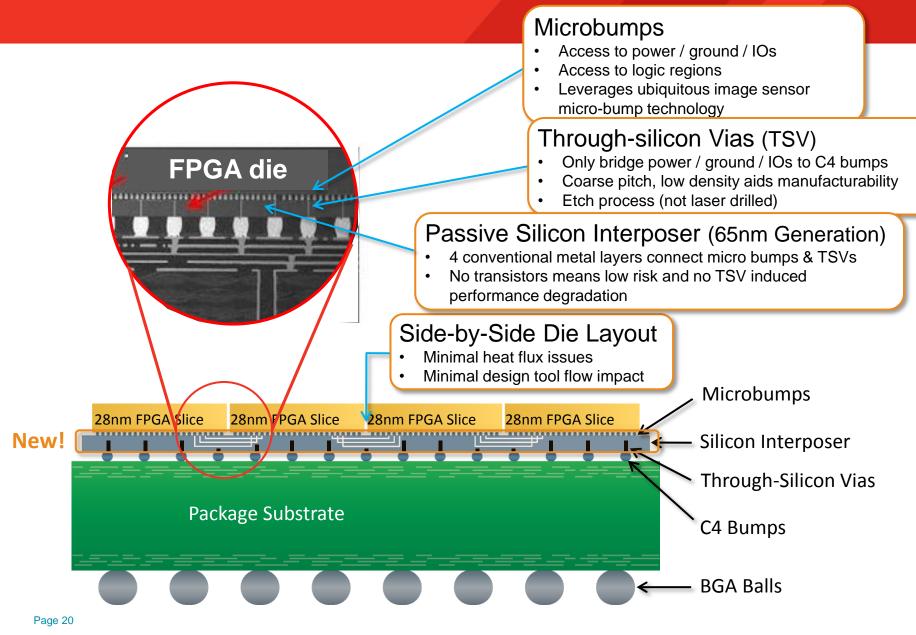

#### 'More than Moore' density increase

- Up to 2M logic cells

- Using Stacked Silicon Interconnect Technology (SSIT)

- Improved GT bandwidth

- GT bandwidth increased to 28 GHz

- Zynq Embedded Processing Platform (EPP)

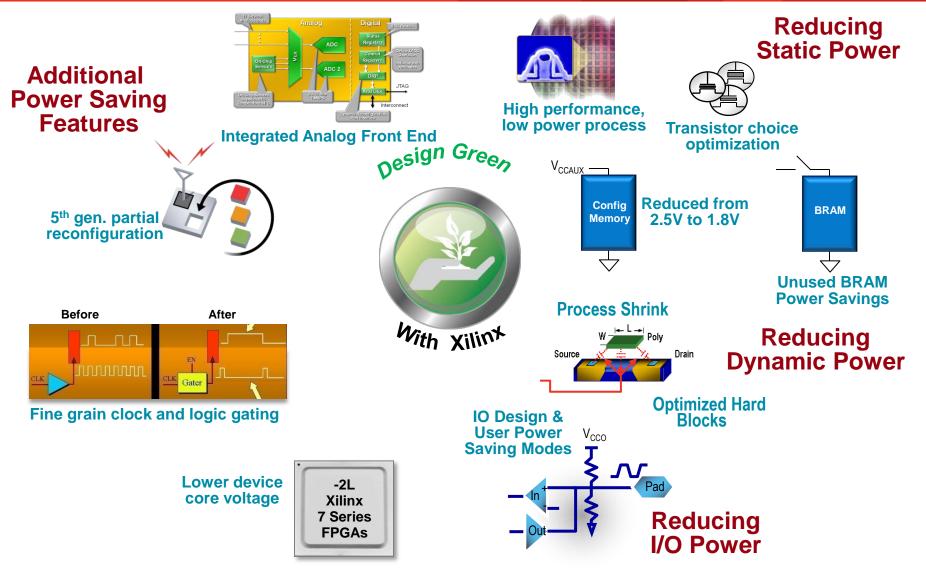

Design Green by Xilinx

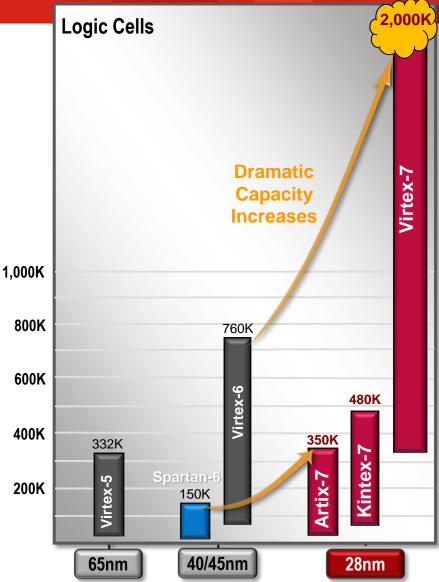

# **Ground Breaking Capacity Gains at 28nm**

World's First 2 Million Logic Cell FPGA

Over 2x capacity increases over Spartan-6 and Virtex-6 FPGAs

| Family                | Capacity Range        |

|-----------------------|-----------------------|

| ARTIX.7               | 8K – <b>350K LCs</b>  |

| KINTEX. <sup>77</sup> | 70K – <b>480K LCs</b> |

| VIRTEX.7              | 330K – <b>2M LCs</b>  |

- 8K 2M LCs; the widest capacity range offered in a single unified product family

- Larger densities enable higher performance

- More calculations/clock cycle by utilizing parallelism inherent in FPGAs

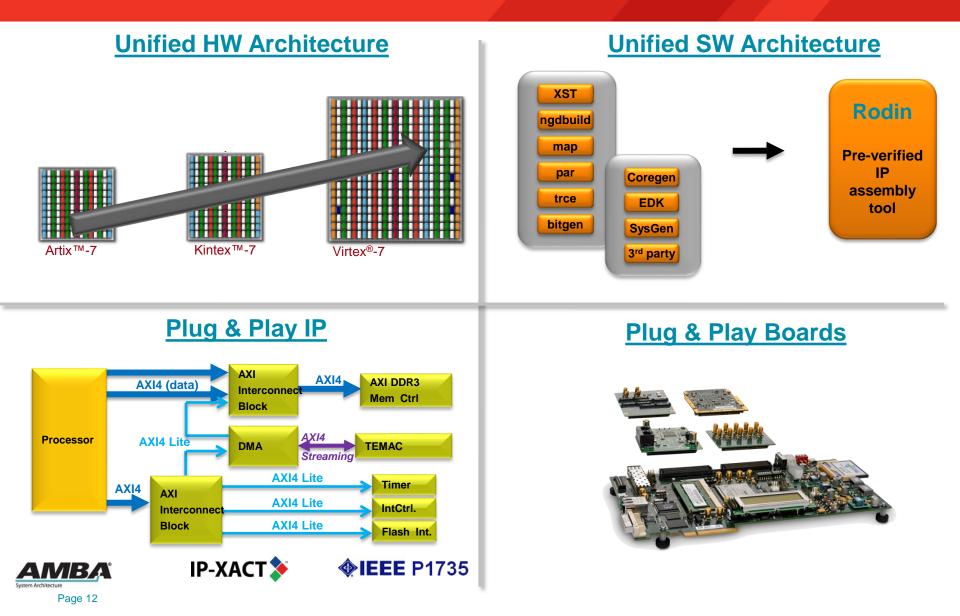

# Unified Architecture Boosts Design Productivity

Accelerating Design Creation, Debug and Simplifying Reuse

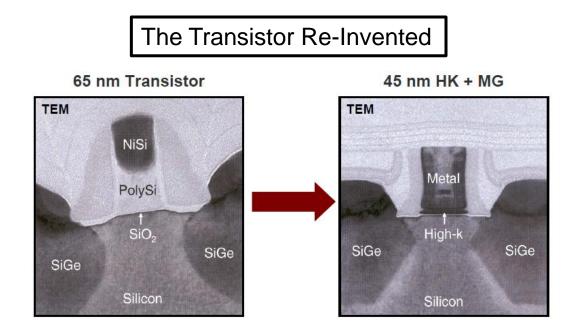

# High-k Metal Gate Transistor Rescues Moore's Law

#### HKMG:

- introduced by Intel at 45nm

- available at 28nm from top foundries

- > 25x lower gate oxide leakage

- > 30% lower switching power

- > 30% higher drive current or

- > 5x lower source-drain leakage

Source: "Challenges and Innovations in Nano-CMOS Transistor Scaling", Tahir Ghani, Intel, Oct 2009

# 7 Series Power Efficiency Focus from Every Angle

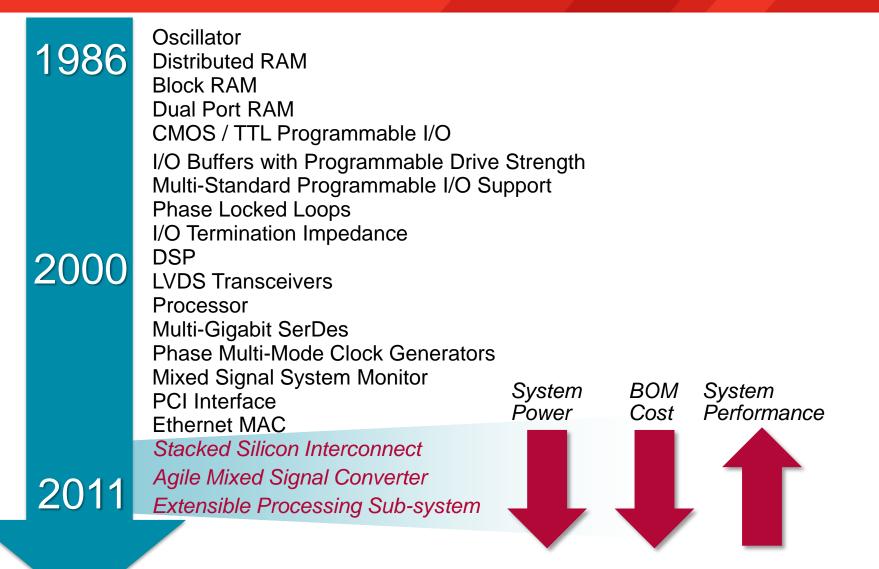

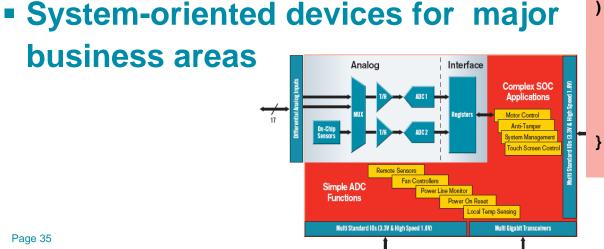

### **Xilinx History of Systems Integration**

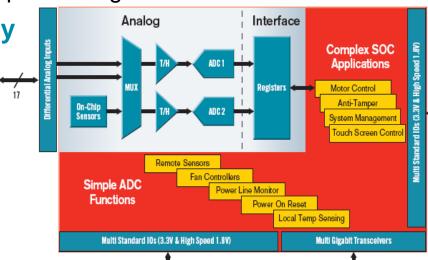

### Agile Mixed Signal (AMS) Technology Customized Analog with FPGA Flexibility

Significant cost & area savings by integrating common analog functionality

- \$3+ discrete analog functions integrated

- General purpose 12-bit Analog Front End covers wide range of General Purpose Analog Applications

#### Customized Analog beyond off-the-shelf Products

- Implement simple analog monitoring or

- Complex analog signal conditioning and processing

#### Enhanced Reliability, Safety, Security

- Single chip

- On-Chip temp & Voltage sensor

- Available in <u>all</u> 7 series devices

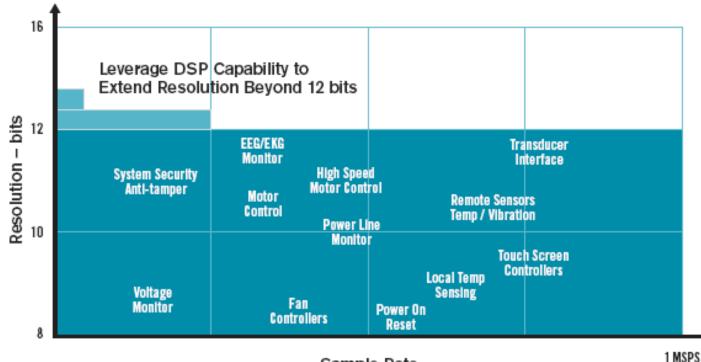

# **Agile Mixed Signal Technology Applications**

### XADC specifications cover a wide range of Data Converter applications

- Wide range of sampling and timing modes

- Accommodates various analog signal types

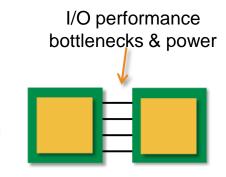

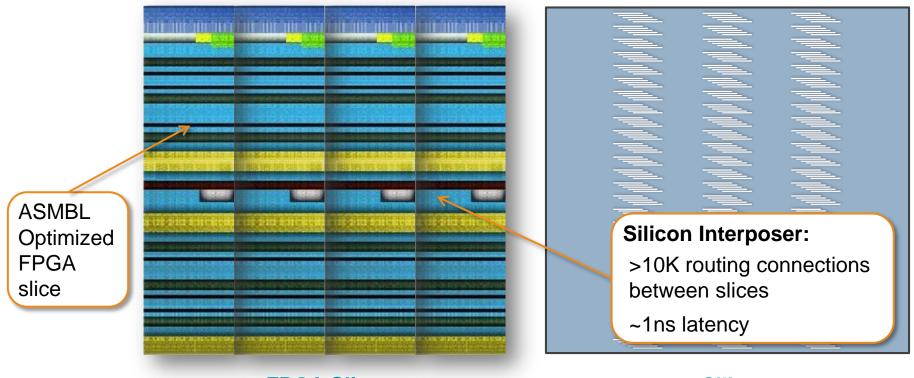

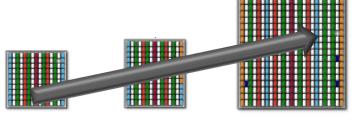

### Introducing Stacked Silicon Interconnect Technology High Bandwidth, Low Latency, Low Power

Large Monolithic FPGA

Die 1

Xilinx Innovation

Multiple chips on PCB or MCB

- Tens of thousands of low latency, die-to-die connections

- Large devices available earlier in time

- No wasted I/O power

- Over five years of R&D

#### Delivers the Best of Both Worlds: High and Usable Capacity

# Xilinx FPGA Architectural Innovations At the Heart of the Technology

FPGA Slices Side-by-Side Silicon Interposer

### Harnesses Proven Technology in a Unique Way

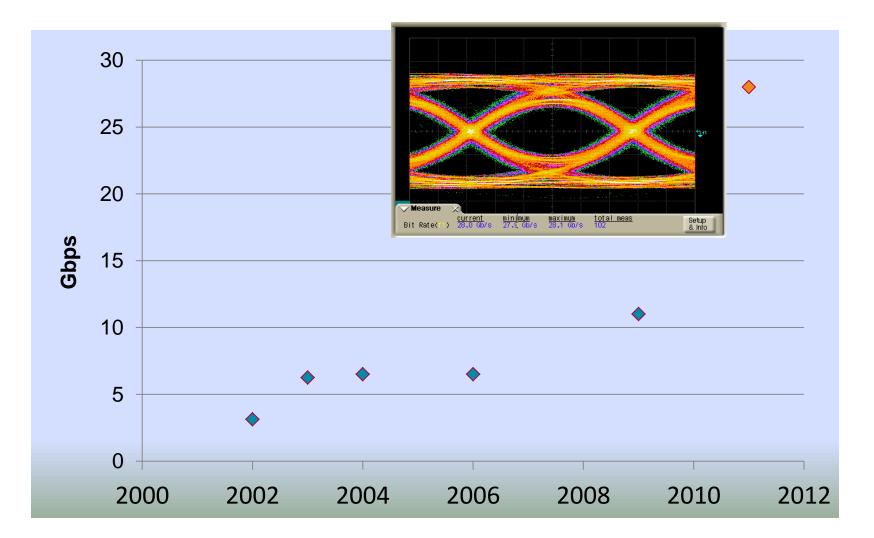

### **Transceiver Speed Expands Rapidly**

# **High-Speed Transceiver Evolution**

#### Challenge:

- Increase device BW

- No increase in total device power

- XCVR gains from scaling: negligible

#### Solution:

- Careful circuit design throughout XCVR

- Increased Gbps / XCVR

- More XCVR / Device

Max Rate (Gbps)

Max GTs per Device

Relative Power (Per GT)

- Low power mode for short channels

- Lanes share a PLL vs PLL per lane

#### Result:

- 60% Increased max device BW

- Device XCVR power unchanged

**GTP**

3.75

0.35x

4

**GTX**

10.3125

56

0.7x

Page 22

# University of Edinburgh Smith-Waterman DNA Matching

| Platfo              | rm                       | ormance<br>*) per \$ spent               | Normali | sed Perform<br>spent | ance per \$           |

|---------------------|--------------------------|------------------------------------------|---------|----------------------|-----------------------|

| FPG                 | A                        | 0.34                                     |         | 4.6                  |                       |

| GPU                 | I                        | 0.14                                     |         | 1.9                  |                       |

| Cell E              | E                        | 0.17                                     |         | 2.3                  | 1                     |

|                     |                          |                                          |         |                      |                       |

| GPF<br>Cell Updates | Per Second               | 0.07<br>Perform                          | ·       |                      | book                  |

|                     |                          |                                          | ance    | Nor                  | nalised<br>nce per Wa |

|                     | Per Second               | Perform<br>Performa                      | ance    | Nor<br>Performa      |                       |

|                     | Per Second Platform      | Perform<br>Performa<br>(MCUPS) pe        | ance    | Nor<br>Performa      | nce per Wa            |

|                     | Per Second Platform FPGA | Perform<br>Performa<br>(MCUPS) po<br>508 | ance    | Nor<br>Performa      | nce per Wa<br>584     |

#### **Emphasis added**

# University of Edinburgh Monte-Carlo Financial Options Pricing

|   |                    |        | Performance pe                                                                           | er\$  |                                                    |        |

|---|--------------------|--------|------------------------------------------------------------------------------------------|-------|----------------------------------------------------|--------|

| P | Platform           | Pe     | erformance (Paths/sec)<br>per \$ spent                                                   | Perfo | Nor <del>mal</del> ised                            | spent  |

|   | FPGA               |        | 3399                                                                                     |       | 32:1                                               |        |

|   | GPU                |        | 3339                                                                                     |       | 32:1                                               |        |

|   | GPP                |        | 105                                                                                      |       | 1:1                                                |        |

|   | [                  |        | Performance                                                                              | -     |                                                    | rmanca |

|   |                    |        | Paths per Second Per                                                                     | -     | malised Perfe                                      |        |

|   | Platfo             |        | Paths per Second Per<br>Watt                                                             | -     | malised Perfe<br>per Watt                          |        |

|   | FPG                | A      | Paths per Second Per<br>Watt<br>3,330,928                                                | -     | malised Perfe<br>per Watt<br>1090:1                |        |

|   |                    | A      | Paths per Second Per<br>Watt<br>3,330,928<br>64,322                                      | -     | malised Perfe<br>per Watt                          |        |

|   | FPG                | A<br>J | Paths per Second Per<br>Watt<br>3,330,928                                                | -     | malised Perfe<br>per Watt<br>1090:1                |        |

|   | FPG/<br>GPU        | A<br>J | Paths per Second Per<br>Watt<br>3,330,928<br>64,322                                      | -     | malised Perfe<br>per Watt<br>1090:1<br>21:1        |        |

|   | FPG/<br>GPU<br>GPP | A<br>J | Paths per Second Per           Watt           3,330,928           64,322           3,055 | Nor   | malised Perio<br>per Watt<br>1090:1<br>21:1<br>1:1 |        |

|   | FPG/<br>GPU<br>GPP | A<br>J | Paths per Second Per<br>Watt<br>3,330,928<br>64,322                                      | Nor   | malised Perio<br>per Watt<br>1090:1<br>21:1<br>1:1 |        |

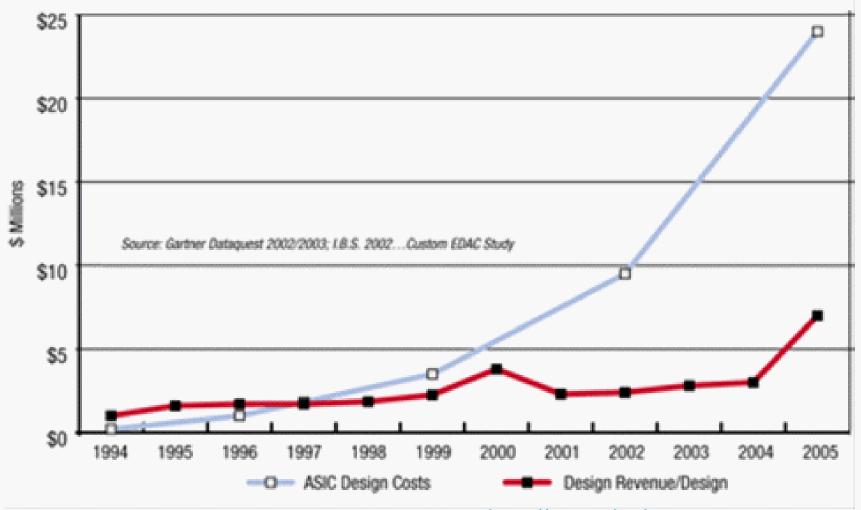

### **Design Costs Grow Exponentially, Too**

http://www.design-reuse.com

### Hardware and Software Programmability

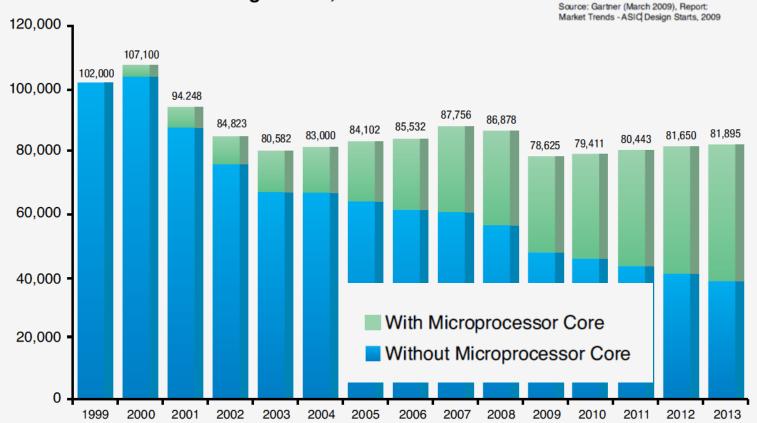

Estimated FPGA /PLD Design Starts, 2003-2013

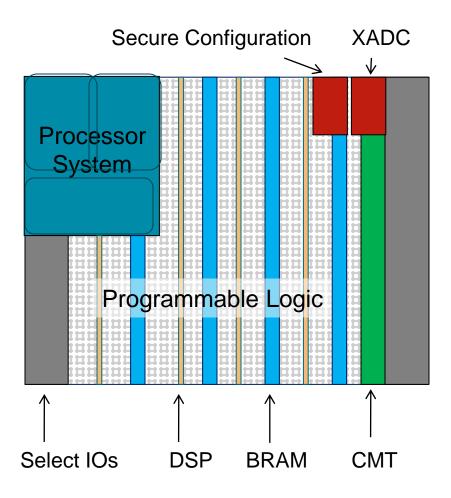

### Zynq-7020 Device Dual-Core ARM with FPGA Peripheral

#### Processor System (PS)

- ARM Cortex-A9 MPcore

- Standard Peripherals

- 32-bit DDR3 / LPDDR2 controller

- 54 Multi-Use IOs

- 73 DDR IOs

#### Programmable Logic (PL)

- 85 K Logic Cells

- 106K FFs

- 140 32-Kb Block RAM

- 220 DSP Blocks

- Dual 12-bit ADC

- Secure configuration engine

- 4 Clock Management Tiles

- 200 Select IO (1.2-3.3V)

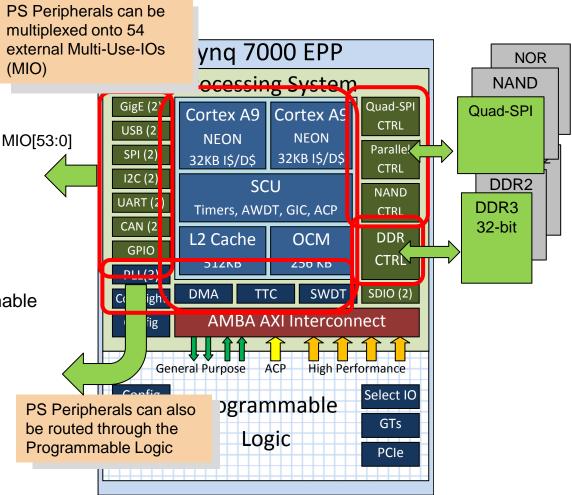

# Zynq-7000 Processor System (PS)

#### Dual Core Cortex ARM A9

- NEON, 512 KB L2 cache

- 256 KB On-Chip-Memory (OCM)

- DDR Interface

- DDR3 Performance

- High BW utilization

- Config & Legacy Memory I/F

- Quad-SPI, NOR, NAND

- Standard Peripherals GigE …

- Available to PS IO or to Programmable Logic

- System Level Peripherals

- Clock generation, Counter Timers

- 8 Channel DMA controller

- Coresight Debugging

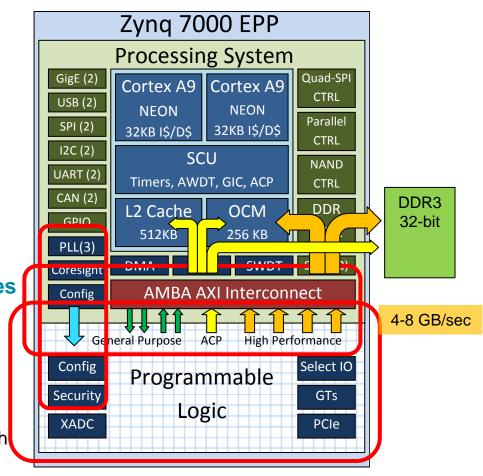

# Zynq-7000 Programmable Logic (PL)

#### Programmable Logic Resources

- 30K 235 K Logic Cells

- Dedicated 36 K-bit BRAMs, DSP, CMT

- XADC dual channel 12-bit ADC

- Up to 12 GTs with PCIe hard core

- Up to 300 Select IOs

#### Programmable Logic AXI Interfaces

- Multiple 32/64 bit AXI interfaces to PL

- Accelerator Coherency Port (ACP) with access to caches

#### Programmable Logic System Interfaces

- Interrupts, DMA control

- Debug

#### High Performance PL Configuration

- Security Decryption Engine

- Under 200 ms configuration time from flash

- Debugging interfaces

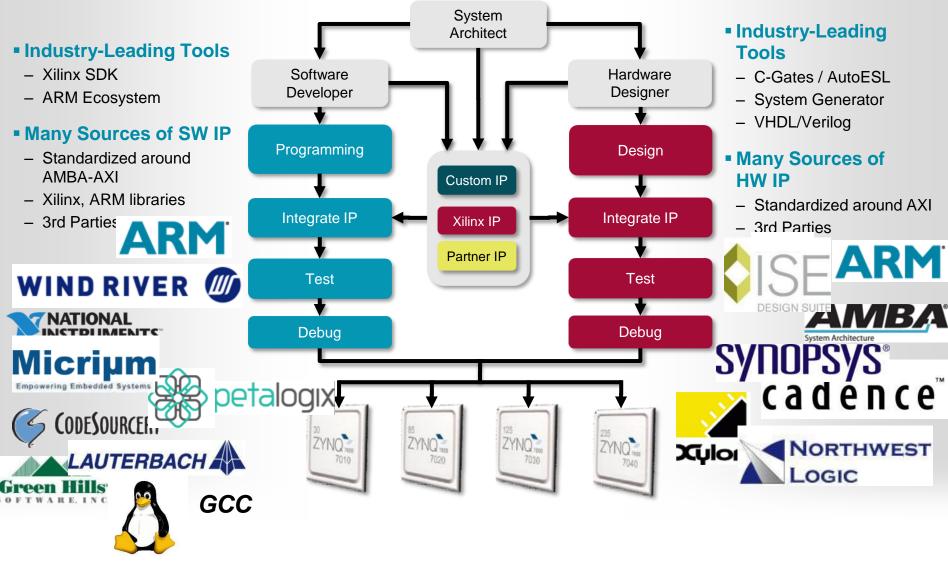

# **Embedded Design Flow Using Zynq-7000**

Page 30

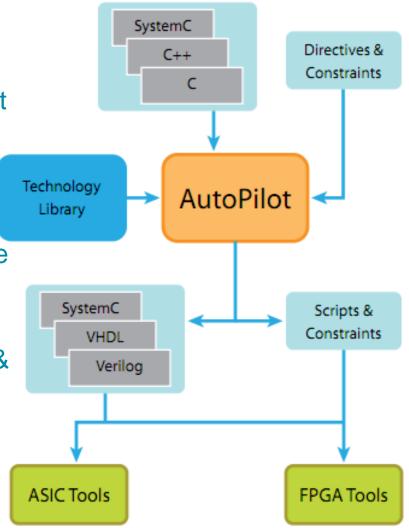

### Axilin© AutoPilot C to Gates

In 2010, BDTI optical flow benchmark showed quality of output comparable to manual design.

"In our test of Man vs. Machine; Machine won hands down! We were able to create and verify complex matrix inverse in 5 days vs. 3 months; Algorithm to FPGA speed & QoR is unbelievable. If I did not verify in hardware I would think the tool is lying. "*—MilAero Company*

# **FPGA Leadership at 28nm**

#### Lowest Total <u>Power</u> FPGAs

- HPL process proven 50% lower over alternative

#### Highest Productivity FPGAs

- Unified, plug and play with extensive Ecosystem

- Agile Mixed Signal (AMS) providing analog capability in all 7 series family members

- Fastest cost reduction path with EasyPath<sup>™</sup>-7 (all Virtex-7 FPGAs)

#### Highest <u>Performance</u> FPGAs

- Largest capacity: 2M logic cells (XC7V2000T)

- Largest transceiver count: 96 (XC7VX1140T)

- 100x better connectivity/watt: Stacked Silicon Interconnect Technology

- Fastest memory interface: 1,866 Mb/s (Kintex-7 and Virtex-7 FPGAs)

- Largest Block RAM capacity: 68 Mb (XC7VX1140T)

- Highest DSP performance: 5,112 GMACS symmetric mode (XC7VX980T)

#### Innovative Architecture Breaks the Rules

Extensible Processing Platform (Zynq-7000 EPP family)

### Looking Ahead: Technology

#### Moore's Law still operates Wafer fabrication delivers more transistors Wafer fabrication does not deliver significantly higher clock rate, lower power **Sombandwidth** Stacked silicon packaging addresses 1.00E+03 internal bandwidth and allows further TSV Interposer system integration 1985 1990 1995 2000 2005 2010 Year

### **Looking Ahead: Power**

- There is a fundamental tradeoff between performance and power

- The power issue will not go away

- The invisible and easy power optimizations have been done

- Next-generation power management will require thoughtful system design

- Watch for "dark silicon"

Before

BRAM

After

### Looking Ahead: Design

The need for efficient design will continue to increase

- More explicit effort on design reuse

- We are raising the design abstraction. Can it get higher than C?

- Specialty languages

```

void core (

```

// input size int n. float \*data in1, // input stream float \*data in2, // input stream float \*data out // output stream ) {

int i, j=0;

```

for (i=0; i<n; i++)

data_out[i] = data_in1[i] + data_in2[i];

```

# **Key Messages**

### Still Pushing IC Manufacturing Technology

- Programmable logic has been successful because of effective use of Moore's Law

- Integrated circuit manufacturing doesn't give us all we need

- More than Moore: 3D, circuits for power, rad-hard, integration

### Xilinx 7-Series is Pretty Impressive

- Capacity, power, I/O bandwidth, processor integration, ADC

- Xilinx targets its major markets: communications, computing, image processing, automotive, industrial control

### Power: its Importance Continues to Grow

- FPGAs still give the best ops/watt

### Design Effort

- Improved devices, architecture and software

### **Thank You**