# A front end chip for SLHC CMS strip tracker

Concept of Silicon strip Pt-module for CMS trigger purpose at SLHC

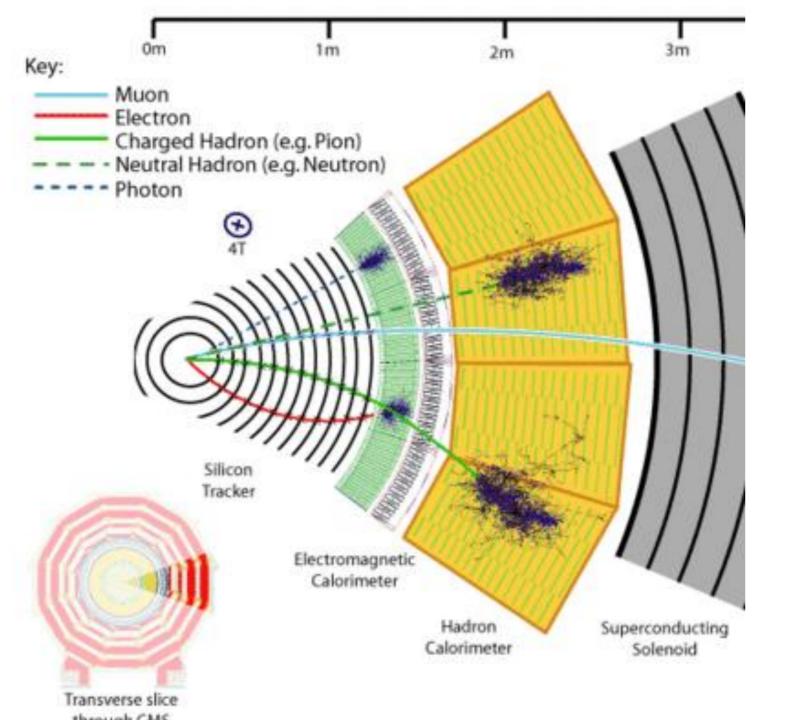

CMS: One of the 4 major experiment of the LHC Run smoothly with 7Tev pp collision since 2010

#### **Upgrade**:

**\*** LHC luminosity to 5x10<sup>34</sup>cm<sup>-2</sup>s<sup>-1</sup> Preserve the performance by including the tracker in the level 1 trigger design chip for selective readout at the LHC clock (based on a local measurement of the particle bending)

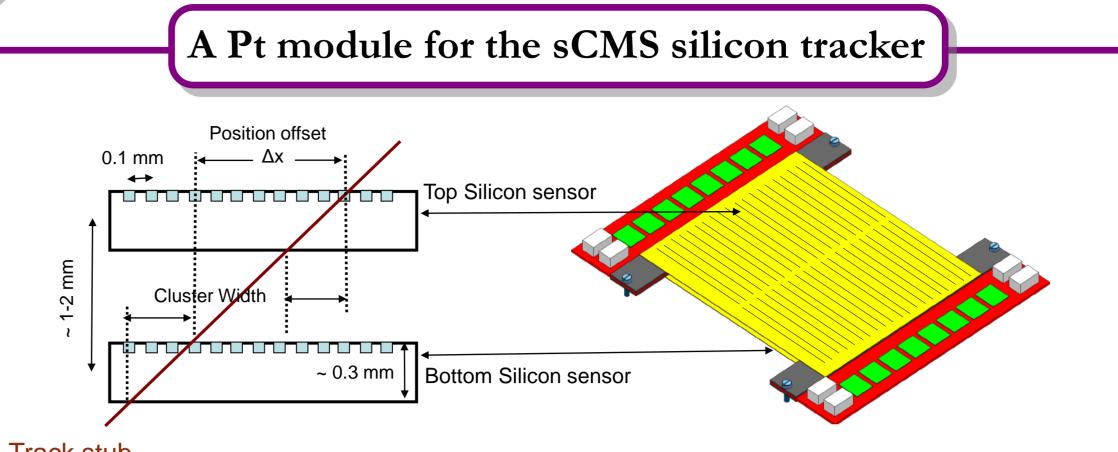

Track stub

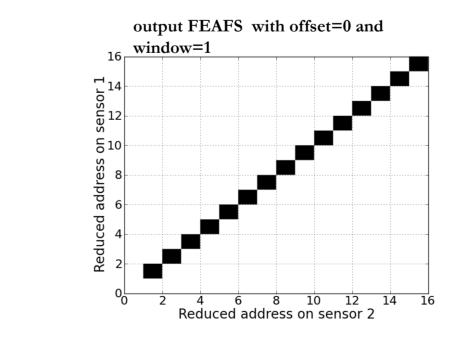

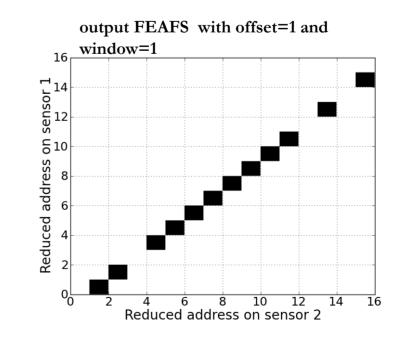

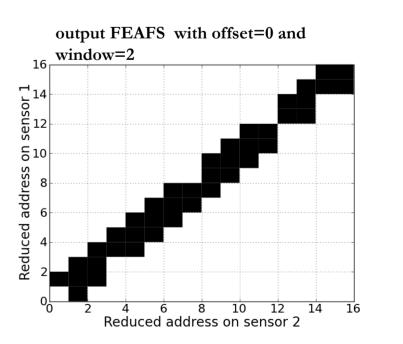

Track bending in the B-field is inversely proportional to transverse momentum Cluster Width and Position Offset selection in 2 sensors connected to same Front End ASICs (Pt-module) allows to reject low Pt tracks, reducing band width for read-out of proper trigger information at the LHC clock frequency

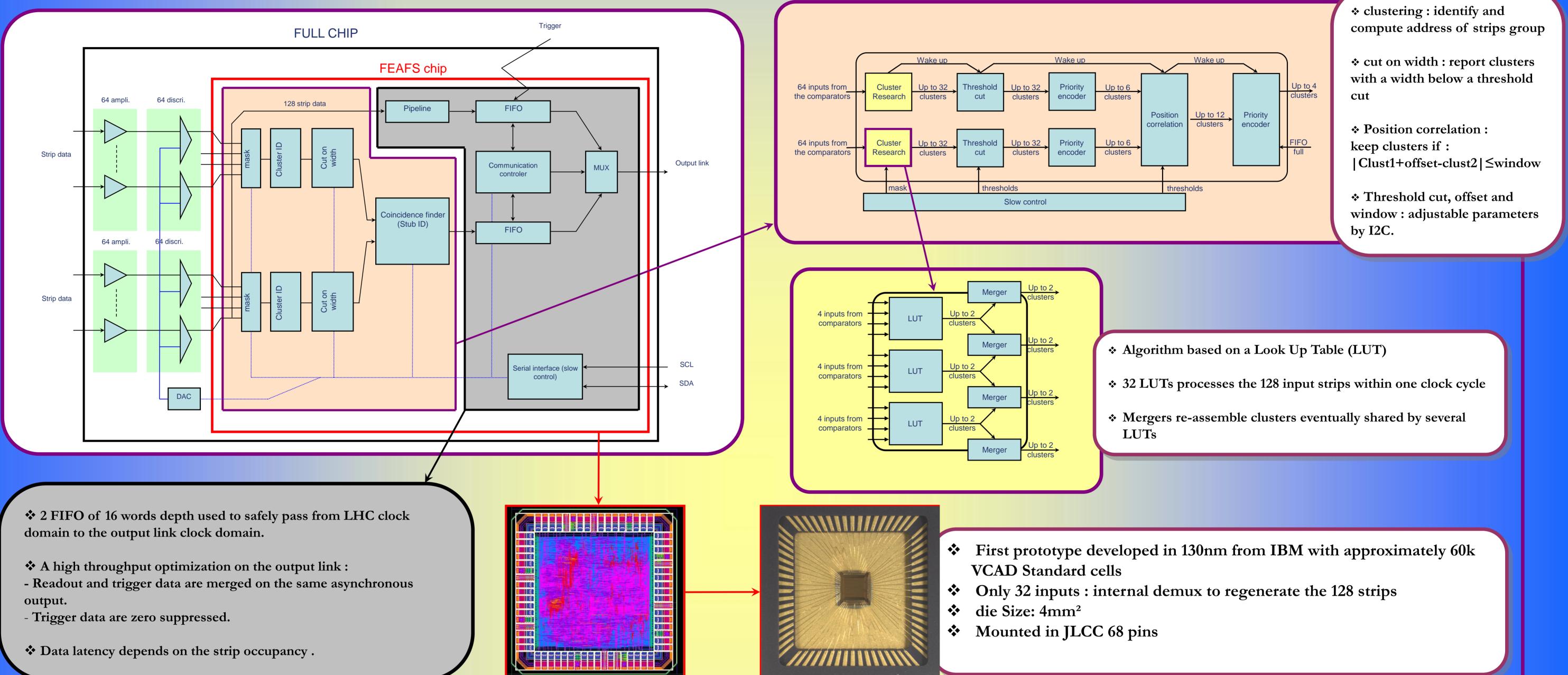

## FEAFS chip : zero suppression and asynchronous architecture for selective readout

# Test bench and results

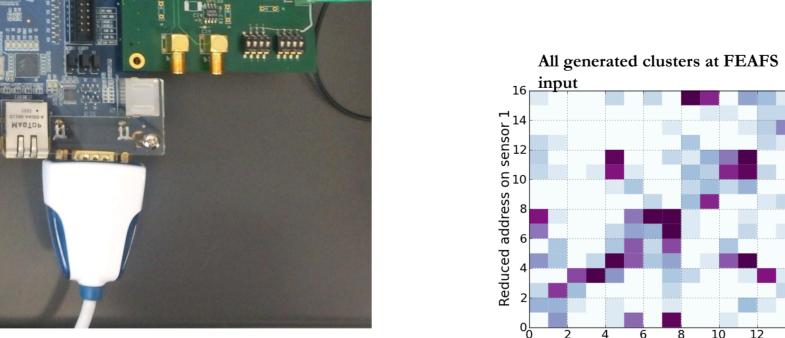

#### Test setup:

\* ASIC test is done by a cyclone IV ALTERA FPGA (on a DE2-115 development board from TERASIC)

test control is done either by USB, RS232 or JTAG.

\* FPGA firmware : A random hit generation (with an adjustable probability) is applied on the FEAFS chip. The output bus is compared with an emulated FEAFS design in the FPGA.

#### **Results:**

\* Power consumption at 40MHz : 75 mW (30 mW used in the 160MHz strip input PAD which will be removed when the analog part will be integrated)

Internal logic is working as expected at 40 MHz frequency.

## **\***Summary and Perspectives

FEAFS prototype, was developed in 130 nm IBM technology. It include the main foreseen features for the digital part of the Strip Pt-modules read-out (Cluster ID and selection, Stub identification, pipeline, FIFO, multiplexer, serial line).

Test results of the chip are in perfect adequacy with simulations.

The FEAFS is the digital part of the front end ASIC, it has to be coupled with an analog part (preamplifier + comparator). A new FEAFS version is now proposed with the analog part, proper data format and adaptation to the GBT (GigaBit transceiver system from CERN). The power consumption need also to be minimized, a new version of pipeline, output interface and clustering algorithm are under development.

More simulation with realistic SLHC event are needed to adjust the design parameters in order to minimize cluster losses and trigger latency.

## H. Chanal<sup>(1-2)</sup>, Y. Zoccarato<sup>(2-3)</sup>

(1) LPC Clermont Ferrand, Université Blaise Pascal, CNRS/IN2P3 (2) MICRHAU: pole de MIcroélectronique Rhone, AUvergne (3) Institut de physque nucléaire de Lyon (IPNL), Université de Lyon, Université Lyon 1, CNRS/IN2P3

#### *TWEPP 2011- Vienna- 26-30 september 2011*