# A READOUT SYSTEM-ON-CHIP FOR A CUBIC KILOMETER SUBMARINE NEUTRINO TELESCOPE

S.Anvar, V.Gautard, <u>H.Le Provost</u>, F.Louis, K.Menager, Y.Moudden, B.Vallage, E.Zonca, on behalf of the KM3NeT consortium<sup>1</sup>

IRFU/SEDI-CEA Saclay F-91191 Gif-sur-Yvette, France

<sup>1</sup> Supported by the European Commission through FP6 and FP7

TWEPP-11, Vienna, Austria, 26-30 September 2011

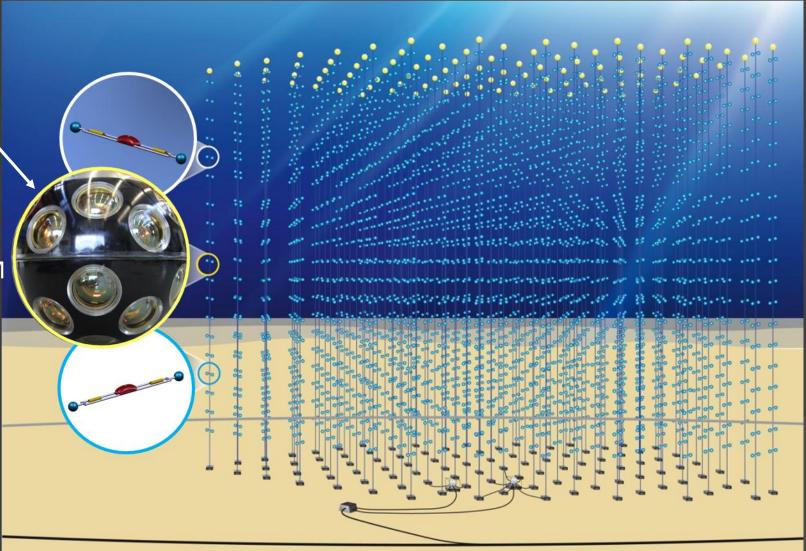

#### The KM3Net Detector

Digital

Optical

Module

(DOM)

31 PMTs/DOM

> 12800 DOMs

320 lines

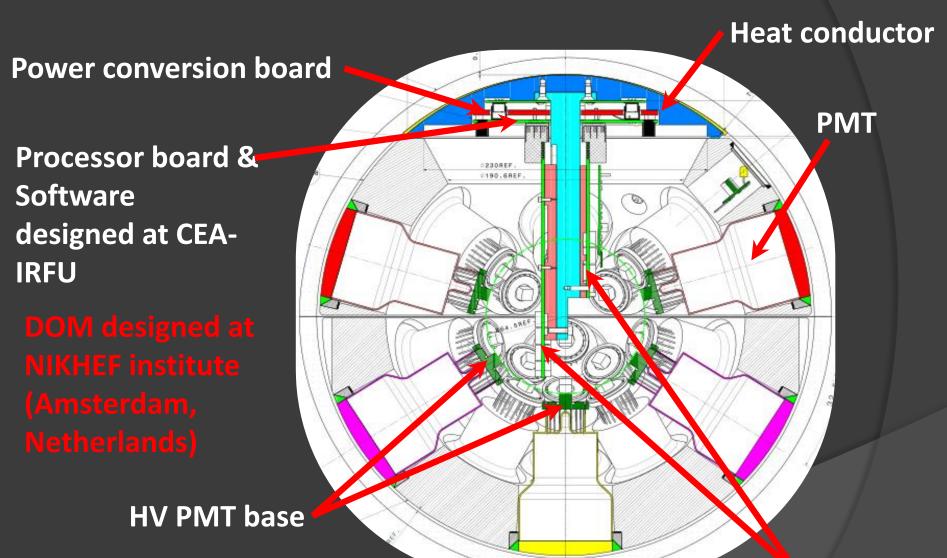

## The DOM processor board

Signal collection board

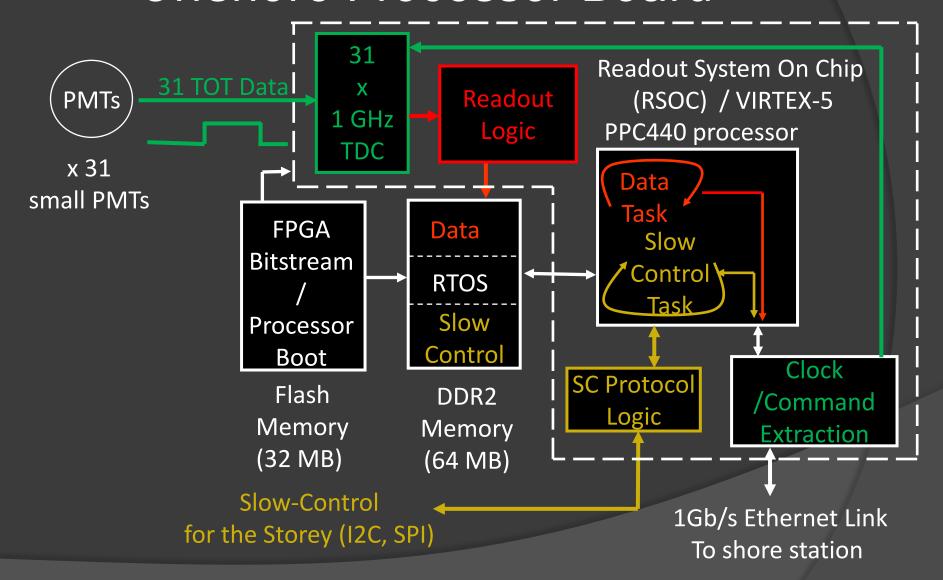

# The KM3Net prototype Offshore Processor Board

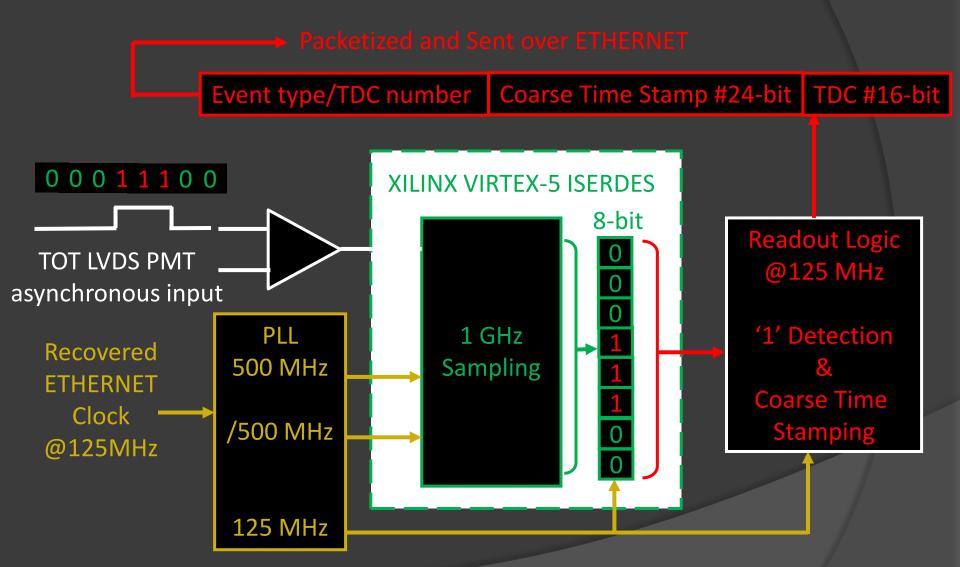

# Firmware TDC Development

[Originally designed by A.Zwart (NIKHEF) / small PMTs test bench for ALTERA]

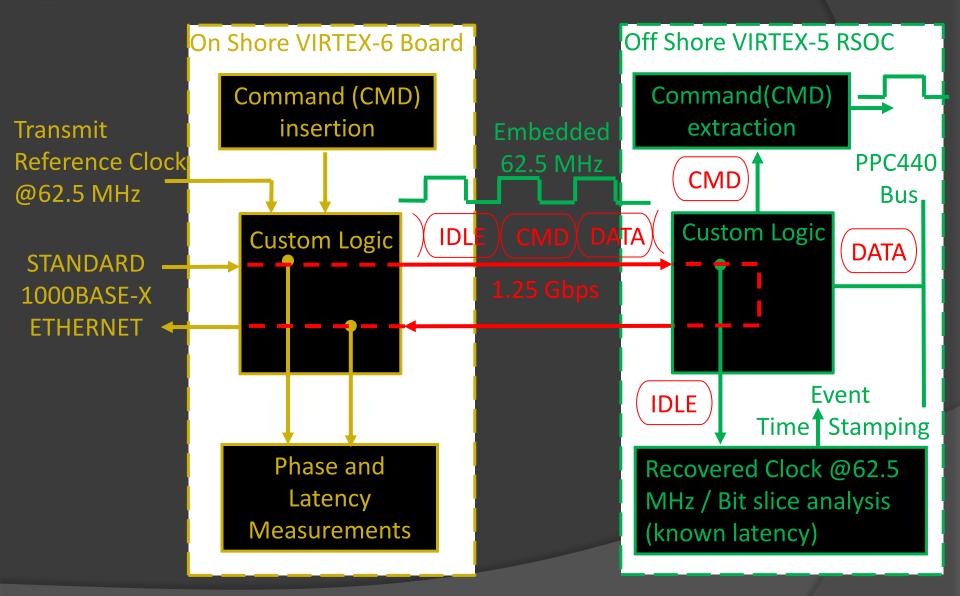

#### Clock distribution

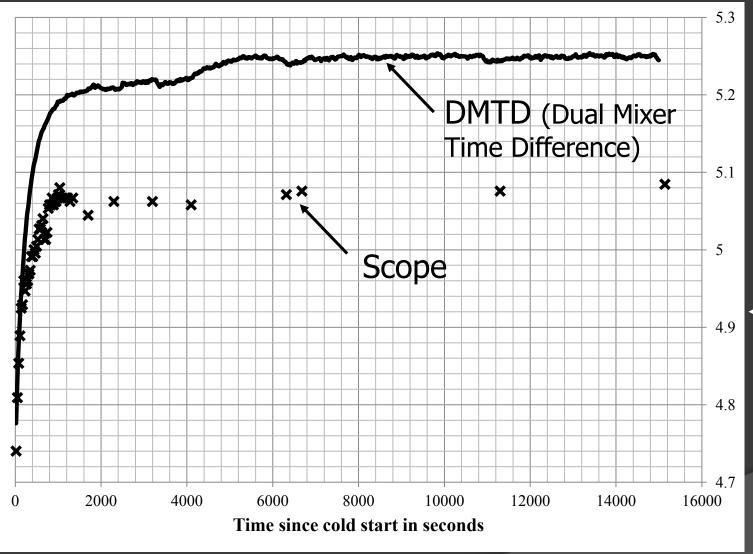

# Transmit/Receive clock skew | Life

Tx/Rx clock skew measured on shore with DMTD and oscilloscope (ns)

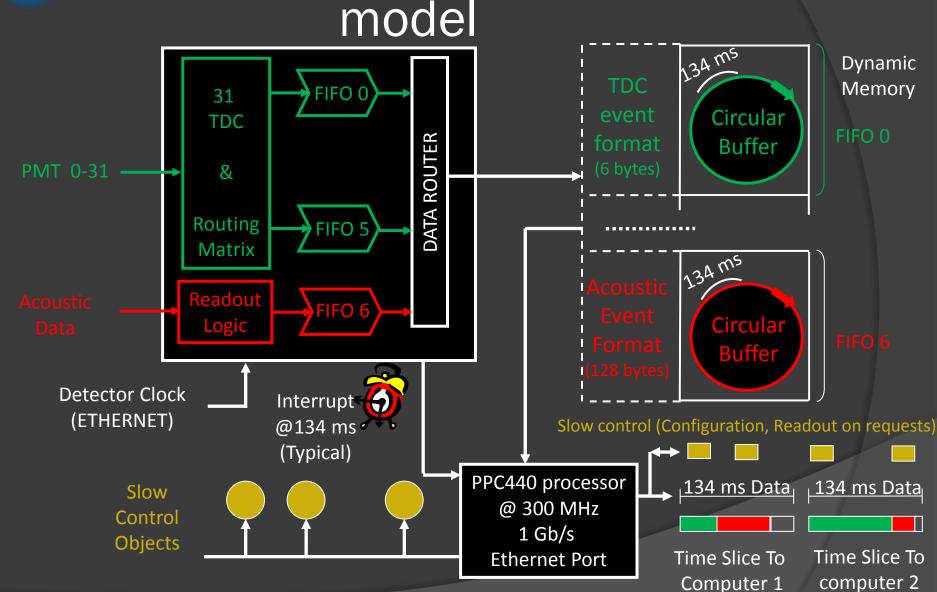

# Store & Forward Acquisition

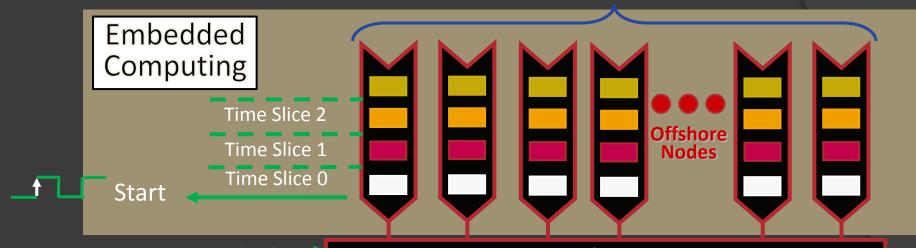

## Time Slice Building

**Intrinsic Parallelism**

Detector Clock (Start) Commands

- •Track reconstruction

- Data routing

Farm Computing

**Clock Distribution/Commands Insertion**

**Multi-gigabit Standard Ethernet Switching**

**Performance Parallelism**

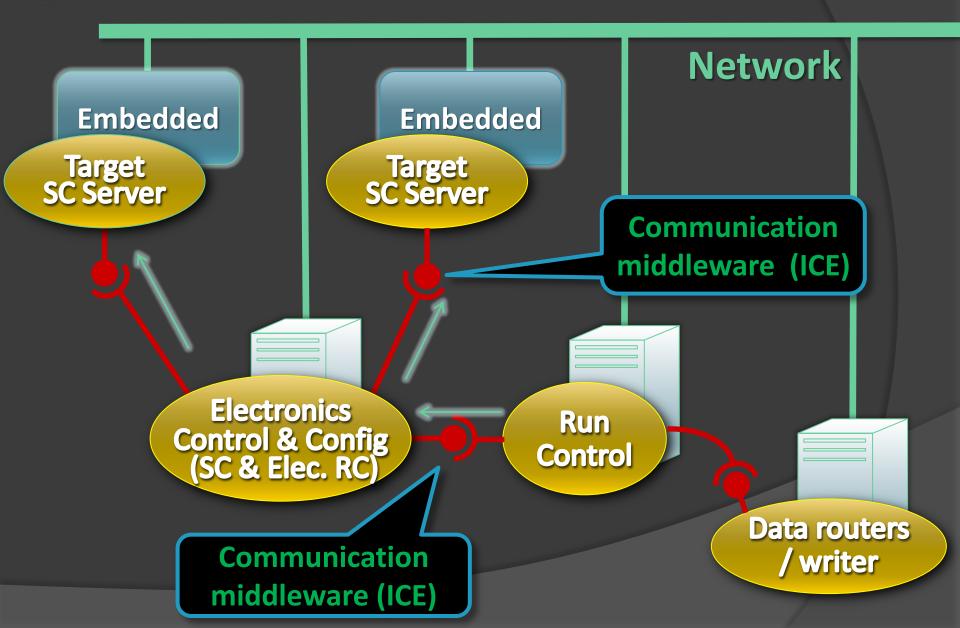

## Electronics control & config

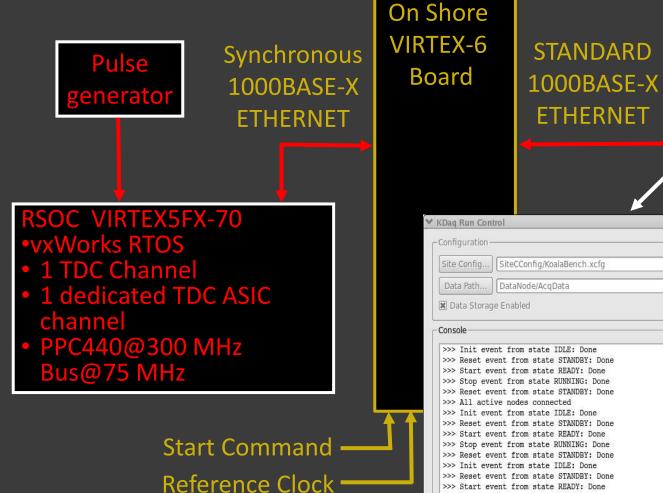

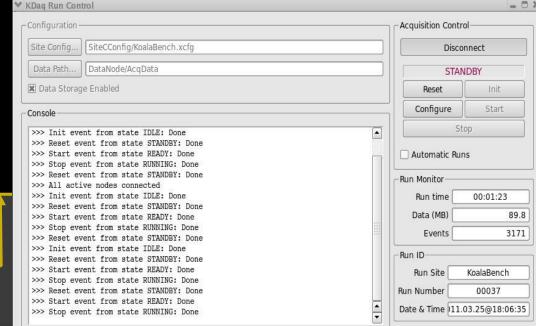

#### Data acquisition setup

@62.5 MHz

Host PC

- •Run Control

- Target Configuration

- Data acquisition

- •vxWorks RTOS boot server

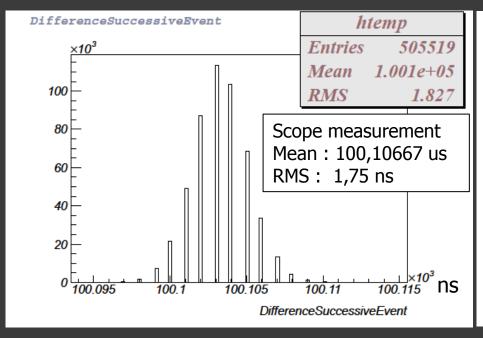

#### Acquisition results

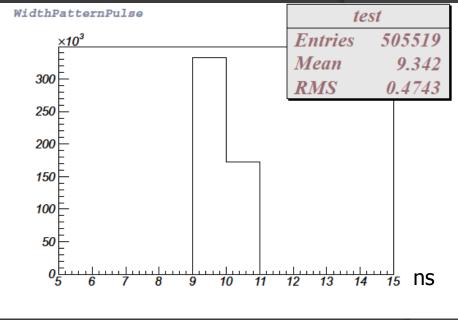

Pulse @  $f=10 \text{ kHz} \frac{2 \text{ ns}}{2 \text{ ns}}$

Power: 7 W

Current acquisition setup (Source limitation): 60 Mb/s

Standalone measured TCP/IP throughput PPC440@400 MHz / Bus@100 MHz /WindRiver Zero Copy buffer /Jumbo frames : 988 Mb/s

#### CONCLUSION

- Common Readout system functions integrated in a single component (RSOC):

- Event Time stamping @ 1 GHz

- Clock and command distribution

- Slow-control and data acquisition performed in a RTOS multi-tasking embedded system

- RSOC is a node designed to be plugged in a complete Data acquisition System

- Server/Client topology (ICE)

- Scalable system