# Exploring the limiting factors of PSEC4 resolution

D. Braga, F. Fahim, N. J. Pastika, P. M. Rubinov, T. N. Zimmerman<sup>1</sup> N. Sullivan<sup>2</sup> H. J. Frisch, M. Heintz, E. Oberla, J. Park, C. Poe, F. Tang<sup>3</sup> G. S. Varner<sup>4</sup> B. W. Adams<sup>5</sup> C. Ertley<sup>6</sup> E. Angelico<sup>7</sup>

1. Fermi National Accelerator Laboratory 2. Angstrom Research, Inc. 3. Enrico Fermi Institute, the University of Chicago 4. Univ. of Hawaii 5. Quantum Optics Applied Research 6. Southwest Research Institute 7. Stanford University

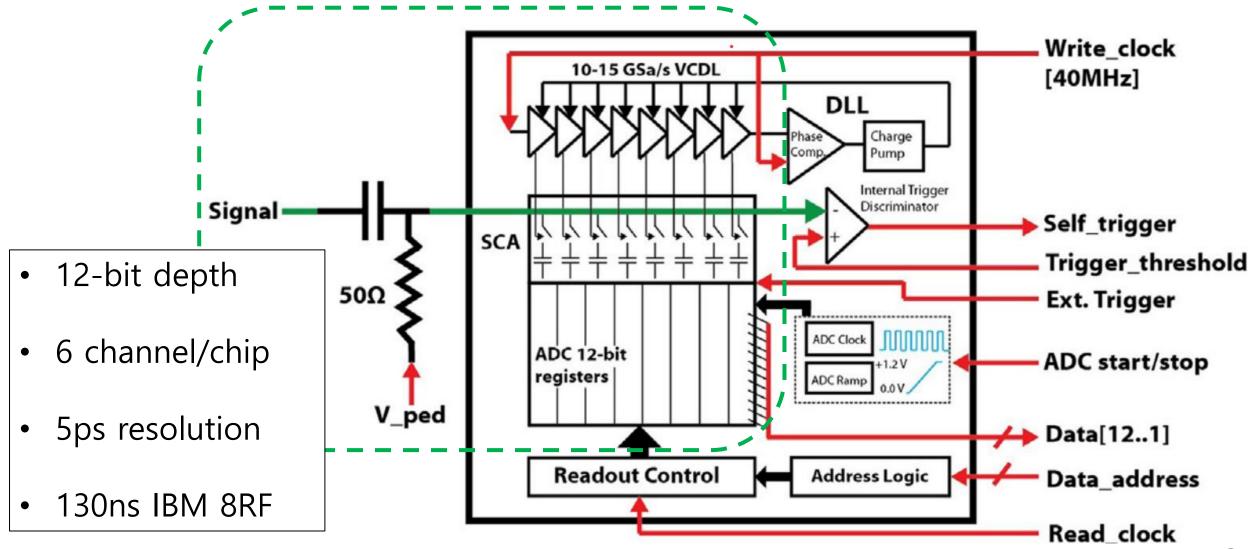

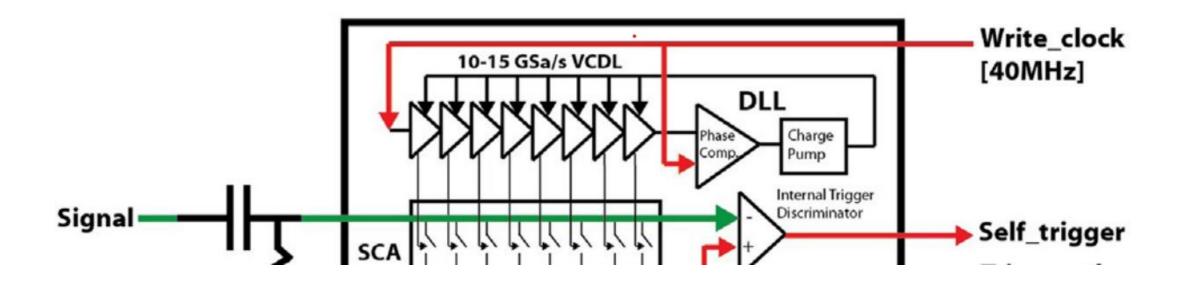

#### **PSEC4 ASIC(2014)**

E. Oberla , J.-F. Genata, H. Grabasa, H. Frisch, K. Nishimura, G. Varner, arxiv.org/abs/1309.4397

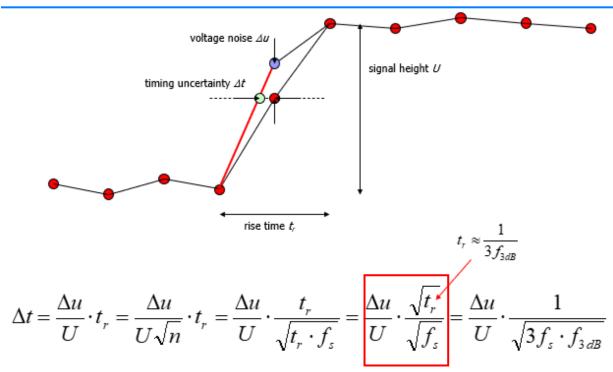

## **Timing resolution factors – PSEC4 studies**

- Must optimize four aspects:

- Signal rise time

- voltage noise of samples

- sampling time jitter/uncertainty How is timing resolution affected?

- Nonlinearity

Adopted from Stefan Ritt "The role of analog bandwidth and signal-to-noise in timing for waveform digitizing"

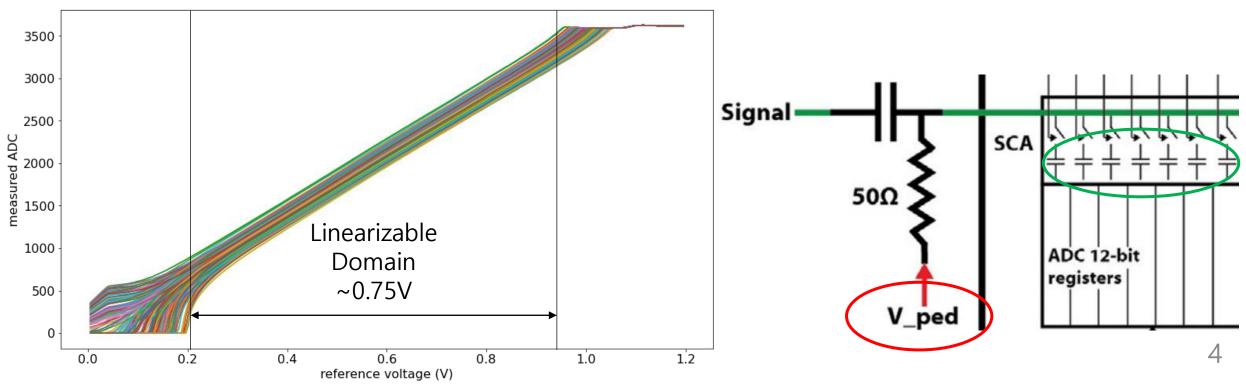

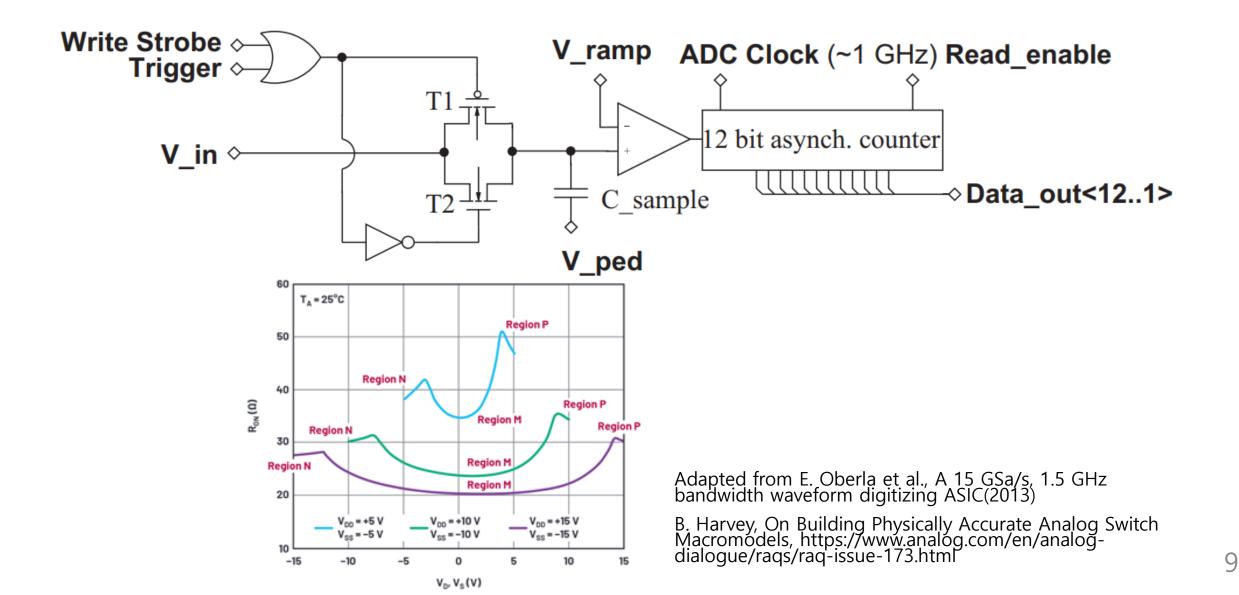

#### **Voltage linearization of PSEC4**

It is necessary to reconstruct voltage from ADC value. The curve differs for each capacitor.

1. **V\_ped** is set to a voltage of interest, 0.0v-1.2v

2. PSEC4 is left in sampling mode for a few cycles, so that all capacitors are set to **V\_ped**. ( $\sigma_V \approx 0.5 mV$ )

3. Each register is read. Each curve corresponds to a capacitor.

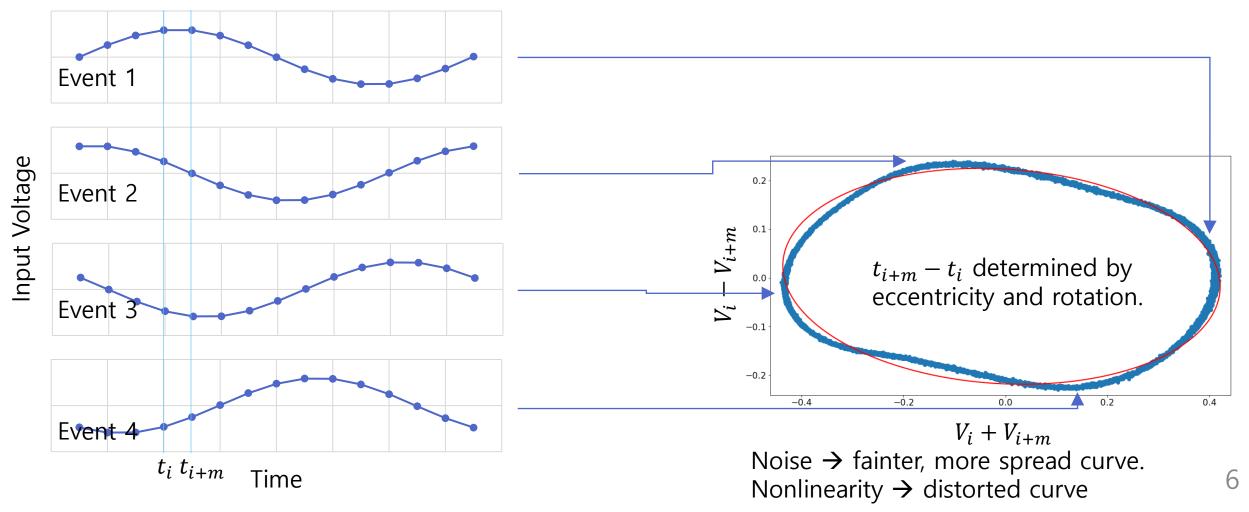

#### **Sample time calibration – Ellipse method**

Time intervals between samples are determined by a VCDL. Each element of the VCDL has a different time offset.

K. Nishimura, A. Romero-Wolf, A correlation-based timing calibration and diagnostic technique for fast digitizing ASICs(2011)

- 1. Measure many events of a sine wave.

- 2. Sum vs. Difference of two adjacent samples, over all events, form an ellipse.

- 3. Time offsets can be determined from the ellipse coefficients.

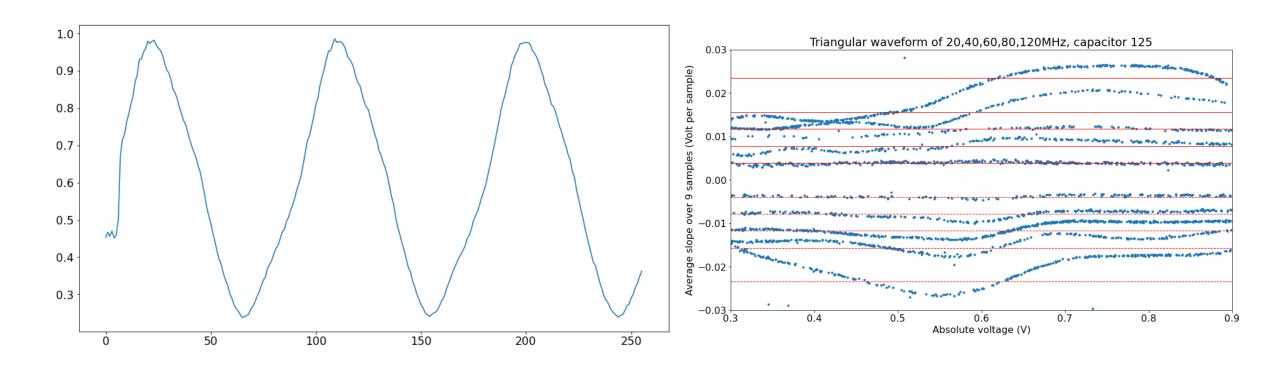

#### **Nonlinearity - Measurement**

Nonlinearity distorts sine wave input, introducing systematic errors in the ellipse method.

#### **Nonlinearity - Microscopic**

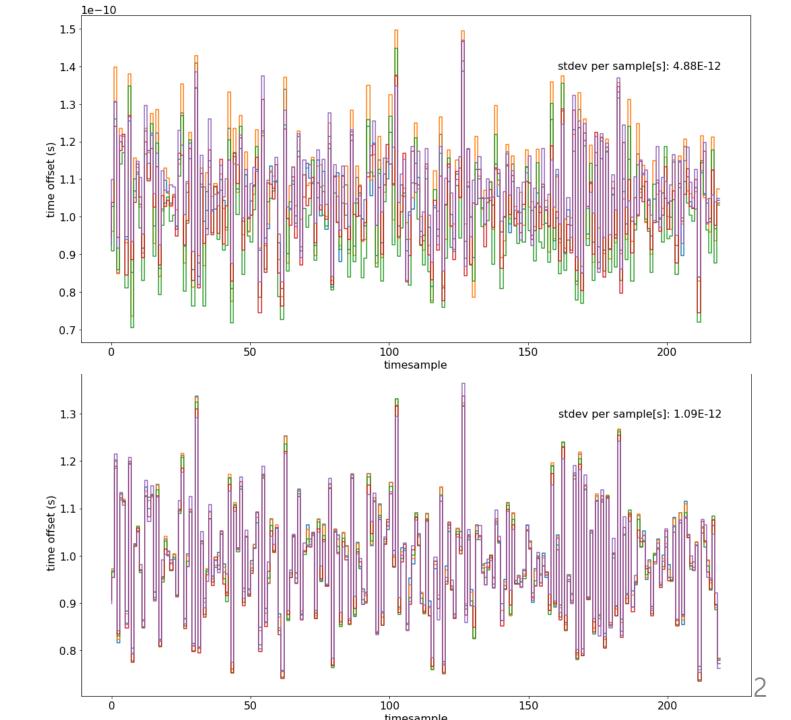

#### Weighted Least Squares Method

We want to estimate the following quantity:

$T = \{t_0, \dots, t_{N-1}\}$

Where  $t_i$  is a time interval between *i*th and *i* + 1th sample. Conventional method of estimating *T* is the following:

$$\begin{pmatrix} a_{01} \\ a_{12} \\ \vdots \\ a_{(N-1)N} \end{pmatrix} = \hat{T} = \begin{pmatrix} 1 & 0 & 0 & \cdots & 0 & 0 & 0 \\ 0 & 1 & 0 & \cdots & 0 & 0 & 0 \\ 0 & 0 & 1 & \cdots & 0 & 0 & 0 \\ \vdots & \vdots & \vdots & \ddots & \vdots & \vdots & \vdots \\ 0 & 0 & 0 & \cdots & 1 & 0 & 0 \\ 0 & 0 & 0 & \cdots & 0 & 1 & 0 \\ 0 & 0 & 0 & \cdots & 0 & 0 & 1 \end{pmatrix} \hat{T}$$

Where  $a_{ij}$  is a measured time interval between the *i*th and *j*th samples.

#### Weighted Least Squares Method

Consider measuring time intervals between *i*th and i + 2th sample.

$$\begin{pmatrix} a_{02} \\ a_{13} \\ \vdots \\ a_{(N-2)N} \end{pmatrix} = \begin{pmatrix} 1 & 1 & 0 & \cdots & 0 & 0 & 0 \\ 0 & 1 & 1 & \cdots & 0 & 0 & 0 \\ \vdots & \vdots & \vdots & \vdots & \vdots & \vdots \\ 0 & 0 & 0 & \cdots & 1 & 1 & 0 \\ 0 & 0 & 0 & \cdots & 0 & 1 & 1 \end{pmatrix} \hat{T}(2)$$

$$\begin{pmatrix} a_{02}/\sigma_{02}^2 \\ a_{13}/\sigma_{13}^2 \\ \vdots \\ a_{(N-2)N}/\sigma_{(N-2)N}^2 \end{pmatrix} = \begin{pmatrix} \sigma_{02}^{-2} & \sigma_{02}^{-2} & 0 & \cdots & 0 & 0 \\ 0 & \sigma_{13}^{-2} & \sigma_{13}^{-2} & \cdots & 0 & 0 \\ \vdots & \vdots & \vdots & \vdots & \vdots & \vdots \\ 0 & 0 & 0 & \cdots & \sigma_{(N-2)N}^{-2} & \sigma_{(N-2)N}^{-2} \end{pmatrix} \hat{T}(2) = A_2 \hat{T}(2) \quad (a/\sigma^2) = \begin{pmatrix} A_1 \\ A_2 \\ \cdots \\ A_k \end{pmatrix} \hat{T}$$

We can use the least squares method to compute  $\hat{T}$ .

#### Only using N=1:

Weighted average N=1-6:

# **PSEC5 Design Philosophy**

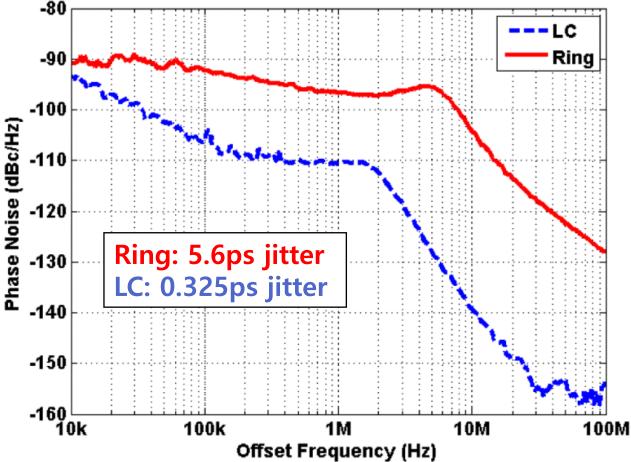

#### Timing uncertainty reduced by an optimized LC-oscillator based PLL

From abstract:

"Both independent PLLs have identical loop dynamics to allow a fair comparison ...

Furthermore these circuits consume the same amount of power. The PLLs were processed in a commercial 65 nm CMOS technology."

J. Prinzie, J. Christiansen, P. Moreira, M. Steyaert and P. Leroux, "Comparison of a 65 nm CMOS Ring- and LC-Oscillator Based PLL in Terms of TID and SEU Sensitivity," in *IEEE Transactions on Nuclear Science*, vol. 64, no. 1, pp. 245-252, Jan. 2017.

## **Comparison to other ASICs**

| Project  | Sampling  | Input     | Buffer    | Number of | Timing     |

|----------|-----------|-----------|-----------|-----------|------------|

|          | Frequency | Bandwidth | Length    | Channels  | Resolution |

|          | (GHz)     | (GHz)     | (Samples) |           | (psec)     |

| ASoC     | 3-5       | 0.8       | 16,000    | 4         | 35         |

| SAMPIC   | 3-10      | 2.5       | 64        | 16        | 10         |

| HDSoC    | 1-3       | 0.6       | 2000      | 64        | 80         |

| AARDVARC | 8-14      | 2.5       | 32,000    | 4         | 10         |

| AODS     | 1-2       | 1.0       | 8000      | 4         | 100        |

| UDC      | 8-10      | 1.5-2     | 4000      | 16/32     | 10         |

| PSEC4    | 5-17      | 1.6       | 256       | 6         | 5          |

| PSEC5    | 5-40      | 3.0       | 4096/64   | 9         | 1          |

H. Frisch et al., A High-Performance Multi-Channel Low-Power ASIC with One Pico-second Resolution for Emerging Detector Technologies in Positron-Emission Tomography, Particle Physics, and Astrophysics