# A real time sub-picosecond phase correction system

D. Dehmeshki, A. Elhadi, E. Frahm, R. Rusack, *R. Saradhy*, Y. Tousi 29/05/2023

# The need for Precision Timing

- The use of precision timing to measure time-of-flight or to distinguish events from the same bunch crossing in collider detectors has become a common feature of many modern experiments.

- Many new experiments are pushing the boundaries of precision timing measurements to improve background suppression and precision measurements

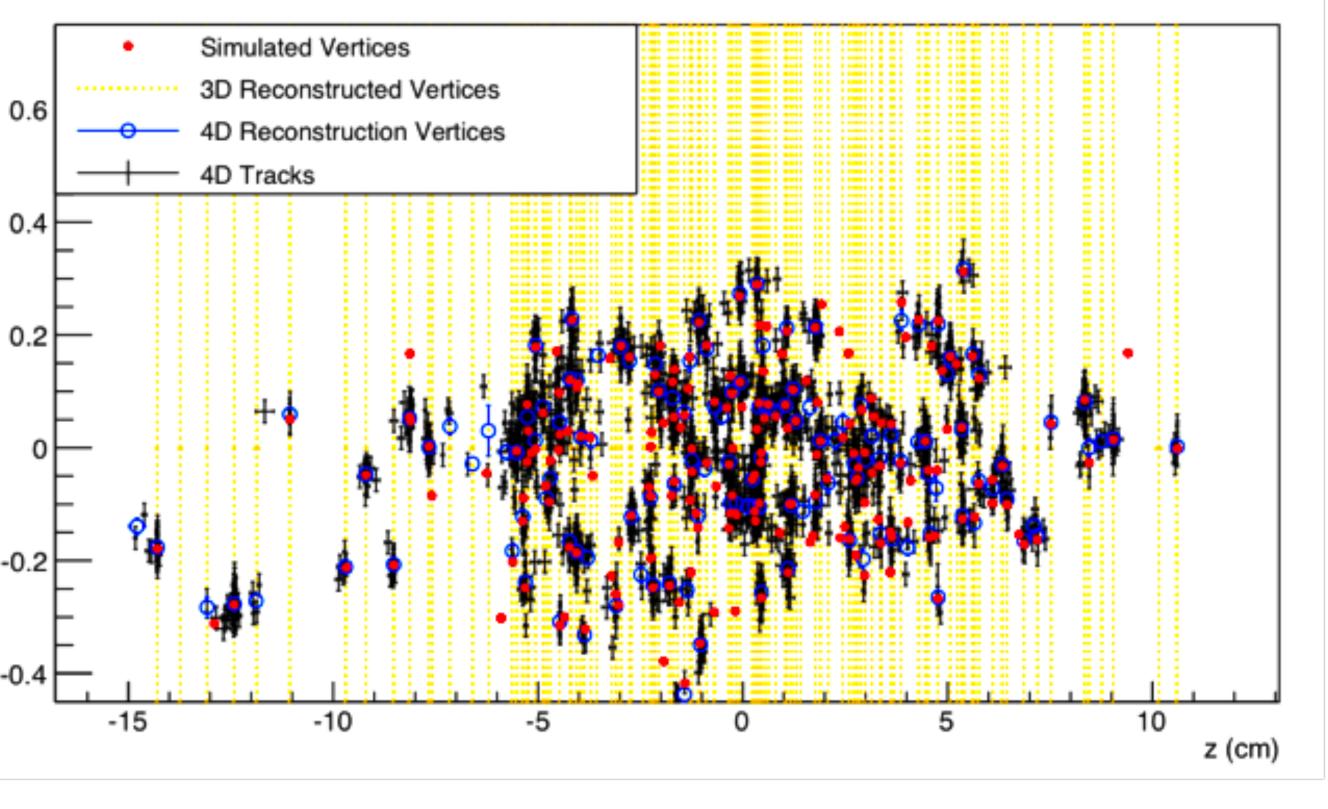

### HL-LHC time v. Position of 140 pile up bunch crossing.

Figure shows the simulation of CMS detector where vertices that are overlapped spatially can be resolved in the time domain

https://doi.org/10.22323/1.398.0813

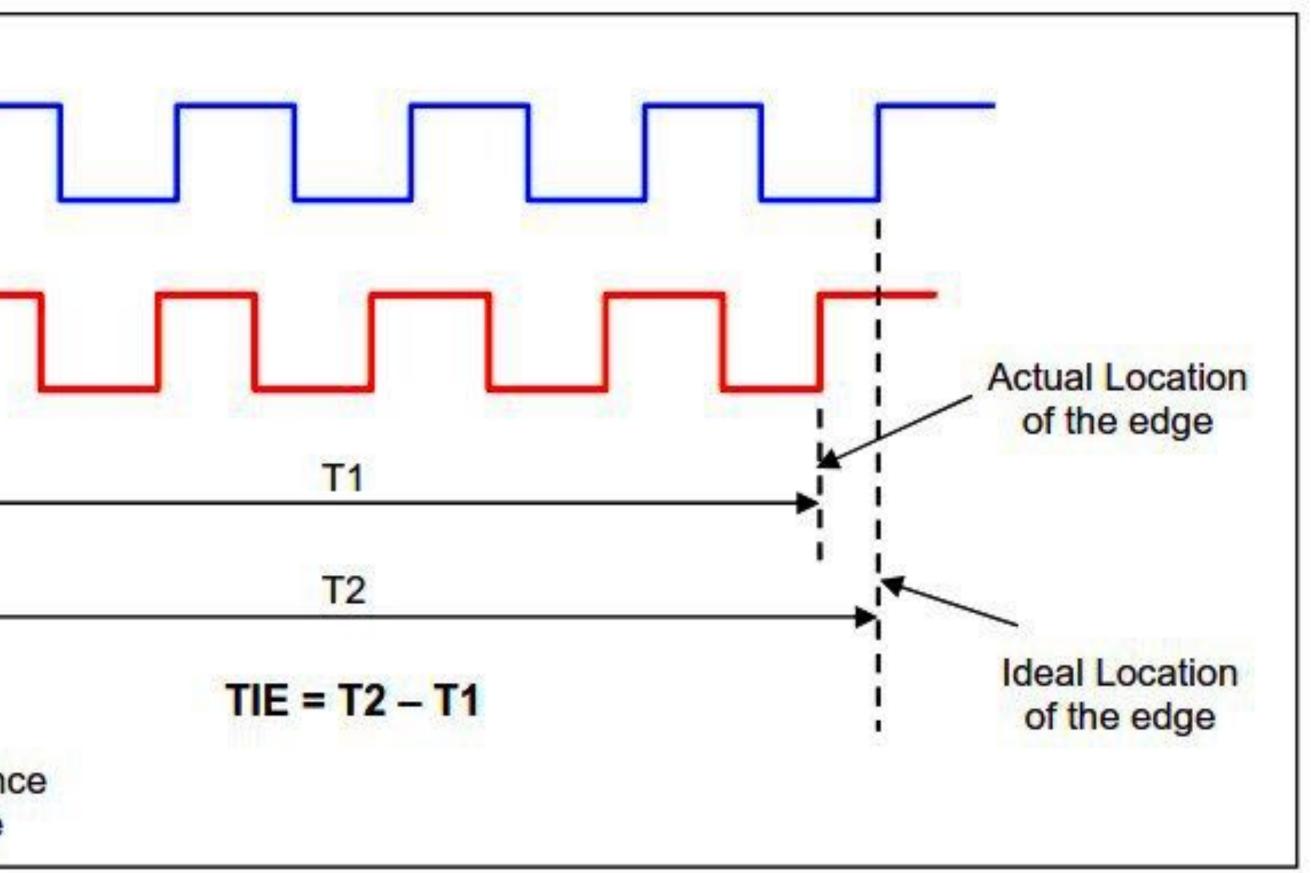

### **Time Interval Error (TIE)** Quantifying Time Jitter in Clocks

- The Time Interval Error is the time difference between the edge of the reference clock and the edge of the distributed clock

- TIE is measured for multiple edges and the standard deviation is quoted as a measure of jitter/wander.

- High speed variation in TIE is called <u>Jitter</u>

- Low speed variations in TIE is called <u>Wander</u>

| Ref. Clock           |             |

|----------------------|-------------|

| Diatributed          |             |

| Distributed<br>Clock |             |

|                      |             |

|                      |             |

|                      |             |

| Refe                 | eren<br>dge |

|                      |             |

# **Precision Timing Needs Better Clocks**

The time resolution of the detector system has contributions from

need to have a reference clock with jitter that adds marginally to the measurement that you are making

Lets look at such a scalable prototype without jitter attenuator

$$\sigma_t^{ele} \oplus \sigma_t^{detector} \dots$$

• In order to measure the time of interaction in your detector precisely, you

Jitter (High Speed Variations) can be mitigated using jitter attenuators and dedicated channels for distribution

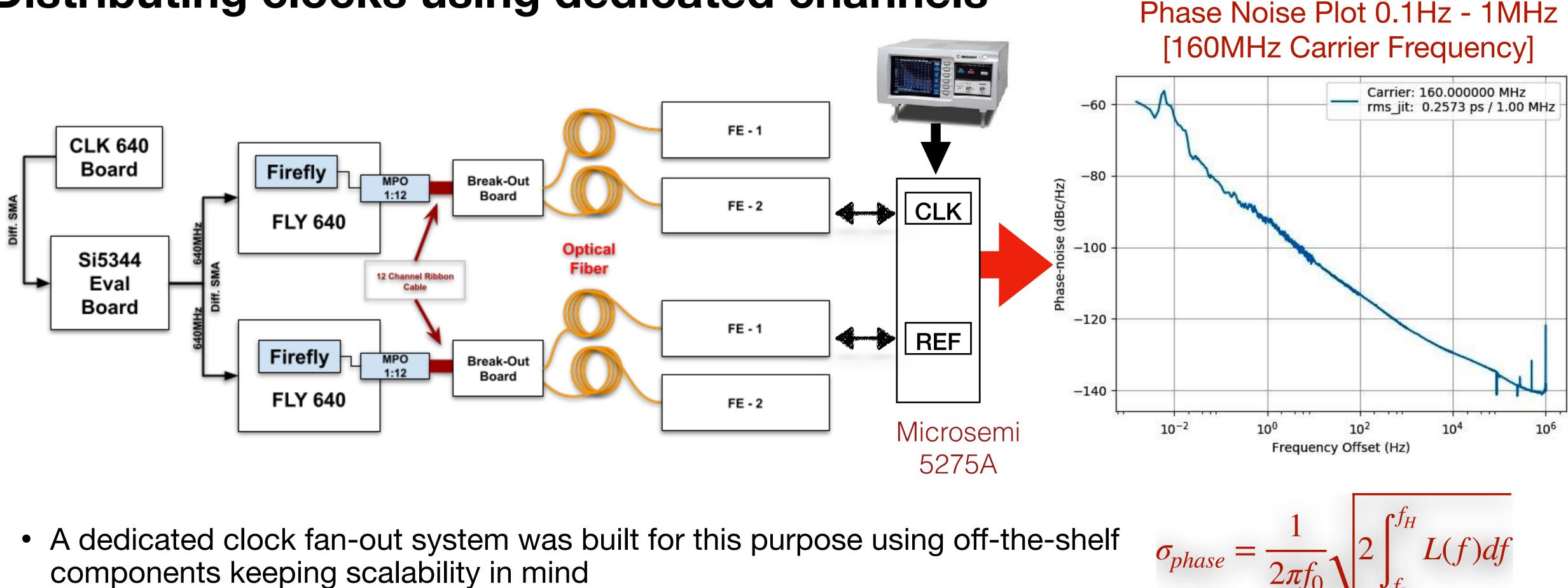

# **'Pure' Clock Distribution System Distributing clocks using dedicated channels**

- - RF Quality Fanout from ON Semiconductor (NB7VQ1005MMNG)

- Each FLY 640 board scalable up to 216 output channels employing 18 fireflies

$\sigma_{phase} = 0.26 ps$

### But what about wander?

Note: Light travels ~300 microns in a picosecond in free space

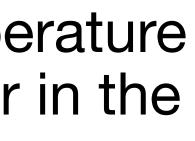

### **Effects of Environment** on the Clock

- Environmental effects such as temperature can introduce low frequency wander in the distributed clock

- Propagation time of 100m long multi-mode fibre changes by ~16ps/°C

- Dedicated channels or jitter attenuator won't mitigate these effects

For a high precision clock, we need to monitor these shifts and correct for it.

7

# Questions: 1. How do we measure wander? 2. How do we correct for it?

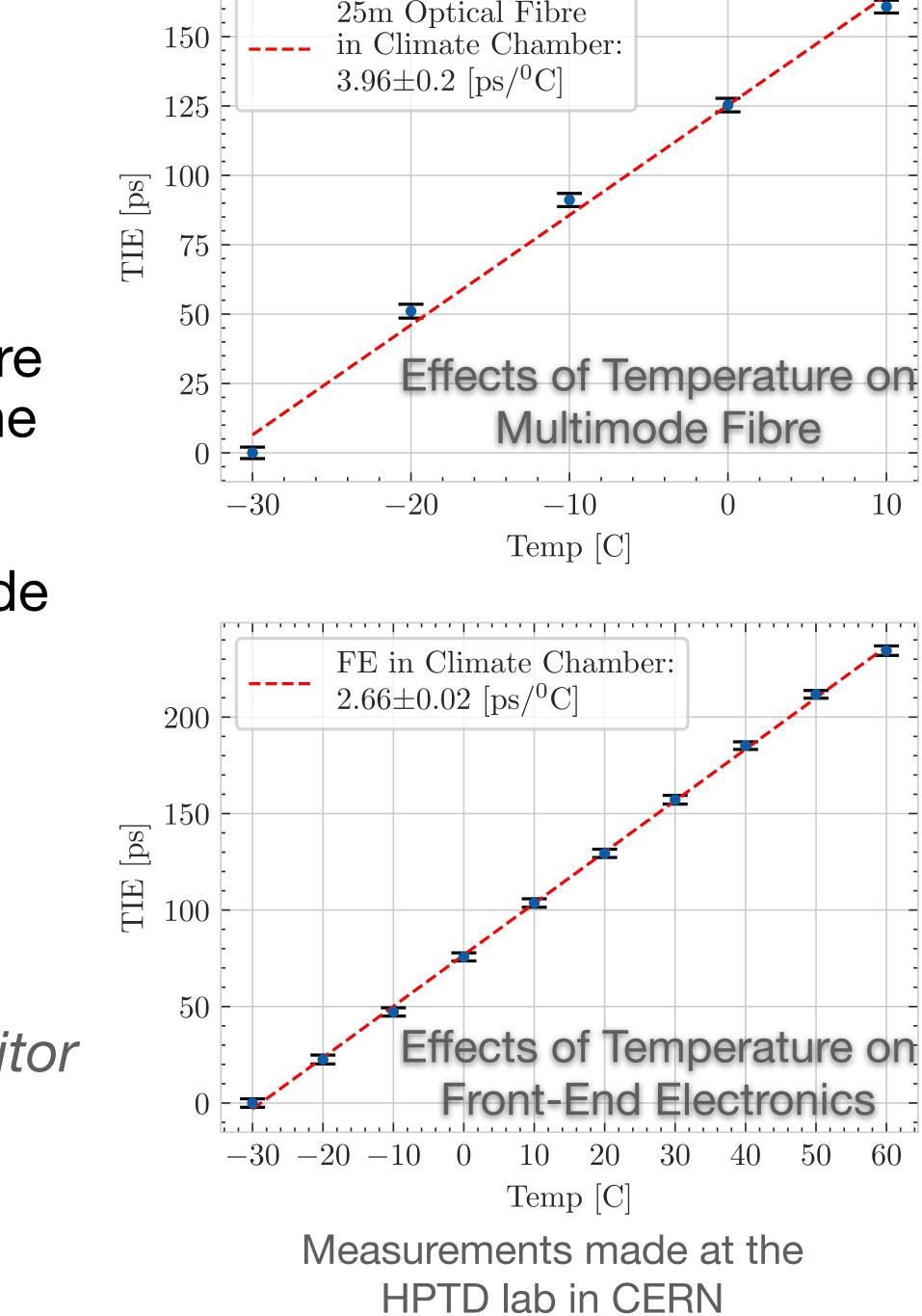

### **Measuring Time** Digital Dual Mixer Time Difference (DDMTD) circuit \*

- Reference Clock and Test Clock are heterodyned with the help of a PLL and Flip Flops

- The PLL generates Offset Clock with the frequency relation:

$$f_{offset} = f_{ref} \cdot \frac{1}{N+1}$$

- N is the integer that determines the number of input clock cycles required for a full phase cycle of the heterodyned signal

- The time difference between the beat clocks is used to calculate TIE between the Ref.Clock and the Test Clock

\*First proposed by P. Moriera in 2010

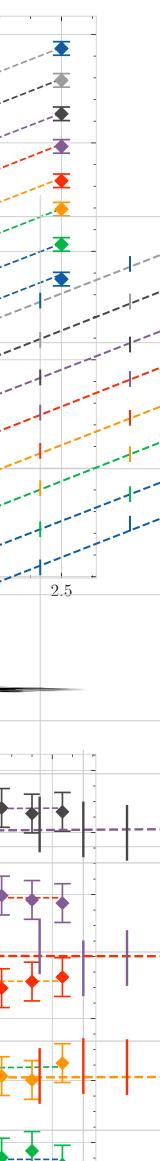

### This means sub-picosecond precision Plugging in some numbers

$$f_{beat} = \frac{1}{N} \cdot f_{offset} = \frac{1}{N+1} \cdot f_{ref}$$

$$\Delta t_{min} = \frac{\Delta t_{beat}}{N+1}$$

With N = 100k,  $f_{ref} = 160MHz$ ,

$$f_{beat} = 1.599984 \text{ kHz}$$

$$\Delta t_{min} = 62.5 fs$$

Note that as we sample at  $f_{beat}$ , we lose sensitivity to higher frequency jitter.

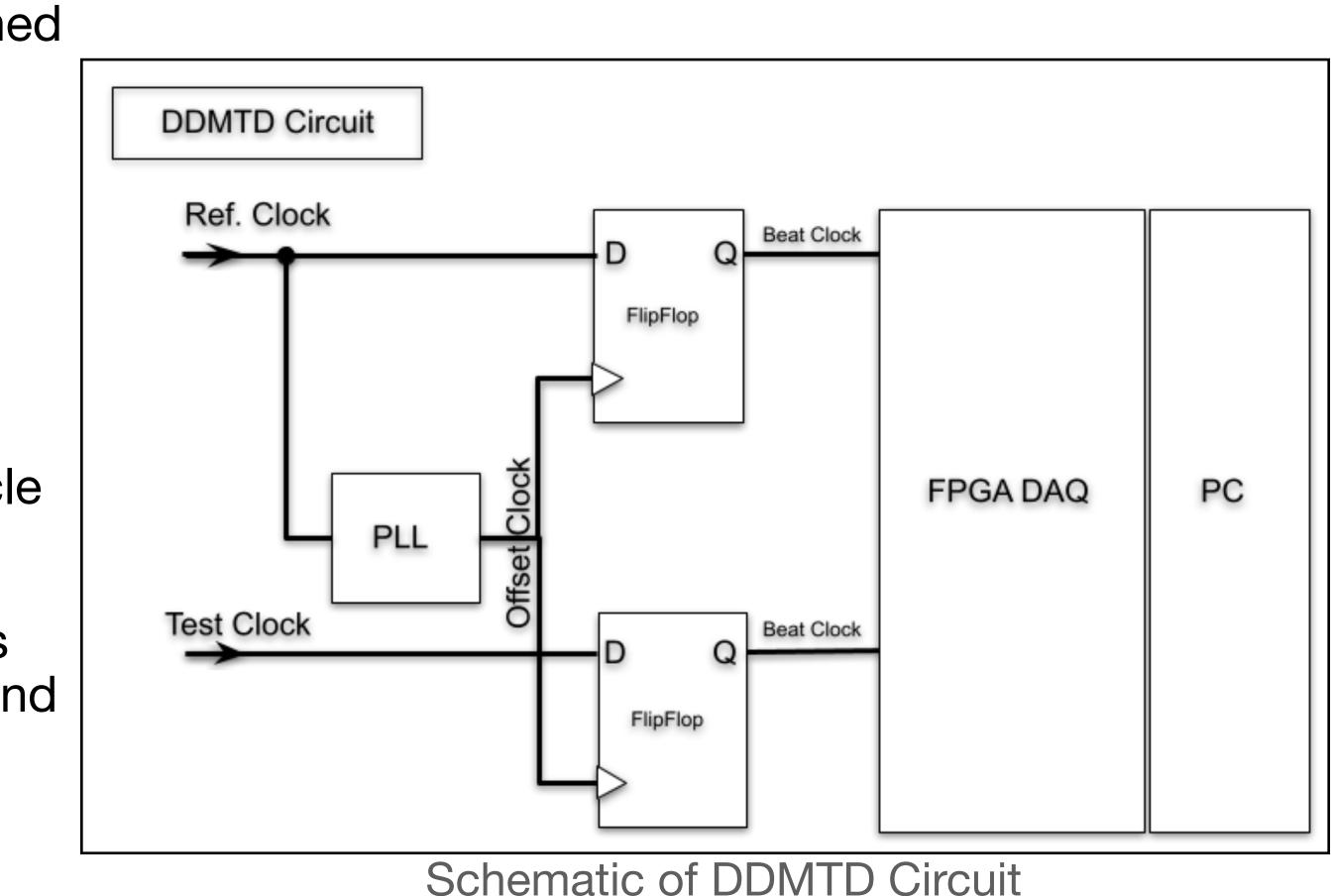

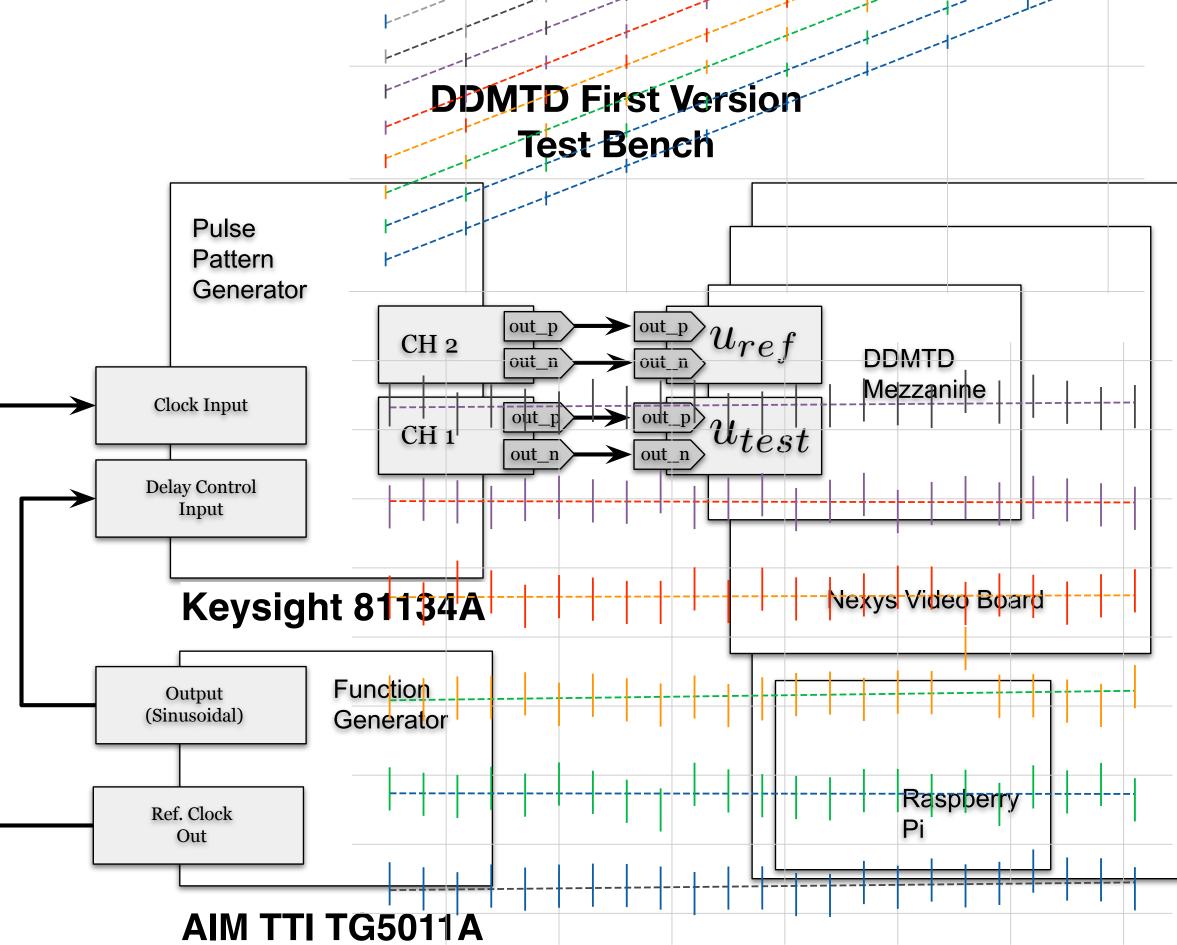

First Version of Single Channel DDMTD Board

### DDNTD Performance

More Information Published Here: 10.1088/1748-0221/18/01/T01003

11

### **Revisiting Pure Clock Distribution Measurements made using DDMTD**

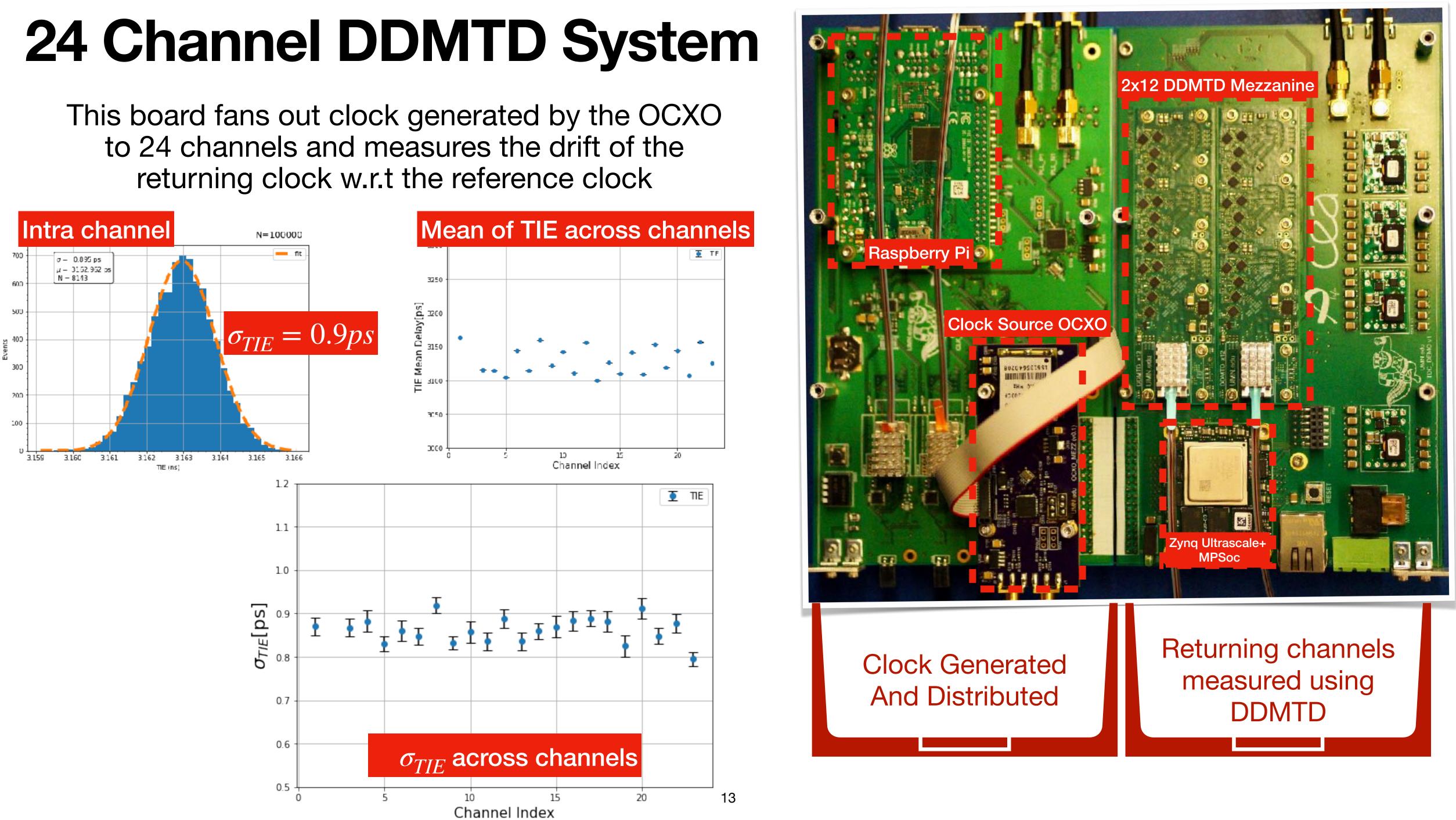

returning clock w.r.t the reference clock

# Questions: 1. How do we measure wander? 2. How do we correct for it?

### **Correcting for Drifts in Clock** How Digitally Controlled Phase Shifter (DCPS) Works

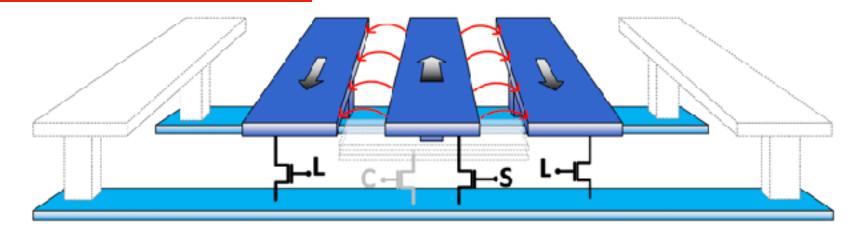

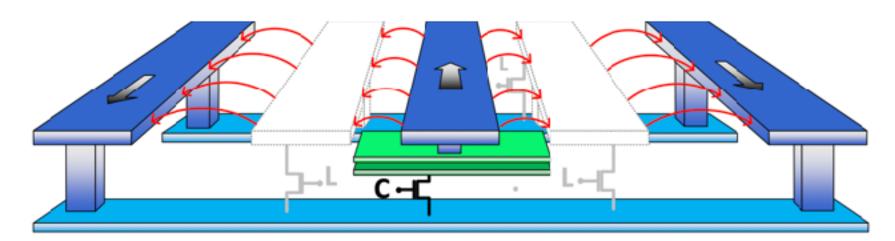

### **3D structure of a unit cell**

- Coplanar waveguide with ground return lines

- Transmission line delay is tuned by controlling the propagation velocity

#### Low Delay State

### **High Delay State**

0.8mm

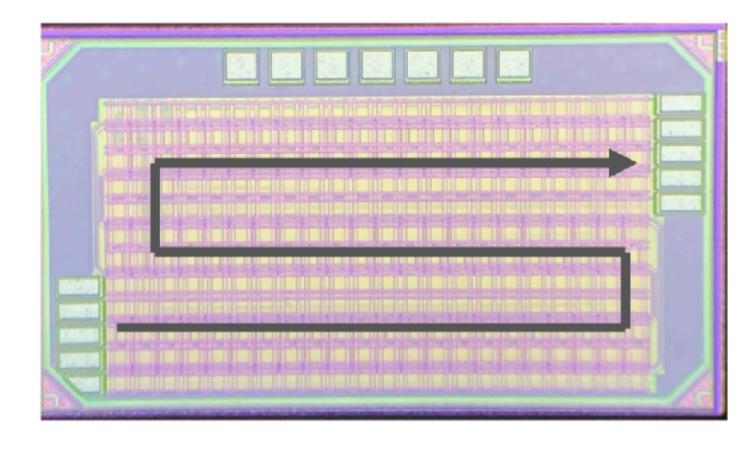

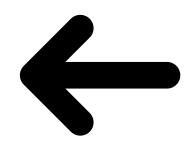

- Chip fabricated with TSMC 65nm CMOS process

- Consists of 66 delay units arranged in 3 rows

1.3mm

- Chip are wire-bonded to the mezzanine board

- 2 out of 12 channels are populated in this particular board

### n TSMC ss y units

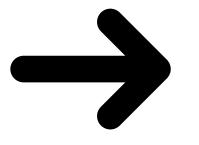

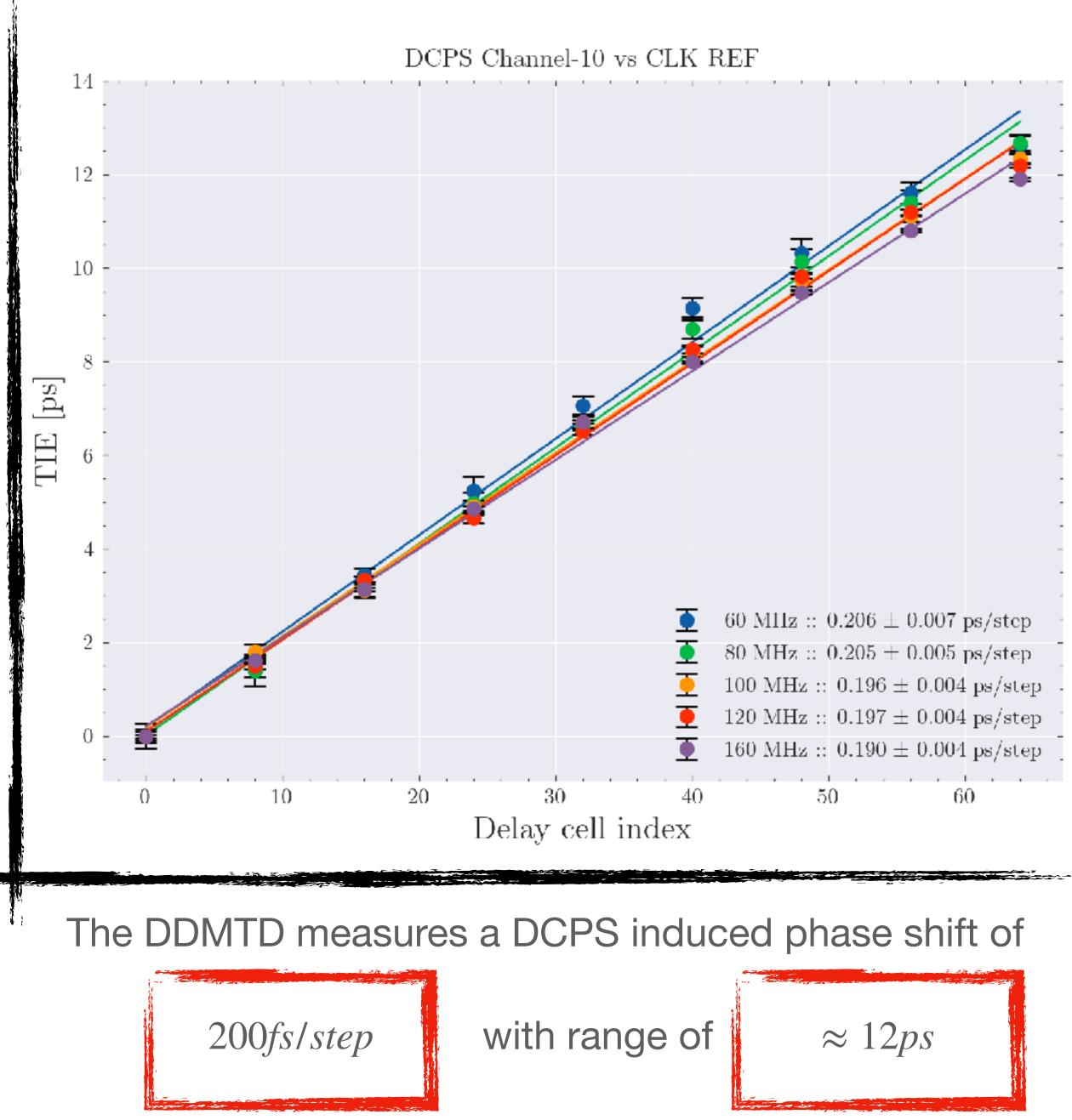

### Multi Channel DCPS Test Bench

Delay measurements were made by activating the delay steps of the ASIC cumulatively (in steps of 8 units)

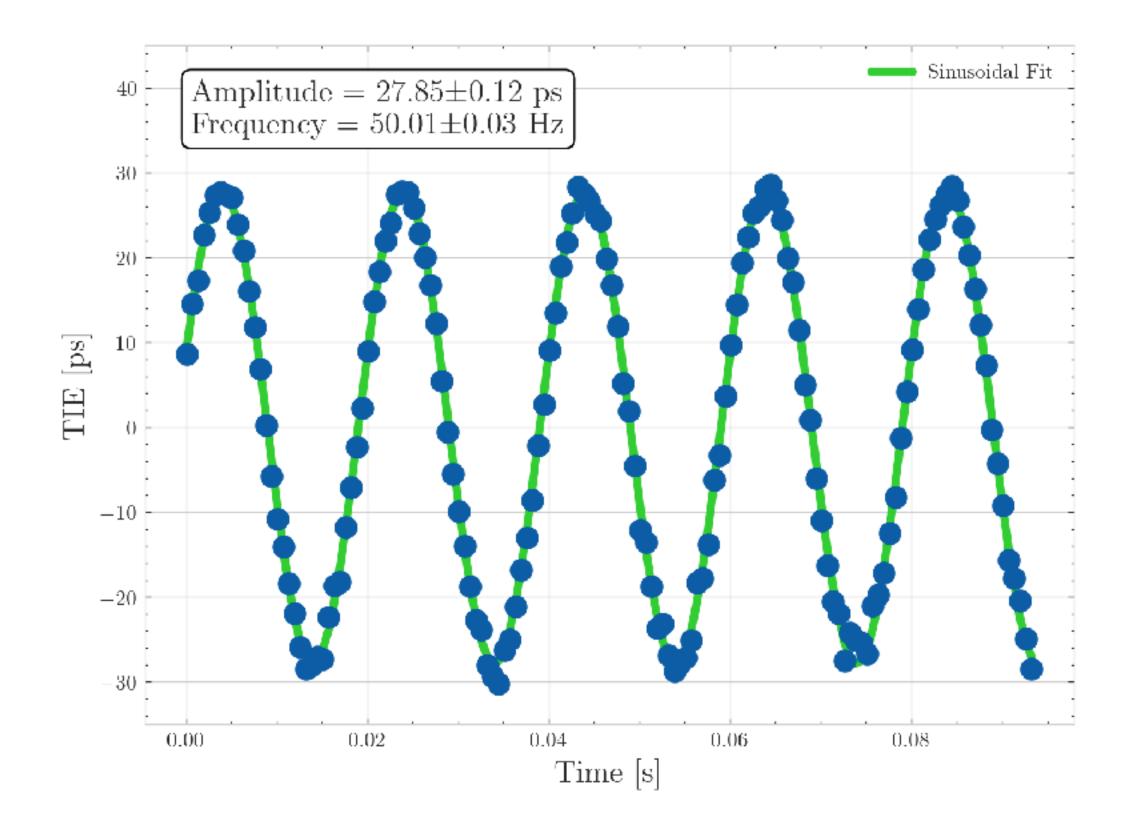

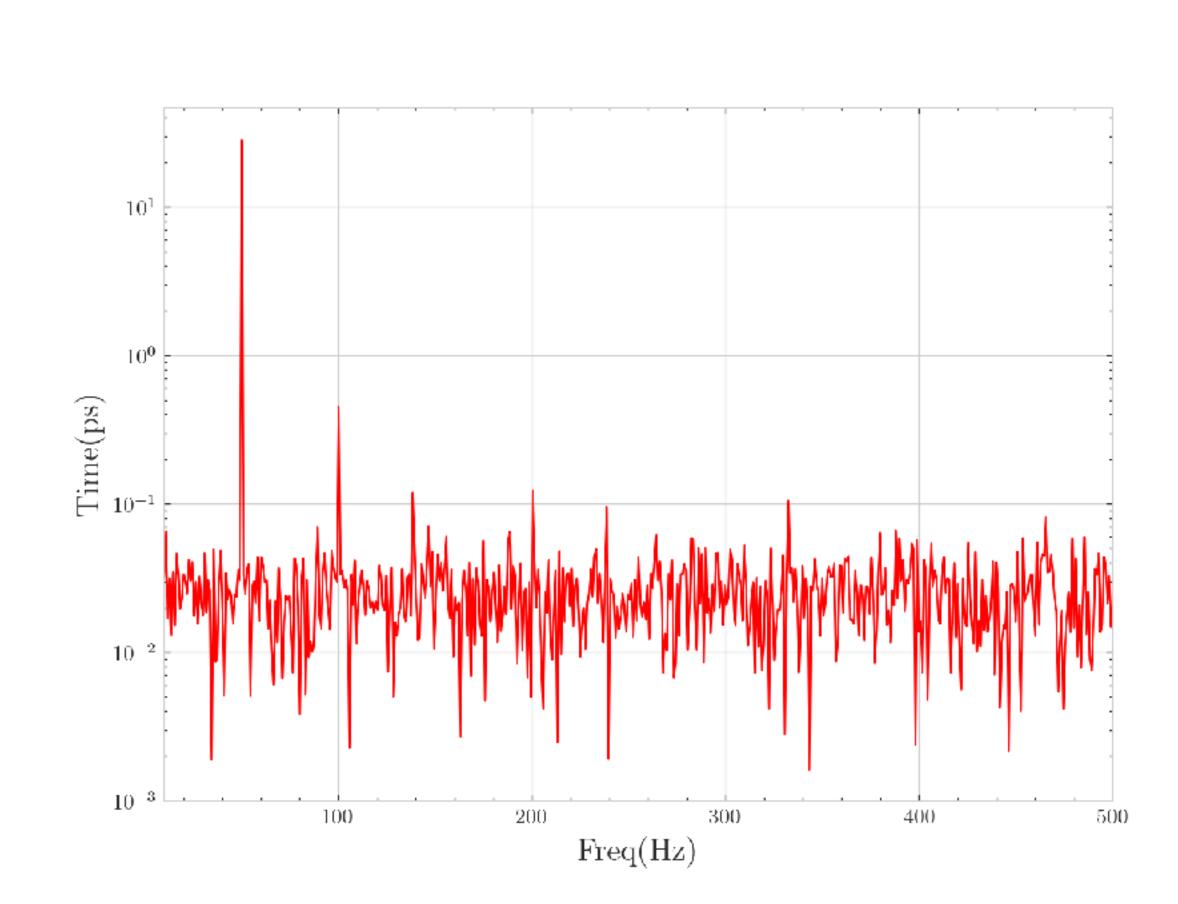

We measured the TIE b/w the distributed clock and the reference clock using DDMTD

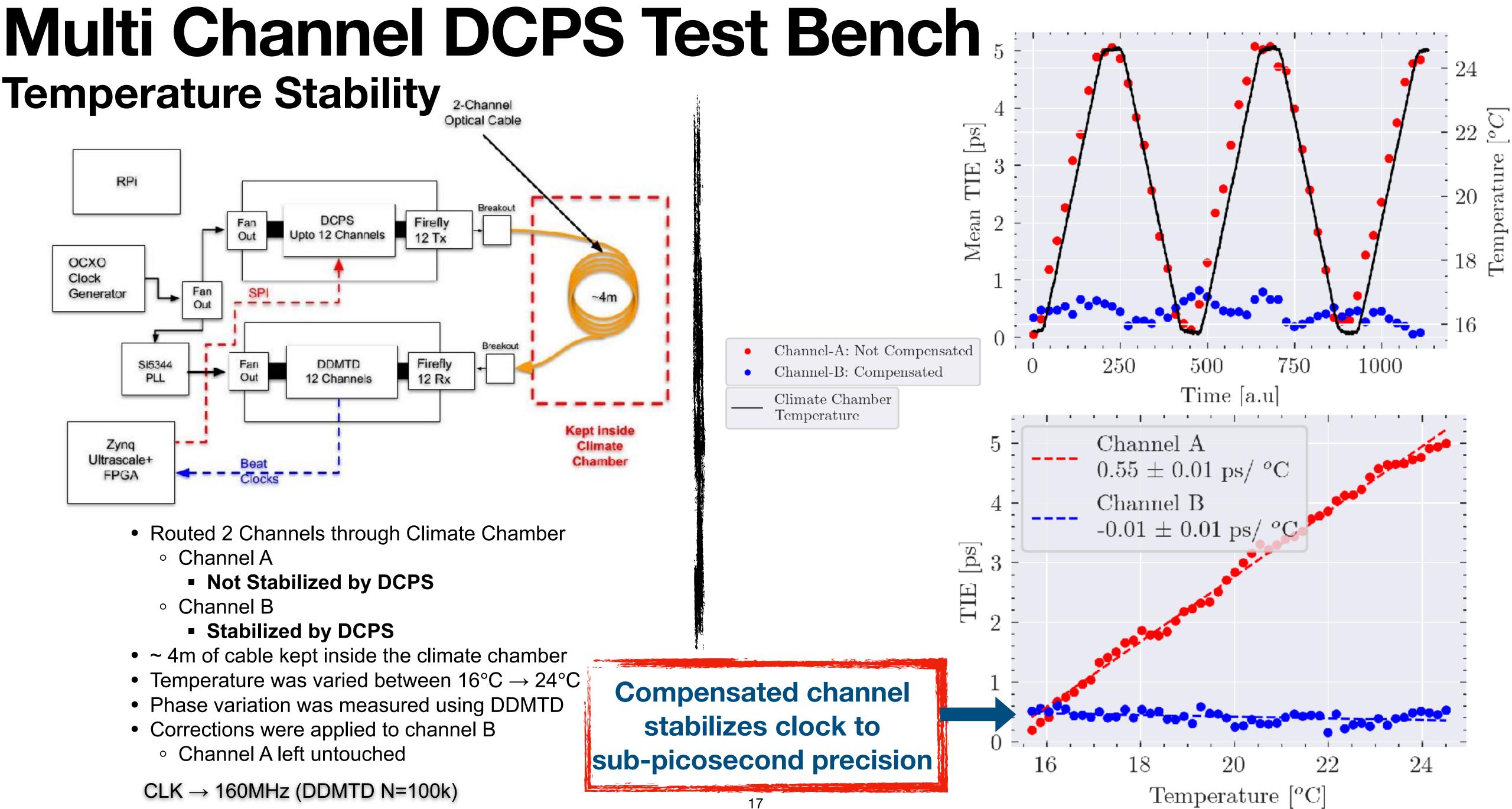

### **Temperature Stability** 2-Channel

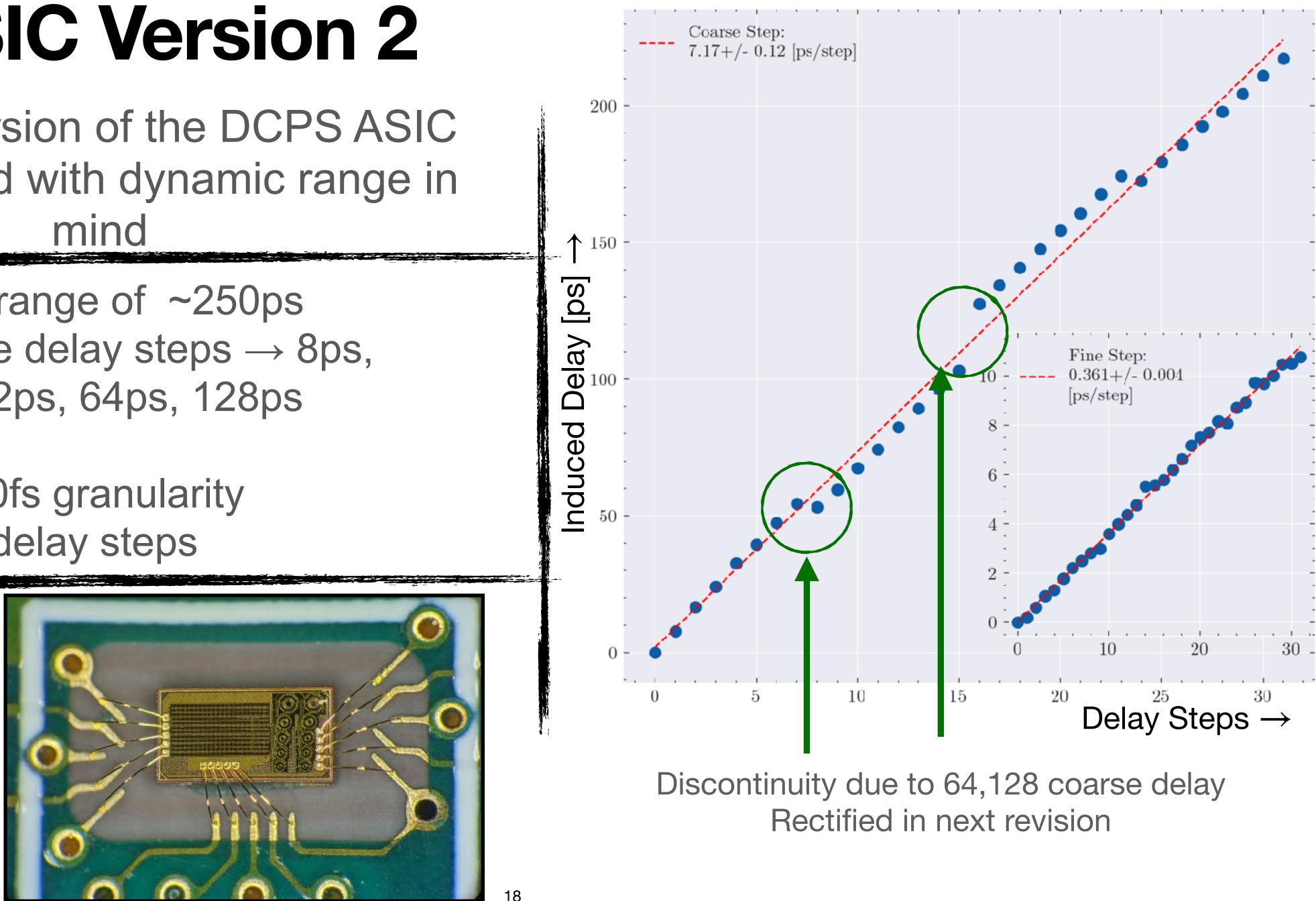

# **DCPS ASIC Version 2**

A second version of the DCPS ASIC was designed with dynamic range in mind

• Dynamic range of ~250ps • 5 coarse delay steps  $\rightarrow$  8ps, 16ps, 32ps, 64ps, 128ps

• With ~400fs granularity 32 fine delay steps

**ASIC Under** Microscope

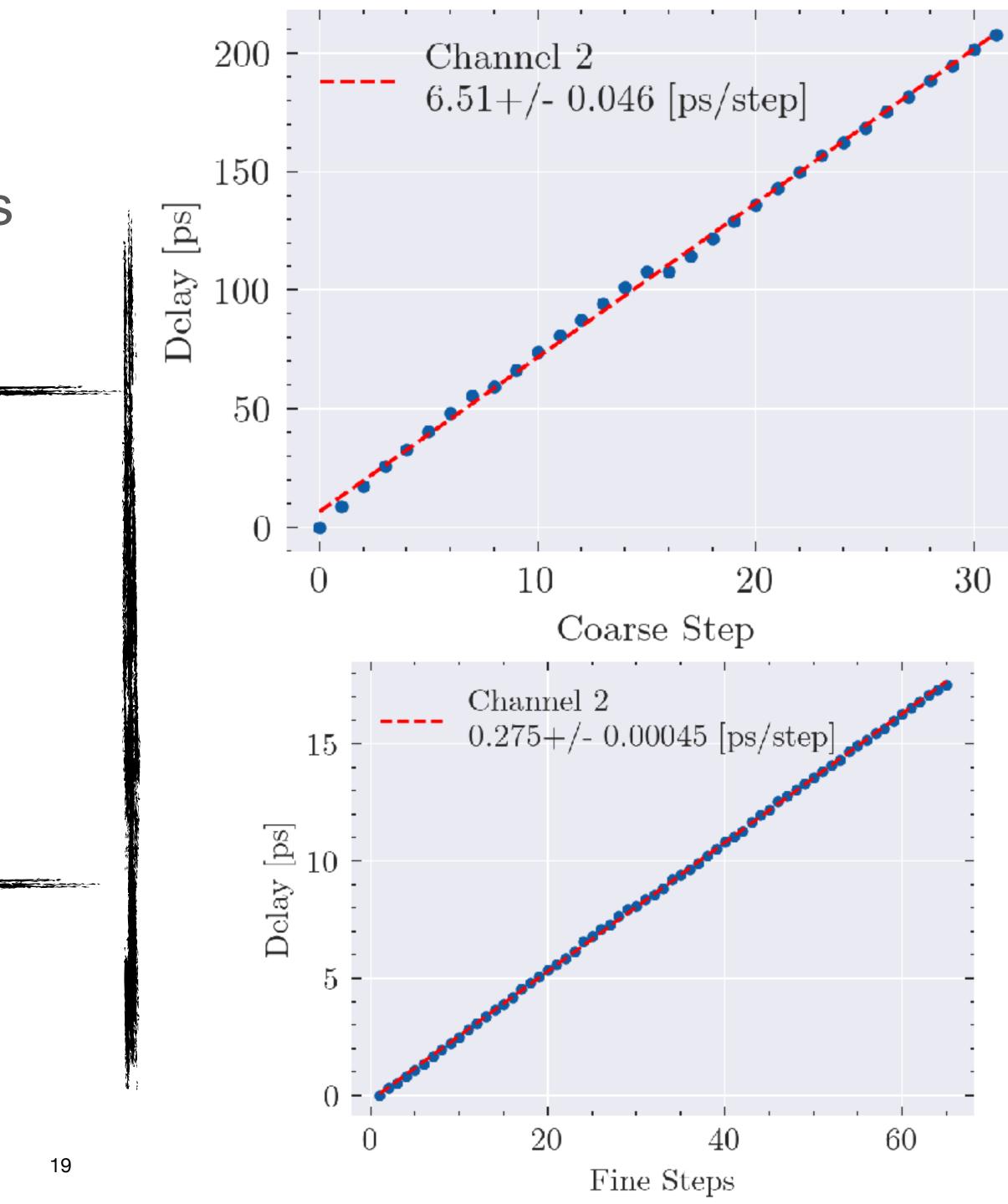

# **DCPS ASIC Version 3**

A third version of the DCPS ASIC was designed with radiation tolerance in mind

Dynamic range of ~250ps

5 coarse delay steps → 8ps, 16ps, 32ps, 64ps, 128ps

2 Tuning Bits

With ~300fs granularity

66 fine delay steps

DCPS v3 has been designed with radiation tolerant I2C controller

Further tests are being conducted (including radiation hardness)

## Summary

#### **Pure Clock Distribution System & DDMTD**

- Demonstrated a scalable clock distribution system that is capable of distributing clocks with sub-picosecond precision

- DDMTD circuit is a low cost circuit capable of tracking low frequency wanders of the clock

#### 24 Channel DDMTD Board

- Developed system capable of tracking the long term wander of 24 channels of clock simultaneously.

- Scalable architecture, developed with offline corrections in mind

- Each channel provides sub-picosecond precision

- Stability of the DDMTD measurements are consistent across channels

#### **Digitally Controlled Phase Shifter ASIC**

- Demonstrated system capable of tracking long term wander of the clock and correcting for it in real time with sub-picosecond precision

- The DCPS distributing the clock doesn't introduce a significant amount of phase noise

- High Dynamic Range >200ps with ~300fs steps

- Designed to be dispersion free up-to ~500MHz

- Radiation tolerant (DCPS v3)

# Acknowledgements

- Award Number DE-SC0020185

- of the DDMTD Board

- Special thanks to Fermilab for helping us with the radiation tolerant DCPS v3

This project is funded by US-DOE Office of Science (High Energy Physics) under

• We thank HPTD lab at CERN for all their support during commissioning and testing

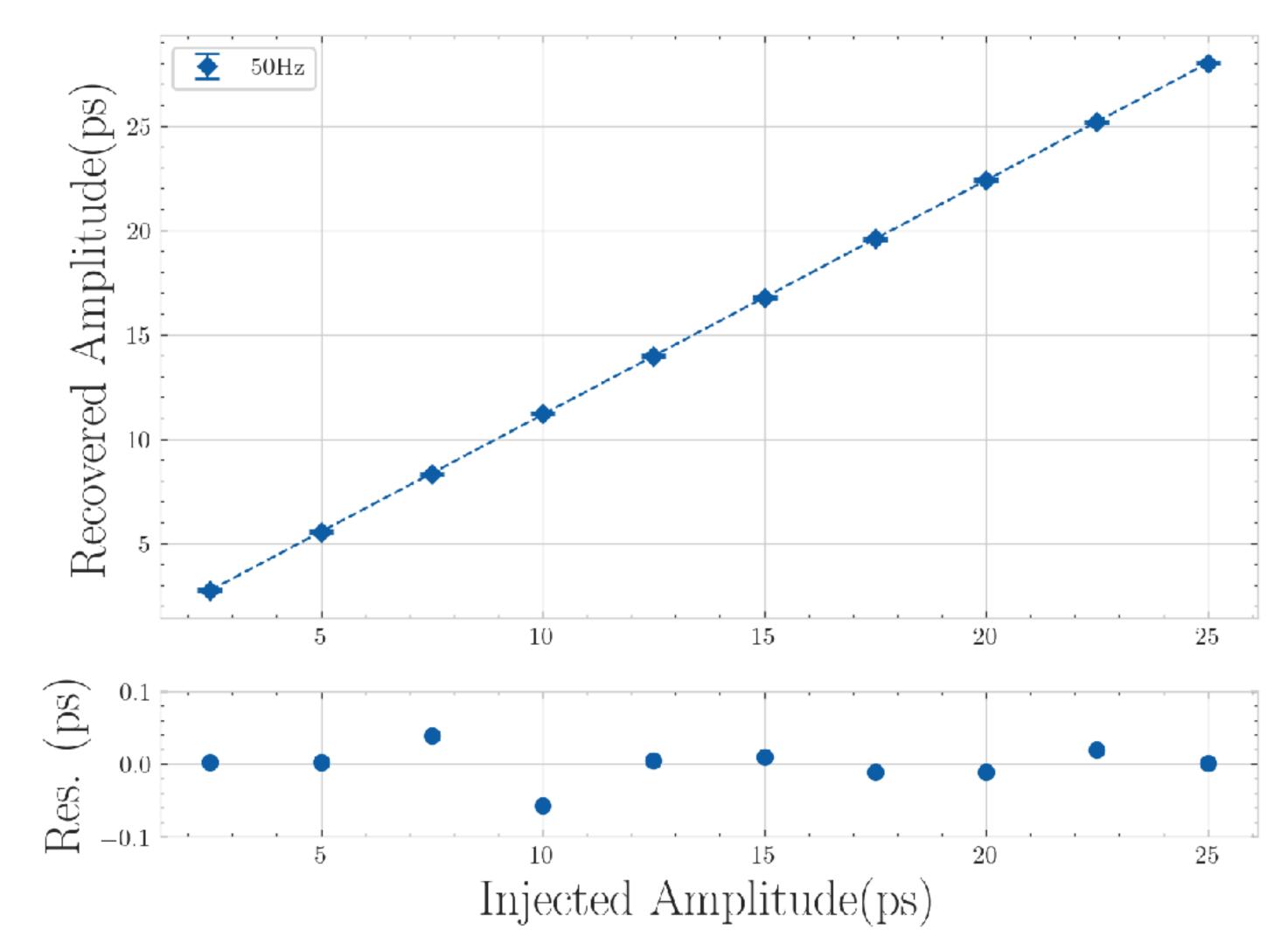

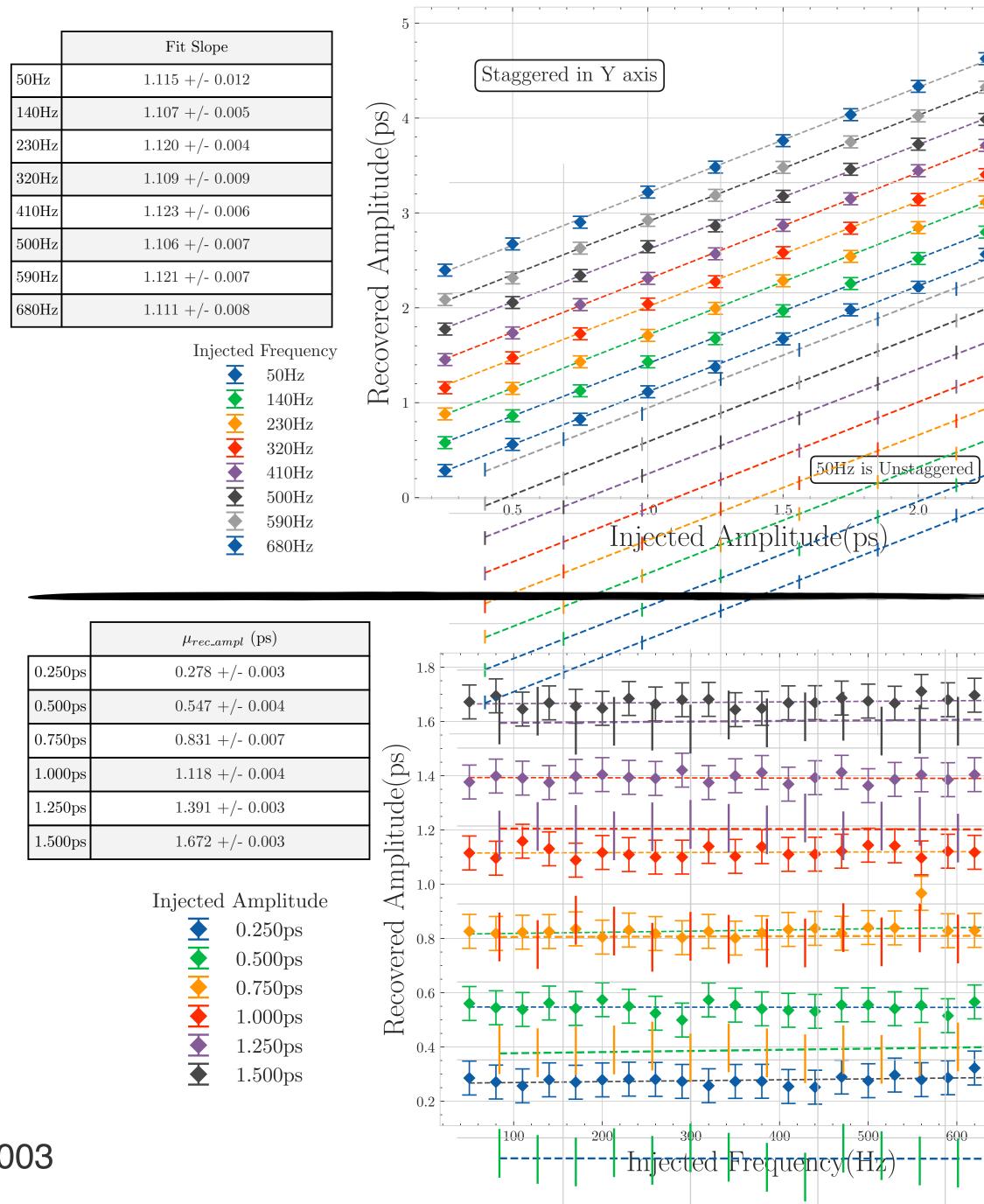

## **DDMTD Performance**

## **DDMTD Linearity**