# Caribou DAQ

M. Benoit (ORNL), E. Buschmann (CERN), Hucheng Chen (BNL), <u>D. Dannheim</u> (CERN), M. Pijacki (Carleton), Simon Spannagel (DESY), T. Vanat (DESY)

# Caribou DAQ System

### Caribou versatile open-source DAQ system

- Re-usable hardware, firmware and software

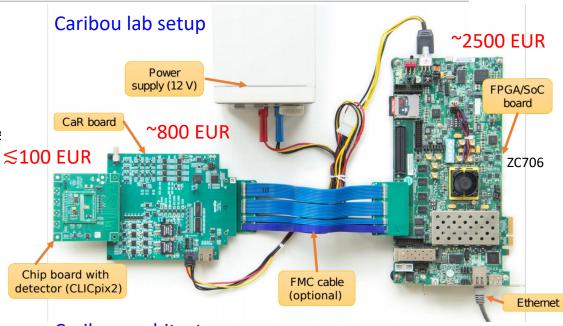

- System-on-Chip (SoC) board

- Embedded CPU for Linux operating system, DAQ software (Peary), user interface

- FPGA for detector control and data processing, TDC

- Common Carboard interface board

- Physical interface from SoC board to detector

- Provides resources (voltage regulators, ADCs, pulse/clock generator)

- Application-specific chip carrier boards

- Detector and passive components

### Target applications:

- Lab and beam tests of silicon-detectors

- Optimised for R&D support, easy integration of new prototypes

- Not targeting project-specific DAQ in large experiments

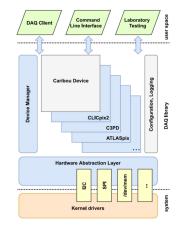

#### Caribou architecture

https://gitlab.cern.ch/Caribou/

http://dx.doi.org/10.1088/1748-

0221/12/01/P01008

http://dx.doi.org/10.22323/1.370.0100

https://doi.org/10.1088/1748-0221/18/02/C02005

# Application examples

#### Caribou integration of many detectors

Profit from re-usable firmware and software

→ largely reduced integration time for new devices

### Support for various readout schemes:

- digital interface via GTx or LVDS

- analogue waveforms (sampling ADCs or external oscilloscope)

- TDC in FPGA (<10ps resolution)</li>

#### Integration in beam-telescope setups

FEI4, Timepix3, Mimosa, ALPIDE

### Caribou chip-board examples

FEI4+H35Demo

APTS (65 nm)

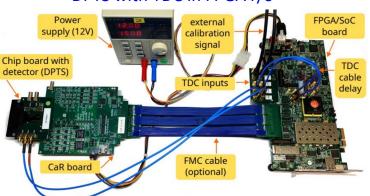

DPTS (65 nm)

#### FASTpix with oscilloscope r/o

DPTS with TDC in FPGA r/o

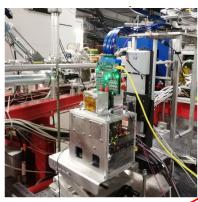

### CLICdp Timepix3 @ CERN

# Telescope integration Mimosa @ DESY

**ALPIDE @ MAMI**

# Development and support

BNL OMEGA group, Carleton University, ORNL

Design of Common Hardware (Carboard)

### CERN / EP R&D

Coordination of common hardware production, firmware development, user support

## DESY / Tangerine:

Coordination of common Peary Software, test-beam integration

### AIDAinnova, RD50

Funding for development and hardware production

# Caribou in RD50

- Caribou used in 10 RD50 member institutes, mostly for HV-CMOS DMAPS prototype development and related radiation-hardness studies

- RD50 common project since 2021

- Support from RD50 for production of batch of 20 Carboards v1.4

- ~50% of the production cost from RD50 common fund (10k EUR)

- Design, prototyping and validation of the new Carboard v1.4 provided by BNL, with support from CERN

- Purchase order, testing, rework, shipment + invoicing provided by CERN

- Significant benefits with modest amount of funding:

- Coordinated purchase reduced price and overhead for institutes

- Project gained visibility and approval status

→ important to secure additional resources

- Incentive for institutes to "get things started" and deliver testing results

| RD50 Caribou participant     | contact        |

|------------------------------|----------------|

| CERN                         | D. Dannheim    |

| BNL                          | H. Chen        |

| DESY                         | S. Spannagel   |

| Univ. Liverpool              | E. Vilella     |

| IFIC Valencia                | R.M. Hernandez |

| HEPHY Vienna                 | T. Bergauer    |

| Jožef Stefan Inst. Ljubljana | I. Mandic      |

| Uni. Sevilla                 | R. Palomo      |

| NIKHEF                       | J. Sonneveld   |

| Lancaster Univ.              | D. Münstermann |

# Ongoing developments and future plans

## Caribou 2.0:

- Carboard 2.0 currently under development

- System-on-Module (SoM) platform based on Zynq UltraScale+

- Replace combination of Xilinx evaluation board + Carboard with a single custom carrier board housing the SoM

- → Reduced cost and improved performance

- Ongoing hardware design effort by Carleton University / BNL / ORNL

- Pre-prototype carrier board tests at BNL using XU1 SoM validated the digital design successfully (M. Benoit and D. Matakias)

- List of resources and design features iterated in Caribou user meetings

- Carboard 2.0 design in progress (M. Pijacki)

- Aim for first prototypes by mid 2023

# Future Caribou extension:

- Caribou version geared towards operating several already characterized detector modules in parallel

- e.g. as a flexible DAQ system for a future beam telescope

#### Enclustra Mercury+ XU1 SoM

#### Pre-prototype for Caribou 2.0 @ BNL

# Caribou in DRD3

# Caribou has proven beneficial for RD50 institutes

- Profit from existing re-usable hardware, firmware and software

- Community / best-effort support for integration of new detectors

- Financial support for hardware investments enables pooling of common DAQ infrastructure

- Visibility / approval status

# We propose to include Caribou as common project in DRD3

- Open to new contributors and use cases

- Gives visibility to project and to groups active in DAQ for detector testing

- Facilitates securing external resources

- Common-fund support helps to accelerate common investments,

e.g. participation in cost for Carboard 2.0 production, contribution to future multi-plane Caribou version