## Cryogenic temperatures

### 7.4: EXTREME ENVIRONMENT AND LONGEVITY

IMPLEMENTING DRD7: AN R&D COLLABORATION ON ELECTRONICS AND ON-DETECTOR PROCESSING

Manuel Rolo manuel.rolo@cern.ch darochar@to.infn.it

## "Deep Cryogenic" electronics for Quantum technologies

- Future R&Ds will propose the development of novel quantum sensor technologies through the consolidation and scaling up of existing and emerging technologies;

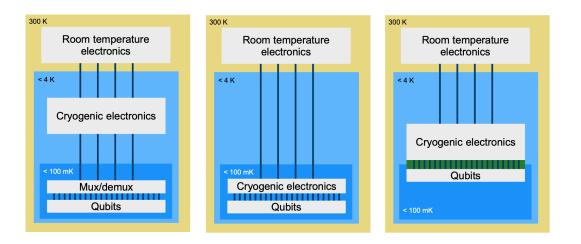

- provide advanced enabling infrastructures and key capabilities for the development of cryogenic electronics in order to solve "the wiring bottleneck" on quantum computers (*see talk from Patrick Vliex*);

- cryogenic CMOS operating <4K and down to the mK will pave the way for scalability into the million qubit realm.</p>

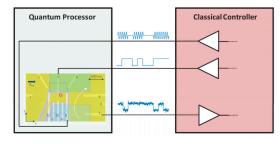

#### **Classical Controller**

- Electronics to control and read-out the quantum processor mostly operated at room temperature (RT)

- Does not scale with the number of qubits

E. Charbon, ESSCIRC 2019.

B. Patra, *et al.*, JSSC, vol. 53, no. 1, 2018.

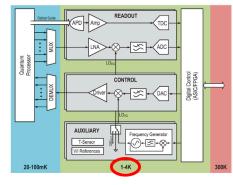

#### **CMOS Integrated Controller**

More scalable approach by moving the control and read-out electronics closer to the qubits and operate it at cryogenic temperature (around 4 K)

C. Degenhardt, "Cryogenic QUBIT Control – The Tyranny of numbers, self-heating and everything"

C. Enz, A. Beckers and F. Jazaer, "MOSFET Compact Modeling down to Cryogenic Temperatures"

## "Mild cryogenic" electronics for Liquid Detectors

- Rare-event search on astroparticles: neutrino physics and direct dark matter detection using liquid scintillators e.g. Liquid Xenon (LXe) and Liquid Argon (LAr);

- Single and dual-phase detectors employing (solid-state) photon sensors require front-end readout electronics operating at 165K (LXe) or 88K (LAr).

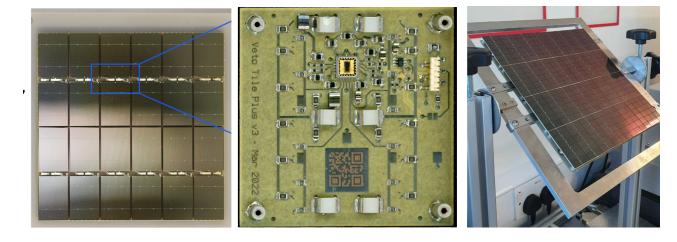

Darkside-20K Veto Tile: Arlon-55NT substrate, hosts 24 SiPMs on front, front end QFN-20 packaged ASIC electronics on back; Motherboard hosts 16 vTiles, sums signals from each quadrant; Outputs 4 differential analogue channels.

| Experiment   | Type | Photon detector                           | Area $(m^2)$ |

|--------------|------|-------------------------------------------|--------------|

| nEXO         | LXe  | SiPMs (FBK [Ch2-18], Hamamatsu [Ch2-19]), | 5            |

|              |      | digital 3D-SiPM                           |              |

| DARWIN       | LXe  | PMTs, SiPMs or Hybrids                    | 8            |

|              |      | (SIGHT, ABALONE)                          |              |

| TAO          | LSci | FBK SiPMs                                 | 10           |

| DarkSide-20k | LAr  | SiPMs (FBK NUV-HD triple-dopant)          | 30           |

| ARGO         | LAr  | SiPM is baseline option                   | 200          |

| DUNE         | LAr  | Light guide or trap $+$ SiPM              | 10-1000      |

Need to commit to strong R&D programs for the development and deployment of new readout schemes suitable for future largescale neutrino and dark matter detectors; today's solutions are not scalable.

# Liquid Detectors: future facilities with cold readout and scalable DSP

Future larger scale experiments will call for innovative cold integrated readout electronics implementing digital signal processing within the photosensor detection module.

"R&D on the 5-year horizon for greater integration include (...) dedicated ASIC design; 3D-vertical integration R&D; and <u>development of lower-power, larger-area and lower-</u> <u>radioactivity photodetection modules</u>."

Scaling up with cryogenic mixed-signal CMOS based photodetector technology.

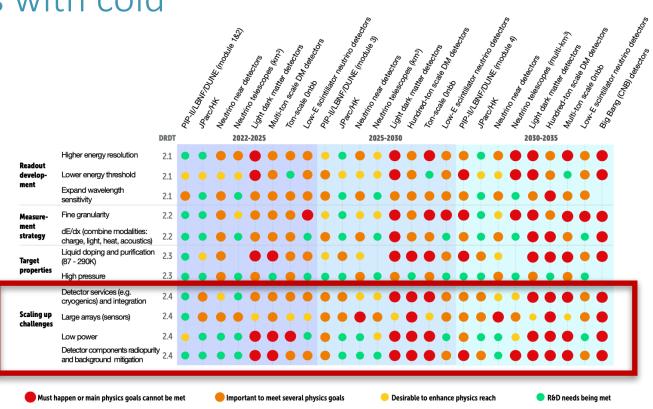

DRDT 2.1- Develop readout technology to increase spatial and energy resolution for liquid detectors  $\rightarrow$  achieve readout of more highly pixelated detectors with greater photon collection capabilities.

DRDT 2.2- Advance noise reduction in liquid detectors to lower signal energy thresholds  $\rightarrow$  future liquid detectors requires R&D to achieve lower sensor and electronics noise.

DRDT 2.4- Realise liquid detector technologies scalable for integration in large systems  $\rightarrow$  detectors with sensor areas reaching 10, 100 and ultimately 1000 m2.

## Outlook for Cryogenic (CMOS) Electronics and future R&D

- CMOS Process Design Kits typically valid down to 233K (-40°C), although models scale relatively well down to 77K. This was verified with VDSM bulk and FDSOI technology nodes.

- Cold CMOS PDKs are fundamental for the development of complex mixed-signal ASICs allowing for innovative detector architecture and concepts, data transfer, readout and control. A future collaboration R&D will certainly focus on infrastructures for device parameter extraction and modelling and development of cold PDKs.

- The sweet spot around LN boiling temperature (where we get the best of the MOSFET characteristics with still no saturation effects) opens promising prospects on the development of innovative readout concepts both for neutrino and dark matter detectors with noble liquids and, in general, for calorimeters and photo detectors operating at 77K.

- The growing interest on the use of CMOS for Quantum Computing and Quantum Sensing could open new opportunities for collaborative efforts with selected silicon foundries on the optimisation of solid-state sensors and CMOS processes for operation at cryogenic temperatures.