## Availability and Access to Advanced (Silicon) Technologies for the HEP community via the EUROPRACTICE services

Paul Malisse, imec

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121

EUROPRACTICE is a true one-stop shop that lowers the barrier to access all services that you need to design and fabricate electronic circuits and smart integrated systems:

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121

### **TODAY's Foundry Offerings**

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121

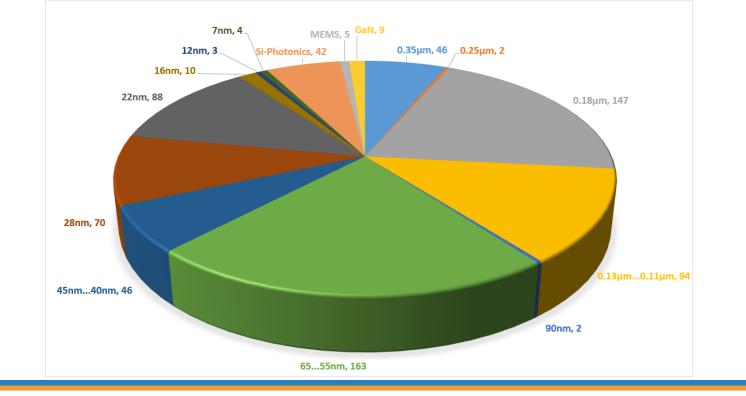

#### TODAY's ASIC technology usage - anno 2022

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121

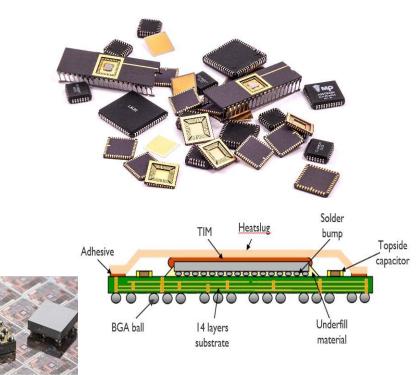

#### TODAY's assembly techniques

- Standard packages are available and used frequently

- Complex circuits and technologies require more advanced assembly techniques.

- Wire bond Ball Grid Array's

- Wafer Level Chip Scale Package (WLCSP)

- Flip Chip Ball Grid Array's with complicated substrate design

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121

# THE FUTURE

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121

## TOMORROW's technology offerings

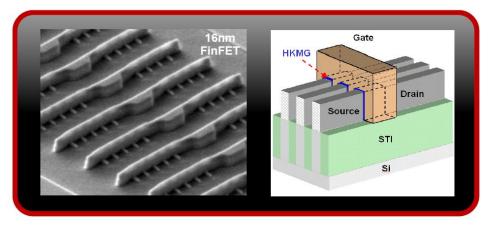

## **TSMC** FinFET Technology

- Better electrical control over channel and more effective leakage suppression

- Driving current enhancement

- Better analog performance from higher intrinsic gain

Security C – TSMC Secret

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121

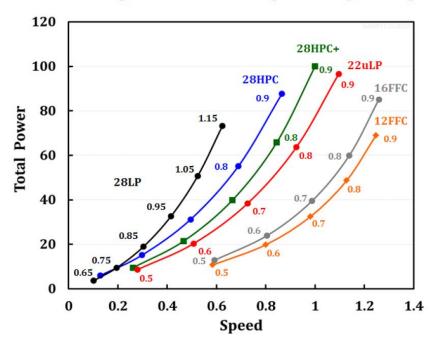

#### TOMORROW's technology offerings

#### Total power vs. Speed (V1.0)

Security C – TSMC Secret

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121

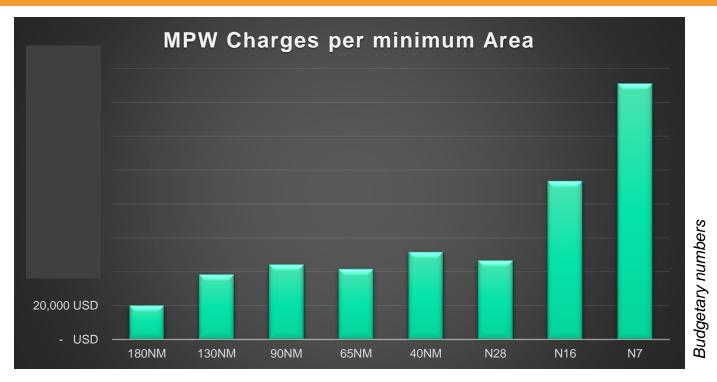

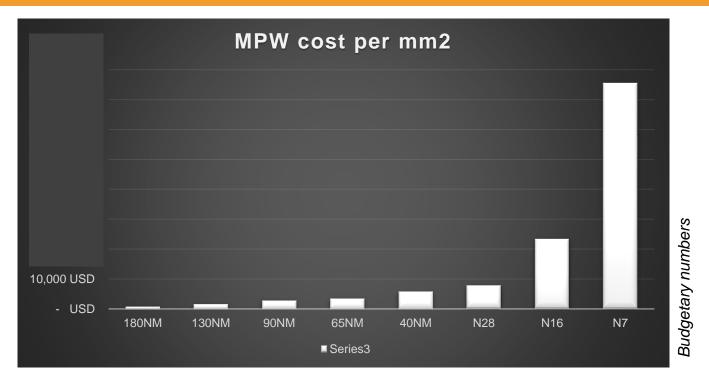

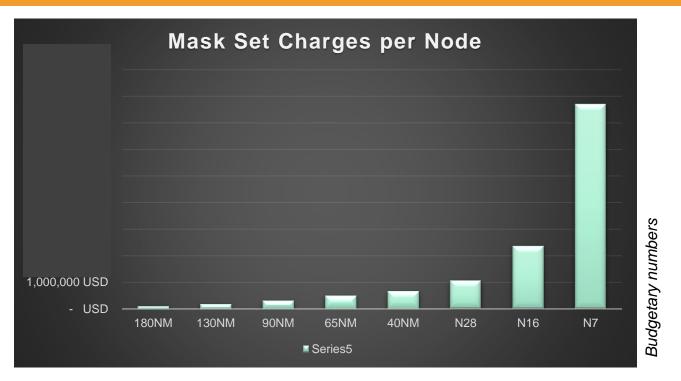

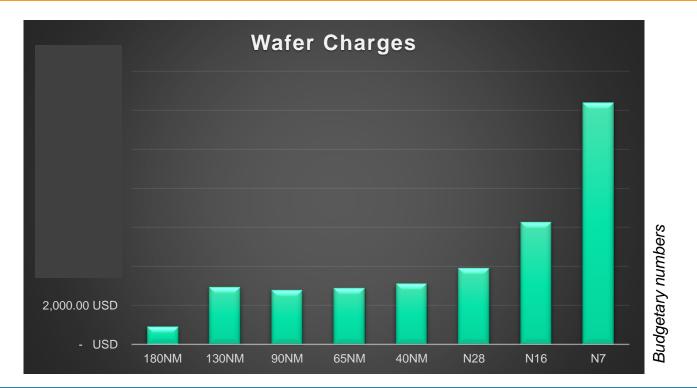

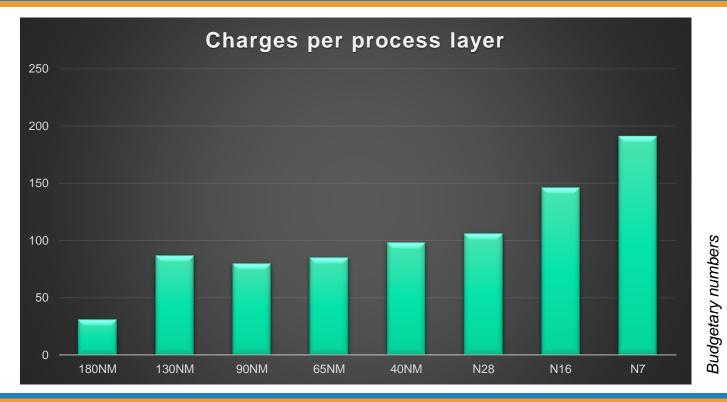

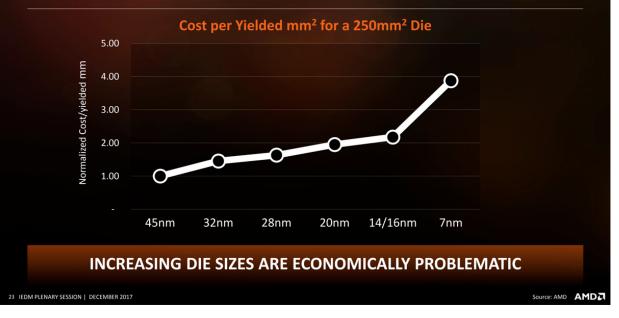

# **THE ECONOMICS**

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121

European Commission

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121

European Commission

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121

# THE NEXT LEVEL

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121

#### MOORE'S LAW SLOWS WHILE COSTS CONTINUE TO INCREASE

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121

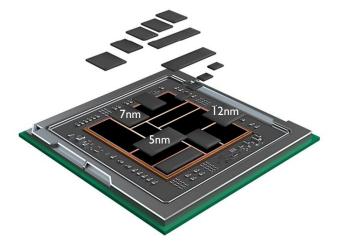

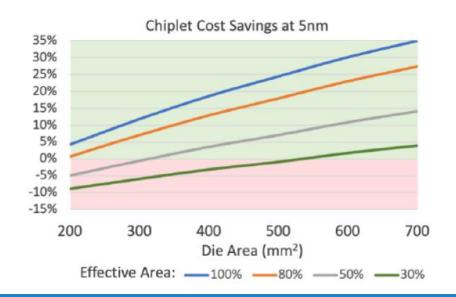

#### MORE than SILICON: CHIPLETS

- Different ASIC, Different TEAM

- Different Semiconductor and foundries combinable

- □ Cost optimization

- □ Higher Yield (KGD)

- HW Reuse

- Dedicated technology for dedicated functions

- □ System Flexibility

- customized and upgraded easily

- Reliable Test coverage

- □ Shorter Time to Market Modularity

- □ Performance scaling

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121

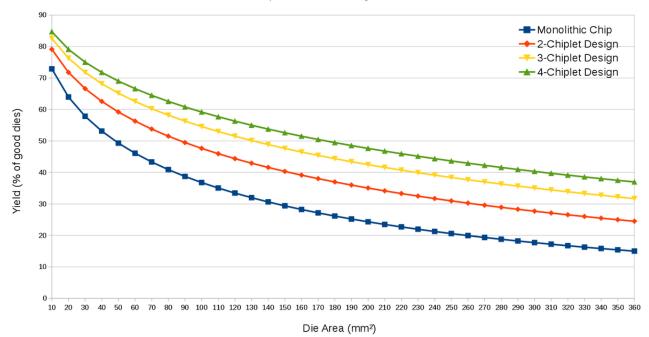

#### MORE than SILICON: CHIPLETS

Chiplet vs. Monolithic Design Yield

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121

#### MORE than SILICON: CHIPLETS

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121

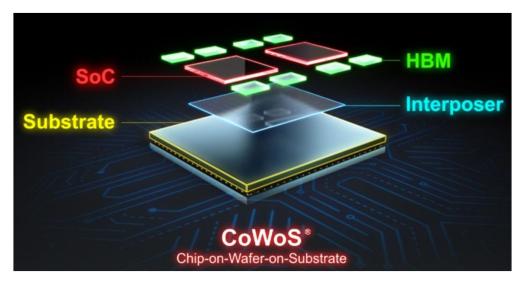

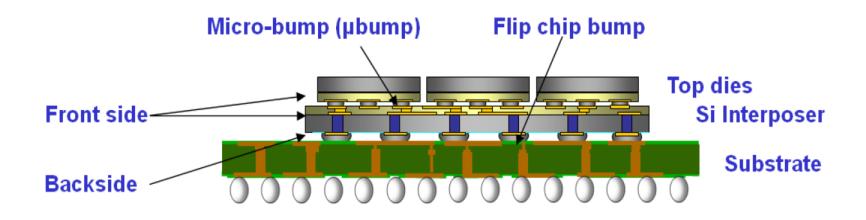

#### MORE than SILICON: COWOS

#### **CoWoS** (Chip on Wafer on Substrate), also known as **TIS** – Through Interposer Stack

- A 2.5D advanced packaging technology offered by TSMC

- Incorporates multiple dice side-by-side bonded using micro-bumps on a silicon interposer

- Uses TSVs on silicon interposer to connect to package substrate using C4 bumps

Front Side Interconnect – interconnect between top dies (e.g. HBM dies) to the silicon interposer using micro-bumps.

Backside Interconnect – interconnect between the silicon interposer (with TSV) to the flipchip bump and to the package substrate

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121

**CoWoS** (Chip on Wafer on Substrate), also known as **TIS** – Through Interposer Stack

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121

# **PHOTONICS**

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121

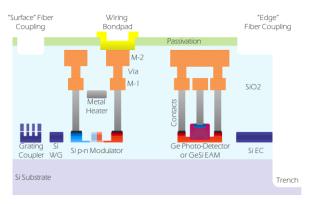

## Imec 200mm Silicon Photonics Platform Evolution

iSiPP50G (2014)

- CMOS full compatible flow (130nm)

- Fully integrated photonics platform

- 1310nm/1550nm wavelength

- Low loss passive waveguide devices

- Low loss fiber coupling structure

- 56Gb/s+ (Ge) Si modulators

56Gb/s+ Ge (Si) photodetectors

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121 iSiPP200 (2020)

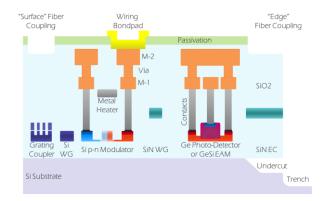

#### iSiPP50G features augmented with:

- Undercut → Improved thermal efficiency and mode confinement

- PECVD SiN WG and edge coupler or SiON edge coupler

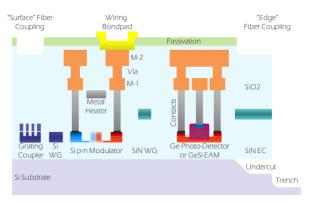

### Imec 200mm Silicon Photonics Platform Evolution

#### iSiPP200 (2020)

iSiPP50G features augmented with:

- Undercut → Improved thermal efficiency and mode confinement

- PECVD SiN WG and edge coupler or SiON edge coupler

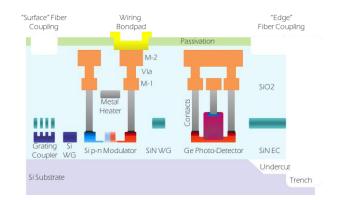

#### iSiPP200N (2023)

#### iSiPP200 features augmented with:

- LPCVD SiN low loss WG

- LPCVD SiN CWDM

- LPCVD edge coupler

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121

#### **MORE ADVANCED TECHNOLOGIES ARE IN REACH**

#### **ASSEMBLY PROCESSES BECOMING** functional part of the component

- Performance, Economics, Form Factor, Security of IP

- **NRE's will become even more dominant for smaller projects**

- **CO-DESIGN** and **VERIFICATION** becoming more important

- New Tool flows

- New Skillsets

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121

# QUESTIONS

Paul Malisse, Business Development, imec Paul.malisse@imec.be

EUROPRACTICE has received funding from the European Unions H2020 Framework Programme for research, technological development and demonstration under grant agreement No 825121

# embracing a better life