# MightyPix

Ivan Peric and MightyPix team

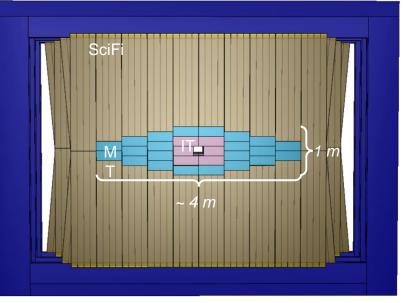

Mighty Tracker

- Mighty Tracker

- SciFi Tracker

KIT

- Scintillating fibres with SiPM readout

- Inner Tracker and Middle Tracker

- Silicon sensors meet requirements of radiation hardness and granularity

- Baseline technology:

HV-CMOS pixel chip MightyPix

- In total over 46000 silicon sensors to cover area of 18 m<sup>2</sup> (minus beam-pipe hole)

Schematic of one layer of the Mighty Tracker. [1]

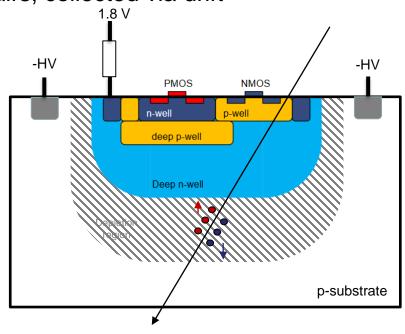

- HV-CMOS sensor

- Sensing element and readout circuit on same chip

- n-well/p-substrate diode acts as sensor

- Readout electronics isolated from high voltage by deep n-well

- High reverse bias creates thick depletion region between deep n-well and p-substrate

- Ionising particles create electron/hole pairs, collected via drift

- MightyPix is based on knowledge from ATLASPix<sup>1</sup> and MuPix<sup>2</sup>

- Final design parameters and requirements:

- First prototype: MightyPix1

| Parameter         | Required Value                                       | Notes                       |

|-------------------|------------------------------------------------------|-----------------------------|

| Chip size         | $\sim$ 2 cm $\times$ 2 cm                            |                             |

| Pixel size        | ~ 50 µm × 150 µm                                     |                             |

| Time resolution   | < 3 ns                                               | Hit assigned to right BX    |

| Power consumption | $< 0.15  W/cm^2$                                     |                             |

| NIEL <sup>3</sup> | $6 \times 10^{14} 1 \text{ MeV } n_{eq}/\text{cm}^2$ | Includes safety factor of 2 |

| Cooling           | < 0°C                                                | Test beam studies           |

<sup>1</sup> HV-CMOS pixel chip for the ATLAS experiment at

CERN

<sup>2</sup> HV-CMOS pixel chip for the Mu3e experiment at PSI <sup>3</sup>Non Ionising Energy Loss

- Implemented in TSI 180 nm process

- Submitted in May 2022

- Chip size: ~ 2 cm × 0.5 cm  $\rightarrow$  full column length, ¼ width

- Pixel matrix: 29 columns, 320 rows

- Pixel:

- 🔹 165 μm × 55 μm

- CMOS amplifier and CMOS comparator

- Data format: 2 × 32 bit words per hit trasmitted

- Data output rate: 1.28 Gbit/s going to lpGBT

The first prototype: MightyPix1

- Digital interfaces:

- Timing and Fast Control (TFC)

- Slow Control (I2C)

- Configuration shift register (SR) interface

- Clock generation:

- External: 40 MHz and 640 MHz coming from lpGBT

- Internal: CML and CMOS PLL with 40 MHz reference clock

- Bias voltages:

- Integrated 10 bit voltage DACs

- Can be supplied externally

The first prototype: MightyPix1

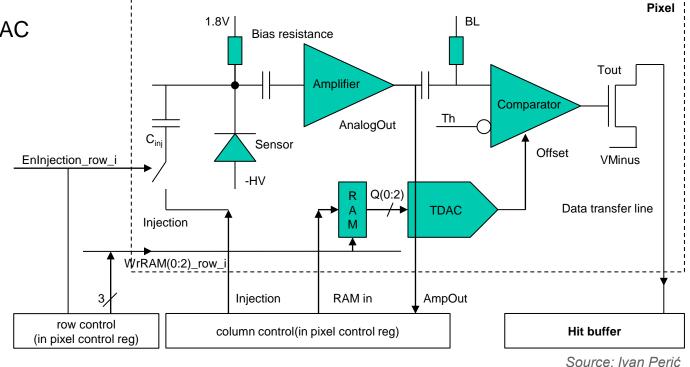

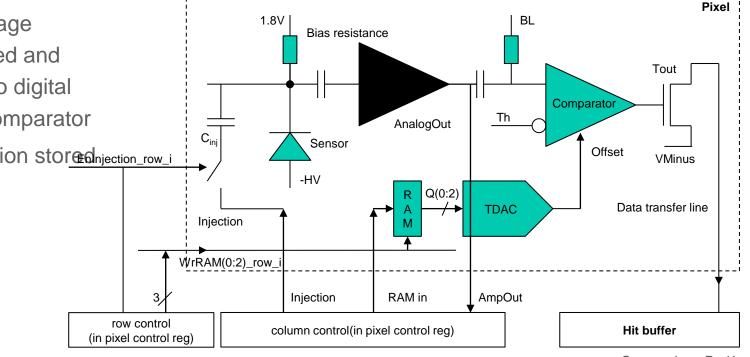

#### **Pixel contains:**

- Sensor diode

- Charge Sensitive Amplifier (CSA)

- Comparator

- Threshold tune DAC

- RAM for tune bits

- 1. Charge collected by pixel n-well

- 2. Converted to voltage signal by Charge Sensitive Amplifier

- Analog voltage pulse shaped and converted to digital signal by comparator

- 4. Hit information stored<sub>njection\_row\_i</sub> in hit buffer

Source: Ivan Perić

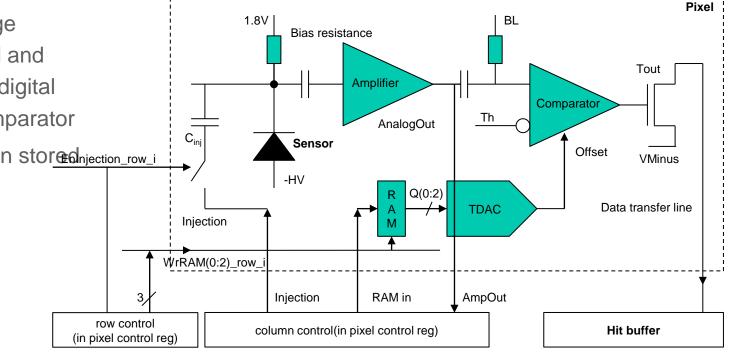

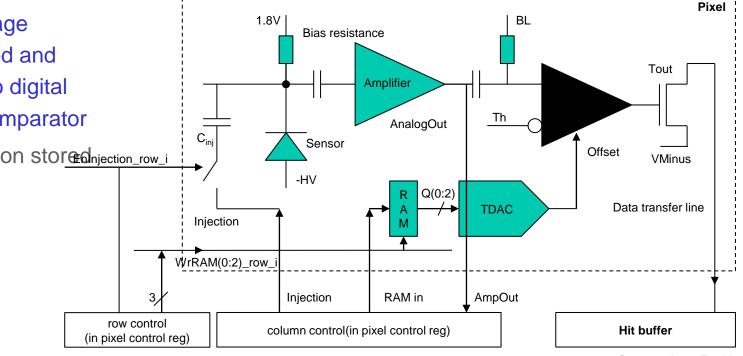

- **1.** Charge collected by pixel n-well

- 2. Converted to voltage signal by **Charge Sensitive Amplifier**

- **3.** Analog voltage pulse shaped and converted to digital signal by comparator

- 4. Hit information stored njection\_row\_i in hit buffer

Source: Ivan Perić

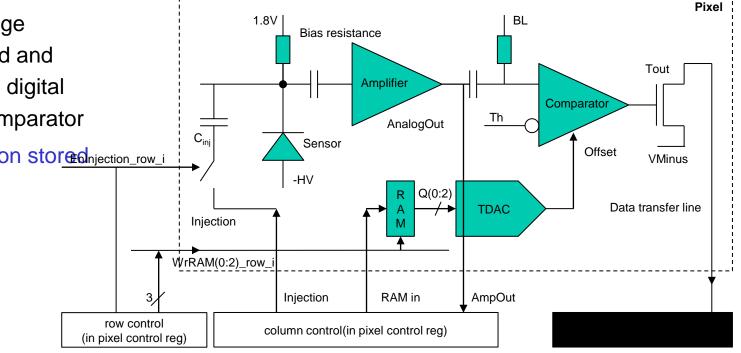

- **1.** Charge collected by pixel n-well

- 2. Converted to voltage signal by Charge Sensitive Amplifier

- **3.** Analog voltage pulse shaped and converted to digital signal by comparator

- 4. Hit information stored njection\_row\_i in hit buffer

Source: Ivan Perić

- **1.** Charge collected by pixel n-well

- 2. Converted to voltage signal by Charge Sensitive Amplifier

- **3.** Analog voltage pulse shaped and converted to digital signal by comparator

- 4. Hit information stored njection\_row\_i in hit buffer

Source: Ivan Perić

• MightyPix1 has been produced – first results soon