# Review of Vertex/Silicon detector Technology

Zhijun Liang

Institute of High Energy Physics, CAS

### **OUTLINE**

- Overview of vertex detector

- CEPC vertex detector R & D

- More Future prospect

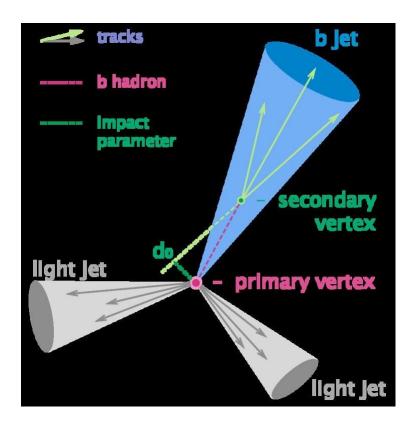

### WHY WE NEED VERTEX DETECTOR?

- High precision vertex detector essential

- Flavor physics

- Higgs physics  $(H\rightarrow bb/cc/gg \text{ and } H\rightarrow \tau\tau)$

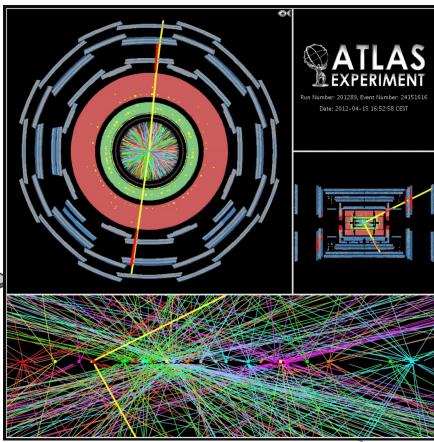

- Pileup vertex rejection for hadron collider

11 Pileup vertex in Z->μμ events at ATLAS

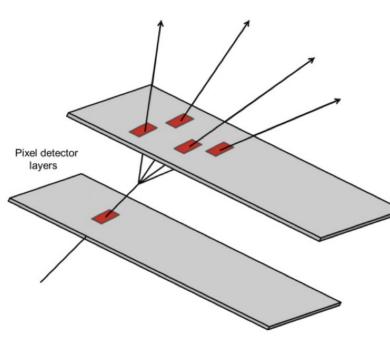

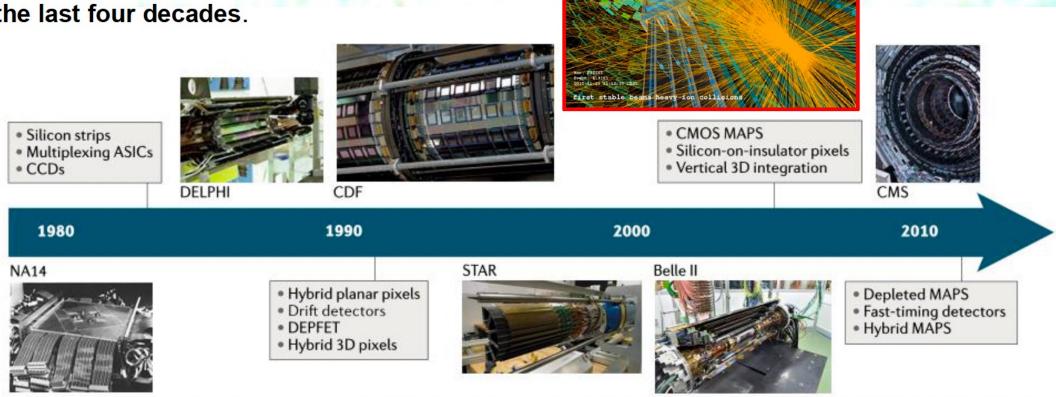

### SILICON DETECTOR DEVELOPMENT

P.Allport, CERN detector seminar, https://indico.cern.ch/event/960851 CERN, Oct.8 2020

Many different silicon detector technologies for particle tracking have been developed over the last four decades.

Applications of silicon strip and pixel-based particle tracking detectors - Nature Reviews Physics - https://doi.org/10.1038/s42254-019-0081-z Allport2019ER

What is remarkable is that <u>every decade</u> the instrumented areas have increased by a factor of 10 while the numbers of channels in the largest arrays have increased by a factor of 100.

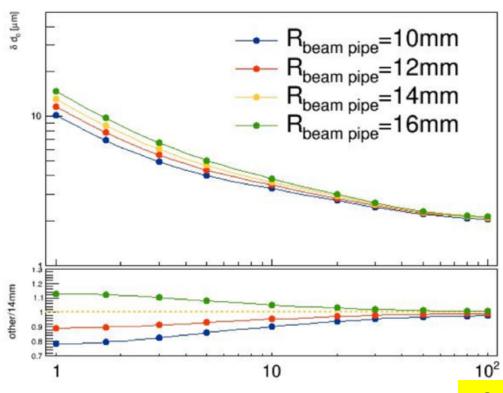

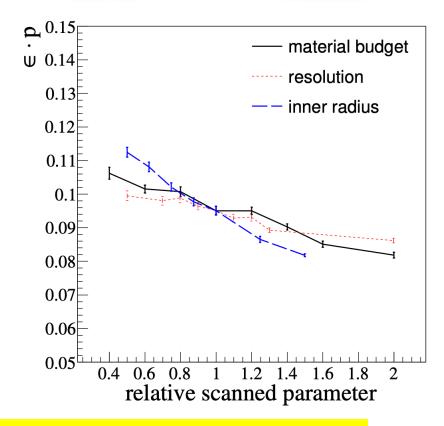

### VERTEX DETECTOR FOR FUTURE COLLIDER: GENERAL WISHLIST

- Wishlist for vertex detector

- Closer to beam pipe (most important!)

- Minimum material

- High resolution pixel sensor

$$\epsilon \cdot p = 0.095(1 - 0.14 \frac{\Delta x_{\text{material}}}{x_{\text{material}}})(1 - 0.09 \frac{\Delta x_{\text{resolution}}}{x_{\text{resolution}}})(1 - 0.23 \frac{\Delta x_{\text{radius}}}{x_{\text{radius}}})$$

ZG Wu, MQ Ruan et al., Study of vertex optimization at the CEPC, 2018 JINST 13 T09002

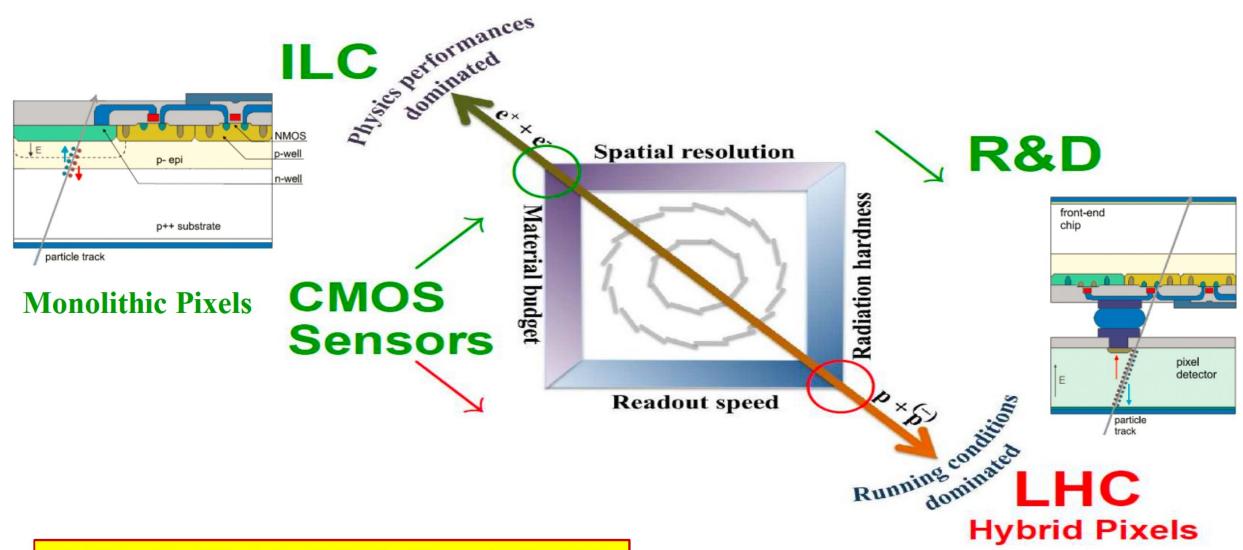

### SILICON DETECTOR DEVELOPMENT

M. Winter, Monolithic Active CMOS Pixel Sensors, iWORID2019

### **VERTEX SENSOR DEVELOPMENT**

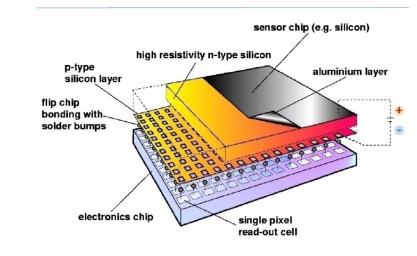

- Hybrid pixel technology (example: ATLAS and CMS, LHCb )

- Sensor and ASIC are designed separately, integrated by bump bonding

- Advantage: Radiation hard, advanced in spin off application (Timepix, ...)

- Drawback: material budget (sensors and ASIC are both about 300um thick)

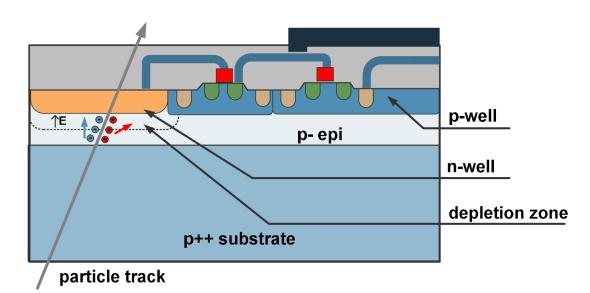

- Monolithic pixel (example: Star, BELLE2, ALICE ITS2, Mu3e....)

- Advantage: low material budget (can be thin down to 50μm)

- Drawback: radiation hardness is not as good compared to hybrid pixel sensor

# Readout Chip Passive Pixel Sensor

## **Monolithic Pixels**

# Hybrid pixel technology

- Radiation sensor

- Current LHC operation showed pixel can work @ 10<sup>15</sup> Neq/cm2 fluence

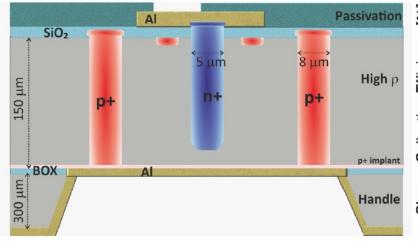

- LHC upgrade (3D pixel sensor)  $\rightarrow$  work up to  $2*10^{16} N_{eq}/cm^2$  fluence

- Future Fcc-hh or Sppc: how to suffer 10<sup>17</sup> N<sub>eq</sub>/cm<sup>2</sup> fluence ?

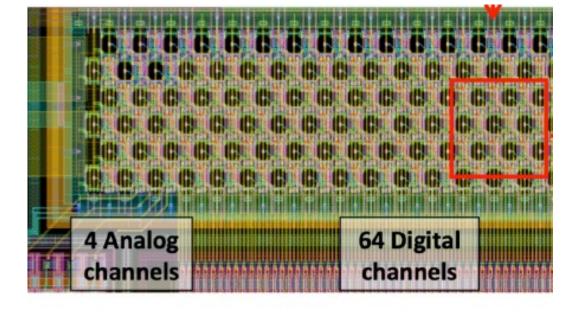

### Fast ASIC

RD53 chip: fast readout chip for HL-LHC ATLAS and CMS vertex detectors

rs 3D pixel sensor performance M. Manna et al., NIMA 979(2020) 164458

Current LHC: CMS silicon tracker

LHC upgrade: 3D pixel sensor

### Monolithic sensors in HEP

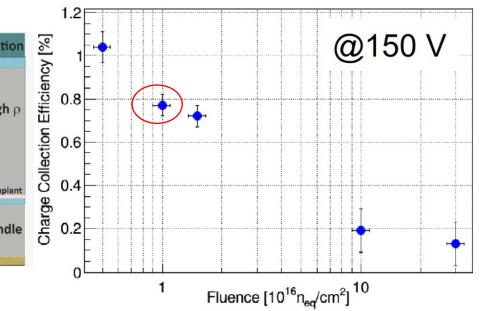

**DEPFET** in Belle

MIMOSA28 (ULTIMATE) in STAR IPHC Strasbourg

First MAPS system in HEP

Twin well 0.35 µm CMOS

- Integration time 190 μs

- No reverse bias -> NIEL few 10<sup>12</sup> 1 MeV n<sub>eq</sub>/cm<sup>2</sup>

- Rolling shutter readout

**ALPIDE** in ALICE

First MAPS in HEP with sparse readout similar to hybrid sensors Quadruple well 0.18  $\mu m$  CMOS

- Integration time <10 μs</li>

- Reverse bias but no full depletion

NIEL ~10<sup>14</sup> 1 MeV n<sub>eq</sub>/cm<sup>2</sup>

DEPLETED MAPS for better time resolution and radiation tolerance Large collection electrode

LF Monopix, MuPix,...

Extreme radiation tolerance and timing uniformity, but large capacitance

Small collection electrode

ARCADIA LF, TJ Malta, TJ

- Sub-ns timing

- NIEL >10<sup>15</sup> 1 MeV n<sub>eq</sub>/cm<sup>2</sup> and beyond

Monopix, Fastpix, CLICTD, ...

W. Snoeys, CEPC workshop 2022

### **OUTLINE**

- Overview of vertex detector

- CEPC vertex detector R & D

- More Future prospect

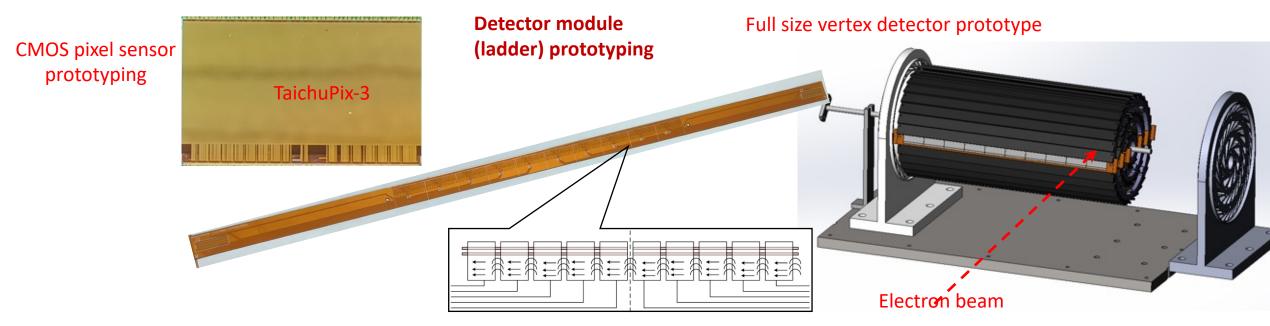

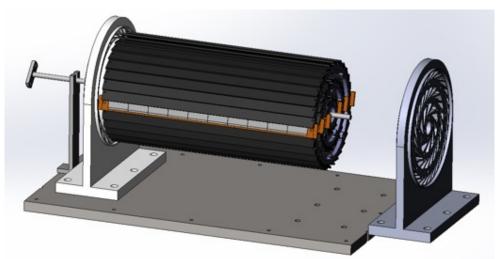

# Overview of CEPC vertex detector prototyping

- Vertex prototype R & D

- ➤ CMOS Pixel Sensor chip R&D

- ➤ Detector module prototyping

- ➤ Detector assembly

Double sided ladder 10 sensors/ladder side, read out from both ends

### **CMOS** MONOLITHIC PIXEL SENSOR

- The existing CMOS monolithic pixel sensors can't fully satisfy the requirement

- Major constraints for the CMOS sensor

- Pixel size: Single point resolution  $< 3 \mu m$

- <500ns deadtime @40MHz clock at Z pole</li>

- Radiation tolerance (per year): 1 MRad &2×10<sup>12</sup> 1 MeV n<sub>eq</sub>/cm<sup>2</sup>

| experiment | Chip                         | Resolution | Readout Speed | TID   |

|------------|------------------------------|------------|---------------|-------|

| ALICE      | ALPIDE                       | <b>√</b>   | X             | X (?) |

| ATLAS      | Malta<br>Monopix<br>ATLASpix | X          |               |       |

| Star       | MIMOSA                       | <b>√</b>   | X             | X (?) |

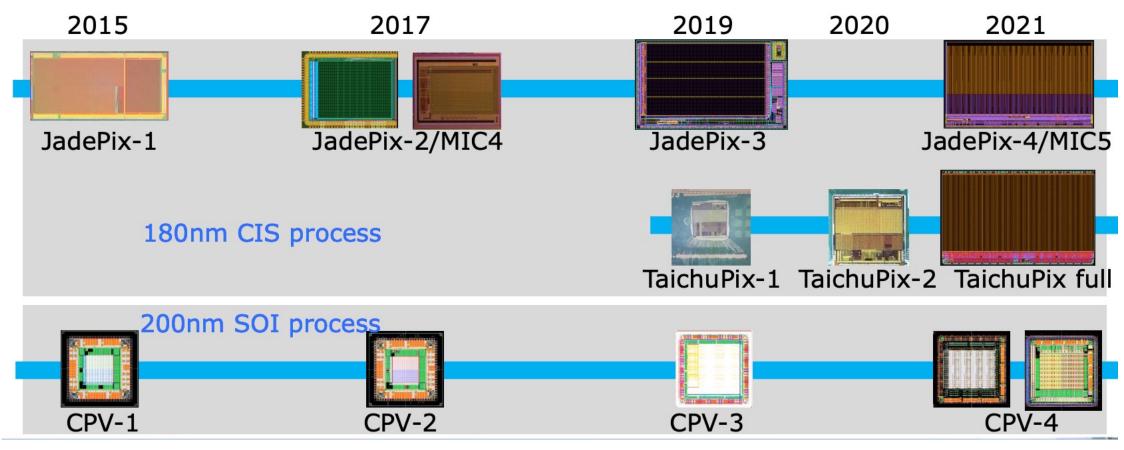

### CEPC VERTEX SENSOR R & D

- CEPC Vertex detector sensor R & D timeline

- Monolithic Pixel sensor design

- Based on Tower Jazz CIS 180nm process (Jadepix, TaichuPix)

- Based SOI 200nm process (CPV chip)

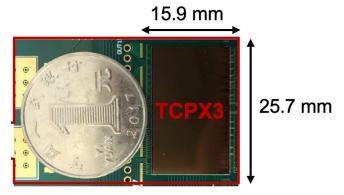

# Large-scale MAPS sensor for CEPC: TaichuPix-3

• 6 TaichuPix-3 wafers (thinned down to 150 μm and diced)

Chip size :  $26 \times 16 \text{ mm}$ Pixel size :  $25 \mu \text{m} \times 25 \mu \text{m}$

Wafer after thinning and dicing

Thickness after thinning

TaichuPix-3 chip vs. coin

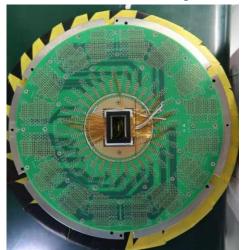

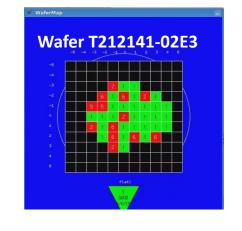

### wafer test on probe-station → 70-80% yield

Probe card for wafer test

An example of wafer test result

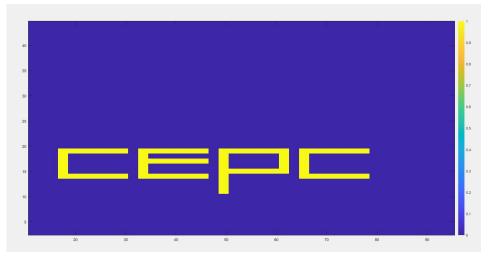

### **Functional tests of the chip**

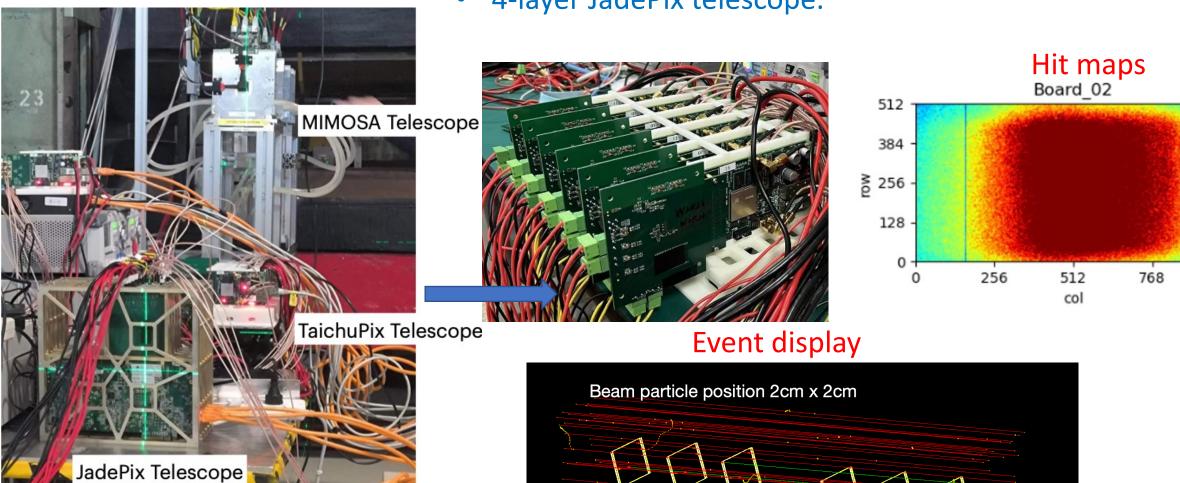

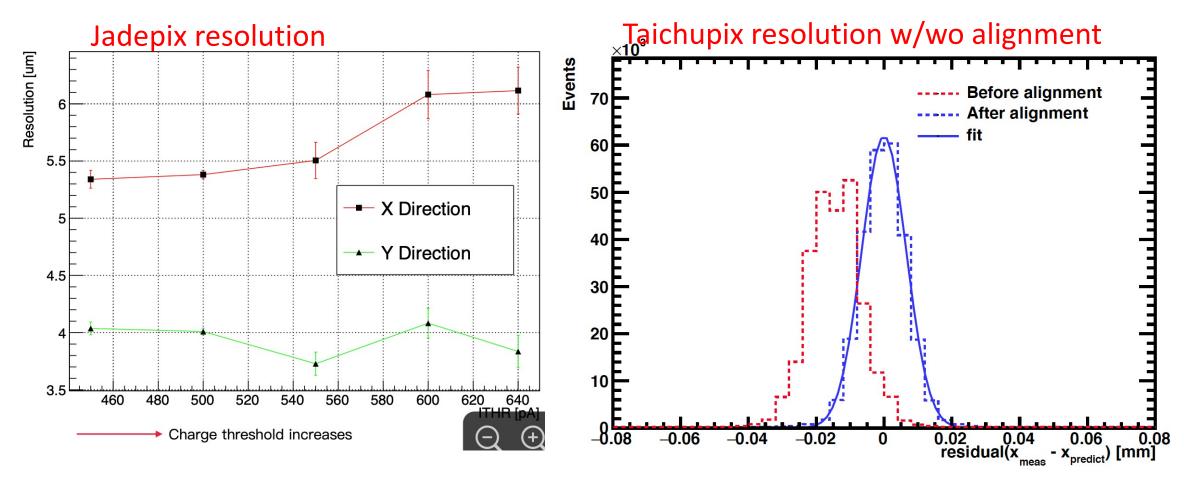

# **CEPC** vertex detector: DESY Testbeam

- The 6-layer of TaichuPix3 telescope

- 4-layer JadePix telescope.

Test Setup @DESY Dec.2022

1024

## **CEPC** vertex detector: DESY Testbeam

- Both CEPC pixel sensor prototype(Taichu and Jadepix) reach 3~5μm resolution

- Efficiency can reach ~ 99%

- ➤ Taichu can work at 20Mhz clock with high efficiency.

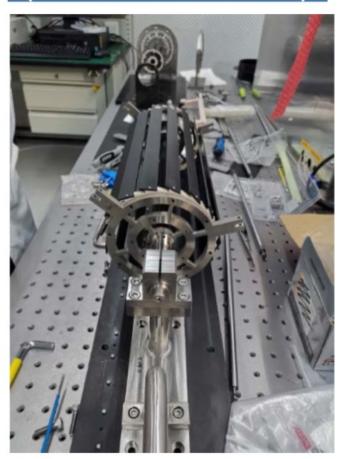

# Vertex detector prototype assembly

• Installation procedure of 3 double layer of vertex detector

Inner barrel

Middle barrel (half number of ladders)

Outer barrel (half number of ladders)

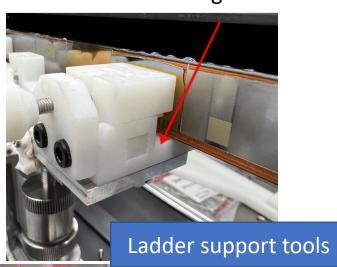

# **CEPC** vertex detector: Ladder loading

- Loading procedure of ladder on vertex detector has been tested

- Another testbeam with full prototype expected in April 2023.

Wire-bonding

### **OUTLINE**

- Overview of vertex detector

- CEPC vertex detector R & D

- More Future prospect

- Alice upgrade

- Timing detector

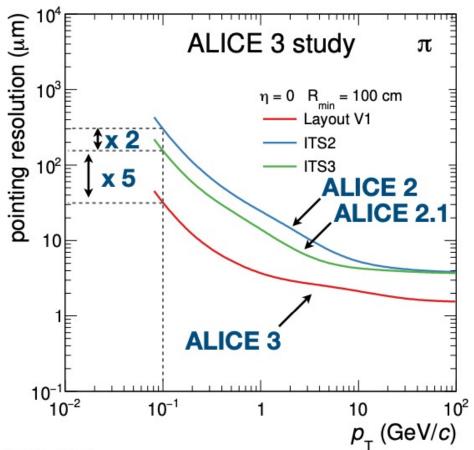

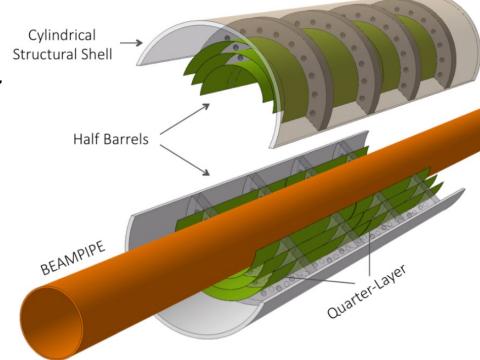

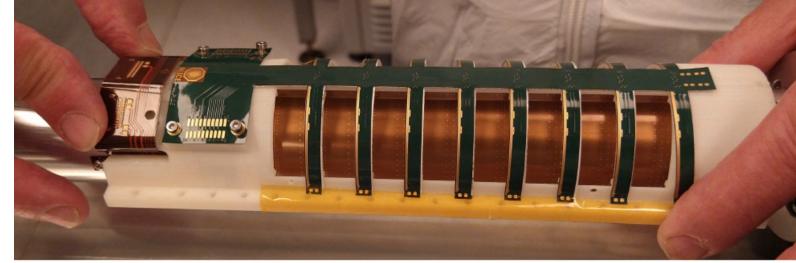

# Alice ITS3 upgrade: MAPS

- Cylindrical inner tracker with curved MAPS wafer

- 5 times better performance expected that ITS2

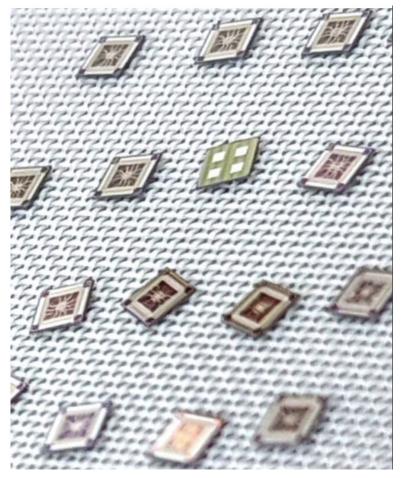

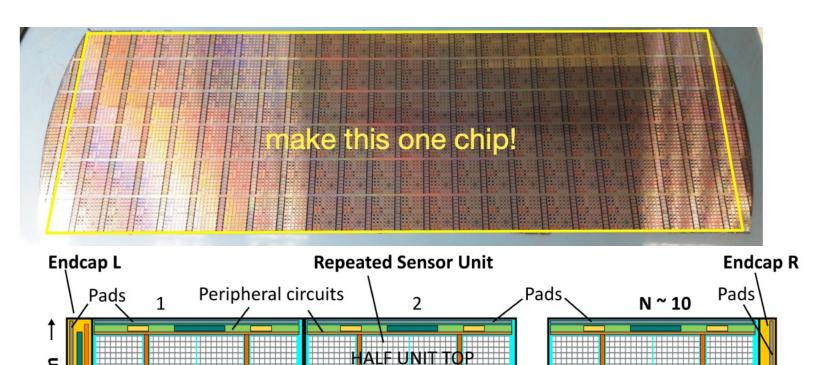

# Alice ITS3 upgrade: 65nm technology & Stitching

- First submission of TPSCo 65 nm CMOS Imaging Technology successful

- next submission by Alice ITS3 community focus on stitching

HALF UNIT BOTTOM

**Pads**

→ Peripheral circuits

2.39 mm

25.5 mm

1.5 mm

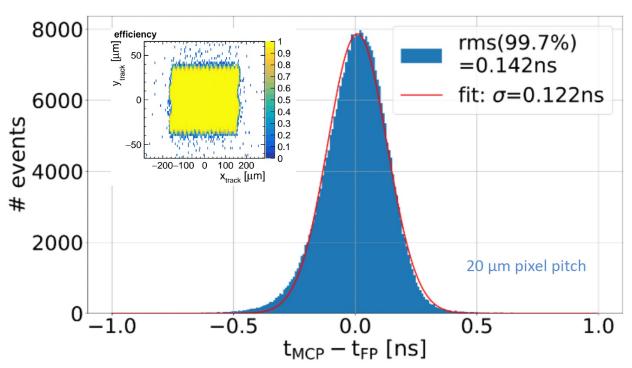

# FastPix development

- Future vertex with 4D precision: space resolution + timing

- 8.6, 10, 15 and 20 µm pixel pitch

- Time resolution better than 150 ps at full efficiency

- Si-Ge fast readout

https://www.mdpi.com/2410-390X/6/1/13

J. Braach, E. Buschmann, D. Dannheim, K. Dort, T. Kugathasan, M. Munker, M. Vicente

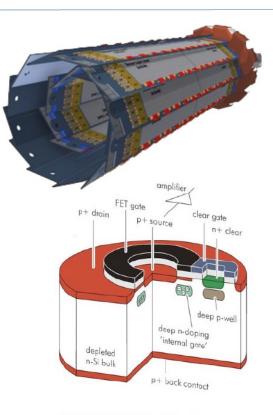

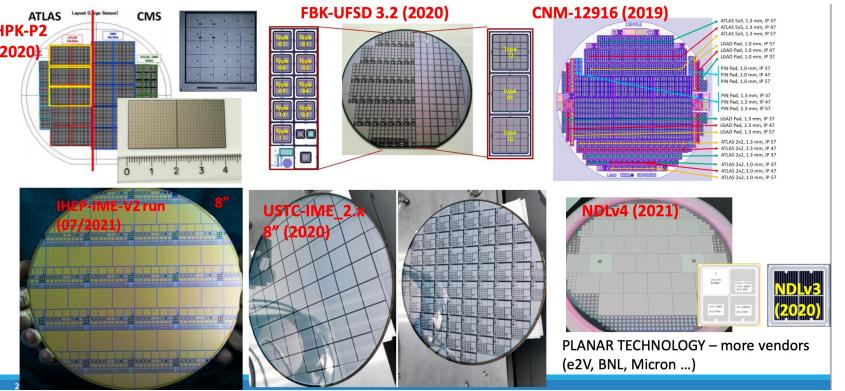

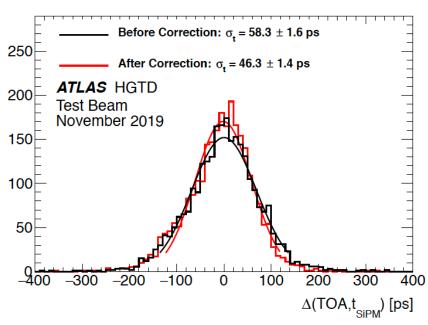

# Silicon timing detector development

- Both ATLAS and CMS is aiming for silicon timing detector

- with Low Gain Avalanche Detectors

- 1.3mm<sup>2</sup> pad, with 30-50 ps resolution for single charge particle

- Mainly for pileup vertex rejection

- Also useful for search long-live particles search

# ATLAS High Granularity Timing Detector: Equipped with LGADs (1.3 x 1.3 mm² pads) targetting > 50 ps resolution (rad-hard only viable solution) | The second of the control of the contro

Two layers

# Silicon timing detector development

- Both ATLAS and CMS is aiming for silicon timing detector

- with Low Gain Avalanche Detectors (LGAD)

- 30-50 ps resolution for single charge particle

- Lots of foundries are doing R & D for LGAD around the world

- LGAD based 4D silicon tracker proposed for future EIC

# Summary

- CMOS Monolithic pixel is very promising for future lepton collider

- CPEC MAPS based vertex prototype is in good progress

- 3 double layer prototype will be built and tested this year

- ALICE ITS3 Cylindrical tracker has excellent potential in future colliders

- Fast time (<150ps time resolution) 4D pixel detector becoming feasible

- LGAD based fast sensor

- MAPS based technology