# The Road Ahead

September 9, 2023 Robert Patti <u>rpatti@NHanced-semi.com</u>

630-561-6813

### How It Started...

1988

2,000 gate equivalent

325MHz FF Toggle Rate

~2M Transistors

1.2um 2 metal CMOS Process

# We Are Going to Build a 0.8um GaAs 3020!

- 0.8um DCFL

- 2V Stacked logic

- FF Toggle Rate >2GHz

It failed...

The Xilinx 4000 Series came out and it run faster even though the FF toggle rate was only ~30% of the GaAs. Why?

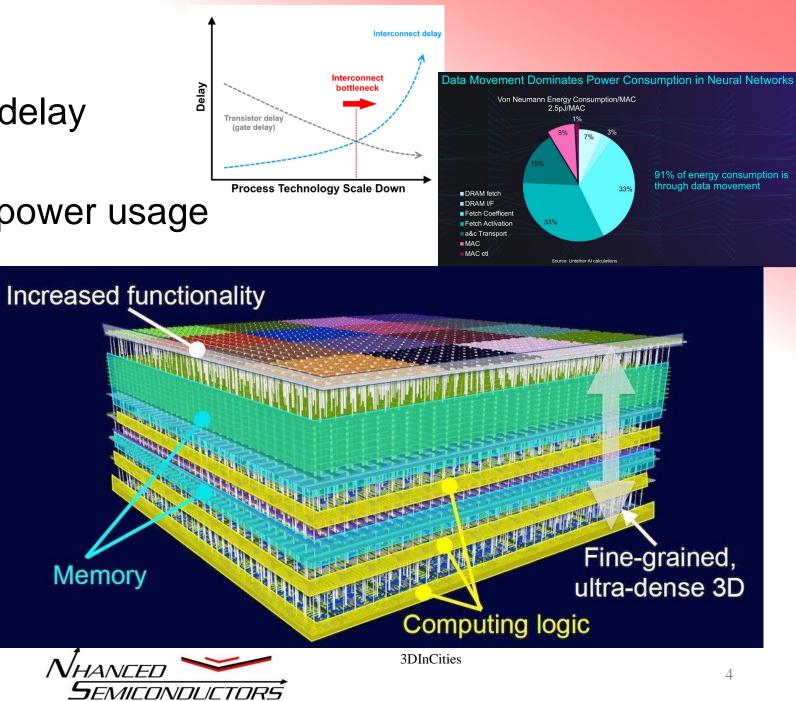

# Its All About The Wire

- Wire length controls the delay

- Span of control

- · Accounts for majority of power usage

- Memory fetch

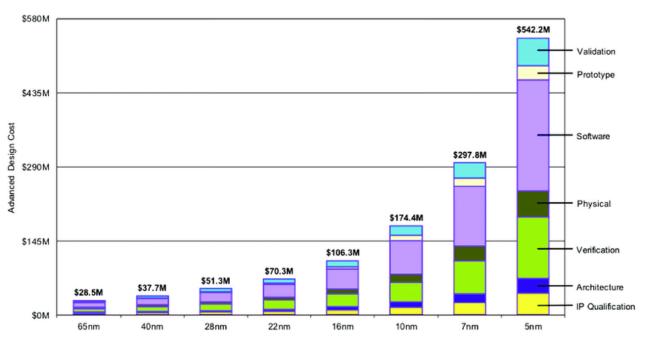

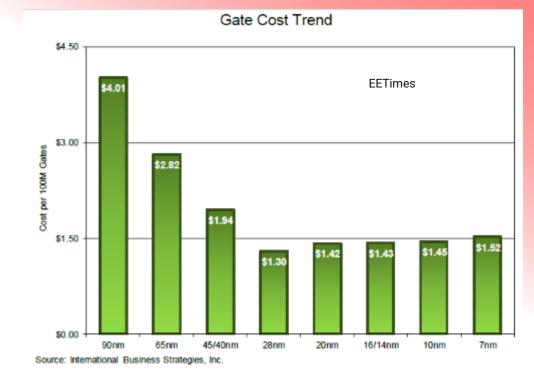

### Moore's Law

Chip Design and Manufacturing Cost under Different Process Nodes: Data Source from IBS

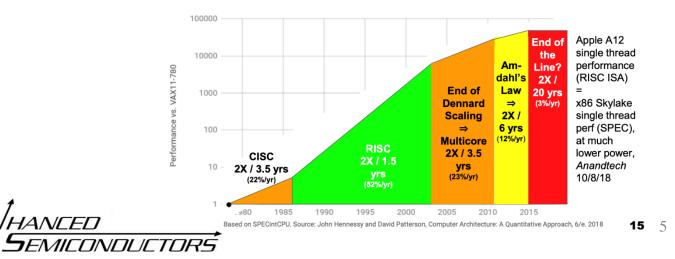

#### End of Growth of Single Program Speed?

#### 40 years of Processor Performance

# Effective End of Moore's Law

Moore's Law was first and foremost a statement about economics. We could shrink transistors and build more of them for about the same cost.

- This has been the basic premise of the semiconductor industry for 50 years and was true up until the last few years.

- Today we can indeed shrink transistors further, but the cost per transistor no longer declines.

- We can get something a little more compact

- Perhaps a little less power

- But we pay more for these features now.

## What Does This Mean?

The semiconductor industry is about to undergo a sea change.

- New ways of accomplishing Moore's law economics and performance are needed.

- The industry is now looking to use advanced packaging to drive future semiconductors.

- Better Cost

- Better Performance

- Better SWaP

# Internet Of Things

## More Than Moore

Semiconductors

# **ADVANCED PACKAGING**

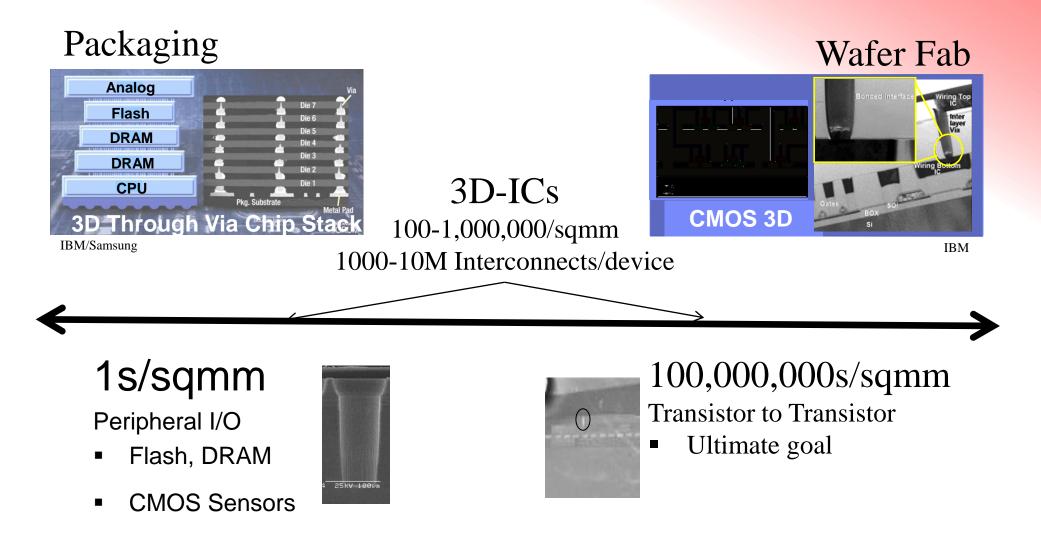

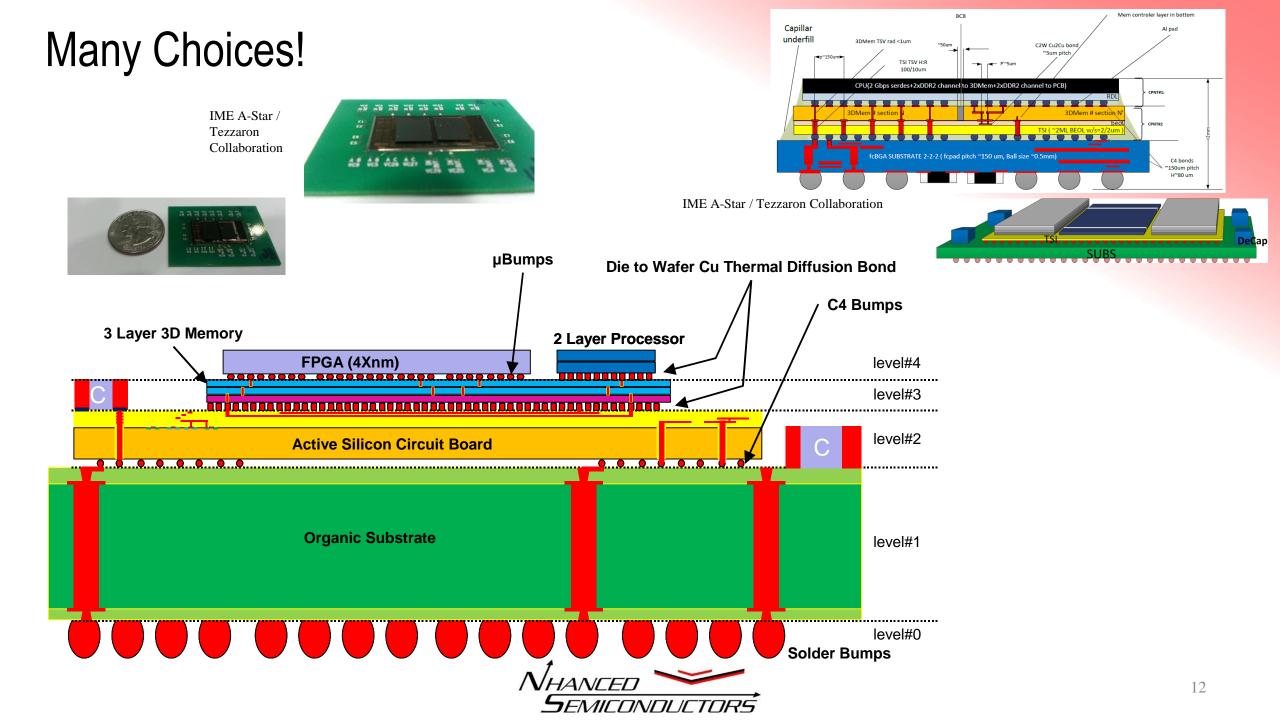

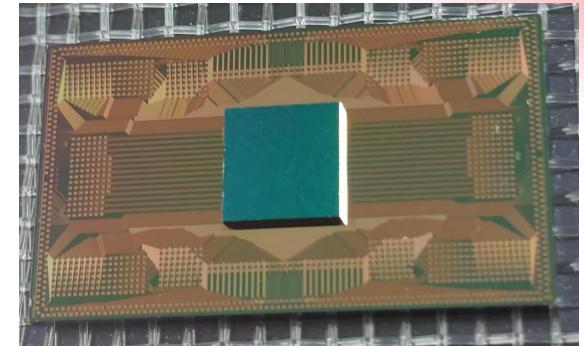

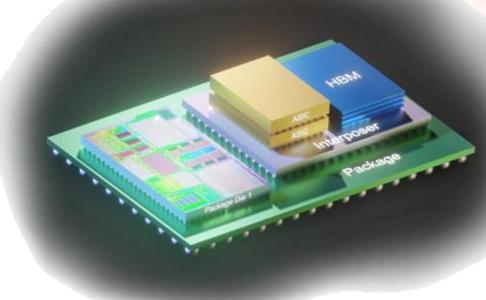

# Span of Advanced Packaging

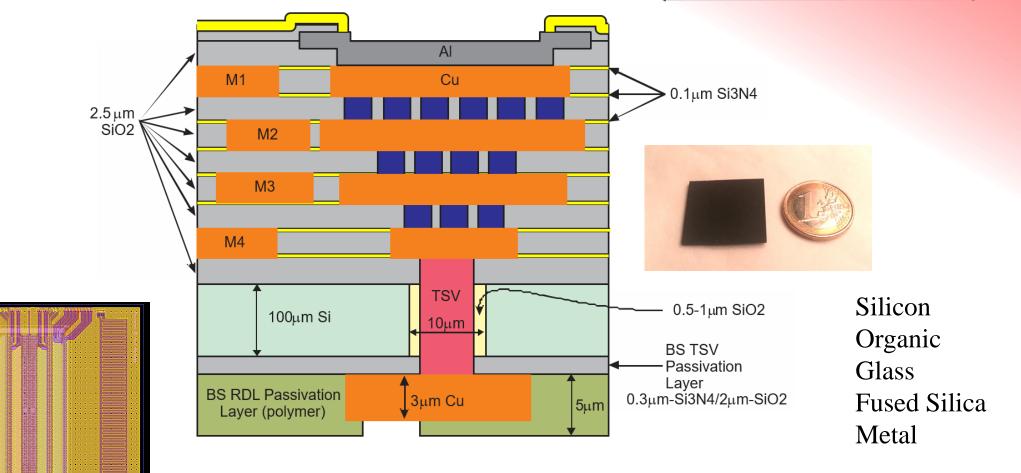

## Interposers

Bigger, Better, Faster >50x50mm, many wiring layers, lower R,L,C

# **Bonding Technologies**

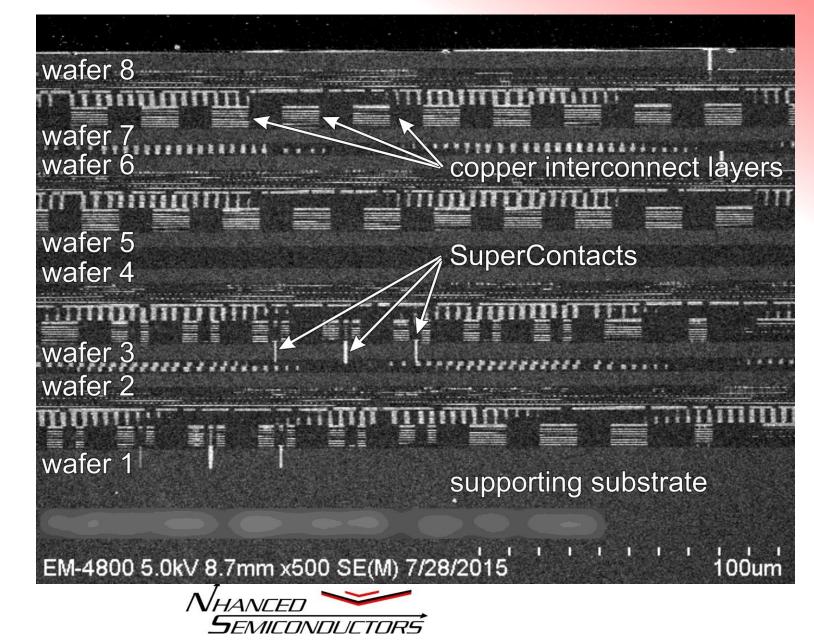

Wafer to Wafer Die to Wafer Die to Die

Silicon GaAs GaSb GaN SiC InP LiNbO3

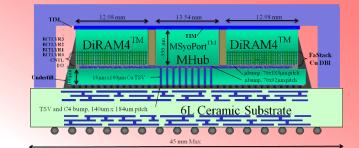

# 5.5D Systems

"I think you should be more explicit here in step two."

# Sensitivities

- Stress

- Planarity

- Thermal

- Memory

- 85-95C

- Logic

- 85-125C

- 3/5 Materials

- SiC @ 400C

- Sensors

- 70-175C

Janus Henderson

• The more unique materials the greater the complexity

# Considerations

- EDA and Multiphysics

- Power distribution

- Cooling

- Technology interactions

- Yield

- Reworkability

- Supply chain resilience

- Environmental

- Test

- Pros / Cons of assembly methods and materials

MIT Tech Review

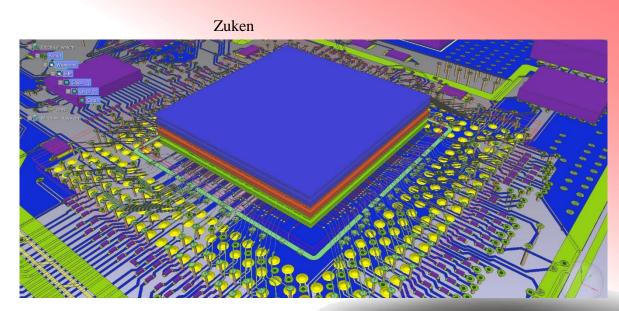

# Co-Design and Multi-Physics

- Multi-Dimensional Tools

- Scale

- Nanometers to centimeters

- Electrical

- Power

- Signal Integrity

- Heat

- Mechanical

- CTE

- Modulus

- Cost

- Photonics

- MEMS

- Liquids

Semiconductor Engineering Oct, 2022

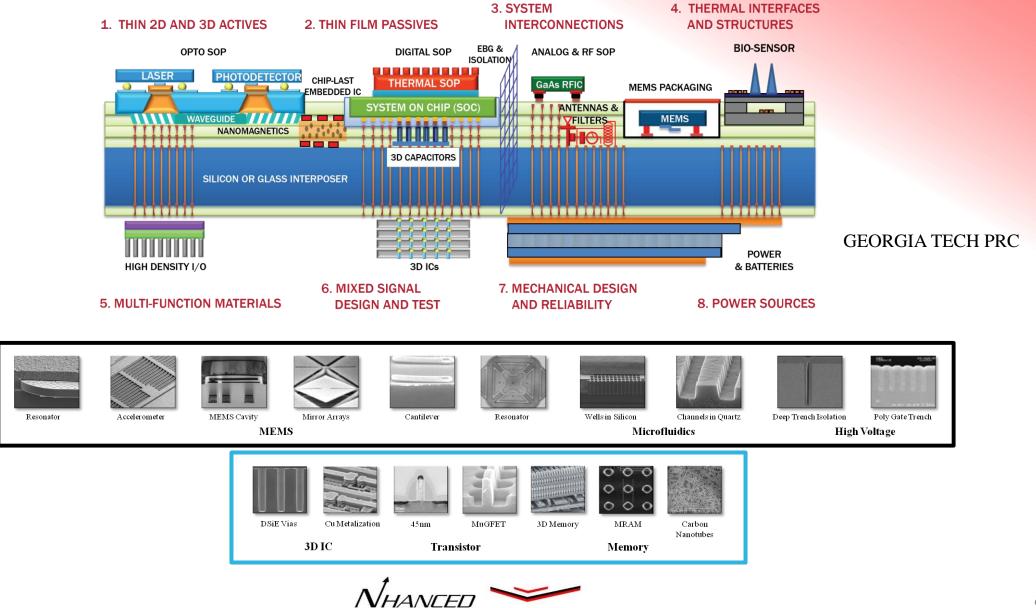

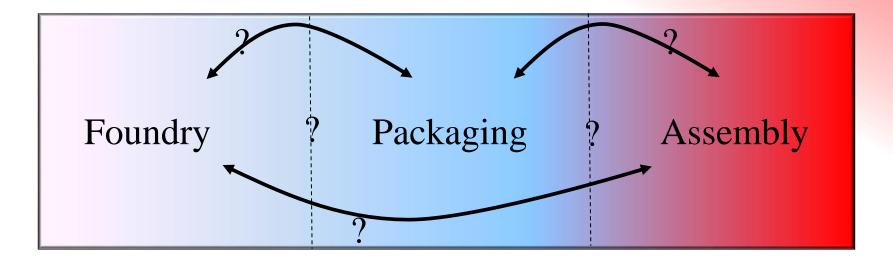

#### Mixing Fab, Packaging and Assembly

SEMICONDUCTORS

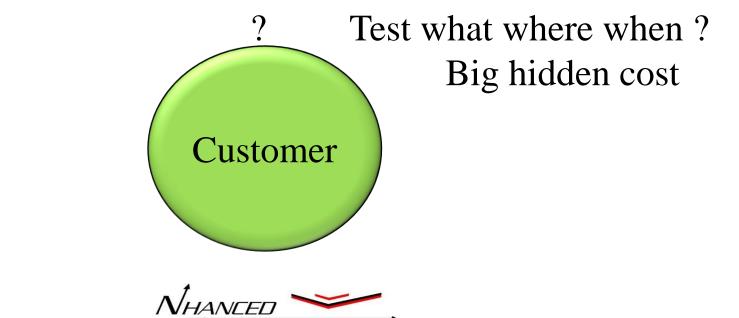

# Testing

- Significant planning required

- Careful analysis of yield cost

- New methodologies

- High I/O count requires self-test

- Deep embedding requires more effort for visibility

- At speed test alternatives

- Embedding memory has numerous test issues

- Standard test interface required.

- Self-repair / Self-redundancy

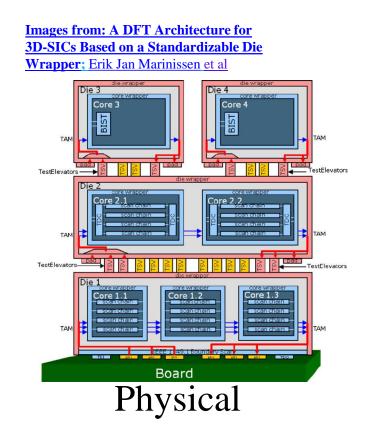

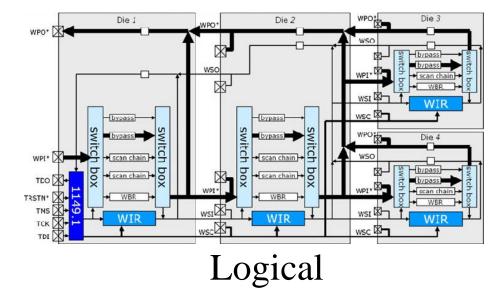

#### One Slide:

Use Standardized DFT + 2.5/3D PCM methods to test Quality and derive Reliability Use repair and redundancy to create KGD and obtain yield.

IEEE 1500 is well defined 2.5/3D DFT starting point building on 1394 standard. Plan is to add 1149.4 analog features targeting device manufacturing integrity.

Augmented JTAG based on IEEE 1500: Add alignment sensing, 3D interconnect R/C measurement, power, temperature ...

System level test, configuration, repair and validation

Objective is to "prove" specific device quality and improve reliability data.

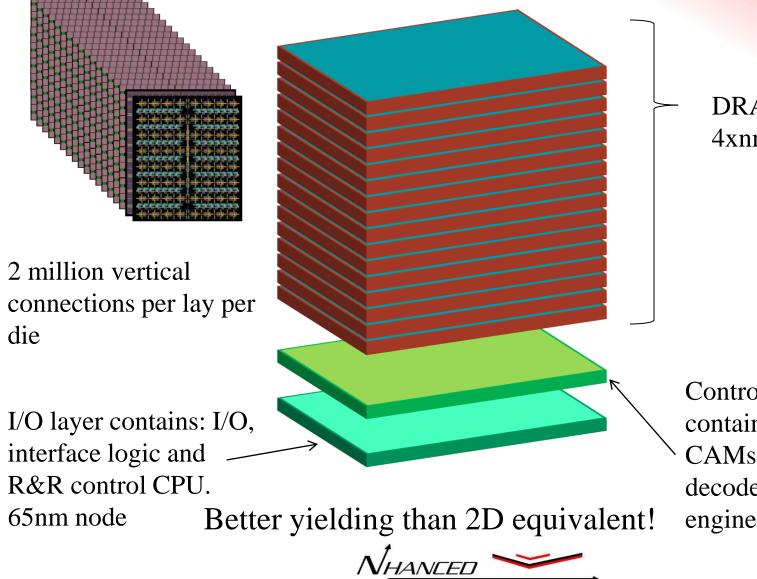

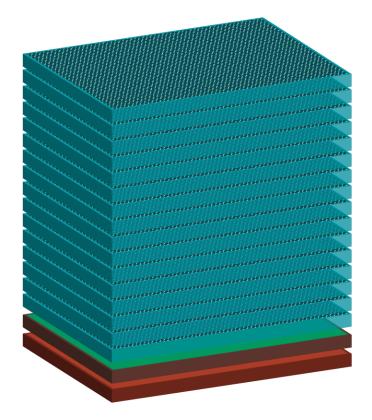

# "Dis-Integrated" 3D Memory

SEMICONDUCTORS

DRAM layers 4xnm node

Controller layer contains: sense amps, CAMs, row/column decodes and test engines. 40nm node

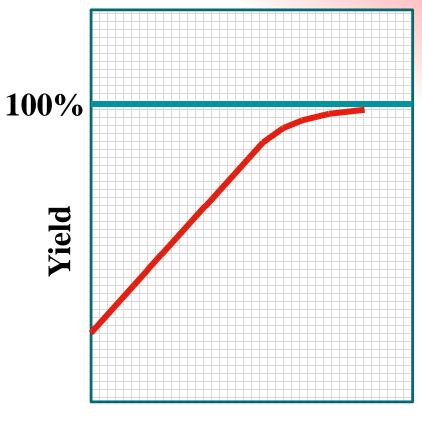

# **Bi-STAR Repair Improves Yield**

#### **Stack Height**

# A Change In Perspective

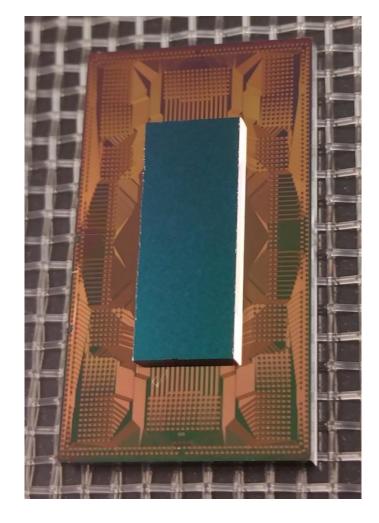

Focused on next generation semiconductors created by

- Advanced Packaging

- Additive Semiconductor Manufacturing

- True heterogenous integration

- Interconnect focused all BEoL additive

- Better ROI

- Lower development costs

- Lower CAPEX

- Leveraging existing foundries

- Split Fab

- More Than Moore Technologies

- IP Centric

- Intrinsic value based not cost of capital

Split Rock Lens – StackExchange