### **Testbeam Analysis**

Patrick Sieberer, on behalf of the RD50 CMOS working group

- This is a continuation to my talk last week: <u>https://indico.cern.ch/event/1220741/contributions/51354</u> <u>00/attachments/2544999/4382676/Testbeam\_Data\_Taki</u> <u>ng\_Analysis.pdf</u>

- Details about setup and the analysis framework can be found here

- What did change?

- Noisy pixels masked using the MaskCreator from Corry

- Less background in plots

- Lot of input from Uwe, Bojan and Bernhard

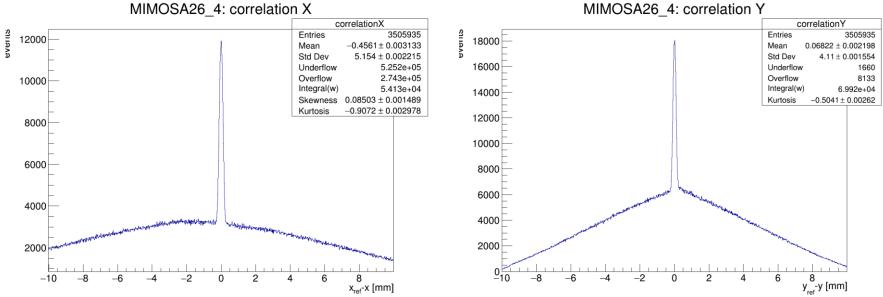

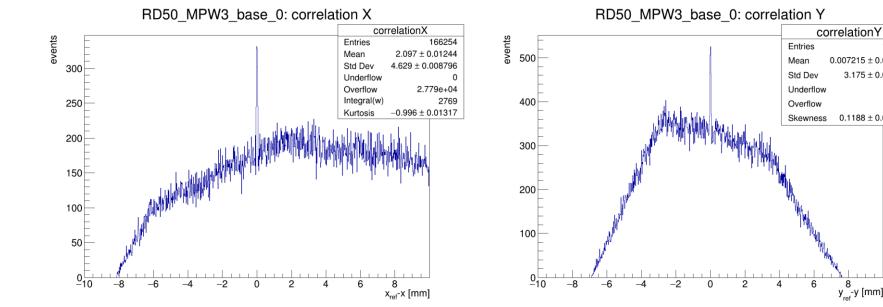

#### Plot taken from Bojan Hiti

MIMOSA26\_4: correlation Y

166254

0

0

$0.007215 \pm 0.007787$

3.175 ± 0.005507

$0.1188 \pm 0.006007$

y<sub>ref</sub>-y [mm]

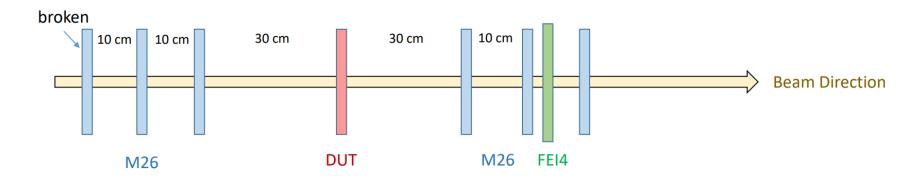

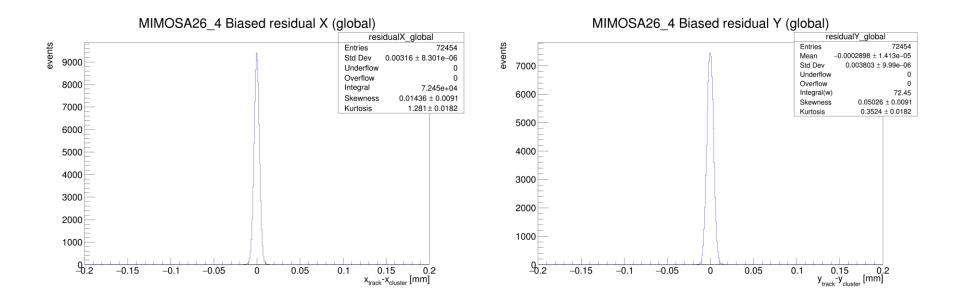

- M26 used as 'golden standard'

- 1. Prealignment (all detectors in parallel)

- 2. Align M26 only (2 steps)

- 3. Align FEI4 (2 steps, alignment of M26 slightly changed as well)

- Requiring hits in all 5 M26 planes

- 4. Align MPW3 (2 steps)

- 5. Analysis

- 2 + 3 can be done in on step -> To be checked

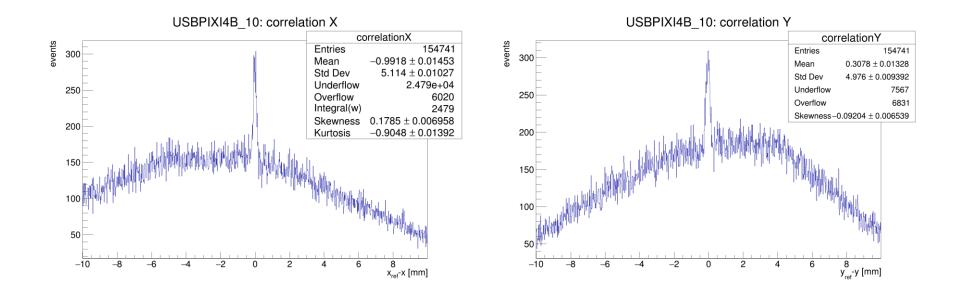

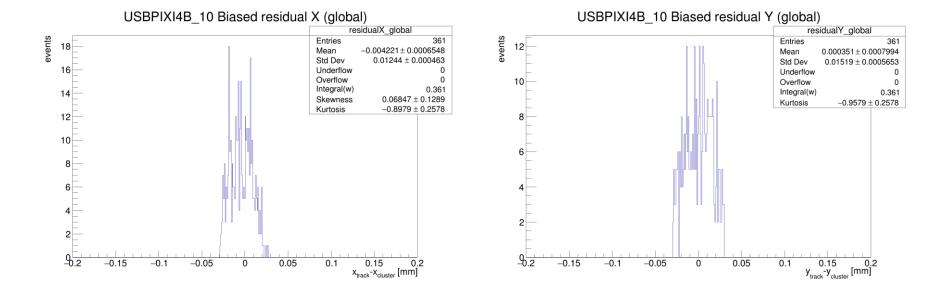

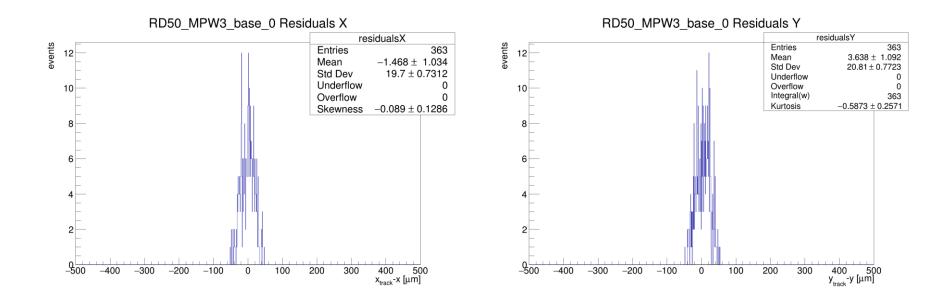

Attention: Different scale on x-axis than in previous plots!

- <u>Without</u> FEI4

3D tracking only

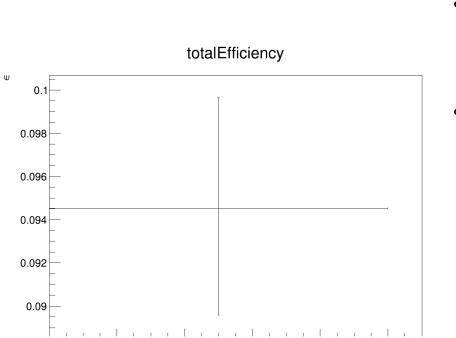

- Efficiency: around 9.45%

- Very high threshold!

- Preprocessing to be checked

- FEI4 can help with checking the preprocessor

- 4D Tracking not yet working...

Take home message: RD50-MPW3 is ready for testbeam, be can integrate the DAQ system, synchronize (somehow ;) ... ) and analyze efficiency.

# WHERE TO GO?

- Shall we design a new Chipboard?

- Shall we test the piggy board?

- Shall we design a new Chipboard?

- Yes, we need more boards anyway

- Ricardo: Modifications easy to implement

- Shall we test produce the piggy board?

- Yes, but we want to check first if modifications needed

- Most likely not

- Only small number -> Only useful for testbeam

- Funding?

Another MPW run is a reasonable option. Current design is not yet ready for engineering run.

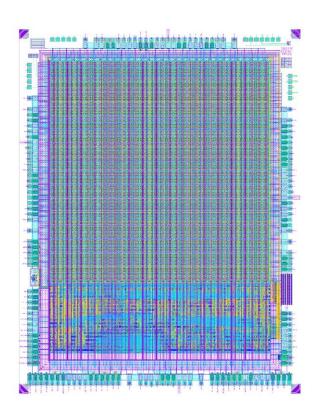

- Fixing current issues of RD50-MPW3:

- Interface between matrix and periphery

- We know the problem and have a solution

- Easy generation of global timestamp

- We know the problem and have a solution

- High noise in lower half of matrix

- We have a hint where the problem is

- Adding more features for the future

- Depends on where we want to go. Telescope? Future detectors (FCC)?

- Thinning, backside processing

- Scaling of the sensor (Does require detailed design study to identify limits)

- Can we already start designing? Who would be in?

- I'm not available for the digital design anymore

- (unless somebody has money for a postdoc ;) )

- Need strategy for transition from RD50 to ECFA DRD scheme from 2024 onwards

Another MPW run is a reasonable option. Current design is not yet ready for engineering run.

- Fixing current issues of RD50-MPW3:

- Interface between matrix and periphery

- We know the problem and have a solution

- Easy generation of global timestamp

- We know the problem and have a solution

- High noise in lower half of matrix

- We have a hint where the problem is

- Adding more features for the future

- Depends on where we want to go. Telescope? Future detectors (FCC)?

- Thinning, backside processing

- Scaling of the sensor (Does require detailed design study to identify limits)

- Can we already start designing? Who would be in?

- I'm not available for the digital design anymore

- (unless somebody has money for a postdoc ;) )

No clear answer, but we should start thinking about this. Design must not stop measurements of MPW3, there is plenty to do!

this

We should also try

**Everybody agreed**

We should absolutely

try this

Need strategy for transition from RD50 to ECFA DRD scheme from 2024 onwards

## RD50-MPW4

- There was a lot of discussion if we (as designers of the chips + systems) should push in one direction or if this should be decided by the collaboration board alone.

- The main outcome was: Let's wait for the collaboration board in Sevilla (which DRD?), but we want show that there are plans for the future of this group:

- For short term (2023) we plan to characterize MPW3 (maybe with backside processing) and can start designing MPW4 (at least fixing issues)

- For long term, there are various options were to go

- Adding more features for the future

- Depends on where we want to go. Telescope? Future detectors (FCC)?

- Thinning, backside processing

- Scaling of the sensor (Does require detailed design study to identify limits)

- Can we already start designing? Who would be in?

- I'm not available for the digital design anymore

- (unless somebody has money for a postdoc ;) )

- Need strategy for transition from RD50 to ECFA DRD scheme from 2024 onwards