# The Monolithic ASIC for the High-Precision Preshower Detector of the FASER Experiment at CERN

Stefano Zambito, on behalf of the FASER Preshower Upgrade team

18<sup>th</sup> Trento Workshop on Advanced Silicon Radiation Detectors *Trento, 2-3-2023*

**Stefano Zambito** | *Université de Genève*

## Outline

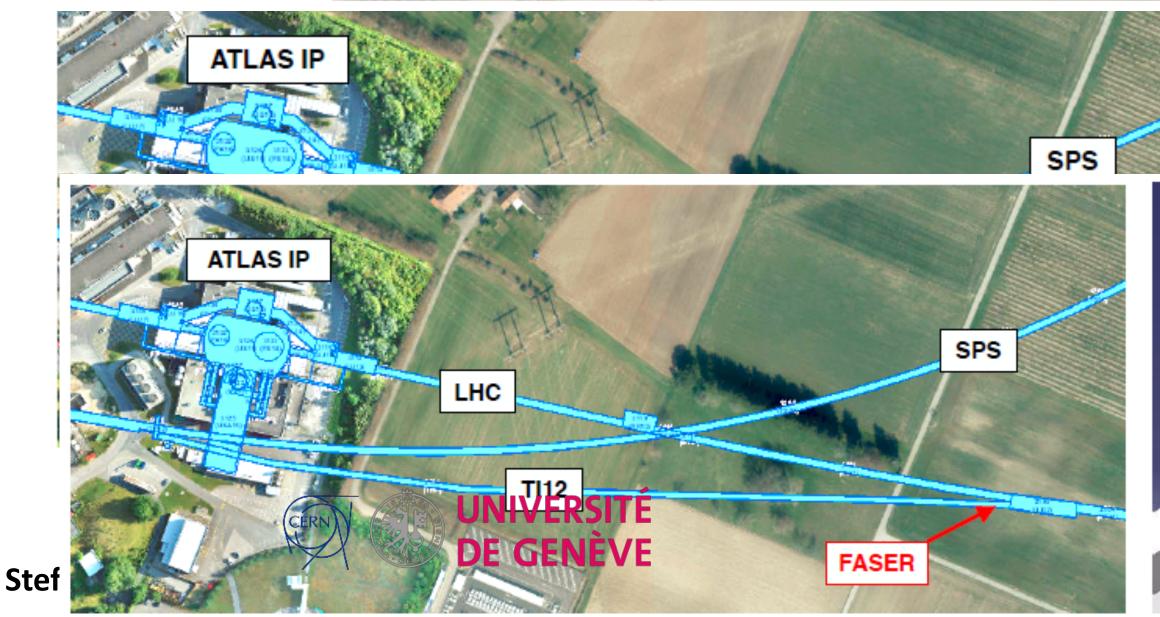

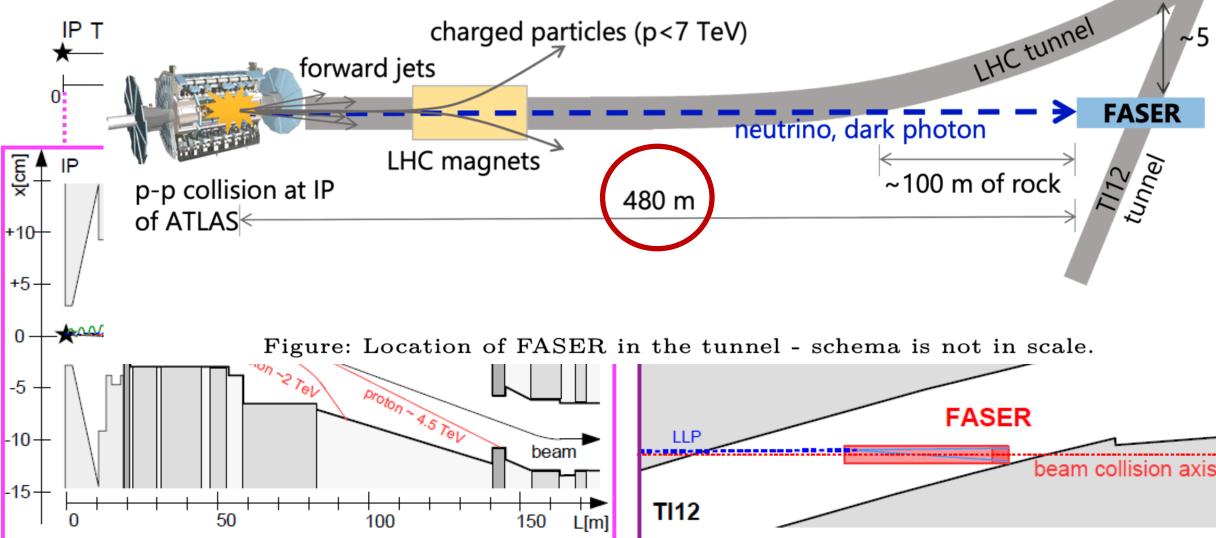

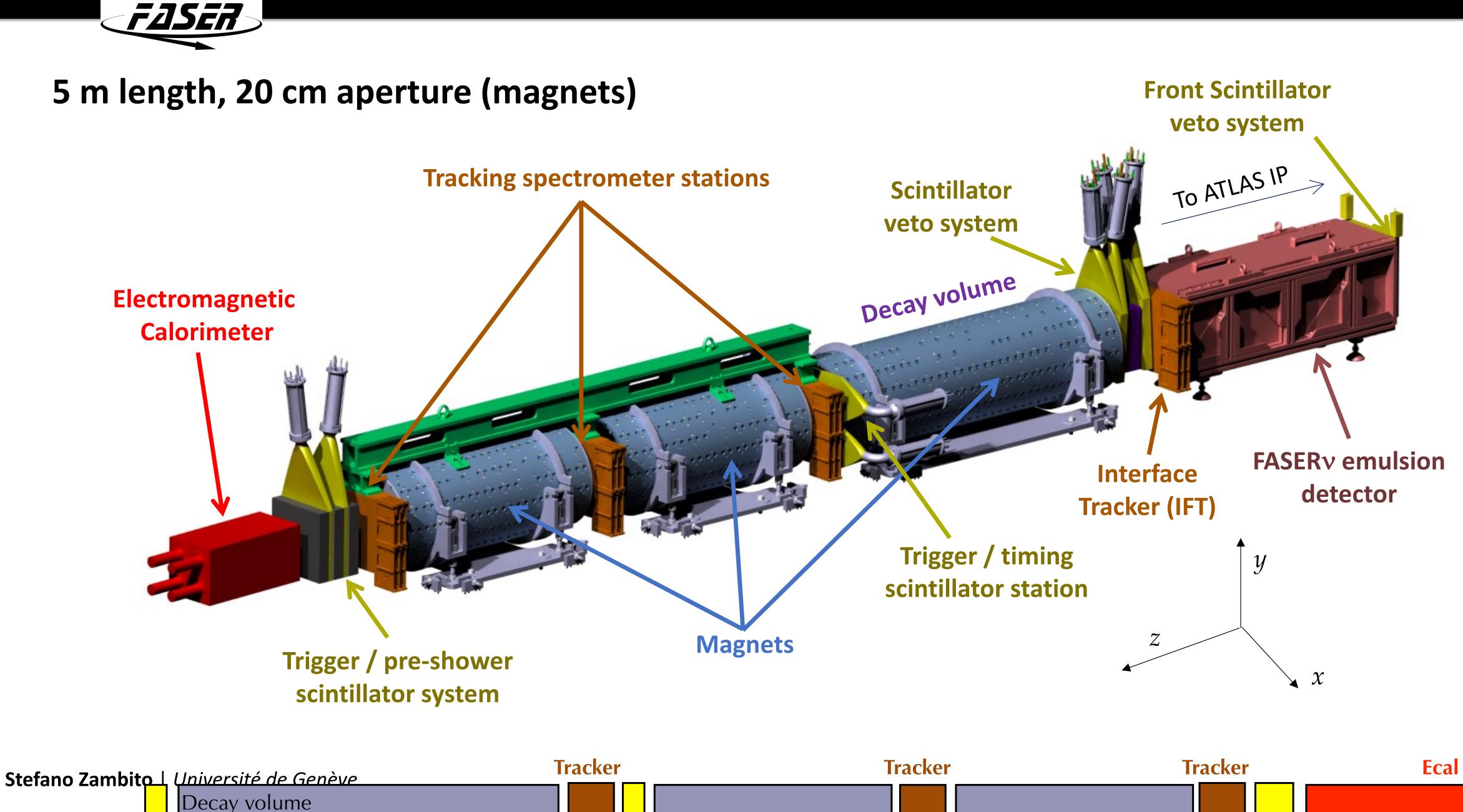

## The FASER Experiment

Zero degrees angle  $\rightarrow$  huge LLPs flux

## 5 m length, 20 cm aperture (magnets)

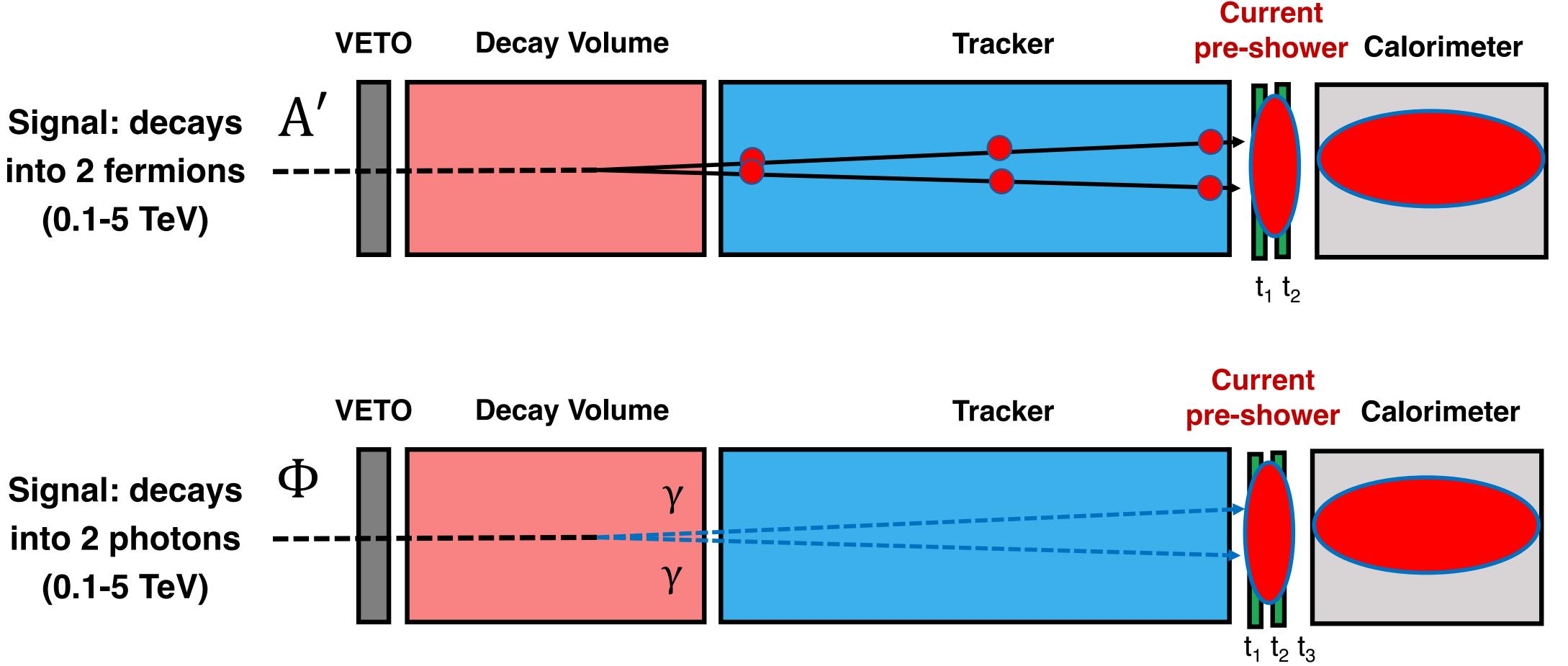

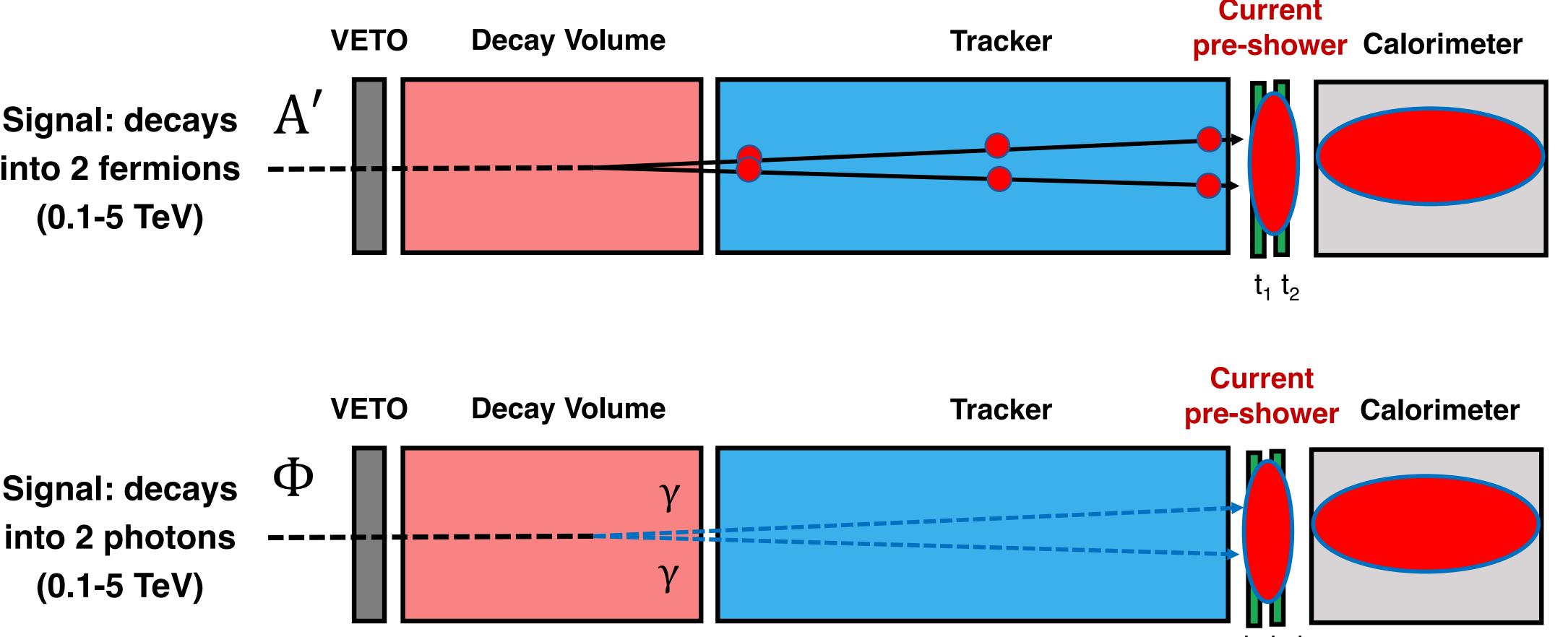

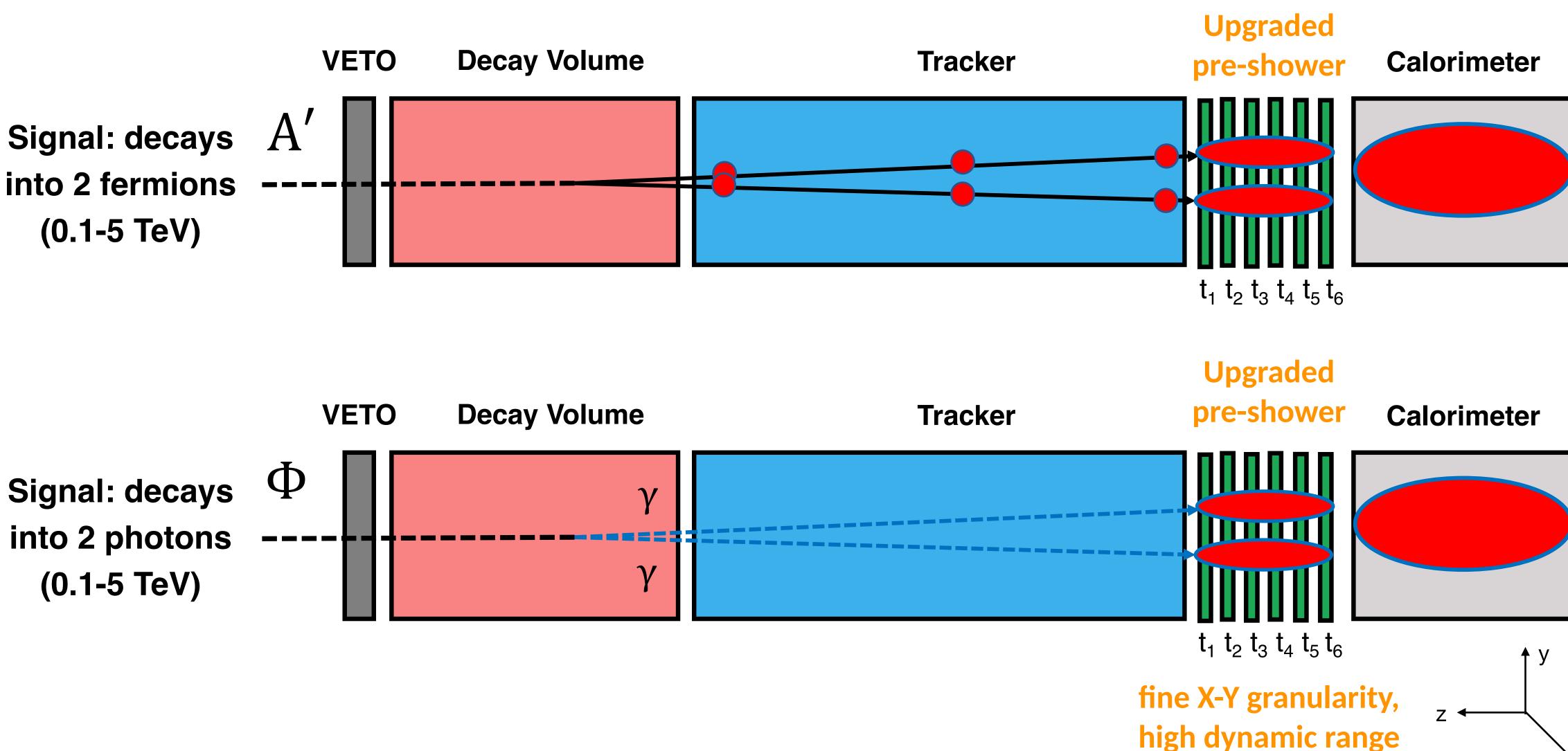

## **Current Detection Capabilities: Two Fermions**

**Stefano Zambito** | *Université de Genève*

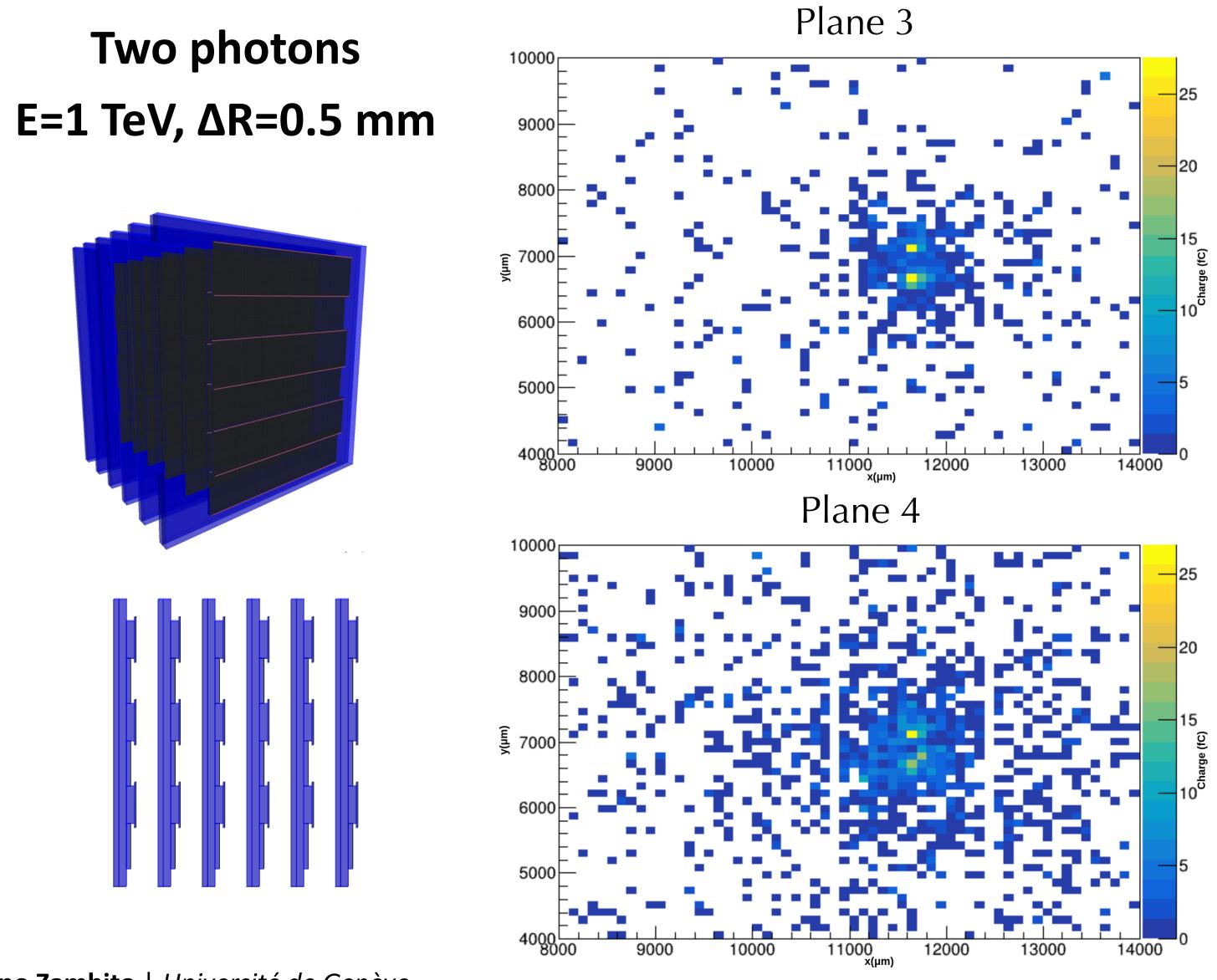

no X-Y granularity: unable to resolve diphoton events!

A \/

## Desired Detection Capabilities: Two Fermions / Photons

# New Preshower Detector []

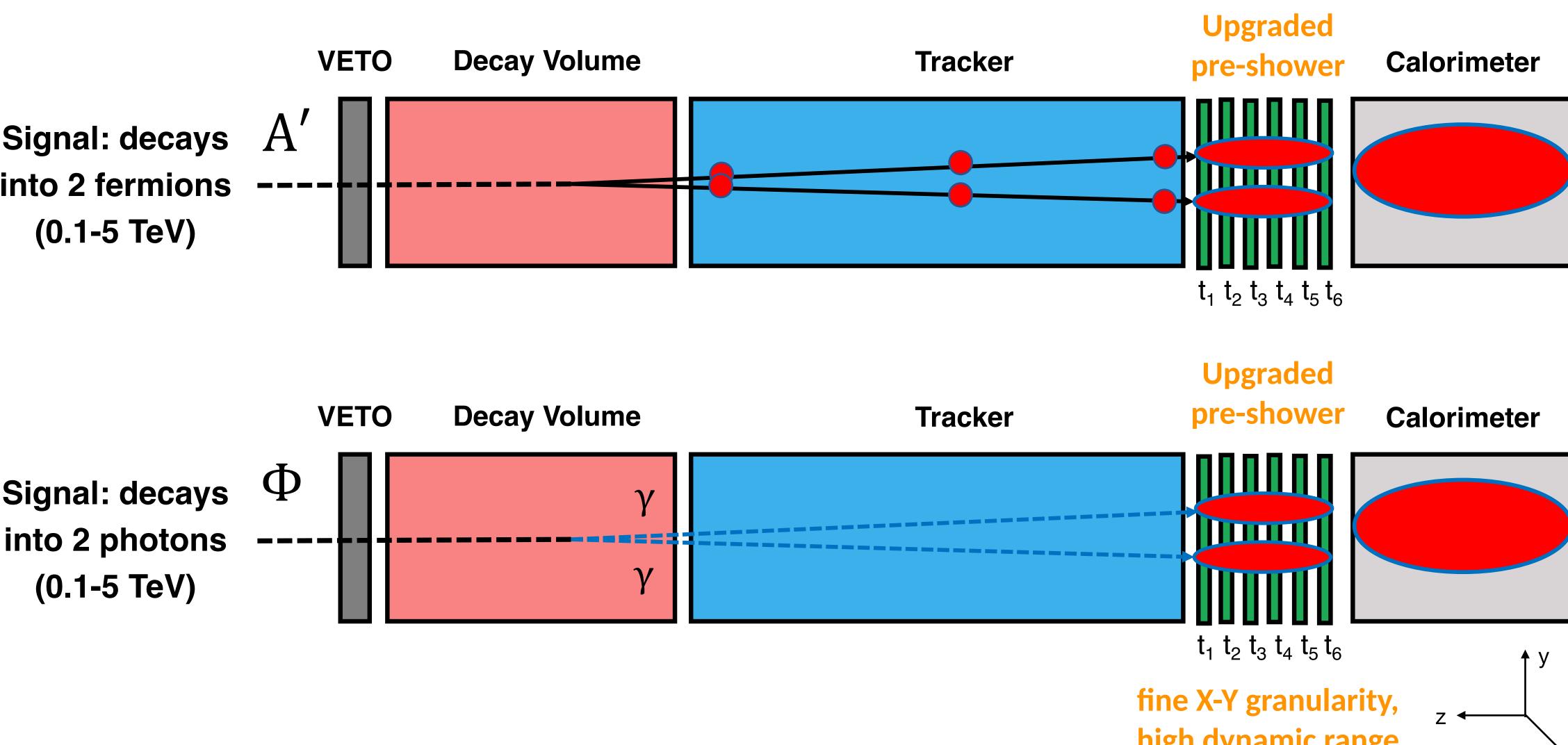

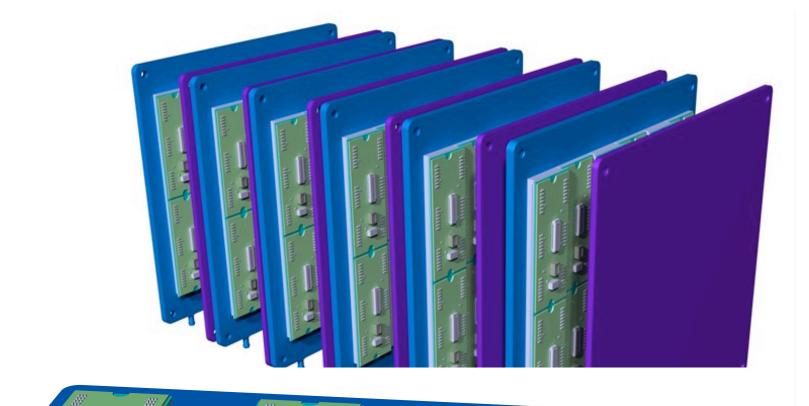

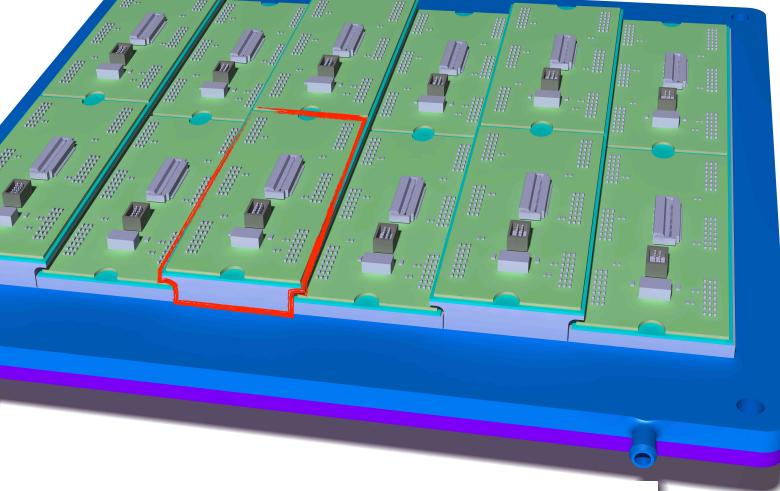

The readout module will consist of an assembly of six ASICs mounted in an array of two by three. Given the expected dimensions of an ASIC the module size will be  $315 \times 67 \text{ mm}^2$ . The gap between Upgraded preshower detector  $(\lesssim 300)$

## 6 detector p $\mapsto$ each plan

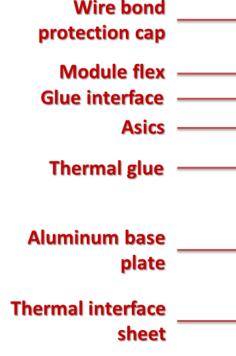

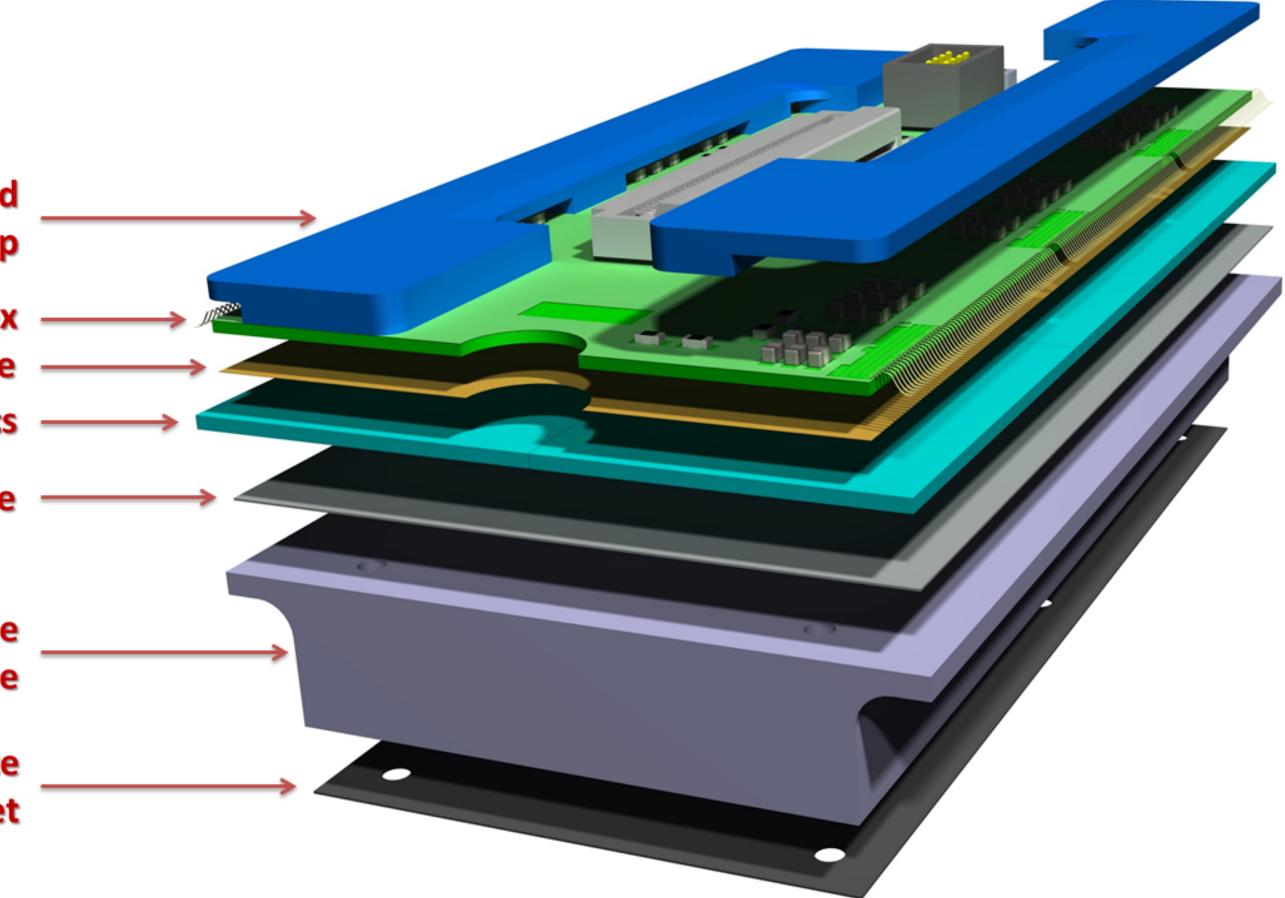

Figure 13: Exploded CAD view of a module assembly. A module is composed by six ASICs glued to an usions and mass. The module consists of fuminum base-plate. The module flex with the electrical interconnection and the SMD components is glued Traon the top of the ASICs. The bottom layer is the thermal interface sheet that

ded when integra

a module to the cooling plate. The size is  $\sim 31 \times 67 \text{ mm}^2$ .

Each module will be supported by a base-plate with thermo-mechanic plate will be made of aluminum wit features (See Figu a reference mounting hole and slot. It be machined six threaded hole a nard anodising for surface insulation receive an electrolytic I breakdown. This procedure was already used to tion of the sense prototy (Figure 14).

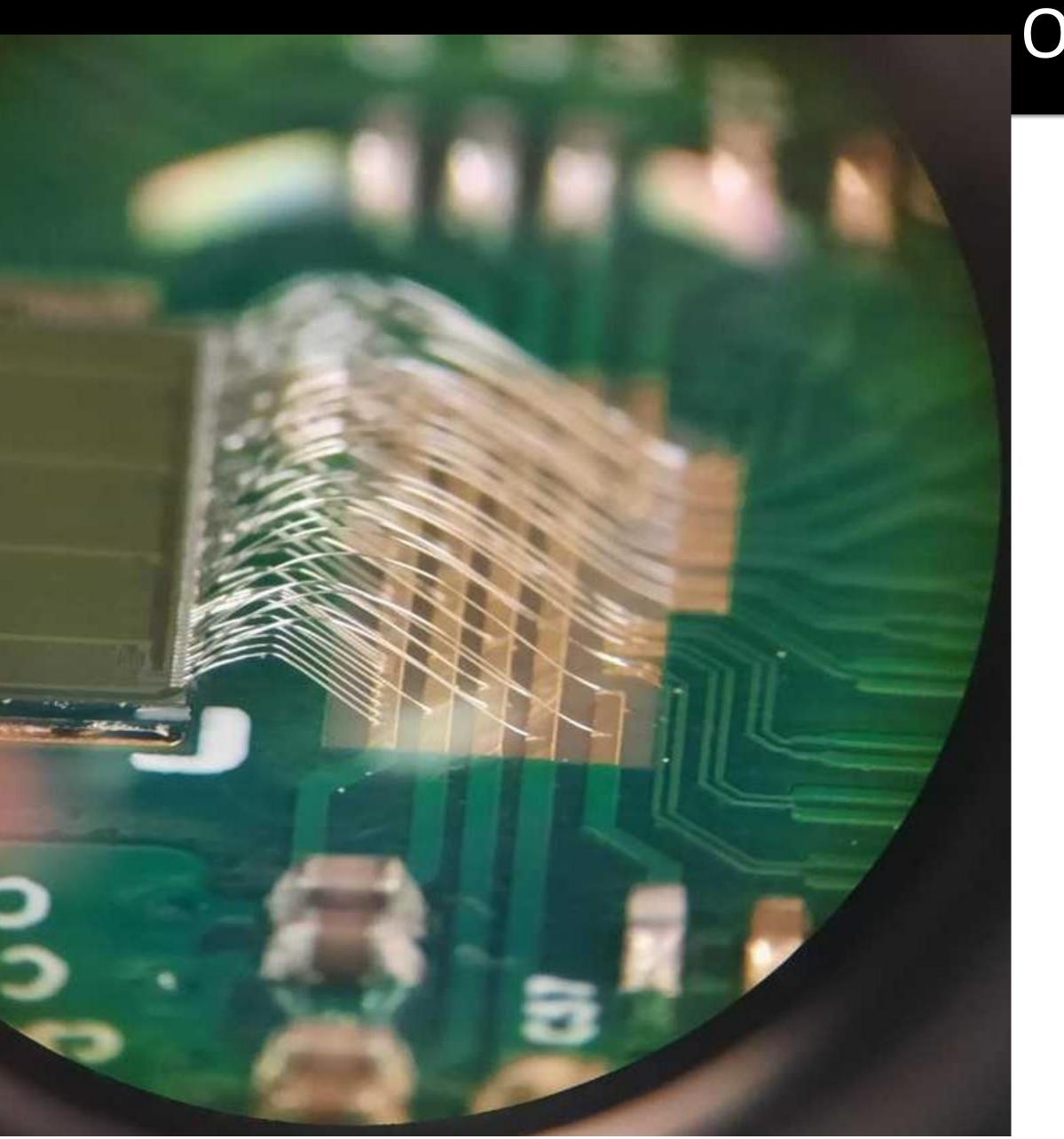

interface to the six ASICs for the I/O and powering will be made through a material flexible printed circuit board (PCB). Each ASIC has  $\sim 100$  wire bonding pads to be interconnected teor grease the flex PCB. The module flex will be interconnected to an external patch panel with zeroand dismountinesertion force connector for the digital signal, clock and command and with a separate pigtail for the module powering.

The module will drive four types of power lines, three LV supply and one HV for the six ASICs. 420 While the sensors will have low current consumption (below 100  $\mu A$ ), the analog, the digital and the driver supply lines will consume  $\sim 1$  A each. The system is designed to handle a module power

sors

# New Preshower Detector [II]

Jo

Wire bond protection cap Module flex Glue interface

Asics

Thermal glue

Aluminum base plate

Thermal interface sheet

### m fithela 12 modules per plange at on cooling plate

dules. The cooling plate size is  $\sim 20 \text{ x } 20 \text{ cm}^2$  and 5 mm thick. Of One

rts i**StefanouZambito**anel with ensites ides Gethèves. The module consists of bed on Figure 13 except the base plate and the thermal interface sheet.

## 6 ASICs per module, 208x128 pixels each

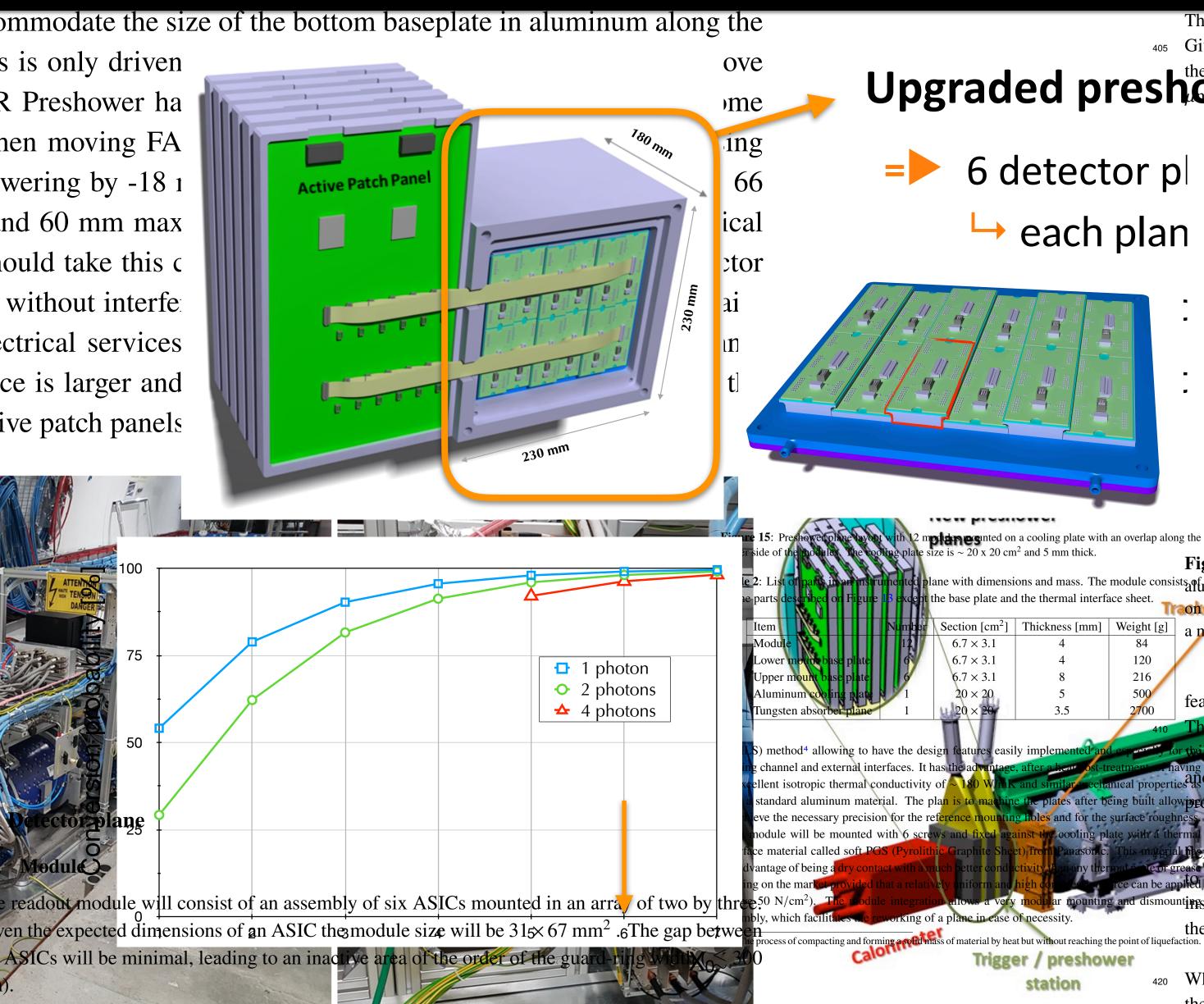

## **Detailed Preshower Simulation**

**Stefano Zambito** | *Université de Genève*

### Plane 5

1000

Plane 6

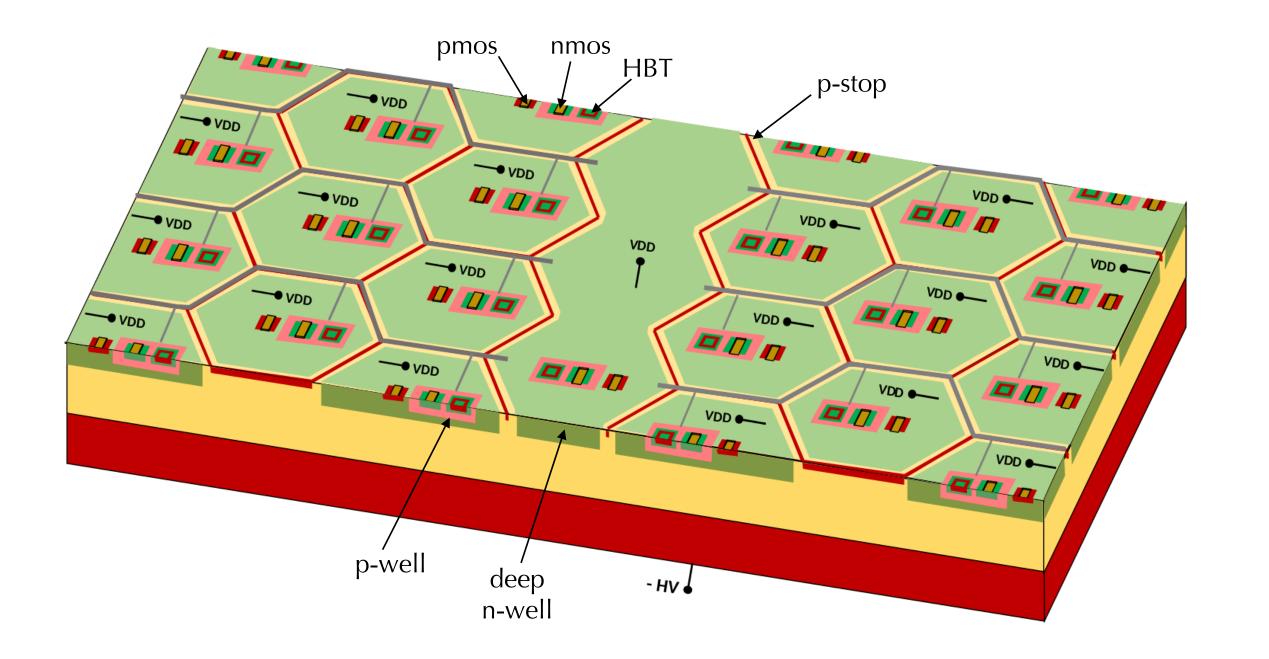

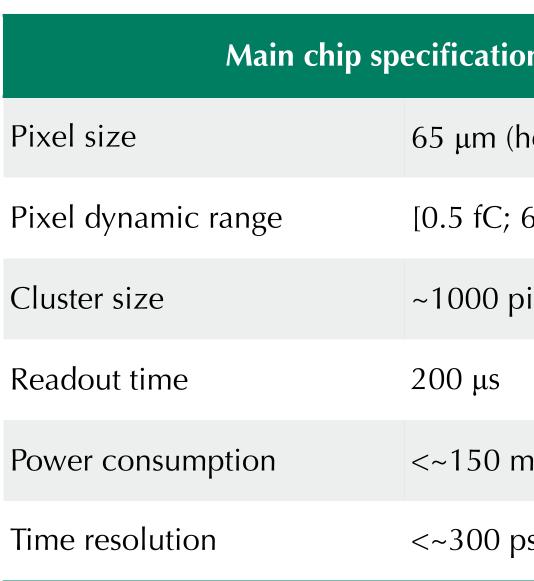

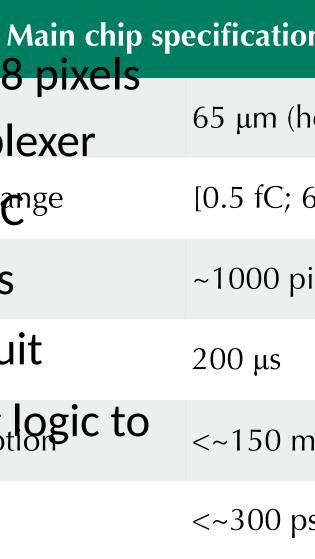

## Monolithic Pixel ASIC: Sensor

## **Monolithic active pixel sensor** 130 nm SiGe BiCMOS technology (IHP SG13G2)

High-resistivity (220  $\Omega \cdot cm$ ) substrate, about 130  $\mu m$  thickness = Hexagonal pixels integrated as triple wells; pixel capacitance of 80 fF

| Main specifications |                          |  |

|---------------------|--------------------------|--|

| Pixel Size          | 65 μm side (hexagonal)   |  |

| Pixel dynamic range | 0.5 ÷ 65 fC              |  |

| Cluster size        | ter size O(1000) pixels  |  |

| Readout time        | < 200 µs                 |  |

| Power consuption    | < 150 mW/cm <sup>2</sup> |  |

| Time resolution     | < 300 ps                 |  |

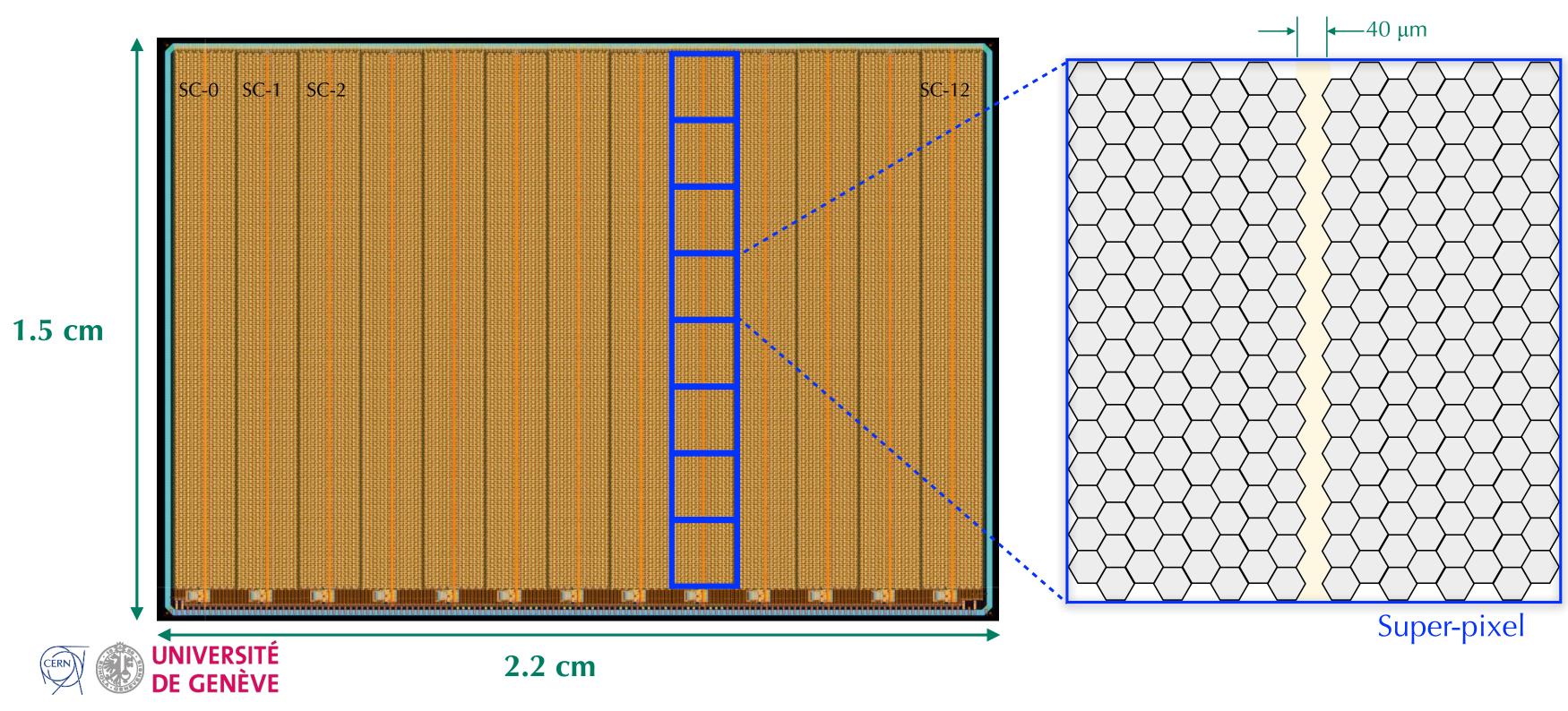

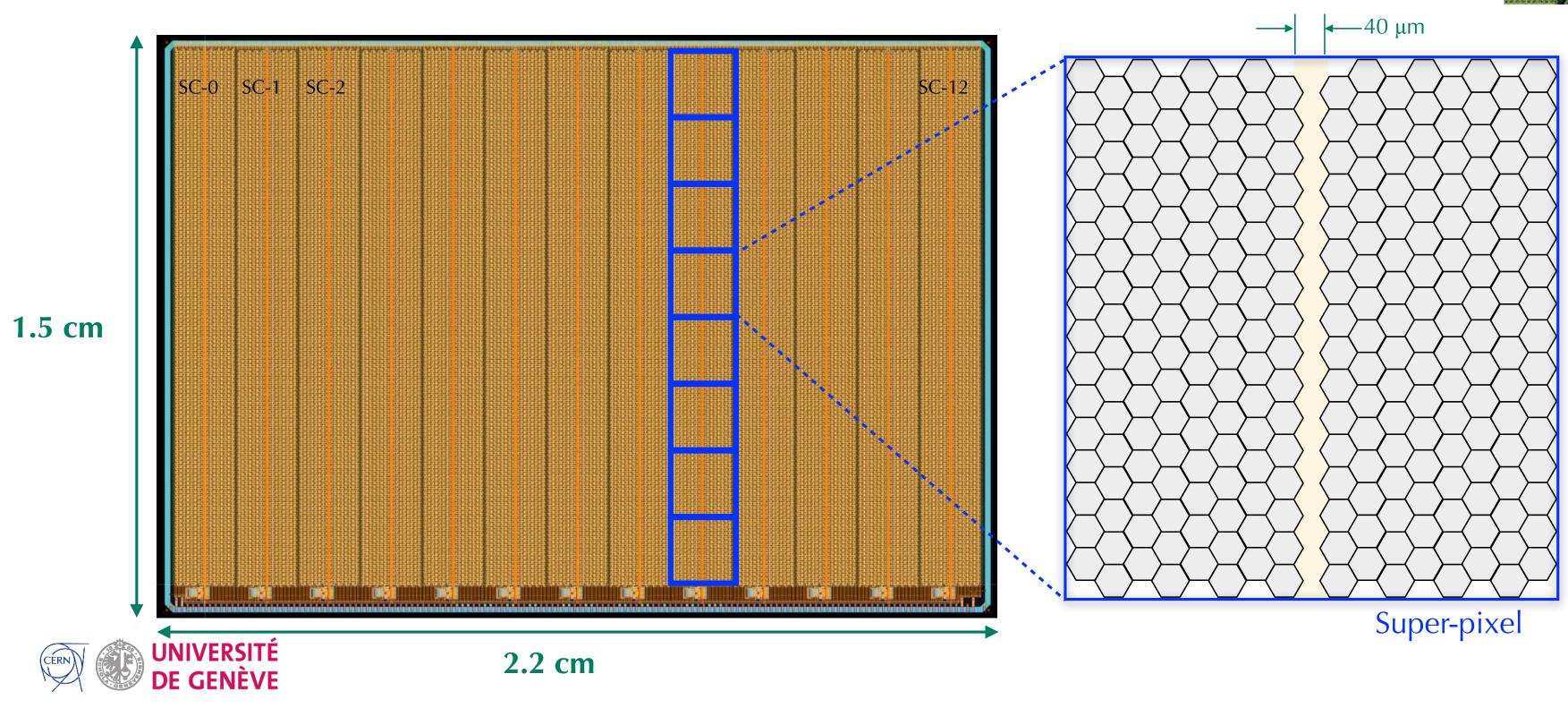

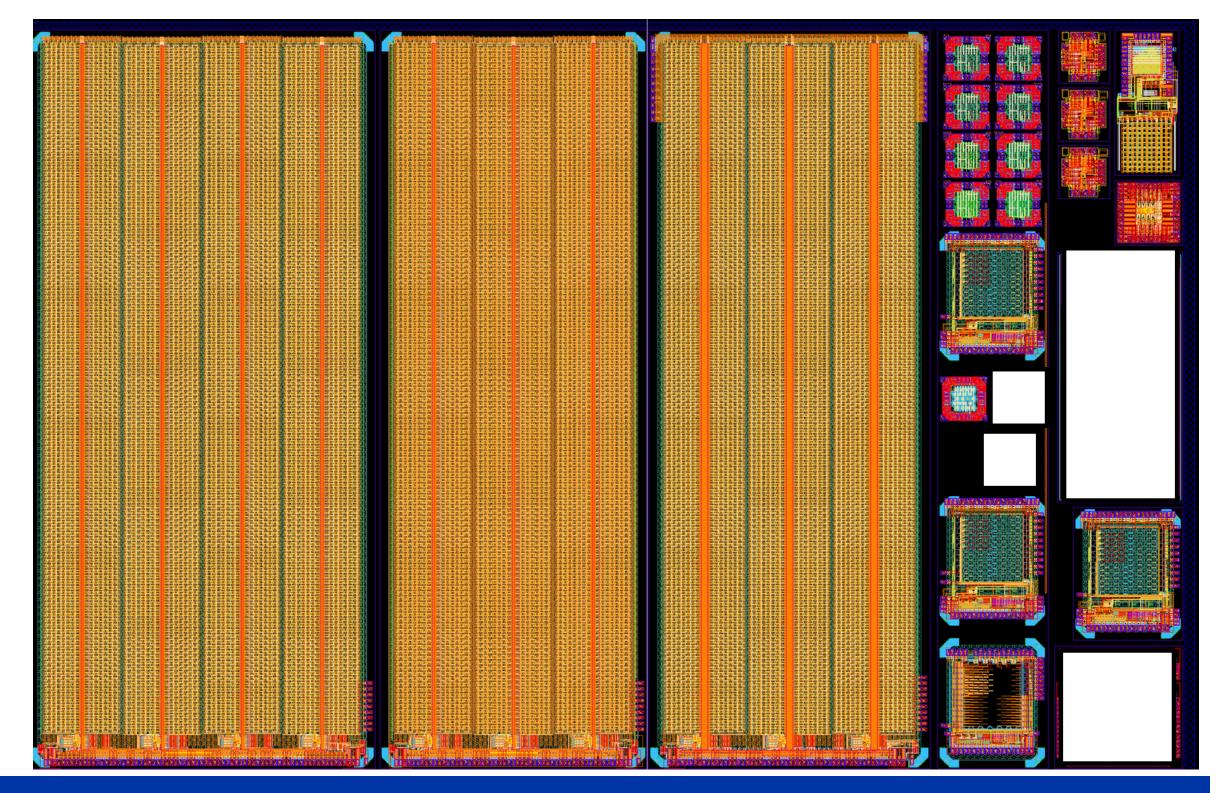

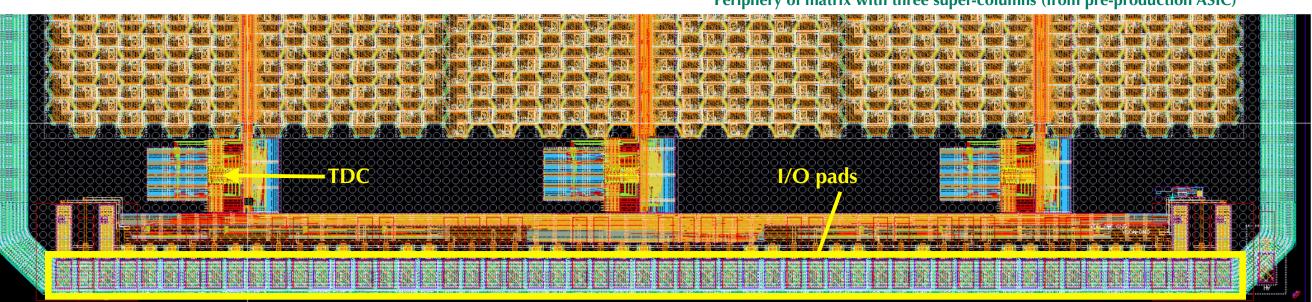

# Monolithic Pixel ASIC: Chip Structure

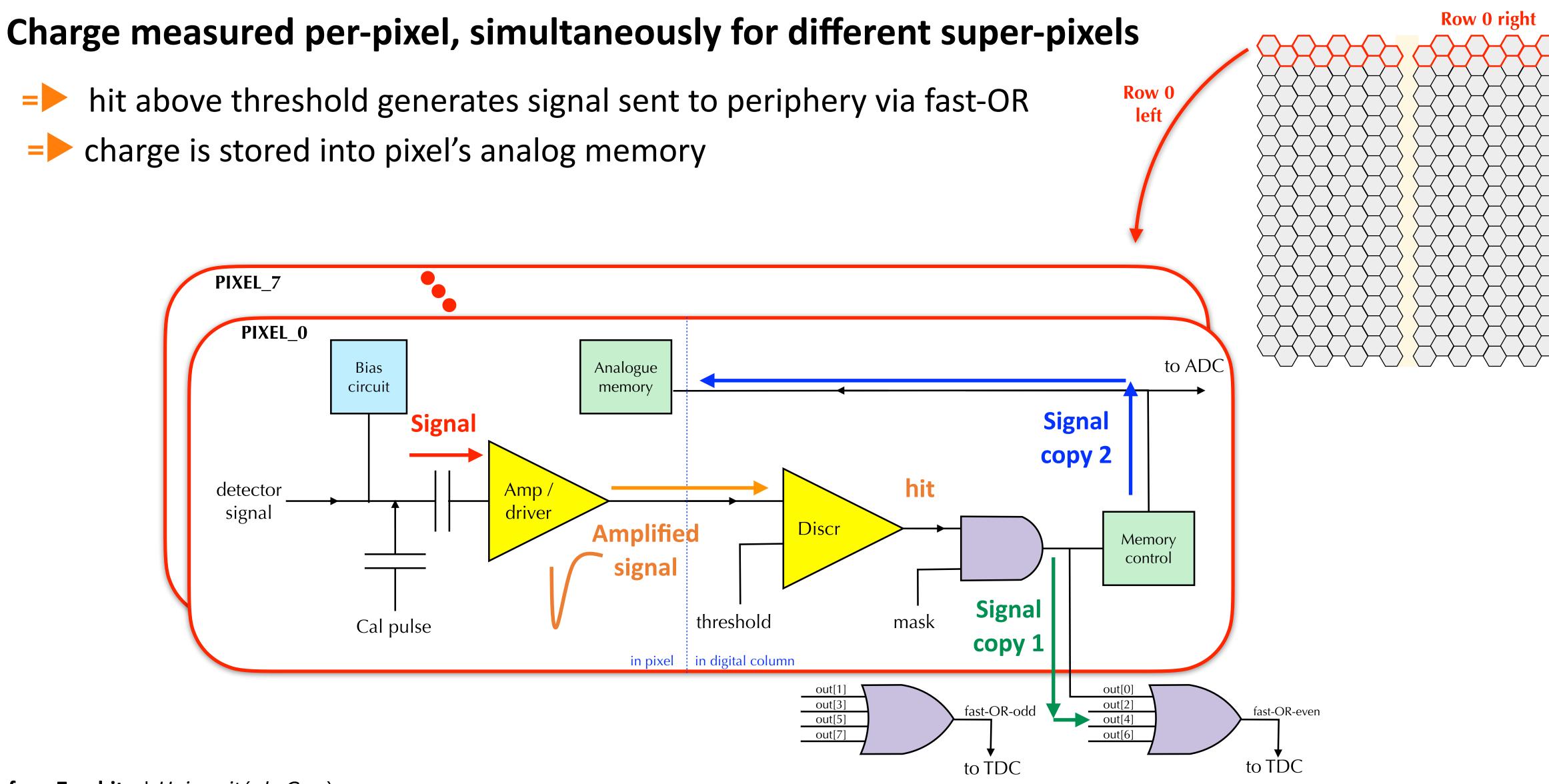

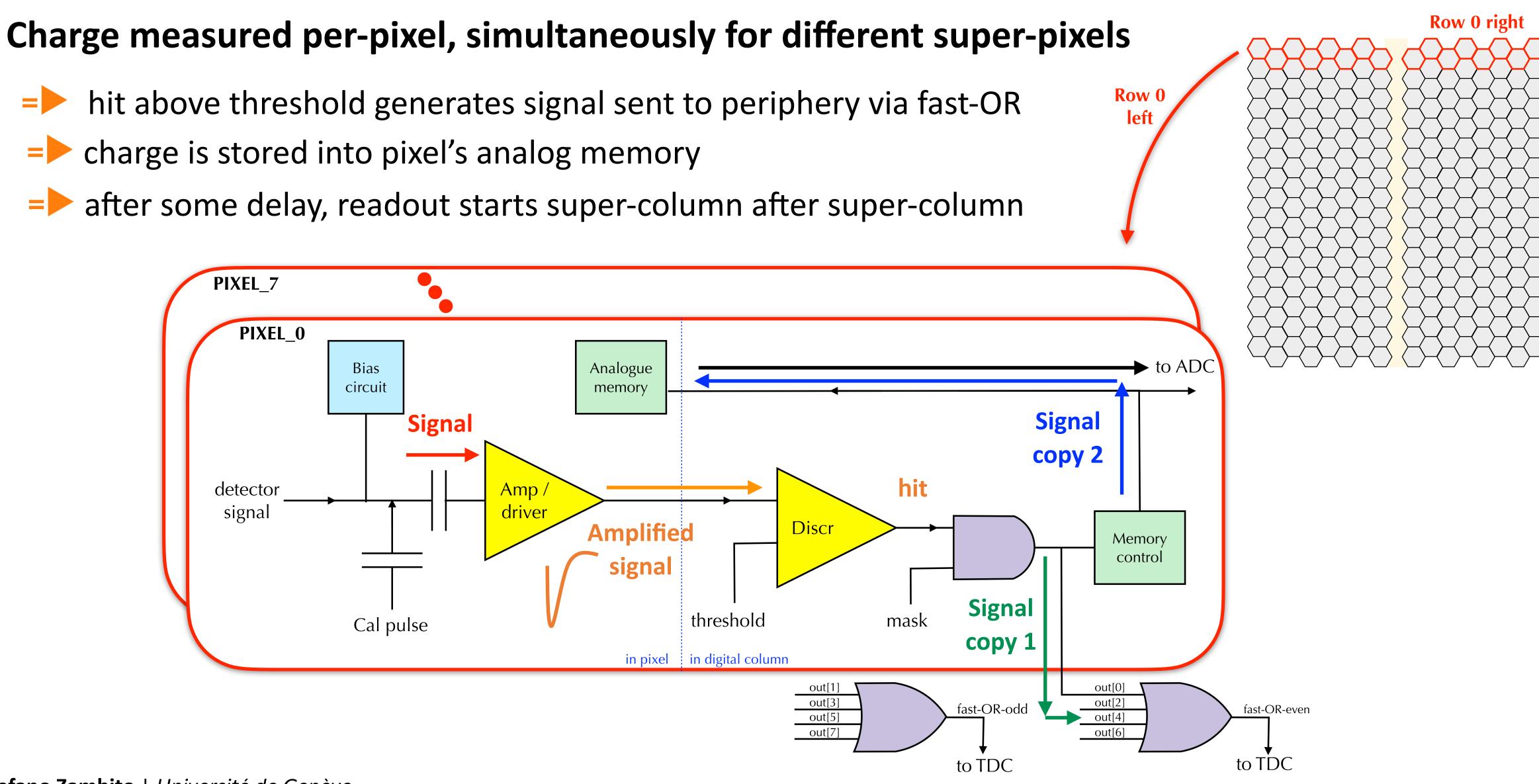

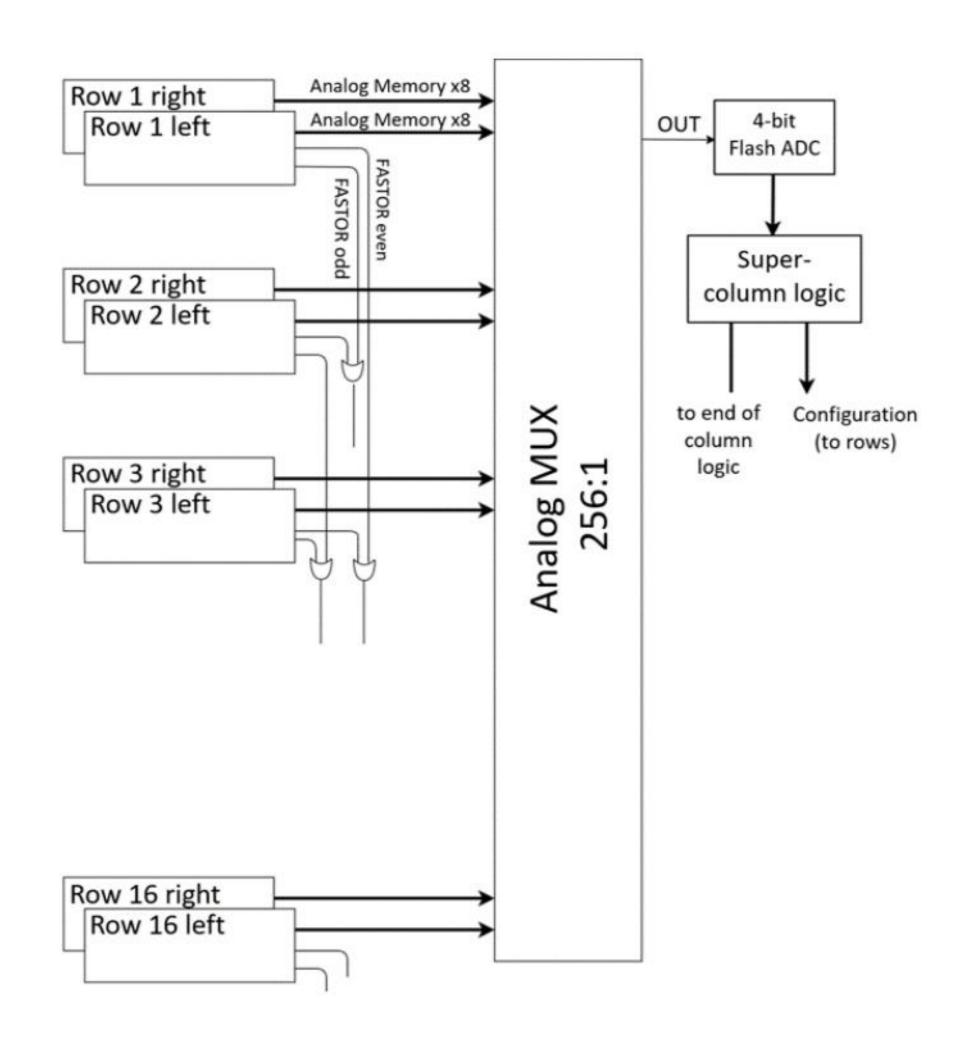

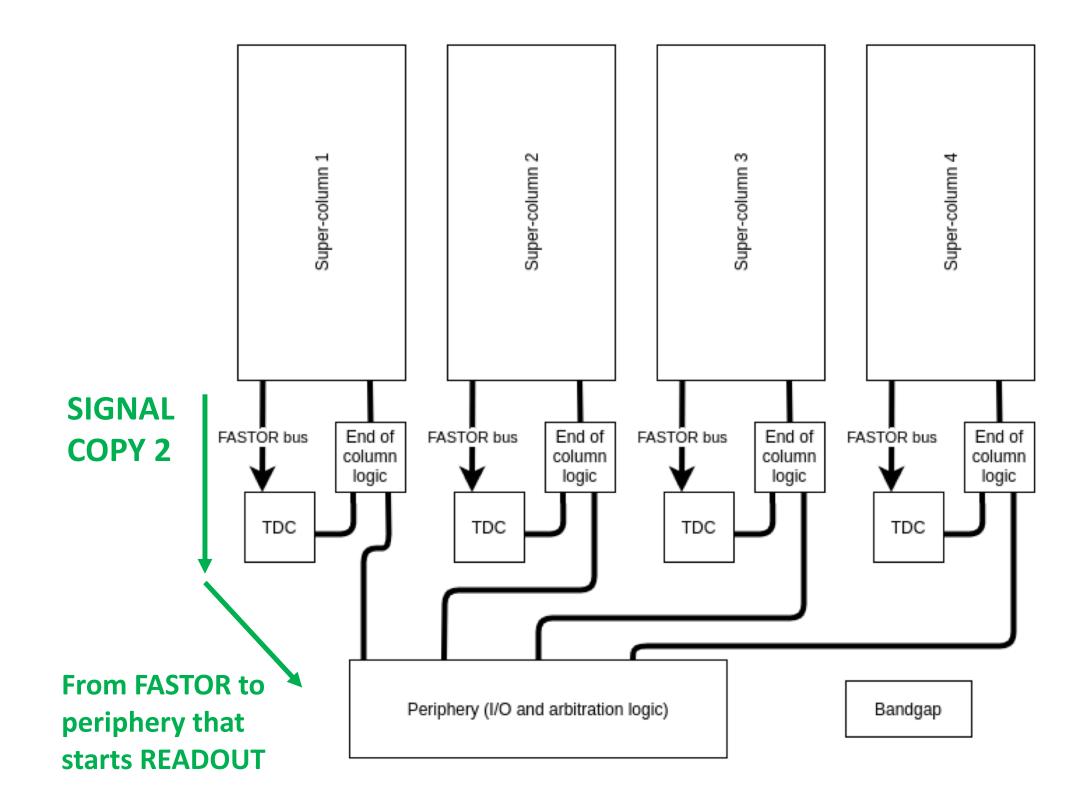

## Chip organized in 13 "super-columns", each with:

- active region, subdivided into 8 "super-pixels" of 16x16 pixel each

- digital column (40 μm) in the middle: sharing of digital electronics Digital periphery on the bottom, and multiple guard-ring structure

**Stefano Zambito** | *Université de Genève*

Time resolution

# Monolithic Pixel ASIC: Chip Structure

## Chip organized in 13 "super-columns", each with:

- active region, subdivided into 8 "super-pixels" of 16x16 pixel each

## Digital periphery on the bottom, and multiple guard-ring structure

**Stefano Zambito** | *Université de Genève*

digital column (40 μm) in the middle: sharing of digital electronics

### Super pix

- $\rightarrow$  16 rows of 8+8 pixels

- → analog multiplexer

- → 4-Biteflash ADC ge

- → 3 fastet @Rzlines

- → localabiatsificuit

- programming logic to mask pixels Time resolution

Dead area <5%

=

= =

- =

- charge is stored into pixel's analog memory

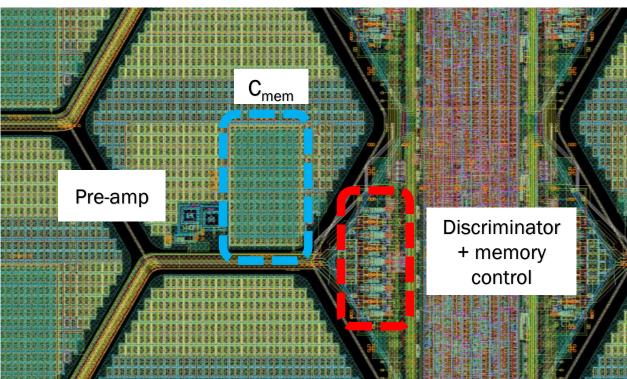

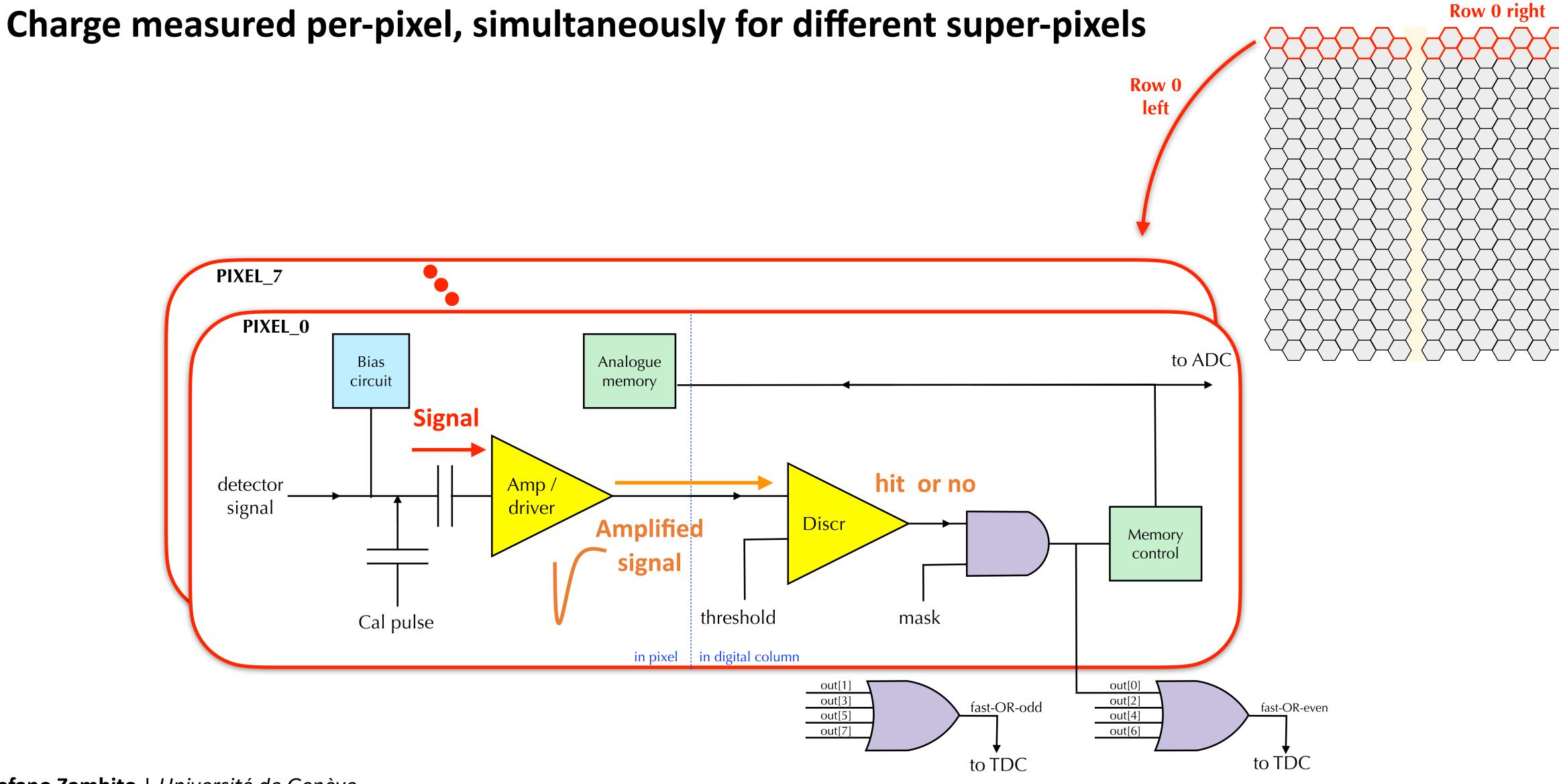

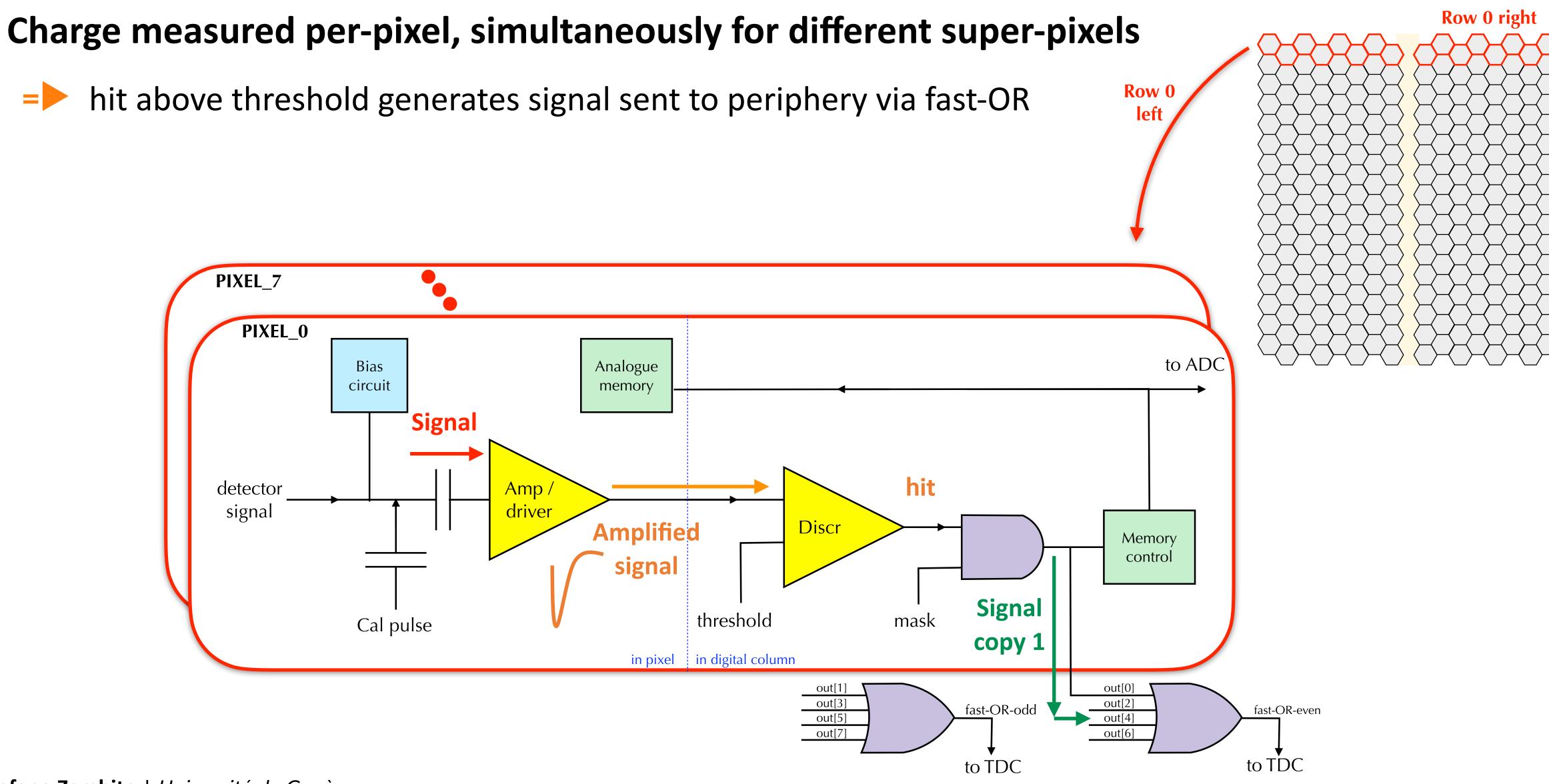

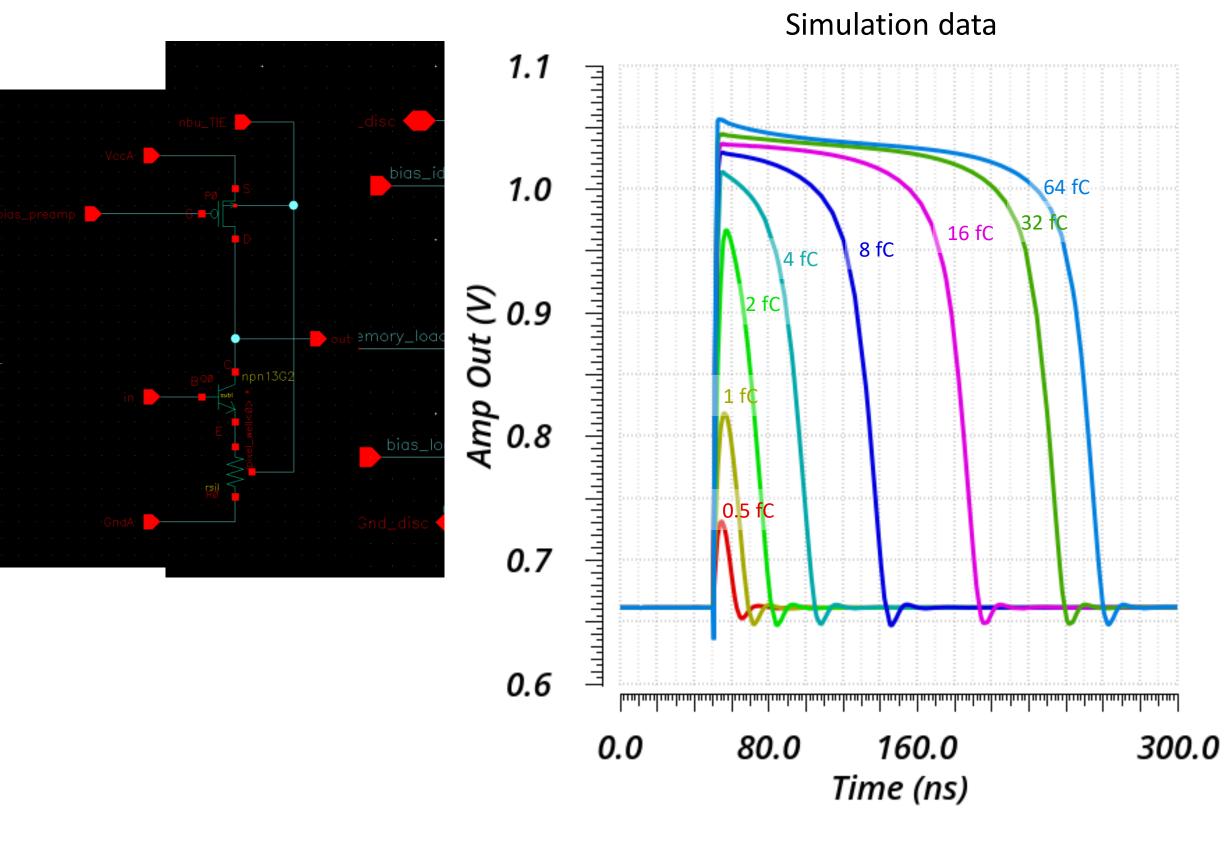

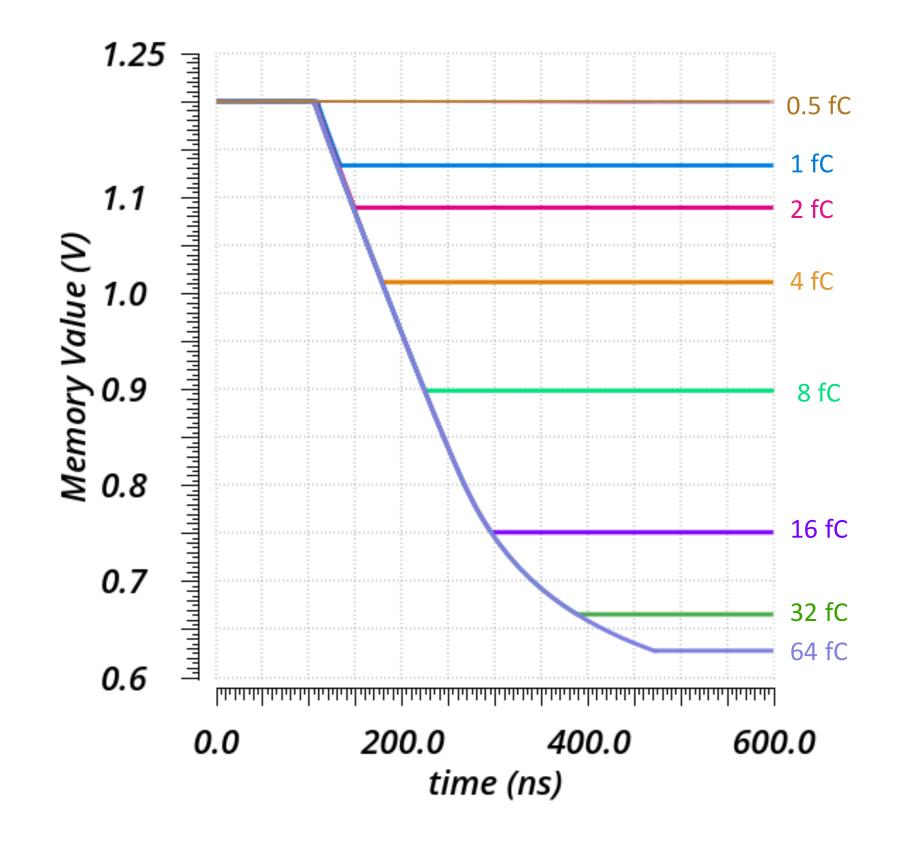

# Monolithic Pixel ASIC: Charge Measurement

## Analog memories: capacitors inside each pixel charged with const current during ToT

when signal returns below threshold, memory is disconnected and left floating until read by flash ADC = preamplifier designed to produce a signal proportional to the *log* of input charge

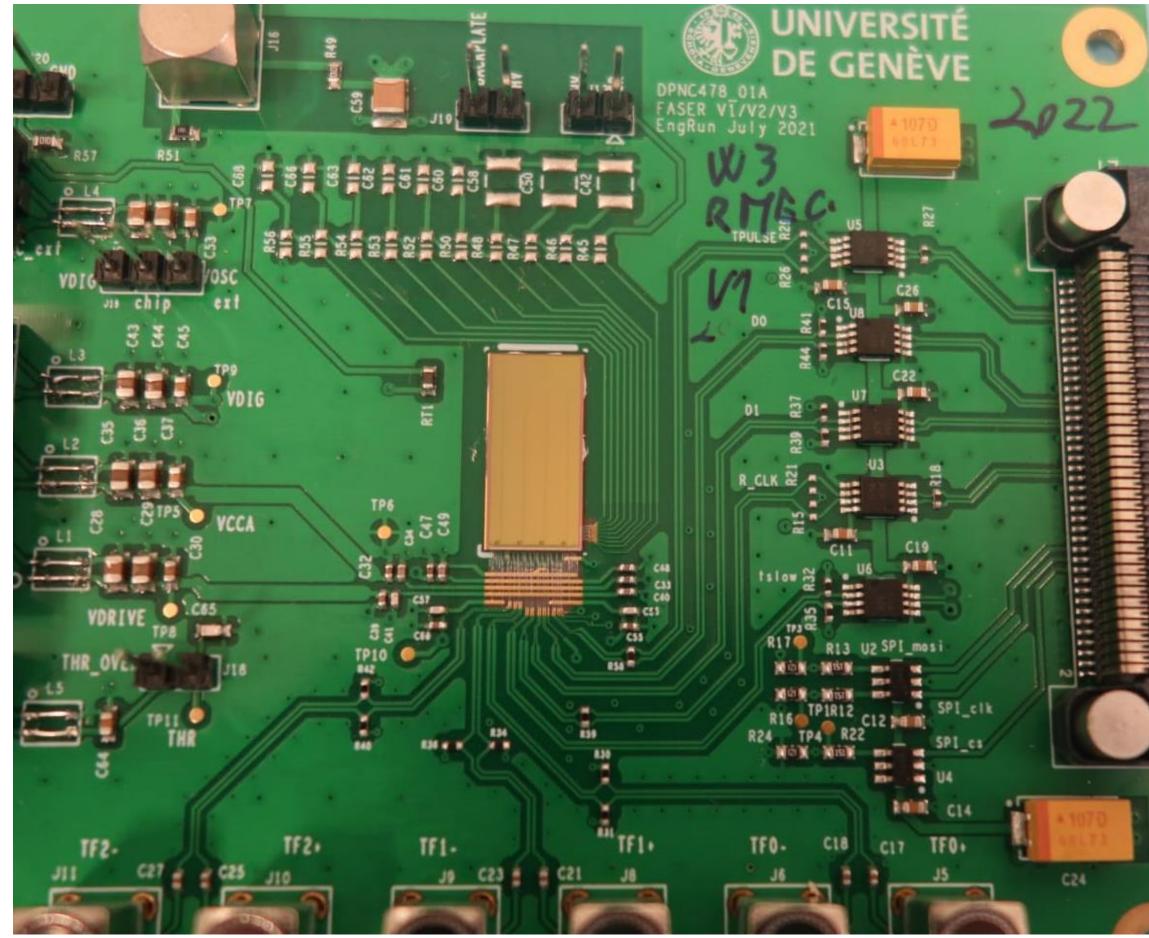

# Pre-production Chip (2022)

## **Engineering run (IHP Microelectronics)**

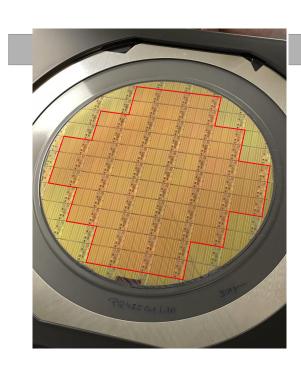

In each reticle, three pixel matrices

FASER\_v1 (baseline)

- → 128 x 64 pixels, 4 super-columns

- → in-pixel pre-amp and driver

- └→ discriminator outside

### FASER\_v2

- → 128 x 48 pixels, 3 super-columns

- → in-pixel pre-amp, driver, and discriminator

### FASER\_ALT

- → 128 x 48 pixels, 3 super-columns

- → no analog memories

- → counter for charge measurement

- Several test structures (TDC, etc...)

### Reticle: 2.4 x 1.5 cm<sup>2</sup>

53 reticles per wafer

Thickness 300 µm

### FASER\_v2

### FASER DE GENÈVE FASER ALT

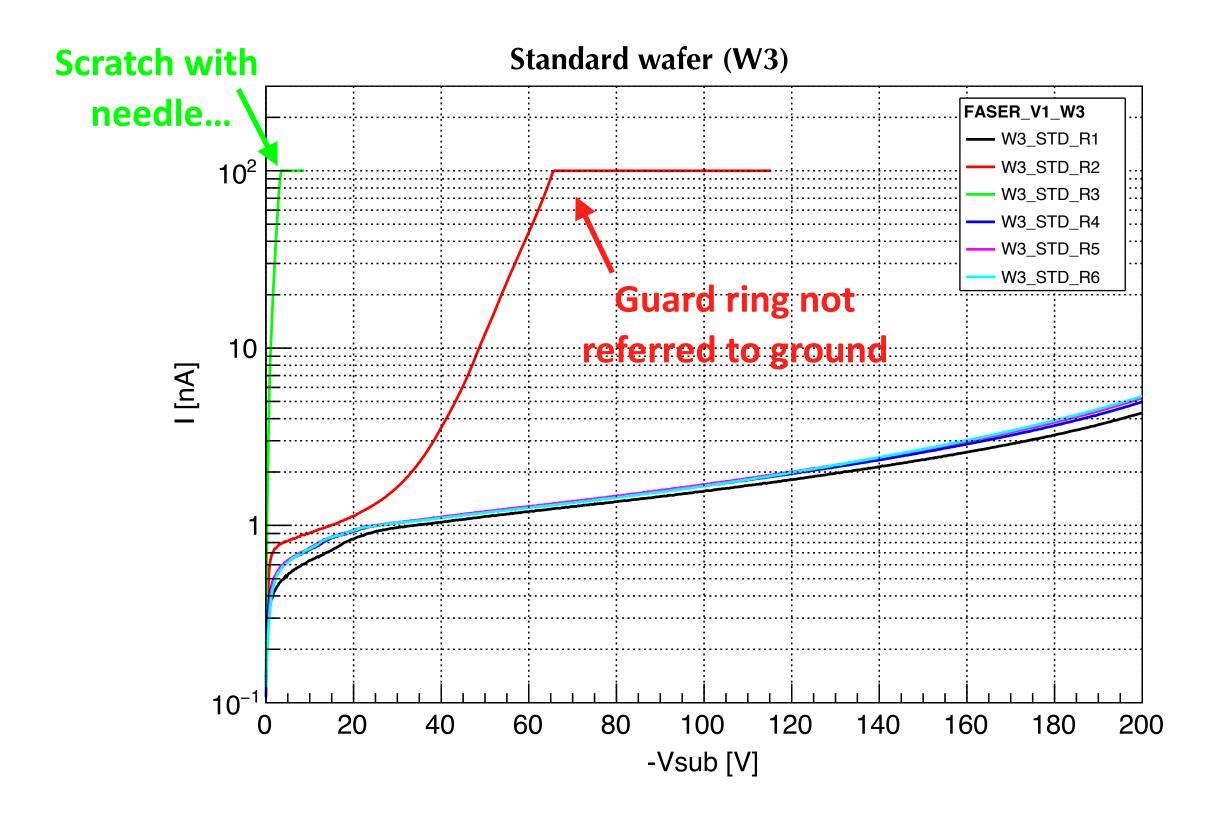

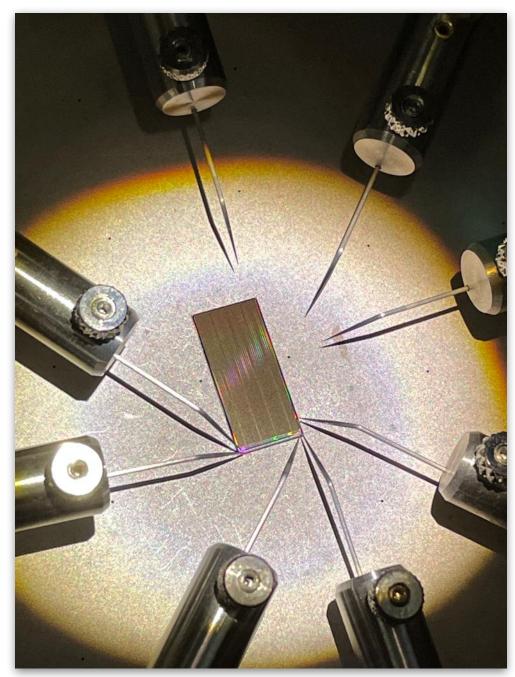

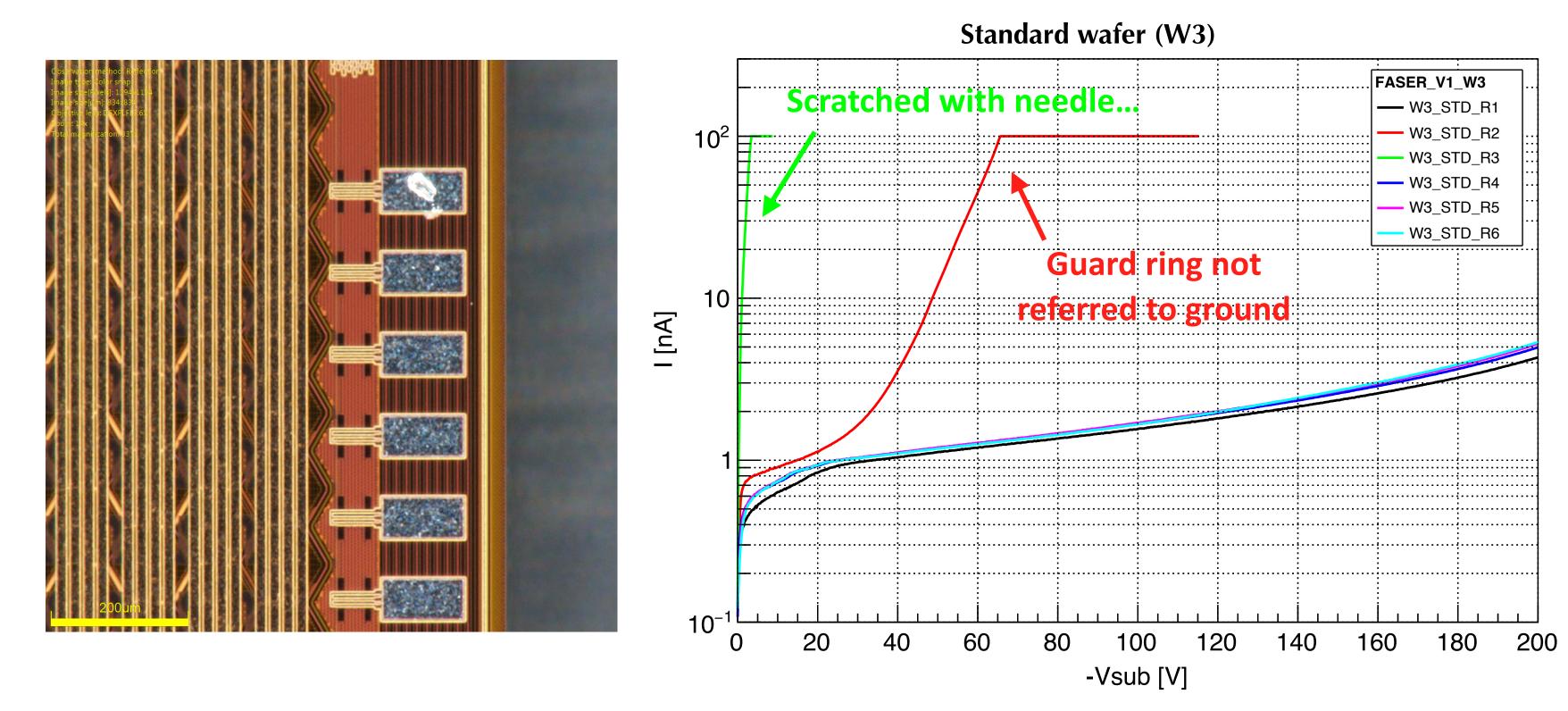

# Pre-production Chip: I-V Characteristic [I]

## Wafers with pre-production prototype chips received on Jun 13th, 2022

## **Good results from I-V characterizations at probe station**

reaching 200 V with guard ring connected to ground, 170 V otherwise =

FASER\_MAIN chip

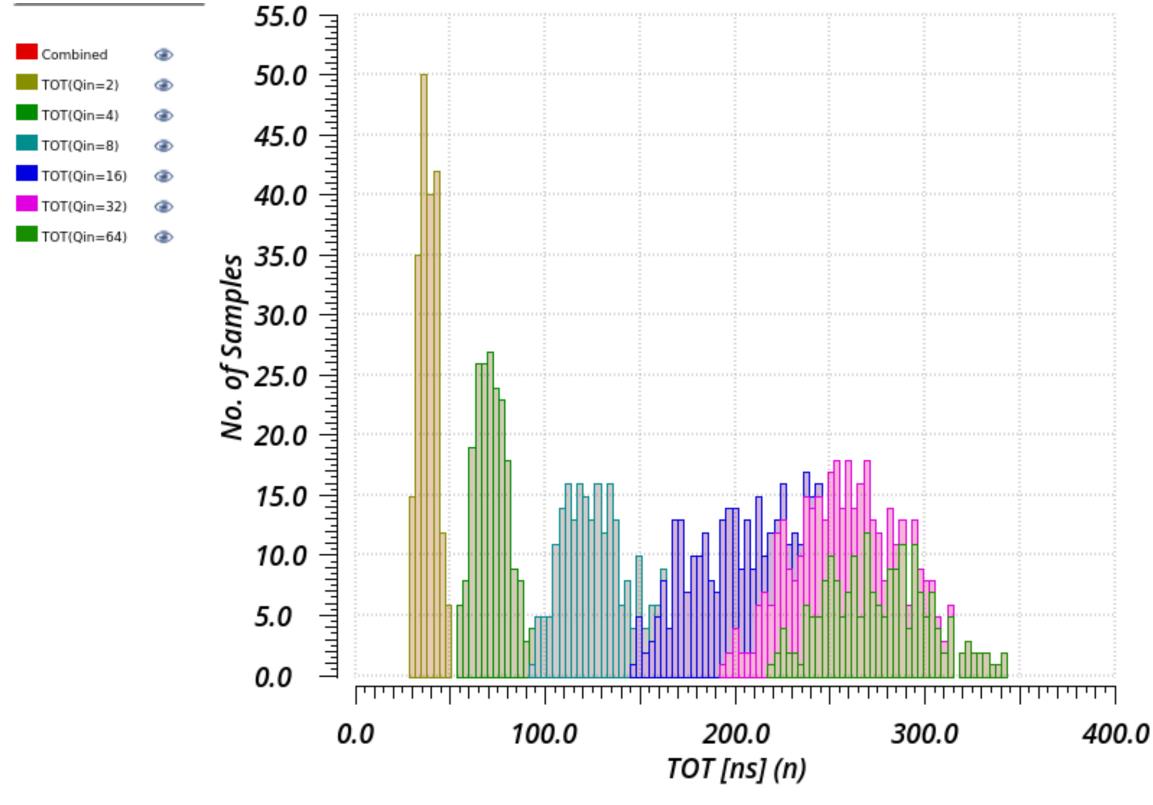

# Pre-production Chip: TOT (Charge) Mismatch [I]

### **Stefano Zambito** | *Université de Genève*

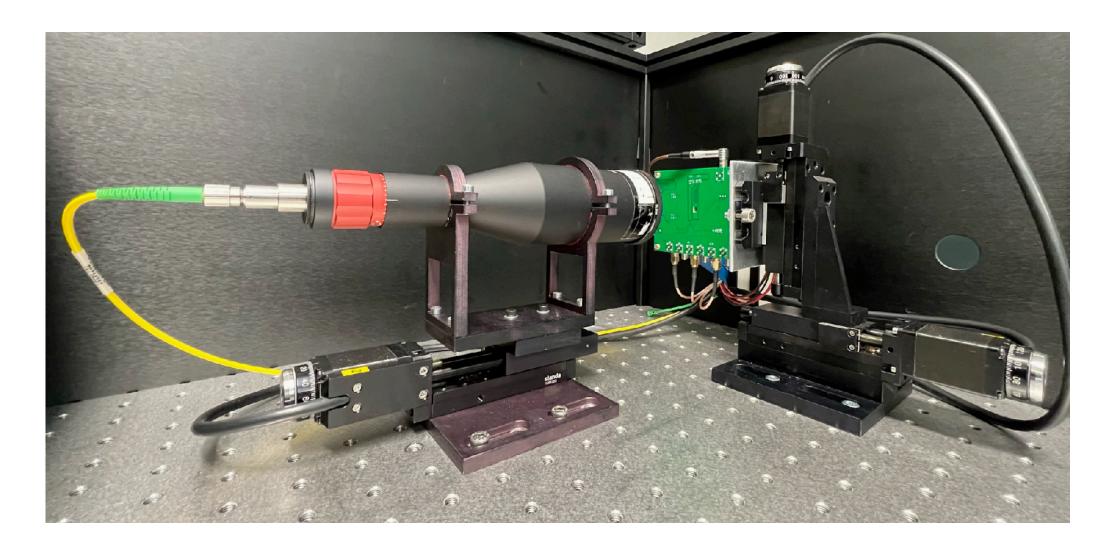

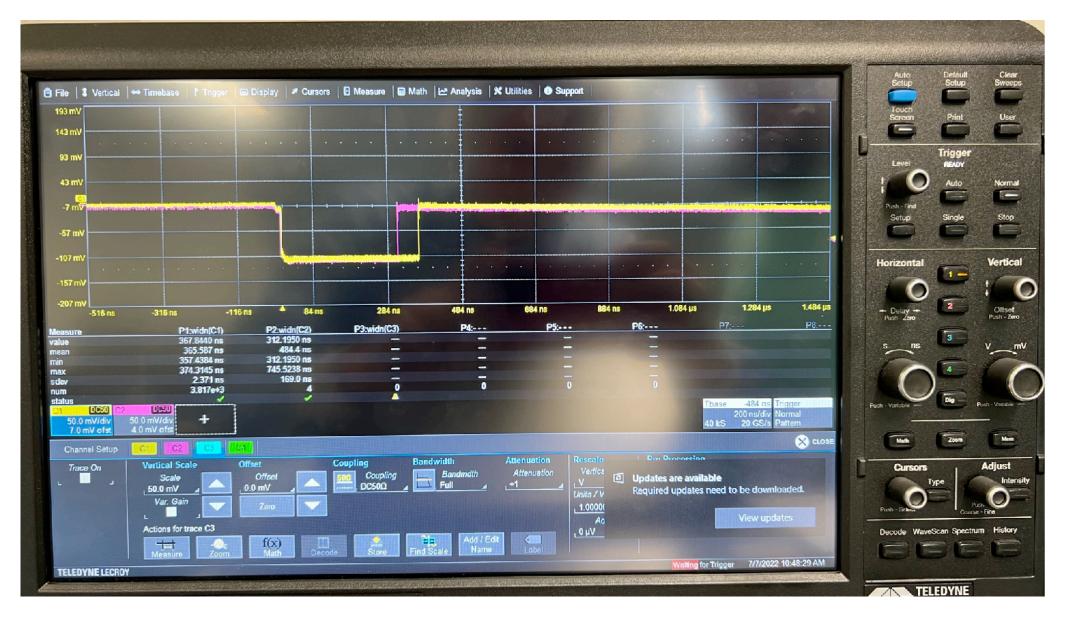

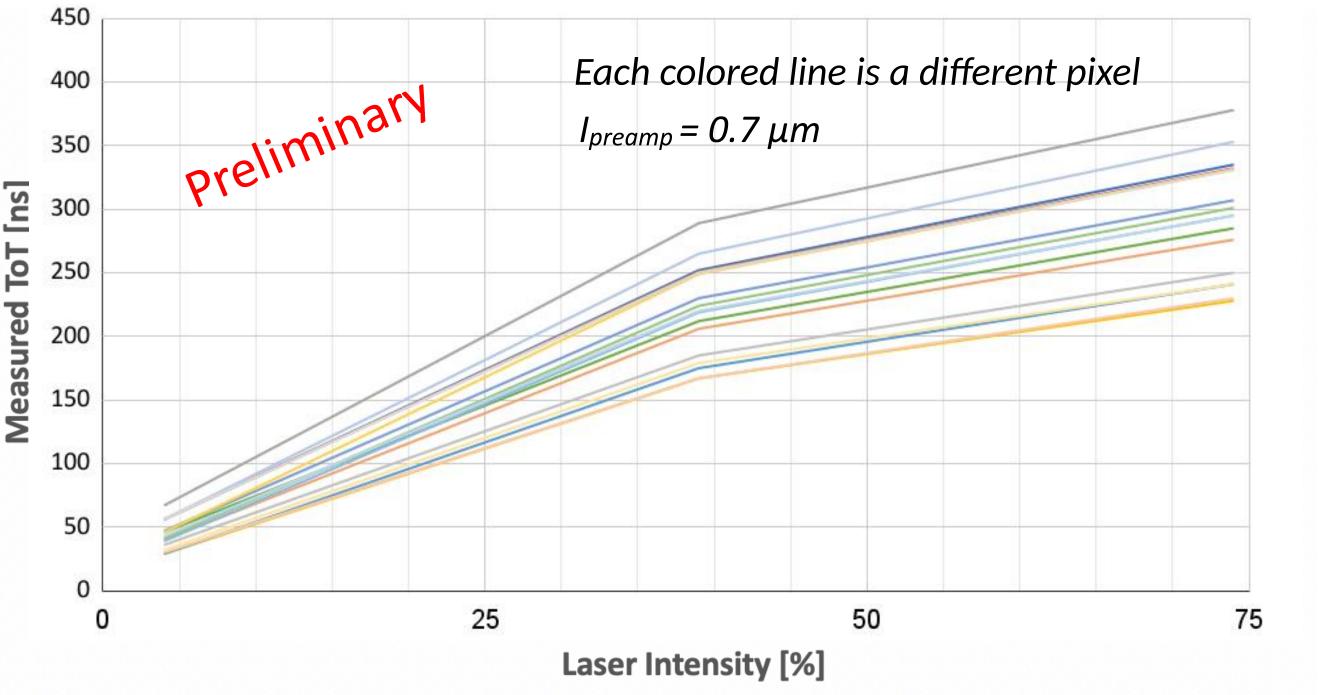

## **Evaluating charge response with infrared laser**

- measuring ToT via fast-OR signal on the scope =

- varying per-pixel injected charge via laser attenuator

- measurement repeated at different *I*<sub>preamp</sub> =

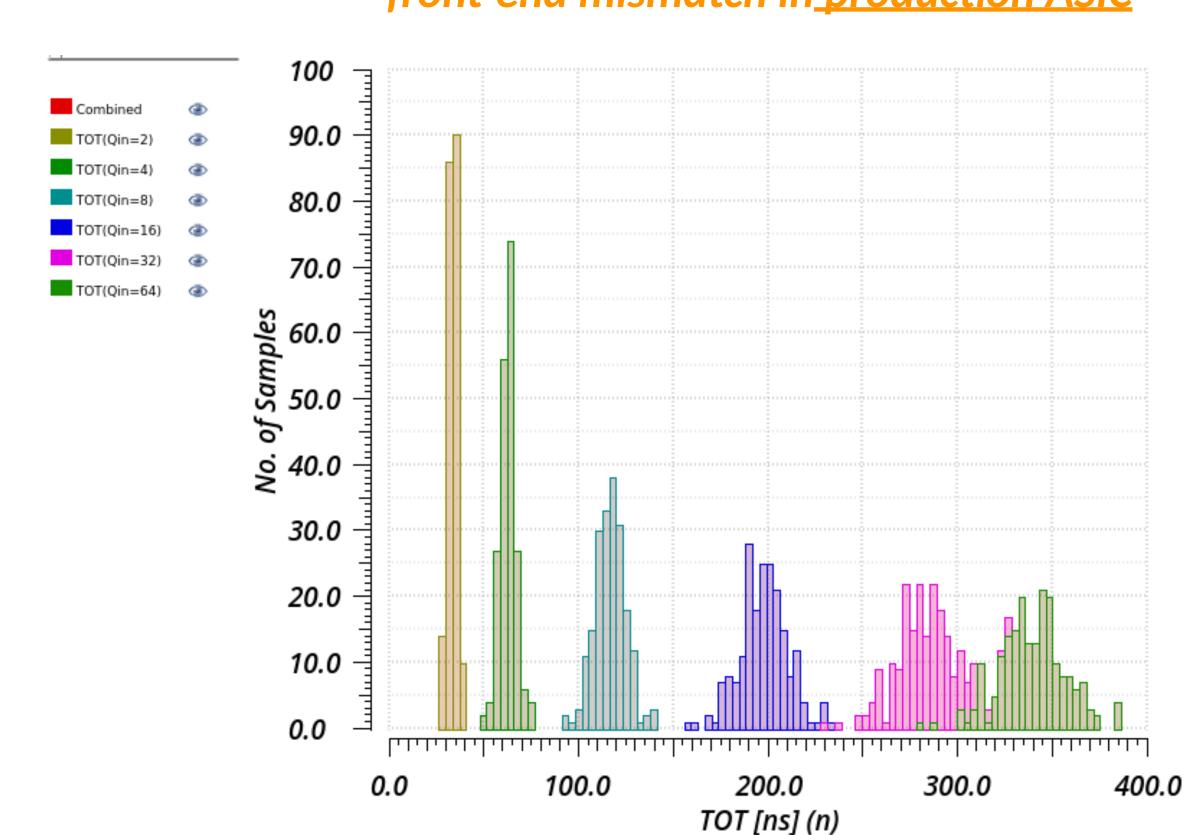

# Pre-production Chip: TOT (Charge) Mismatch [II]

## Expect improvement of front-end uniformity in production ASIC thanks to bigger transistors

**Cadence Spectre Simulation:**

front-end mismatch in <u>pre-reduction prototype</u>

**Stefano Zambito** | *Université de Genève*

### **Cadence Spectre Simulation:**

### front-end mismatch in production ASIC

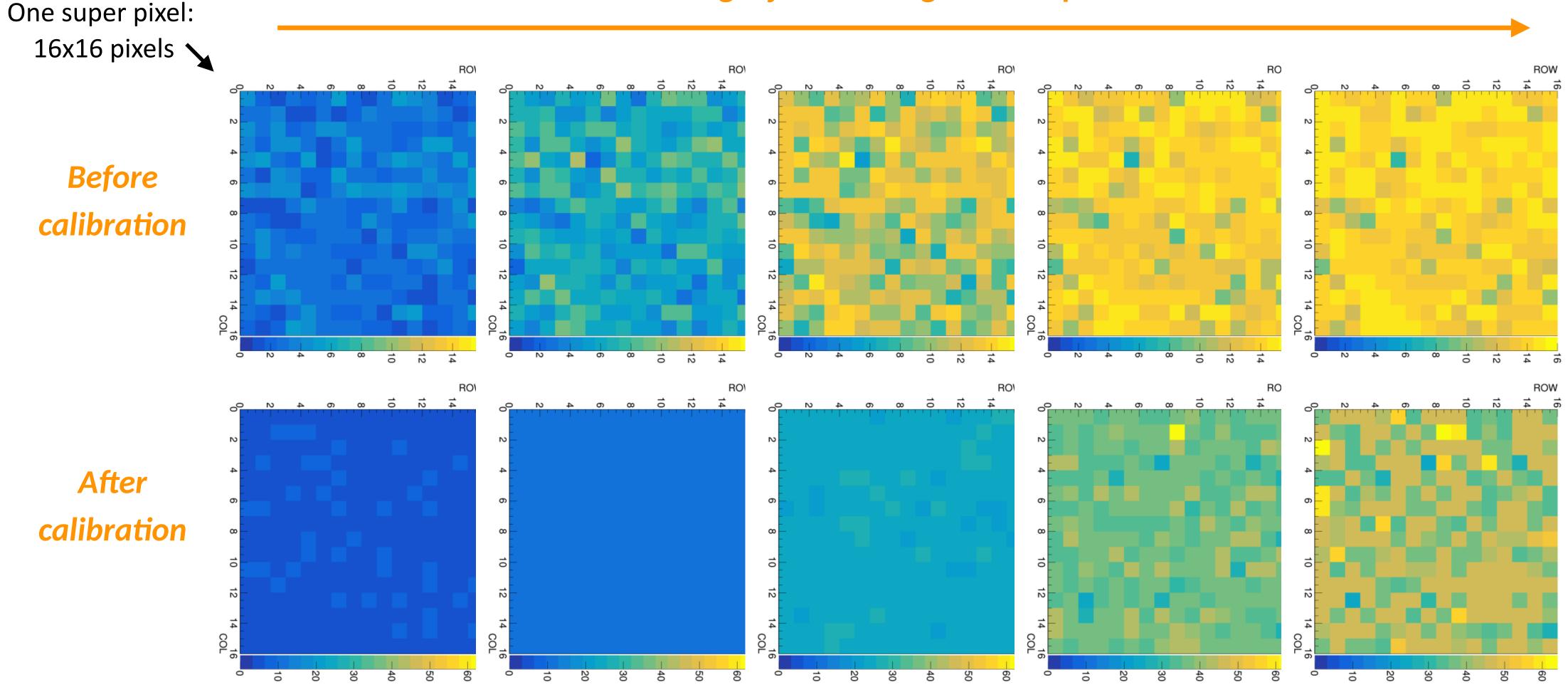

# Test With Full Readout: Charge Calibration

Color map  $\Rightarrow$  ADC response: [0-15] before calibration, [0fC-65fC] after calibration

**Stefano Zambito** | *Université de Genève* UNIVERSITE

### Increasing injected charge via testpulse

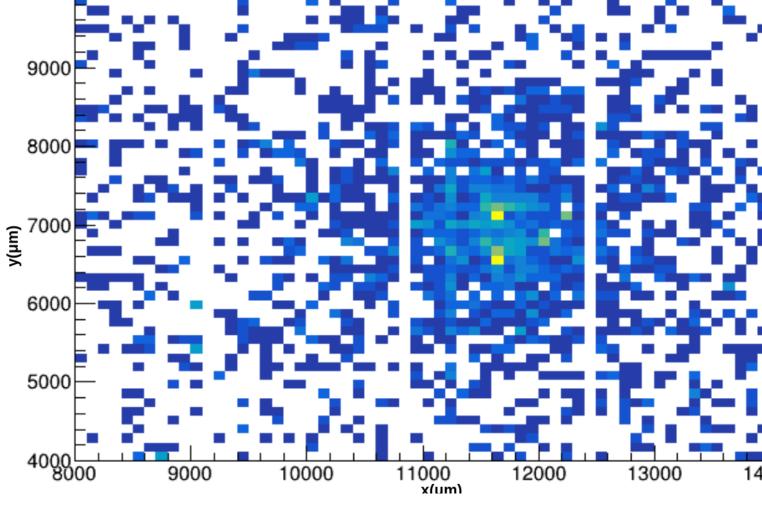

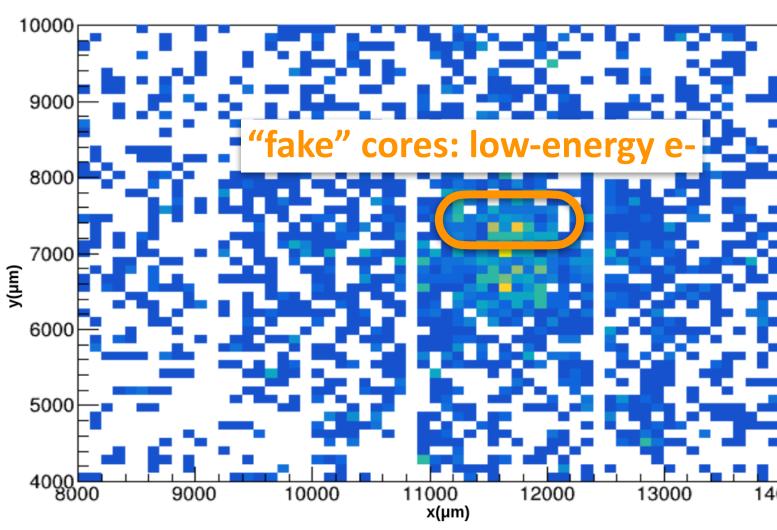

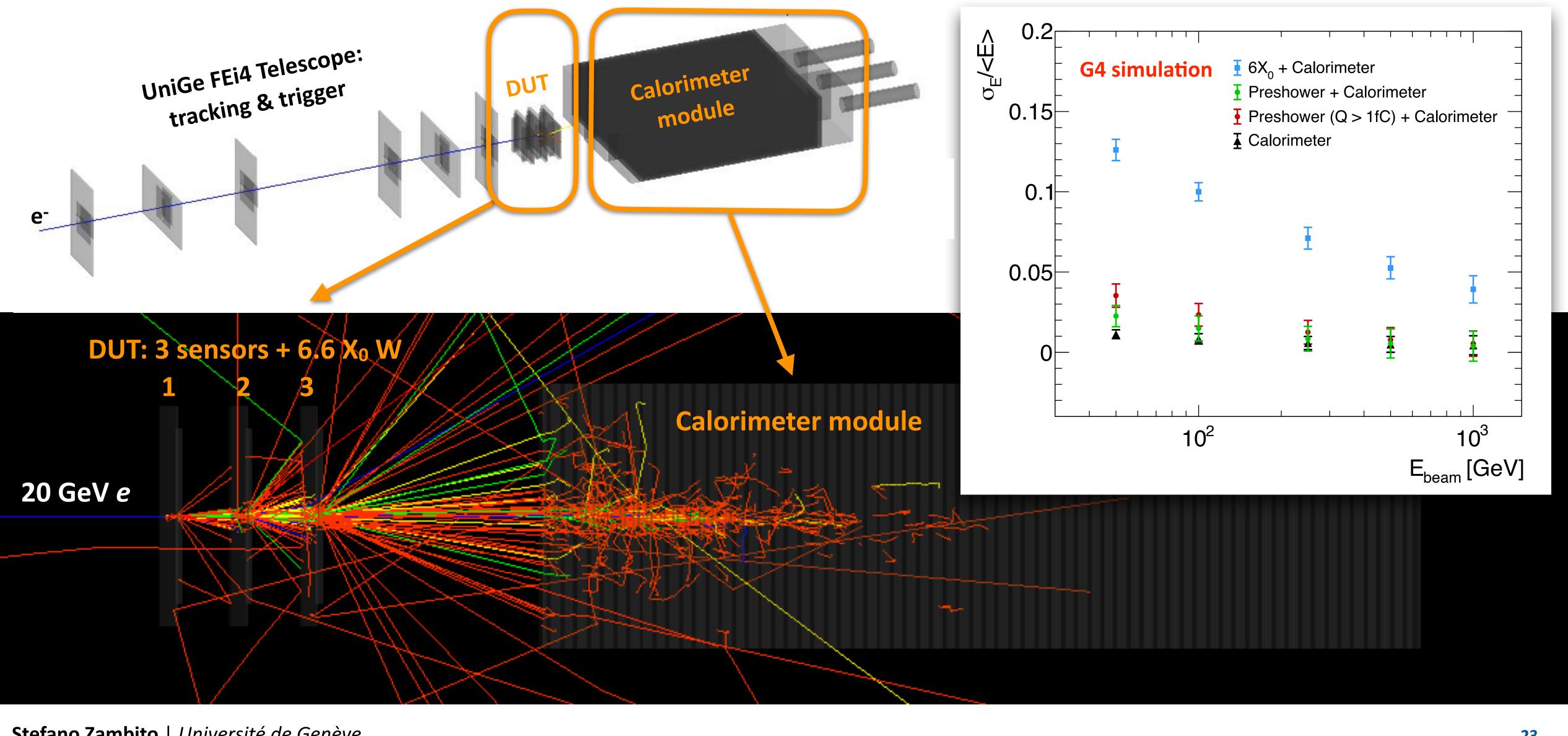

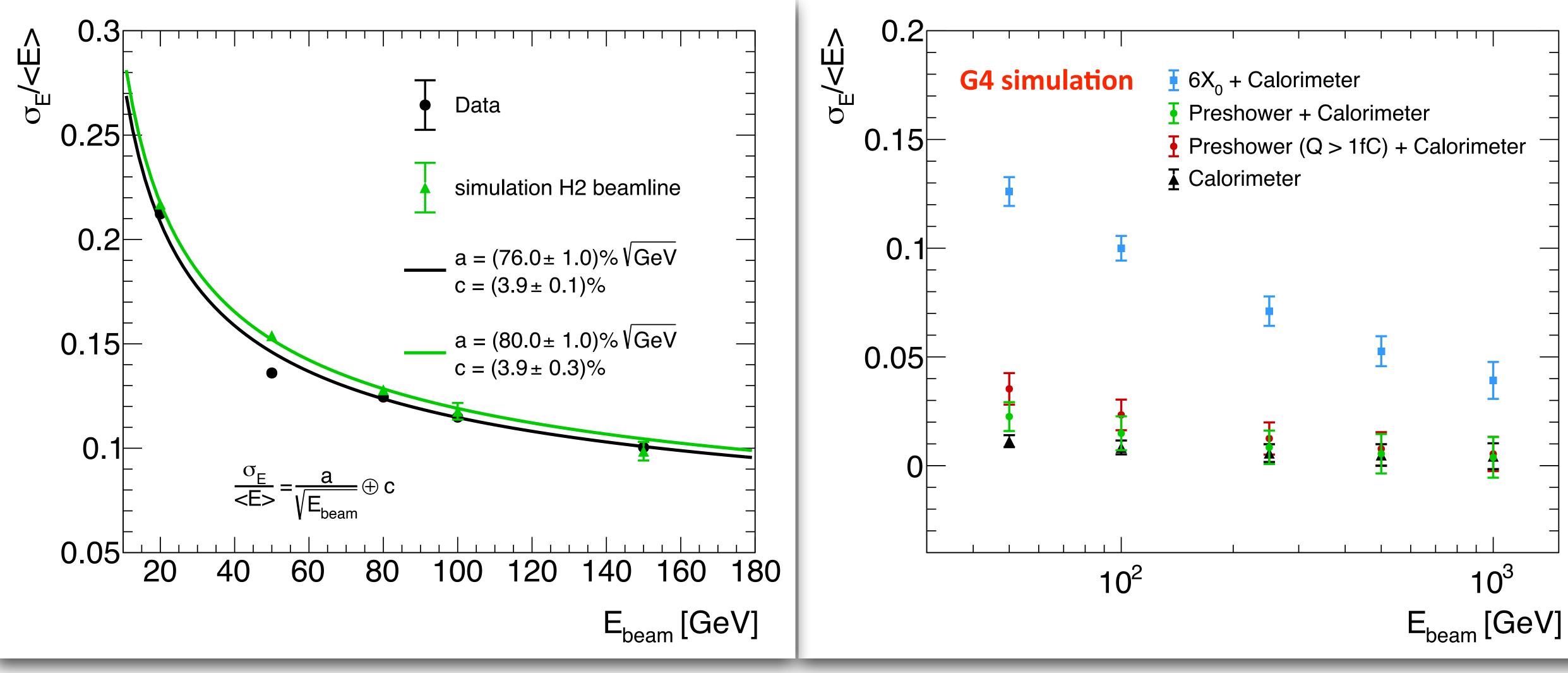

# September 2022: CERN SPS Test Beam (20-150 GeV e<sup>-</sup>)

## Summary & Outlook

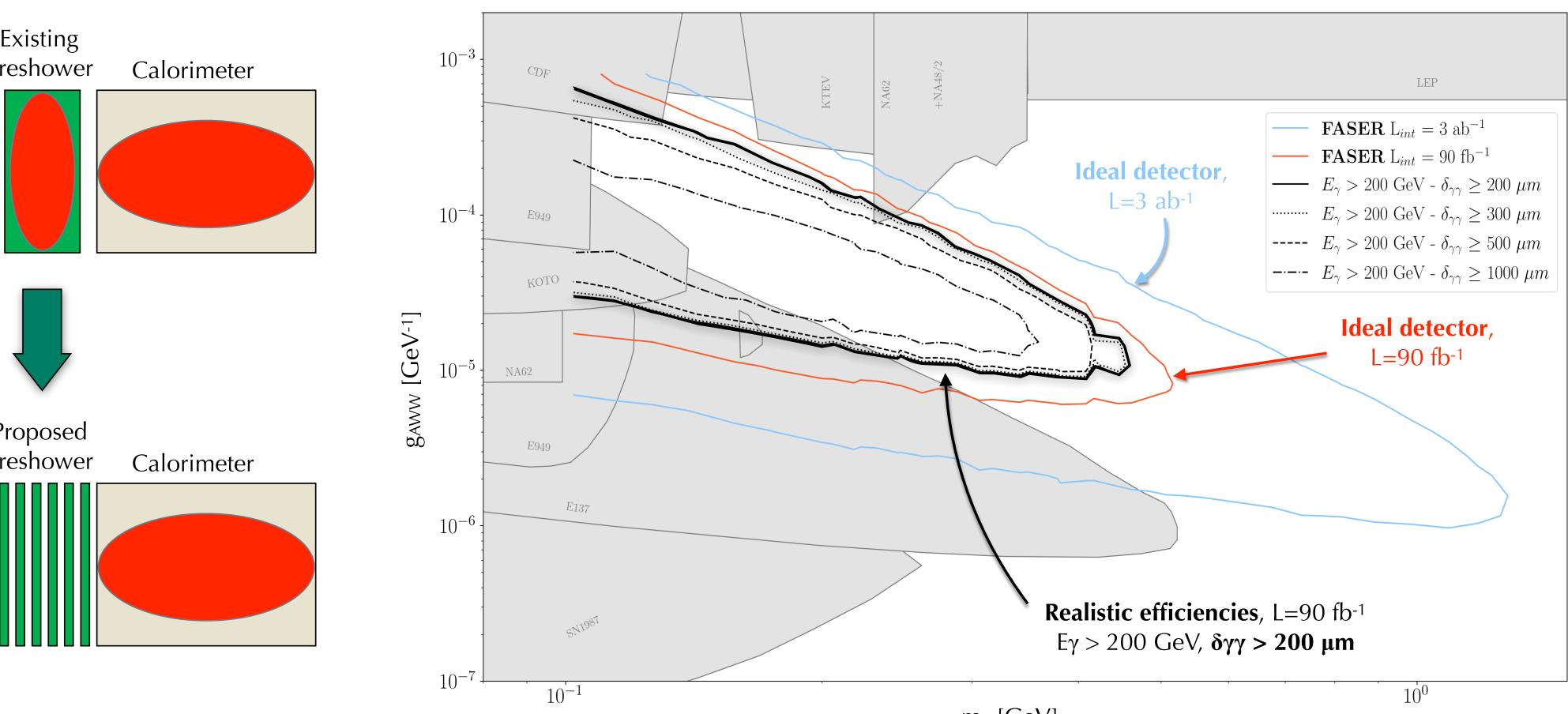

## A new preshower detector is being developed for the FASER experiment at the LHC

- enabling discrimination of ultra-collimated multi-TeV diphoton events from LLP decays

- chosen technology: SiGe MAPS designed and developed at UniGe =

- => targeting installation in 2024, for data taking during LHC Run 3

## **Pre-production chips received in June 2022, tests ongoing**

- => I-V characteristics OK up to 200 V, charge measurement and readout also OK

- possible improvements (e.g. TOT mismatch) individuated and planned

- further tests on single chips and first assembled modules currently ongoing

## Submission of final chip design in May 2023

## Spares

The development and construction of the W-Si pre-shower of the FASER experiment was funded by the Swiss National Science Foundation (SNSF) under the FLARE grant 20FL21-201474 at the University of Geneva. Additional financial contributions from KEK, Kyushu University, Mainz University, Tsinghua University and the Heising-Simons Foundation are also acknowledged.

m<sub>a</sub> [GeV]

## **CERN SPS Test Beam: Simulation Vs Data**

**Stefano Zambito** | Université de

All front-end system in Pixel Driver in Pixel, discriminator outside

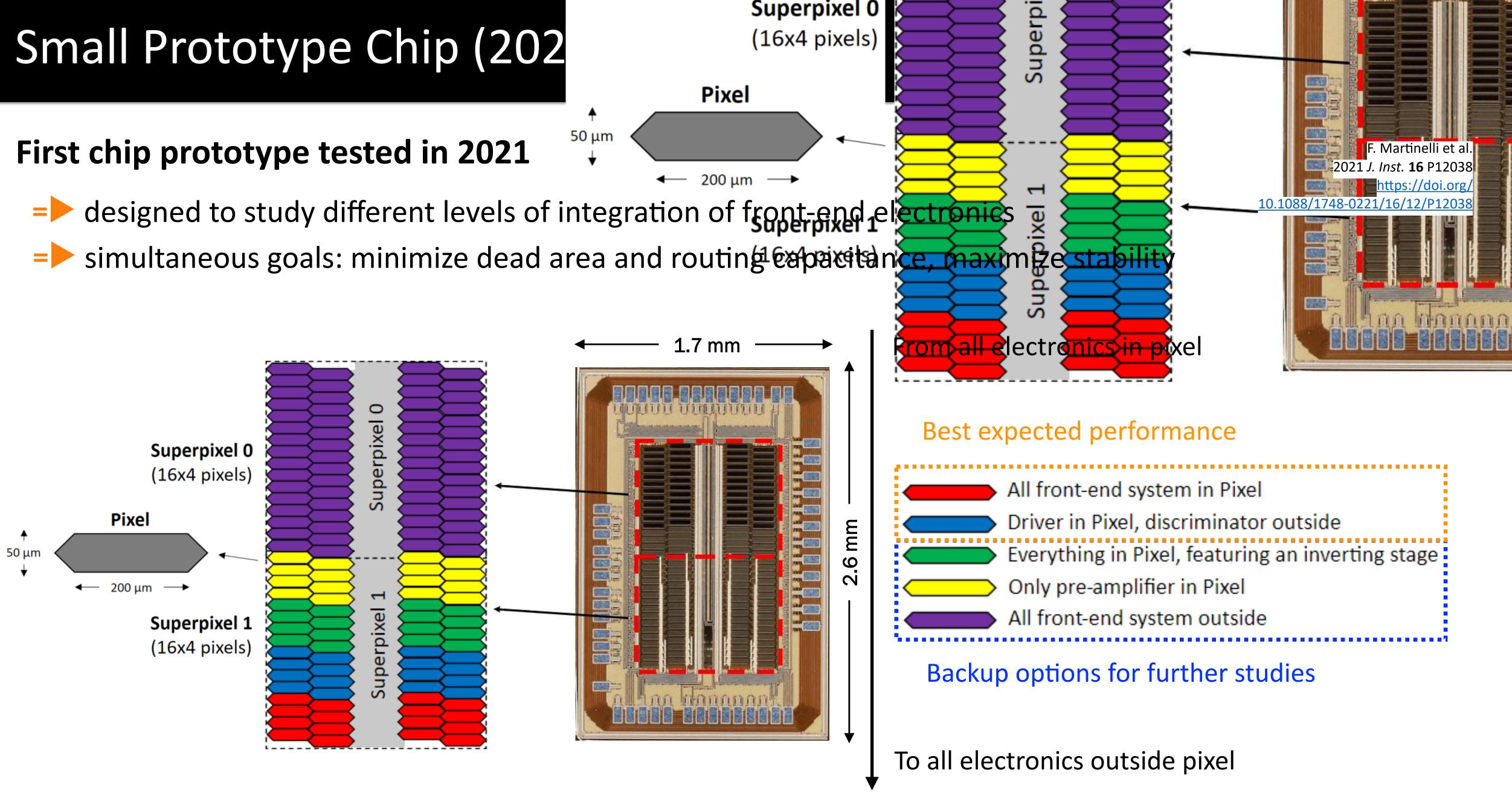

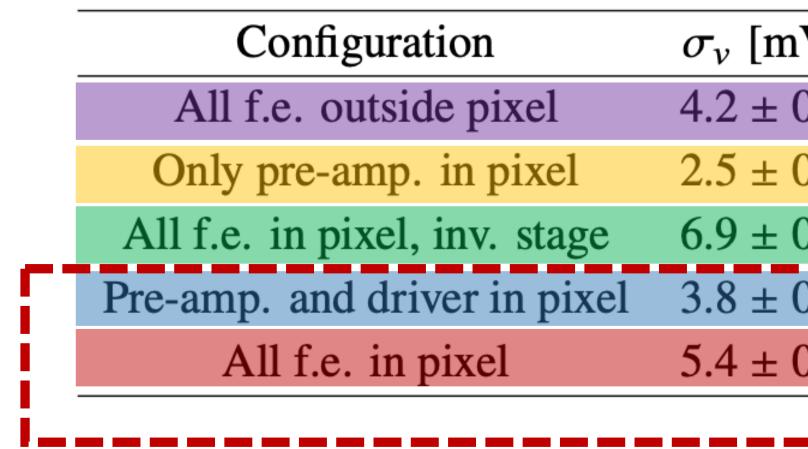

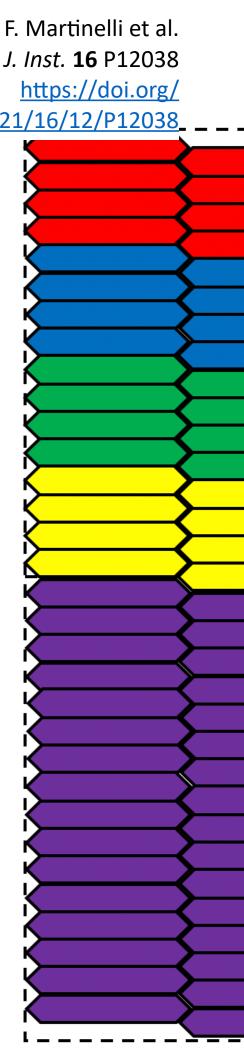

# Small Prototype Chip (2021)

## First chip prototype tested in 2021

designed to study different levels of integration of front-end electronics = simultaneous goals: minimize dead area and routing capacitance, maximize stability =

Last two configurations are good compromise between *compactness* and *performance*: adopted for pre-production prototype

**Stefano Zambito** | *Université de Genève*

2021 J. Inst. 16 P12038 10.1088/1748-0221/16/12/P12038

|     |                 |                              |                        | _ |

|-----|-----------------|------------------------------|------------------------|---|

| V]  | $G_c$ [mV/fC]   | <i>ENC</i> [e <sup>-</sup> ] | $\sigma_{V_{th}}$ [mV] | _ |

| 0.2 | $159 \pm 1.0$   | $165 \pm 9$                  | 32.3                   | - |

| 0.1 | $96.8 \pm 0.5$  | 161 ± 9                      | 26.9                   |   |

| 0.5 | $179 \pm 1.0$   | $241 \pm 19$                 | 30.8                   |   |

| 0.2 | $133.7 \pm 0.6$ | 178 ± 9                      | 23.4                   |   |

| 0.4 | $148 \pm 1.0$   | $228 \pm 20$                 | 27.1                   |   |

|     |                 |                              |                        | - |

# Monolithic Pixel ASIC: Charge Digitization & Readout

**Stefano Zambito** | *Université de Genève*

### Periphery of matrix with three super-columns (from pre-production ASIC)

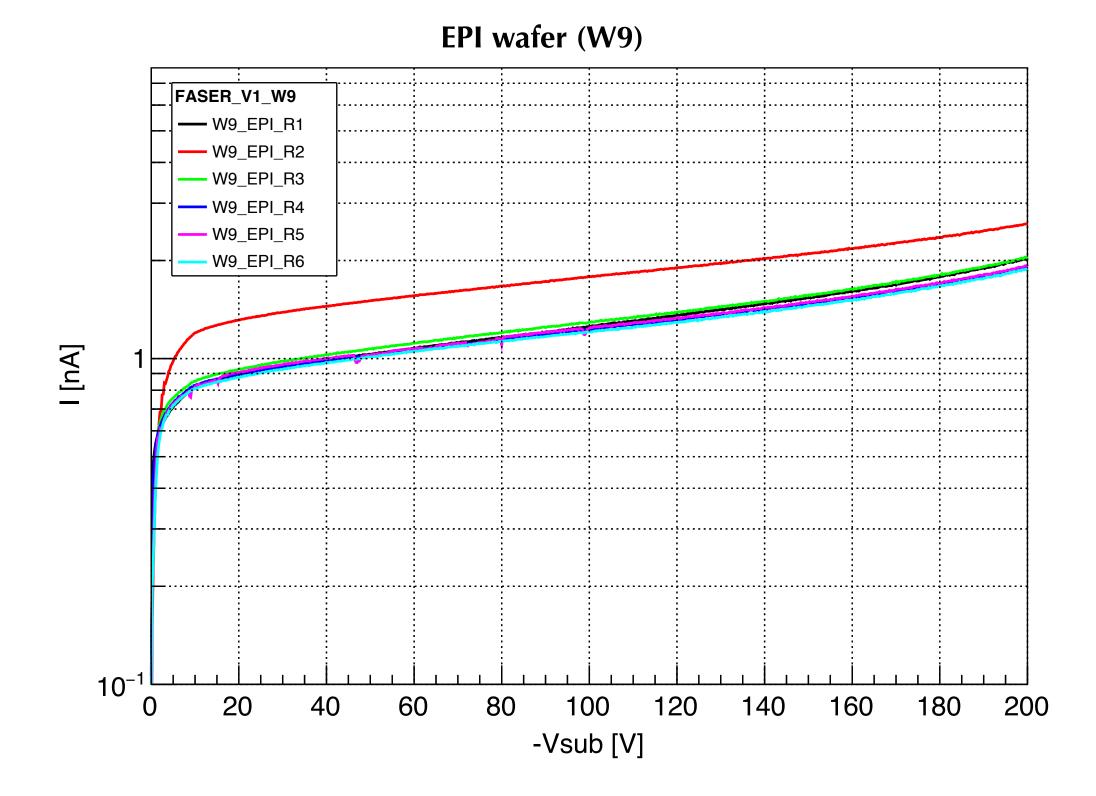

# Pre-production Chip: I-V Characteristic [II]

## Probed several chips from different wafers, at room temperature (22 °C)

- good I-V characteristics, similar results for standard and EPI wafers

- two chips going to early breakdown, under investigation (scratched by probe needle...)