## Performance of the RD50-MPW3 HV-CMOS Detector

Uwe Kraemer on behalf of RD50

01 Mar. 2023

#### **CERN-RD50** Collaboration

- CERN-RD50

- 66 institutes, more than 400 members

- Development of radiation hard semiconductor detectors

- CMOS working group

- 17 institutes

- Focus on radiation hard monolithic CMOS sensors

- ASIC design

- TCAD simulations

- DAQ development

- Chip characterization

Nik hef

2

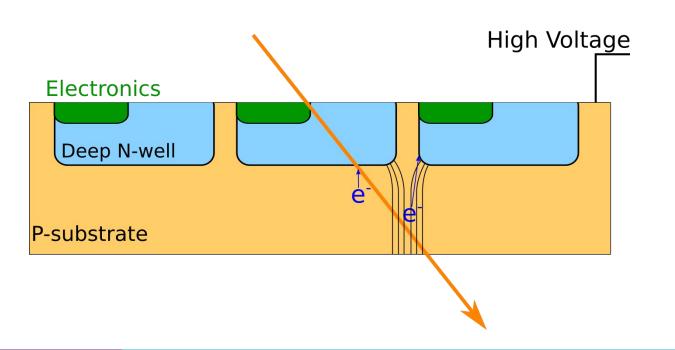

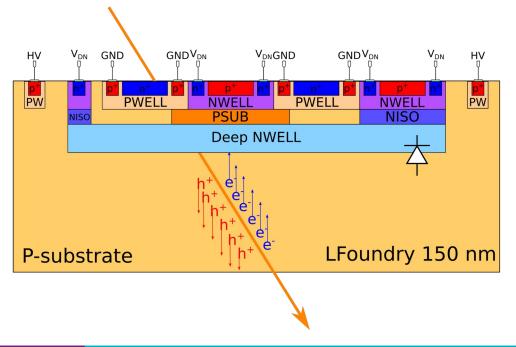

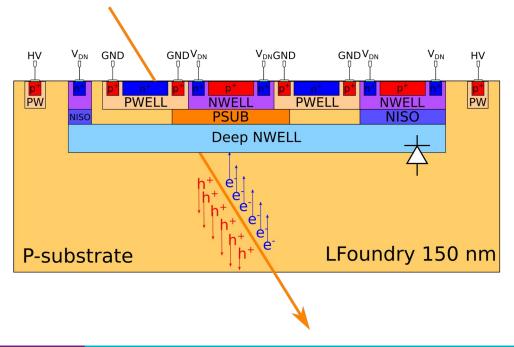

#### HV-CMOS for radiation hard depleted MAPS

- Electronics embedded in a large deep N-doped well to shield from high voltage

- Allows for application of  $\sim O(100 \text{ V})$  reverse bias

- Large depletion zone

- Fast charge collection

- $\rightarrow$  Less sensitive to trapping

- $\rightarrow$  Improved time resolution

**TREDI 2023**

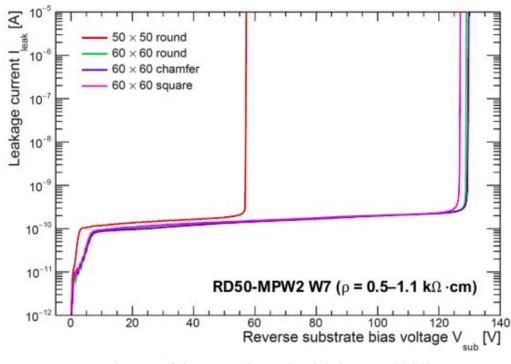

Fig.: IV of the MPW2 HV-CMOS (Vertex 2020)

Nik hef

01. Mar. 2023

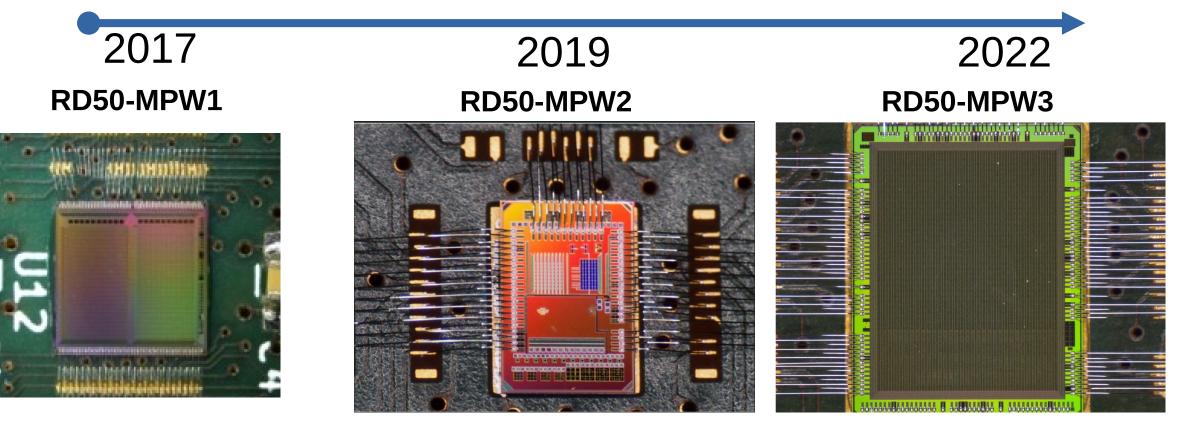

#### The RD50 DMAPS sensors

**TREDI 2023**

- Currently three iterations of Depleted Monolithic Active Pixel Sensors (DMAPS) as part of RD50 project

- All manufactured by LFoundry in 150 nm HV-CMOS process

- Recent prototype RD50-MPW3 was delivered in July 2022

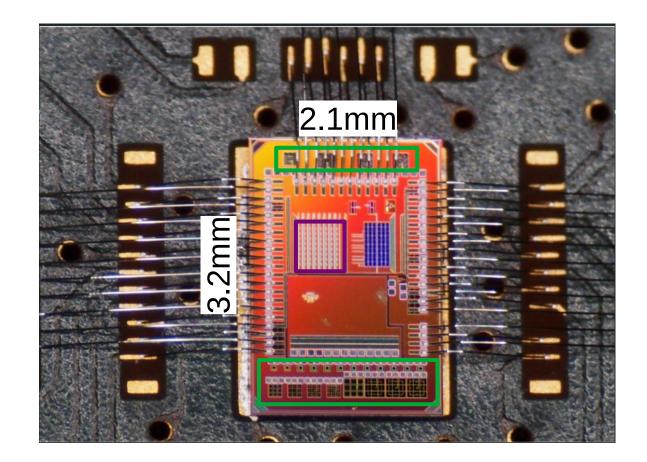

#### MPW2, the previous generation

- 8x8 pixel matrix

- Two pixel flavors

- Large variety of test structures

- Purely analog readout

- Depletion depths of  $\sim$ 190  $\mu$ m

- Produced in 1.9 kΩ cm and 3.0 kΩ cm resistivities

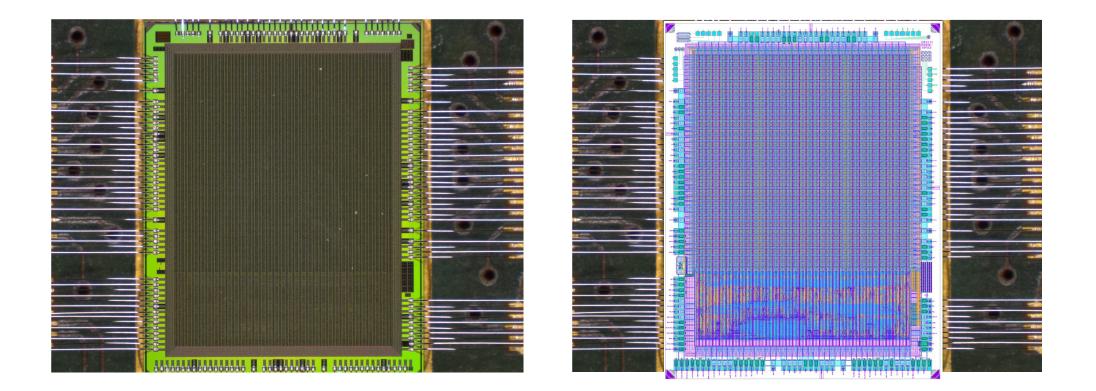

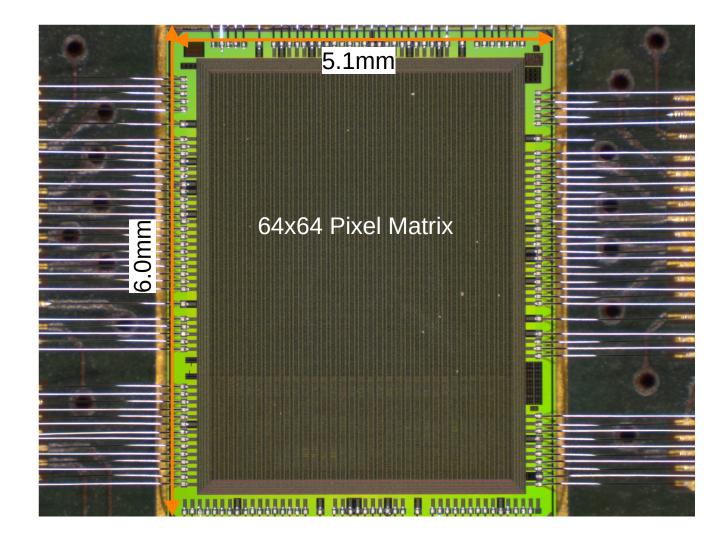

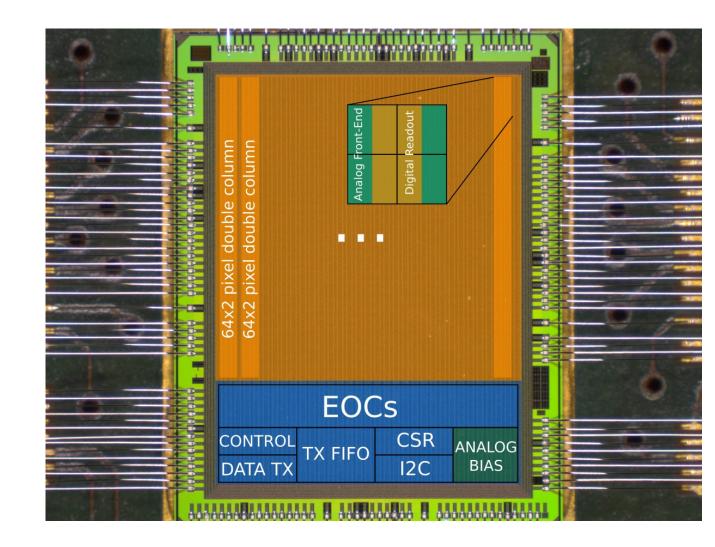

#### The RD50-MPW3

- CMOS chip with full analog and digital electronics

- 1.9 kΩ·cm and 3.0 kΩ·cm resistivities

- 320 MHz input clock

**TREDI 2023**

**Uwe Kraemer**

01. Mar. 2023

Nik hef

#### 6

#### The RD50-MPW3

- CMOS chip with full analog and digital electronics

- 1.9 kΩ·cm and 3.0 kΩ·cm resistivities

- 320 MHz input clock

7

**TREDI 2023**

**Uwe Kraemer**

01. Mar. 2023

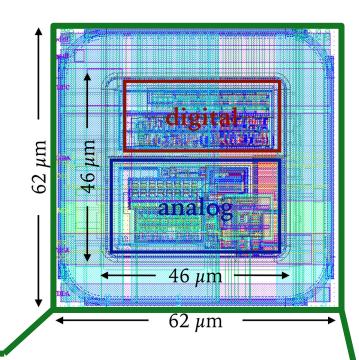

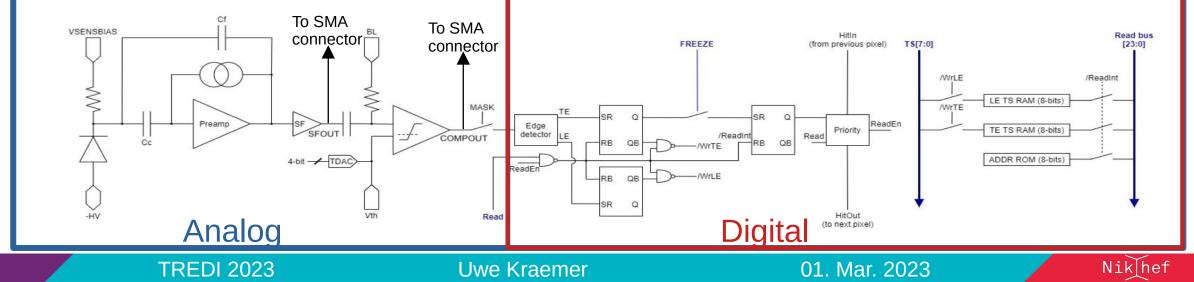

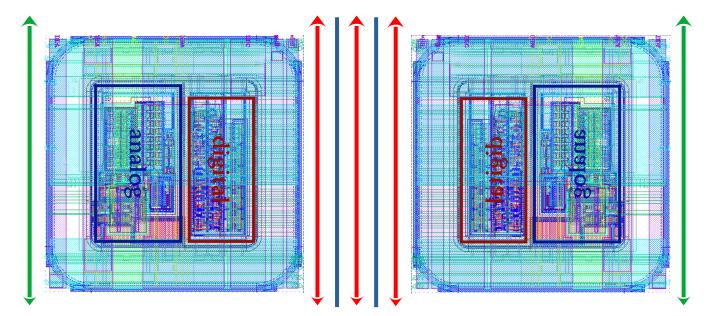

### The pixel logic

- Inherited analog pixel design from MPW2

- 4-bit trim DAC for threshold adjustment

- Continuous reset current readout

- Injection circuit for calibration

- Routing of analog pixels to SMA

- Digital logic newly integrated

- 8-bit timestamp of leading and trailing edge

- Double column drain readout and rolling shutter

#### Double column readout

- Pixels within double column are mirrored

- Double columns with digital signal line in between pixels

- Columns are separated by analog signal lines

- Voltage via mesh from all sides

- Analog signal line

- $\longleftrightarrow$  Digital signal line

- Shielding line

Nik[hef

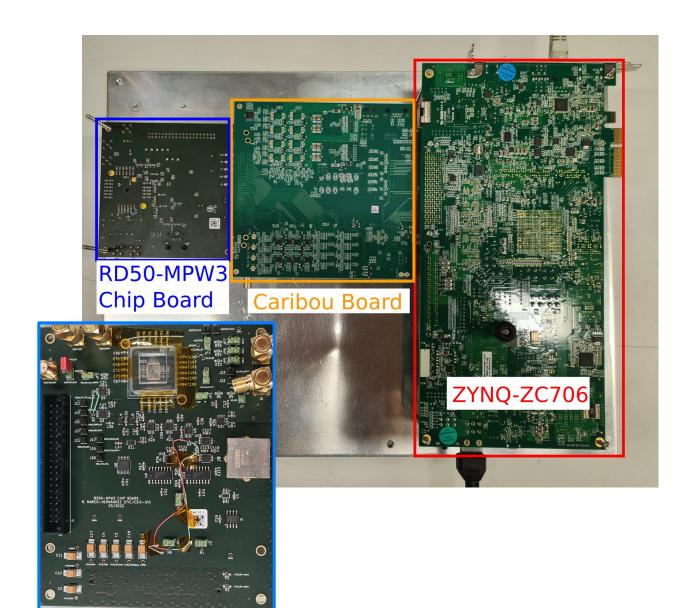

#### DAQ system

- Chip readout based on Caribou readout system

- ZYNQ-ZC706 with Yocto based linux

- Caribou for power distribution

- Custom chip carrier board

- Allows chaining of second chip board

- SMA connectors to probe analog outputs from circuitry

**TREDI 2023**

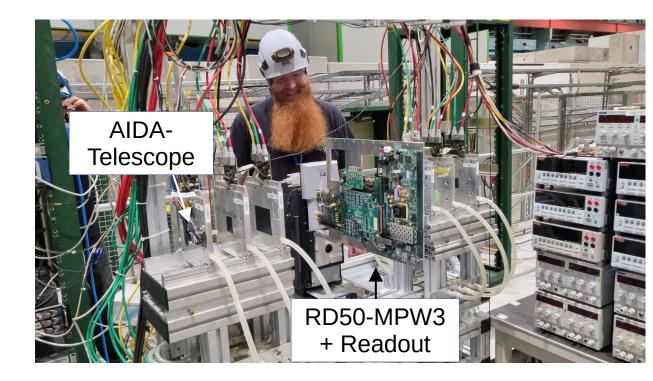

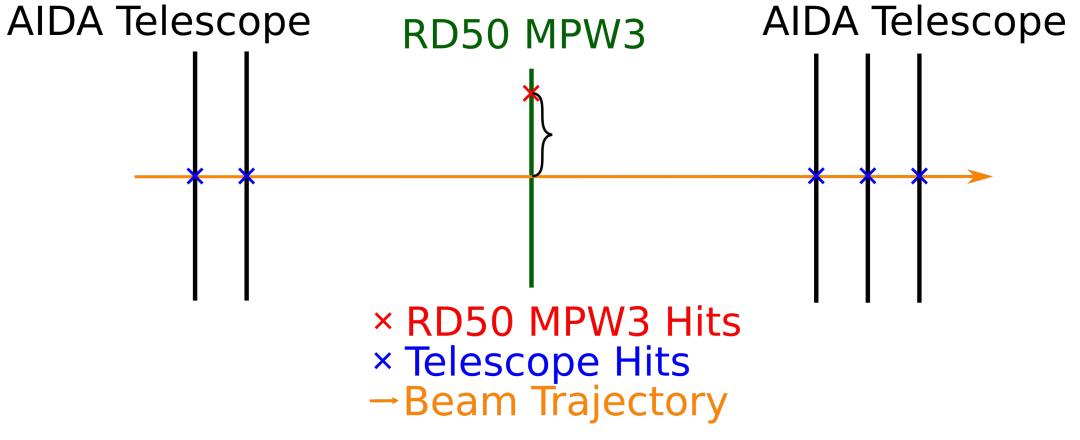

#### SPS test beam campaign

- SPS test beam week in October 2022

- Placed within SPS proton beam line

- EUDET-type telescope used as reference

- Based on Mimosa26

- $\bullet$  115  $\mu s$  rolling shutter frame readout

- No timestamps

- O(1  $\mu$ m) track resolution

- Synchronized data taking via AIDA TLU using EUDAQ2

- Analysis using Corryvreckan G

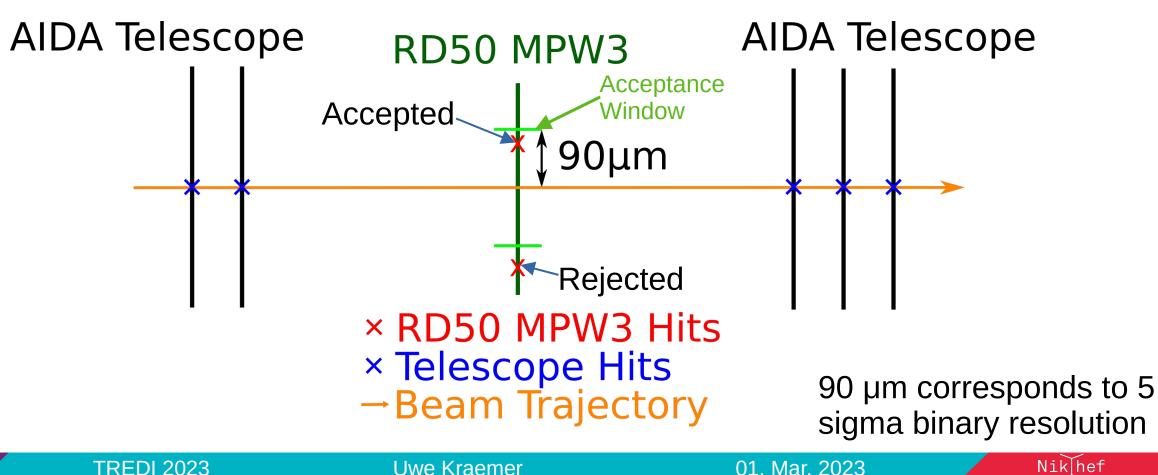

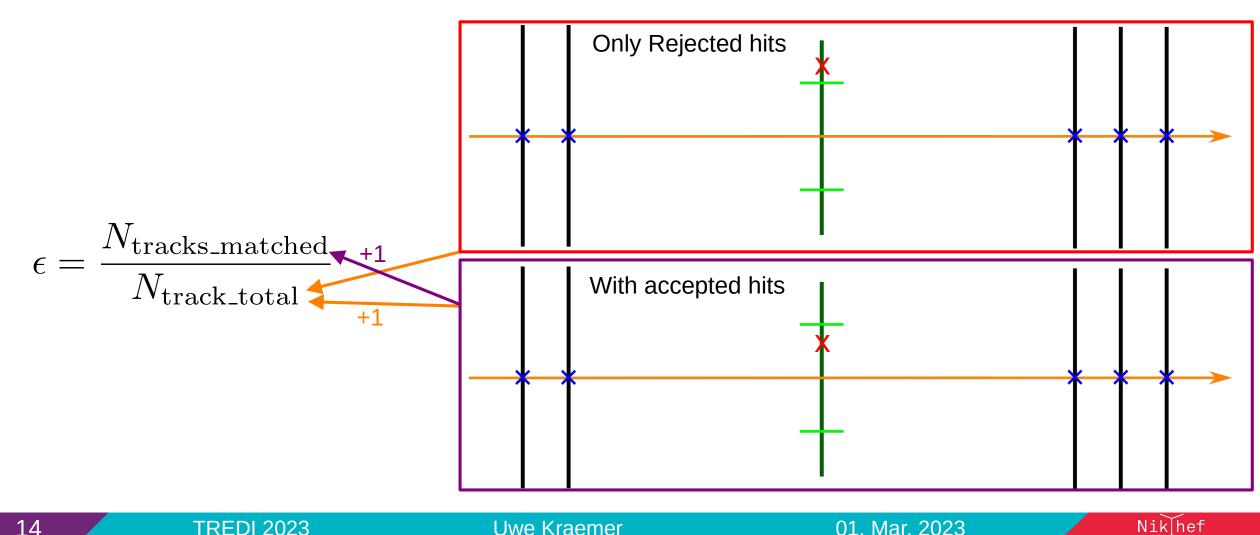

#### Spatial matching

- AIDA Telescope provides reference tracks

- Only accepted hits matched to tracks are shown in further results

- For in-pixel measurements the interpolated track position is used

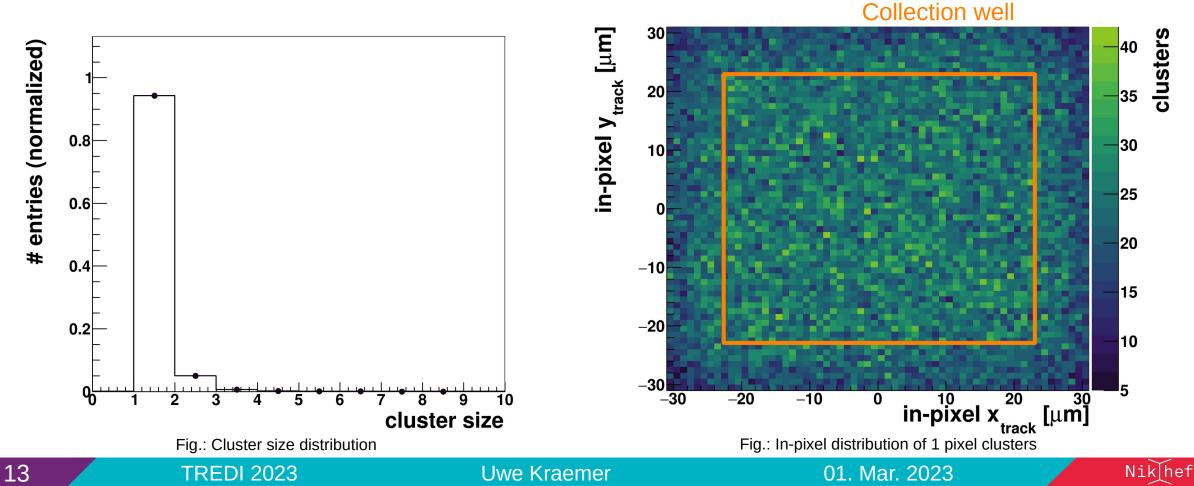

#### **Cluster size distribution**

- 94% 1 hit clusters

- Homogeneous distribution of 1 hit clusters within pixel

- Reduction towards the edges due to charge sharing

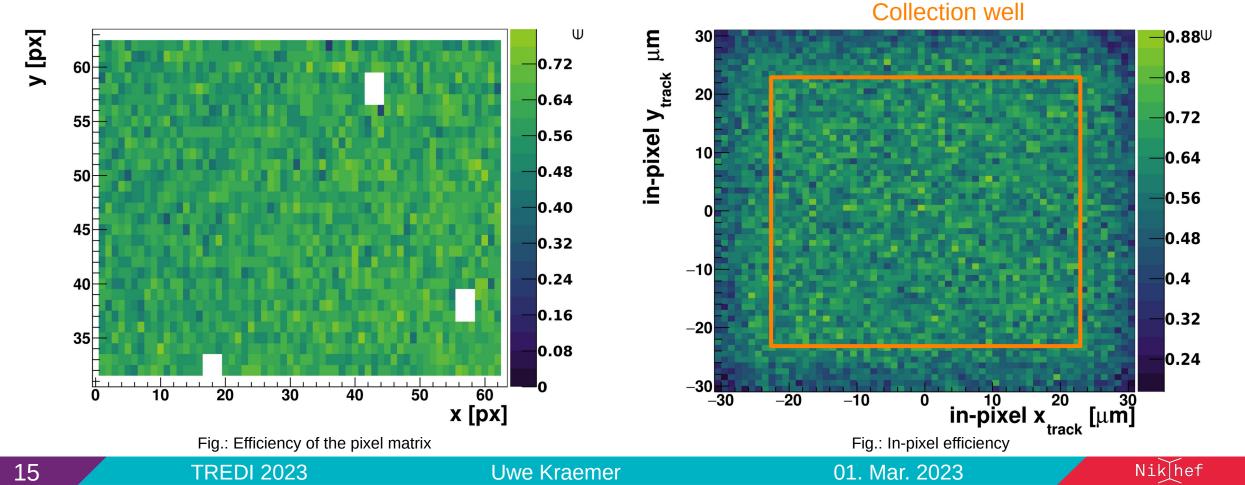

#### Chip and In-Pixel Efficiency

**TREDI 2023**

• Efficiency based on ratio of matched to total tracks

01. Mar. 2023

**Uwe Kraemer**

#### Chip and In-Pixel Efficiency

- Average efficiency of active sensor of 60%

- Efficiency hindered by threshold

- Set at 1/3 MIP MPV for 190  $\mu m$  depletion depth

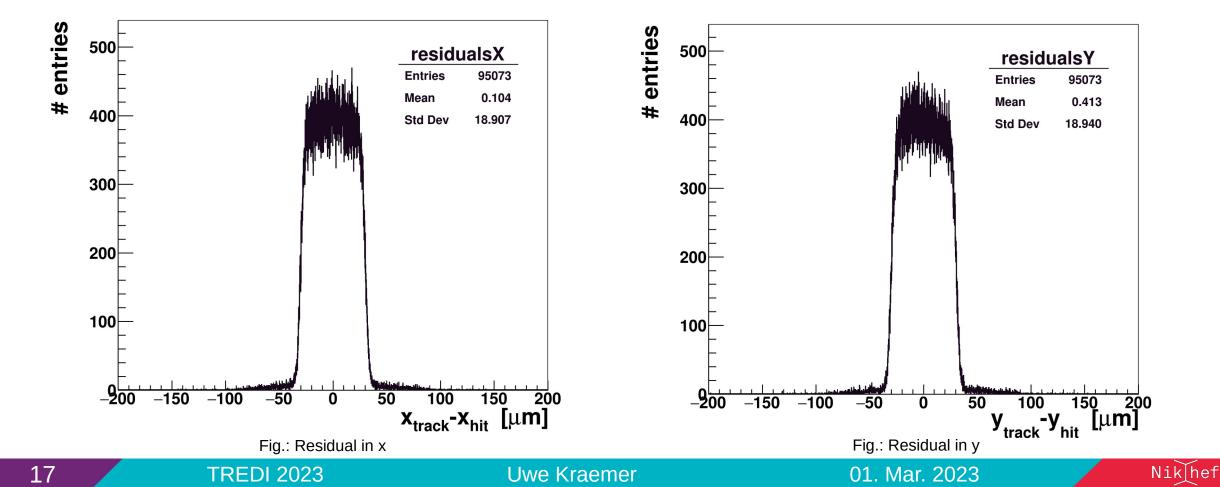

#### **Spatial Resolution**

- Residual between:

- interpolated track position

- measured pixel hit location

#### **Spatial Resolution**

• Low double hit clusters results in almost binary distribution

$$\sigma_{\rm meas} = 18 \mu {\rm m} \approx \frac{62 \mu {\rm m}}{\sqrt{12}} = \sigma_{\rm binary}$$

#### Summary

- New RD50-MPW3 chip produced by LFoundry

- Larger matrix

- Full digital and analog readout

- Different resistivities

- System was tested at the CERN SPS beamline and operated with EUDET-type telescope

- Completed full test beam campaign and performed analysis of combined data

- Chip performance acceptable considering sub-optimal settings

- Gained valuable insight for system operation for both laboratory and future testbeam measurements.

#### Outlook

- Further tests of operation and improvements being worked on:

- $\rightarrow$  New firmware to increases overflow counter used for time synchronization

- $\rightarrow$  Threshold and noise optimizations

- $\rightarrow$  Ramping up lab measurements concerning analog and digital performance

- $\rightarrow$  First irradiated sensors expected in spring

- $\rightarrow\,$  Further test beam campaigns at the DESY II Test Beam Facility in July 2023 and CERN SPS in October 2023

# **Backup slides**

Nikhef

**TREDI 2023**

2

**Uwe Kraemer**

01. Mar. 2023

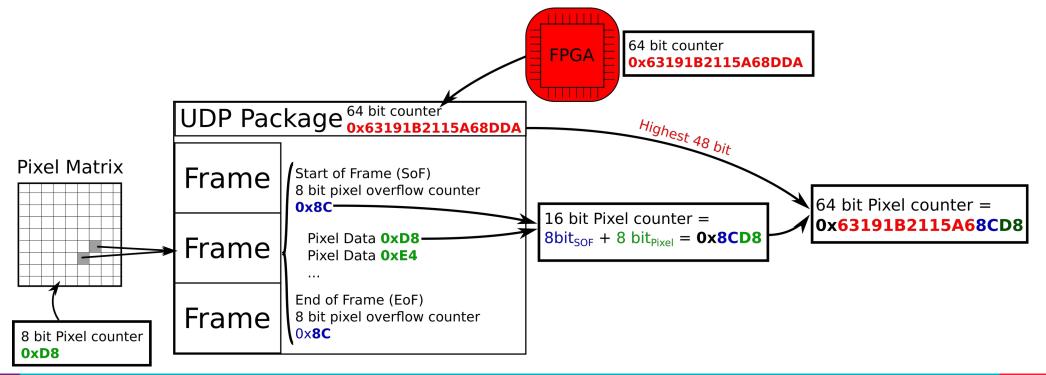

#### Test beam data synchronization

• Timestamp of the system given by:

**TREDI 2023**

- in-Pixel logic (8 bit)

- Data package overflow counter (8 bit)

- Overflows every 3.27 ms (accounted for in analysis)

- $\rightarrow\,$  Combined with 64 bit counter from FPGA for global timestamp

**Uwe Kraemer**

Nik hef

01. Mar. 2023

#### **Testbeam Data Synchronization**

- Time shift can vary depending on number of overflows within UDP package

- Data can be shifted in multiples of the overflow to match with telescope

- Actual shift per pixel is unknown requires external data handling

| UDP Package <sup>64 bit counter</sup><br>0x63191B2115A68DDA |                                                                                        |                                                                                                                            |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Frame                                                       | Start of Frame (SoF) 0xFF                                                              |                                                                                                                            |

| Frame                                                       | Pixel Data <b>0xE8</b><br>Pixel Data <b>0x44</b><br><br>End of Frame (EoF) <b>0xFF</b> | Overflow Within UDP package<br>Need to adjust 17th bit<br>(and possible higher for multiple OF)<br>50ns * 2^16 = 3.2768 ms |

| Frame                                                       | Start of Frame (SoF) 0x0A<br>Pixel Data 0xD8<br>Pixel Data 0xE4<br>                    |                                                                                                                            |

| Frame                                                       | End of Frame (EoF) 0x0A                                                                |                                                                                                                            |

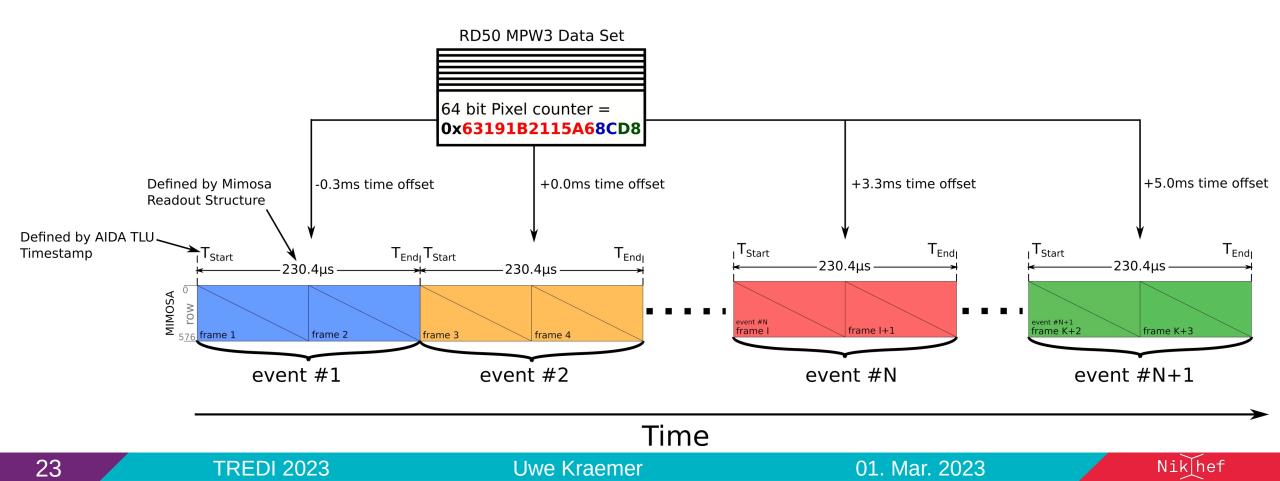

#### Test beam data Synchronization

Global pixel timestamp is used to assign to the correct "event" which is defined by the AIDA TLU + Mimosa Telescope

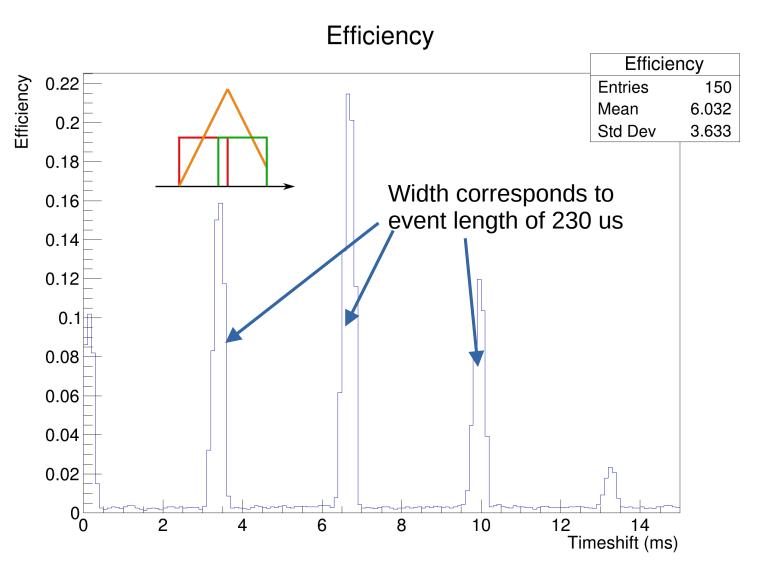

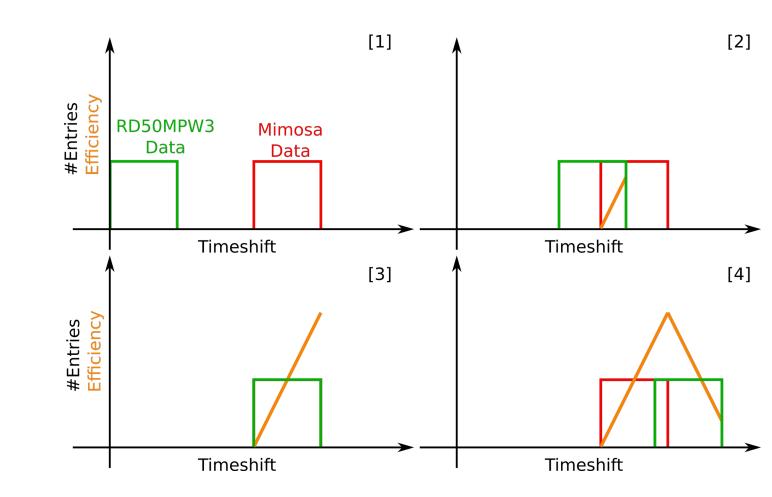

#### Timeshift scan

- Scanned over a larger range with newly implemented buffer to:

- see what the sum of the results are

- how many events can be matched beyond 3.3 ms

- determine if there is another offset except for the 16 bit overflow

- In effect a convolution of the two data distributions

#### Data combination

- Found clear correlation with the 16 bit TS overflow (3.27 ms)

- Slight offset O(100us) for first peak indicates some inherent offset that needs to be taking into account for the data

- Otherwise just random correlations with very minor contributions

- Total efficiency of the sensor = Sum of the peaks - N\*baseline

- ≈ 60%

- Issue is resolved in new firmware with 48 bit overflow counter