Jens Sören Lange (*Justus-Liebig-Universität Giessen*) EURIZON School, Wuppertal, 19.07.2023

European network for developing new horizons for RIs NEUE WEGE. SEIT 1607.

JUSTUS-LIEBIG-

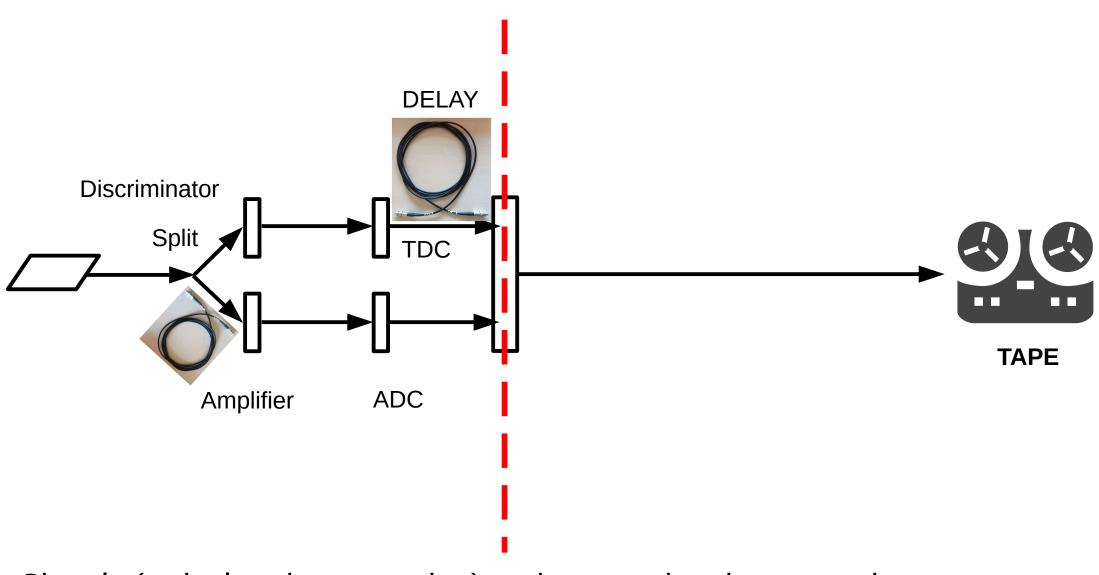

### Delay

- Part I

- The basics:

frontend, backend, realtime, discriminator, ADC, TDC, eventbuilder, trigger, latency

- Example of producing a frontend board

- Part II

- Example for an experiment with many TDCs calculate the data bandwidth

- Example for an experiment with many ADCs calculate the bandwidth

- Introduction to FPGAs

- Data links (1G, 5G, ...?)

non-CERN experiments

We often say "Realtime DAQ", but what is ,,REALTIME" ?

• Definition:

reply to an INTERRUPT within  $n \mu s$ (typically n=10, for some systems more strict e.g. airbag in a car)

• Example code:

measure the reply time to an interrupt (CTRL-C) on this computer

```

soeren@soeren-galaxy:~/SOEREN/soeren BASE/CODE/TUTORIAL/TI/interrupt$ more signal time.c

#include "stdio.h"

#include "signal.h"

#include "stdio.h"

#include "math.h"

#include "time.h"

struct sigaction naction;

clock t t 1;

clock t t 2;

void signal received(int test)

t_2 = clock();

double time taken = ((double)(t 2-t 1))/CLOCKS PER SEC;

printf("Time for catching CTRL-C %f %f %f \n", (double)t 1, (double)t 2, time taken);

return;

int main()

while(1) {

t 1 = clock();

sigaction(SIGINT, (struct sigaction *)0, &naction);

naction.sa handler = signal received;

sigaction(SIGINT, &naction, (struct sigaction *)0);

}

return 0;

```

# Measure the time of ,,catching' an interrupt on a PC

| <pre>soeren@soeren-galaxy:~/SOEREN/soeren_BASE/CODE/TUTORIAL/TI/interrupt\$ gcc signal_time.c</pre> |

|-----------------------------------------------------------------------------------------------------|

| <pre>soeren@soeren-galaxy:~/SOEREN/soeren_BASE/CODE/TUTORIAL/TI/interrupt\$ ./a.out</pre>           |

| ^CTime for catching CTRL-C 1546174.000000 1546179.000000 0.000005                                   |

| ^CTime for catching CTRL-C 1901502.000000 1901507.000000 0.000005                                   |

| ^CTime for catching CTRL-C 2139984.000000 2139991.000000 0.000007                                   |

| ^CTime for catching CTRL-C 2334249.000000 2334255.000000 0.000006                                   |

| ^CTime for catching CTRL-C 2556517.000000 2556523.000000 0.000006                                   |

| ^CTime for catching CTRL-C 2813186.000000 2813192.000000 0.000006                                   |

| ^CTime for catching CTRL-C 3011919.000000 3011925.000000 0.000006                                   |

| ^CTime for catching CTRL-C 3174031.000000 3174038.000000 0.000007                                   |

| ^CTime for catching CTRL-C 3345678.000000 3345683.000000 0.000005                                   |

| ^CTime for catching CTRL-C 3561479.000000 3561486.000000 0.000007                                   |

| ^CTime for catching CTRL-C 3755866.000000 3755871.000000 0.000005                                   |

| ^CTime for catching CTRL-C 3944870.000000 3944877.000000 0.000007                                   |

| ^CTime for catching CTRL-C 4100340.000000 4100346.000000 0.000006                                   |

| ^CTime for catching CTRL-C 4300448.000000 4300455.000000 0.000007                                   |

| ^CTime for catching CTRL-C 4483679.000000 4483685.000000 0.000006                                   |

| ^CTime for catching CTRL-C 4677947.000000 4677952.000000 0.000005                                   |

| ^CTime for catching CTRL-C 4855793.000000 4855799.000000 0.000006                                   |

| ^CTime for catching CTRL-C 5033488.000000 5033494.000000 0.000006                                   |

| ^CTime for catching CTRL-C 5238807.000000 5238813.000000 0.000006                                   |

| ^CTime for catching CTRL-C 5449759.000000 5449765.000000 0.000006                                   |

| ^CTime for catching CTRL-C 5643917.000000 5643924.000000 0.000007                                   |

| ^CTime for catching CTRL-C 5821592.000000 5821598.000000 0.000006                                   |

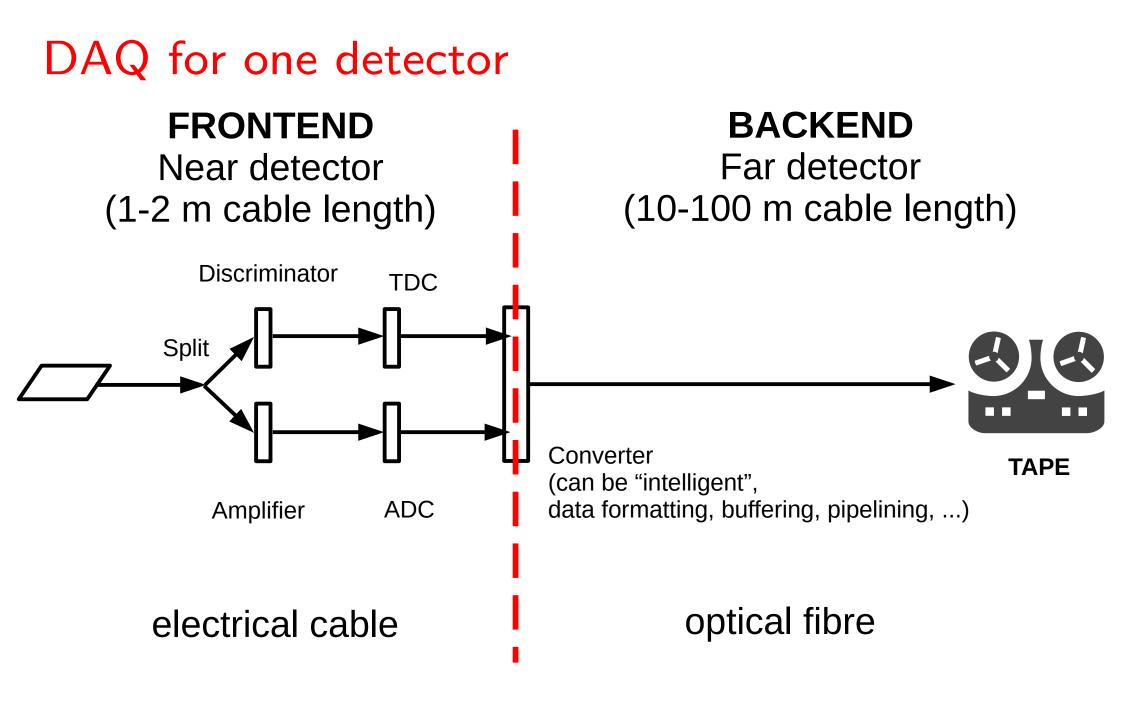

### DAQ for one detector

Signals (arrival and propagation) and processing times may have different timings and may need **DELAY**

### Delay

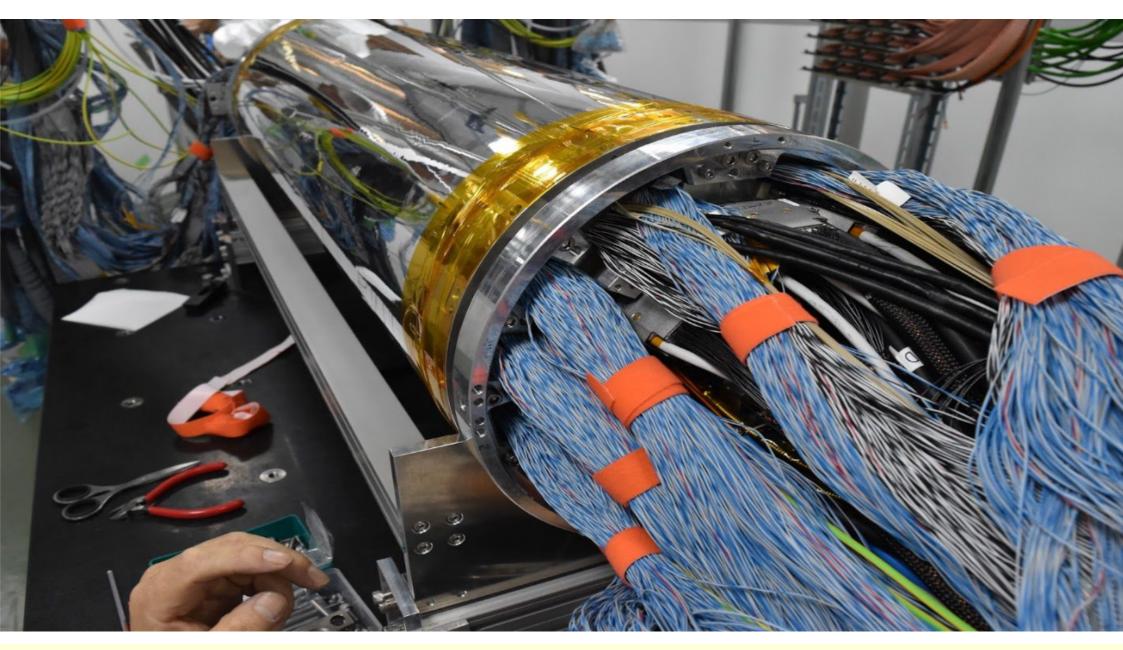

- There are fast detectors (e.g. 1 ns), there are slow detectors (e.g. 100 ns)

- There are fast modules, there are slow modules

- Needs compensation (signals should arrive synchronously)

- Easiest and cheapest solution: cable!

- Speed of light is ~30 cm/ns, speed of light in the cable is about ~20 cm/ns

- Cables can be purchased not as "length 40 cm" but as "length 2 ns", which includes any delay in the connectors (guaranteed by the company)

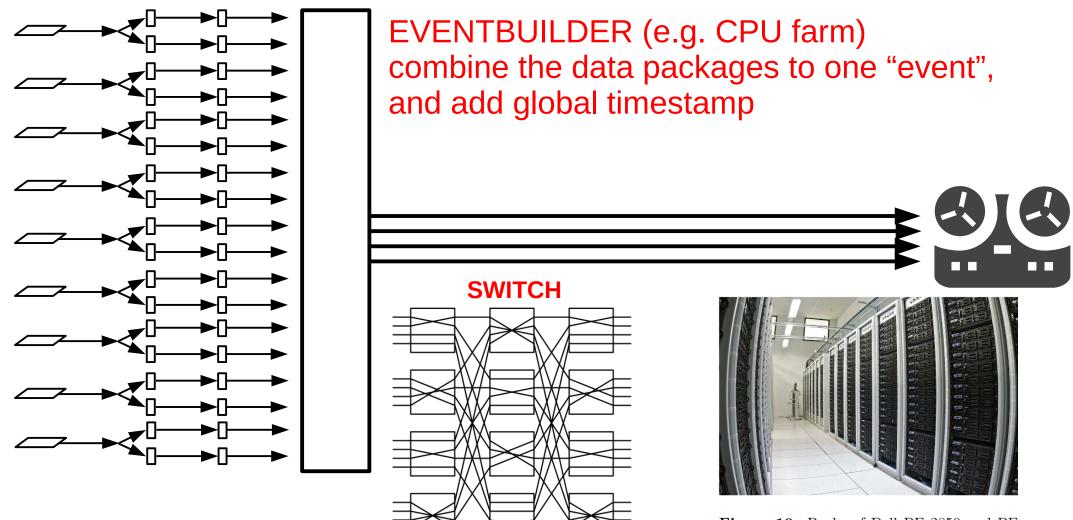

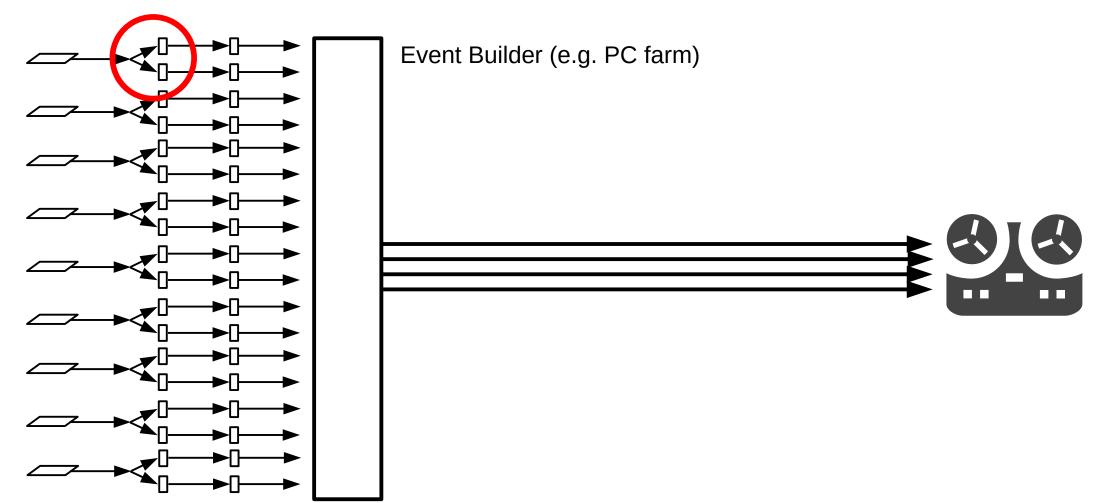

### DAQ for many detectors

Figure 10. Racks of Dell PE 2850 and PE 1950 computers used for the event building and for the high-level triggers.

https://www.wikiwand.com/en/Nonblocking\_minimal\_spanning\_switch#Media/ File:Minimal\_spanning\_switch\_4\_4\_4.svg

G. Bauer et al. (CMS), Journal of Physics: Conf. Ser. 219 (2010) 022038

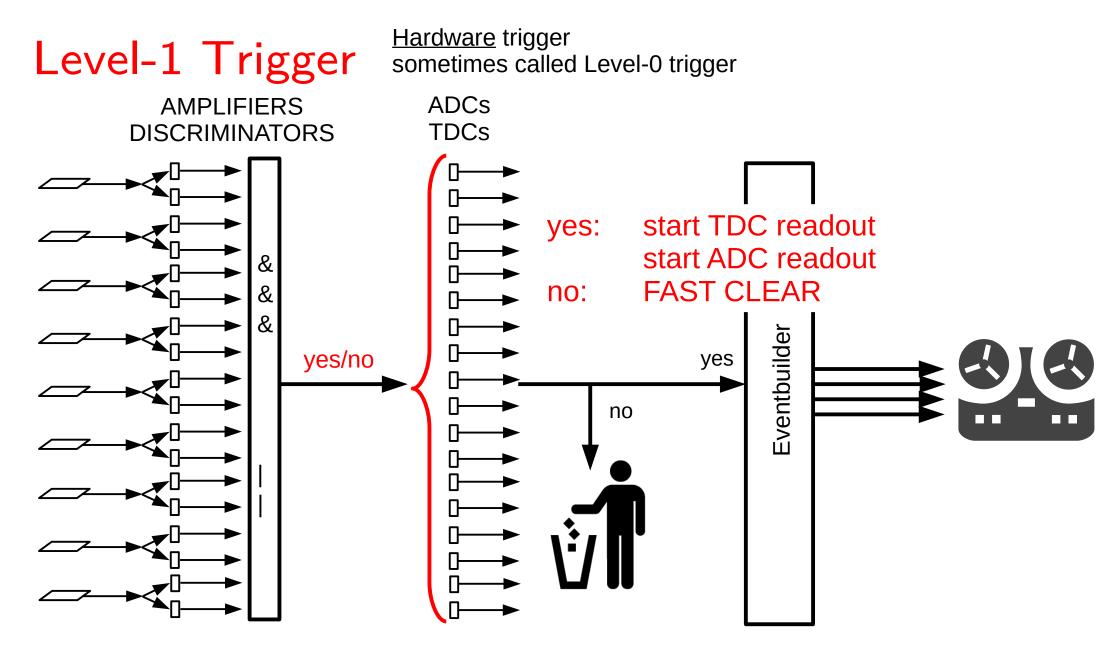

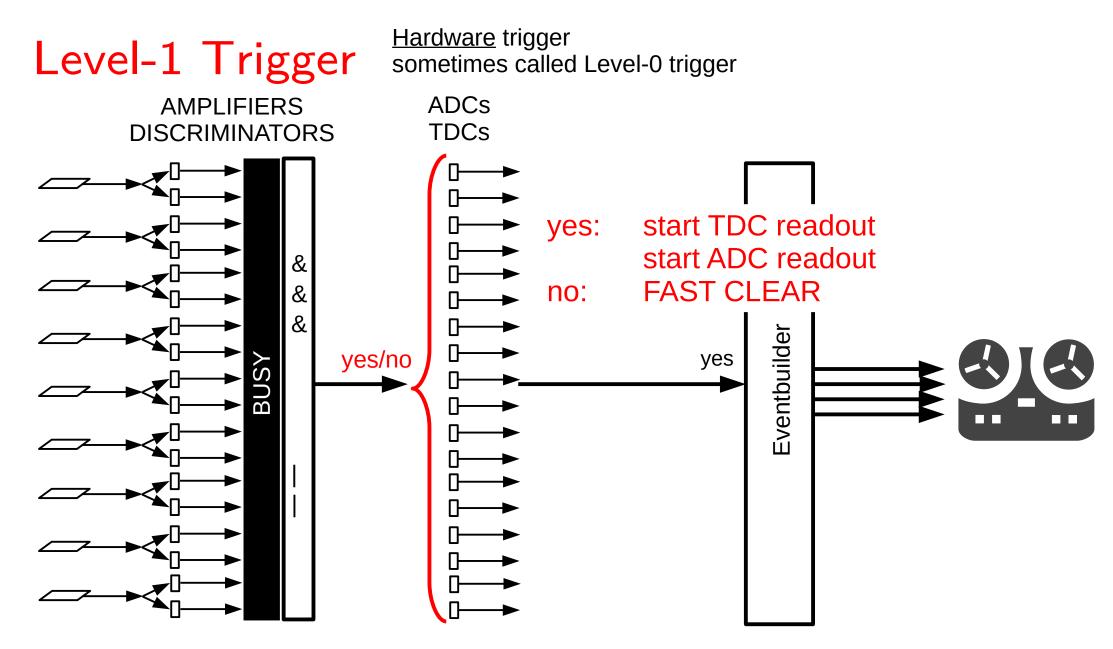

Logical operations (AND, OR) can be quite complex (e.g. detector hits combined to clusters and tracks, and counted) trigger rate can be ~1 kHz to ~1 MHz

Logical operations (AND, OR) can be quite complex (e.g. detector hits combined to clusters and tracks, and counted) trigger rate can be ~1 kHz to ~1 MHz

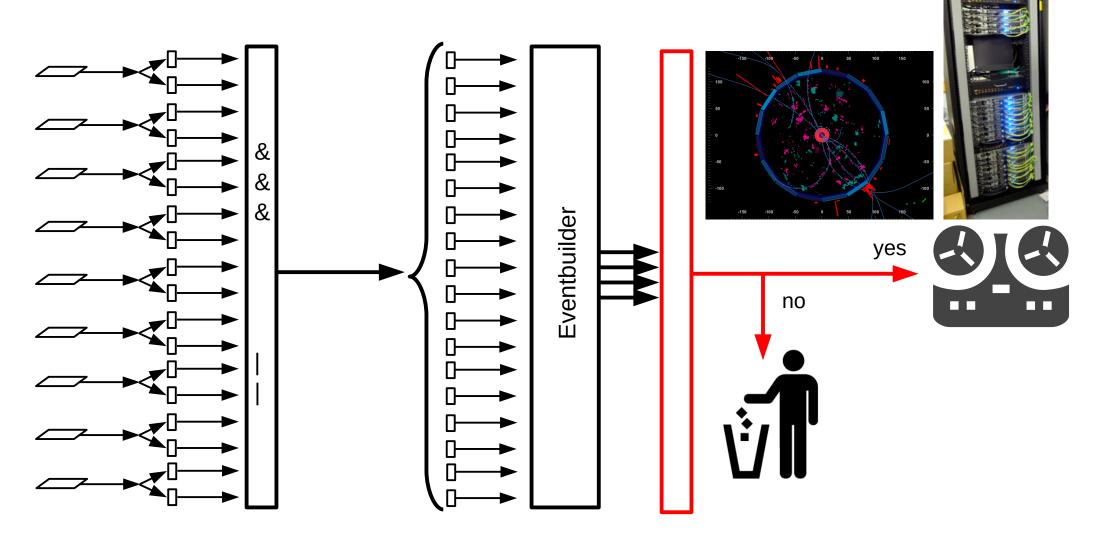

### High Level Trigger So

<u>Software</u> trigger sometimes called Level-3 trigger

## Full event reconstruction (invariant mass, topology, missing energy, ...)

### Trigger and DAQ numbers at CERN

| ATLAS | No.Levels | S    | <b>Level-0,1,2</b><br>Rate (Hz) | <b>Event</b><br>Size (Byte)            | <b>Readout</b><br>Bandw.(GB/s) | HLT Out<br>MB/s (Event/s)                                       |

|-------|-----------|------|---------------------------------|----------------------------------------|--------------------------------|-----------------------------------------------------------------|

| CMS   | 3         |      | 10⁵<br>3x10³                    | 1.5x10 <sup>6</sup>                    | 4.5                            | <b>300</b> (2x10 <sup>2</sup> )                                 |

|       | 2         | LV-1 | <b>10</b> <sup>5</sup>          | <b>10</b> <sup>6</sup>                 | 100                            | <b>100</b> (10 <sup>2</sup> )                                   |

| LHCb  | 2         | LV-0 | <b>10</b> <sup>6</sup>          | 3x10⁴                                  | 30                             | <b>40</b> (2x10 <sup>2</sup> )                                  |

|       | 4         |      | 500<br>10 <sup>3</sup>          | 5x10 <sup>7</sup><br>2x10 <sup>6</sup> | 25                             | <b>1250</b> (10 <sup>2</sup> )<br><b>200</b> (10 <sup>2</sup> ) |

#### C. Schwick (CERN/CMS), DESY Seminar, 17.10.2007

Belle II (10<sup>4</sup> Events/s)

Lange | Lecture TDAQ | EURIZON Wuppertal | 07/2023

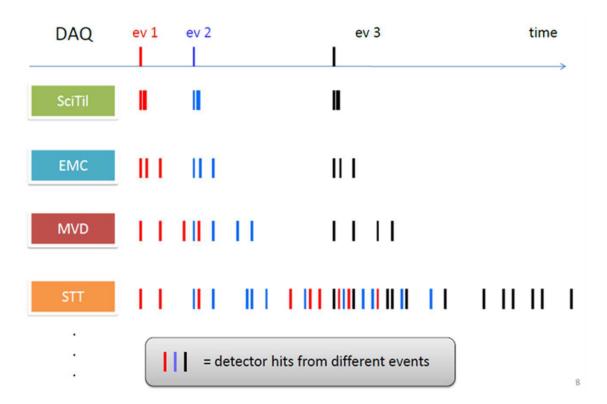

### What is ,,triggerless" DAQ?

There is a new generation of experiments, in which no Level-1 trigger is issued. The frontend is pushing all data ,,self-triggered''.

Examples: LHCb, DUNE, Panda (see below).

Data are ordered and combined based upon time stamps.

S. Spataro, Journal of Physics: Conference Series 396 (2012) 022048

### What is "latency" ?

The time to form the trigger decision and send it to the TDCs and ADCs.

Example: trigger rate 10 kHz

#### 0.1 ms

i.e. average time distance between 2 triggers arriving.

Latency can be larger, e.g. 1 ms !

i.e. average time in which the trigger is working on the frontend data.

#### Example STAR Experiment

|         | au                  |

|---------|---------------------|

| Level-0 | $1.5~\mu { m s}$    |

| Level-1 | $100~\mu{\rm s}$    |

| Level-2 | $5 \mathrm{ms}$     |

| Level-3 | $200 \mathrm{\ ms}$ |

### Data links

- Central components of every DAQ system, for <u>data transfer</u>

- <u>Electrical</u> links

- backplane (inside a crate)

- cables (twisted pair or shielded)

- <u>Optical</u> links

- fibres

### Cables and connectors

- Type I: Coaxial cables (with shielding)

- Type II: Differential cable, often "twisted pair"

- We say "50 Ohm cable"

- This is stable impedance up to high frequencies (e.g. 3 GHz).

RG58 cable with BNC adapters

S Fifteen Instruments

https://www.mcgillmicrowave.com/product/rg58/

### Twisted pair cable (Belle II Vertexdetector)

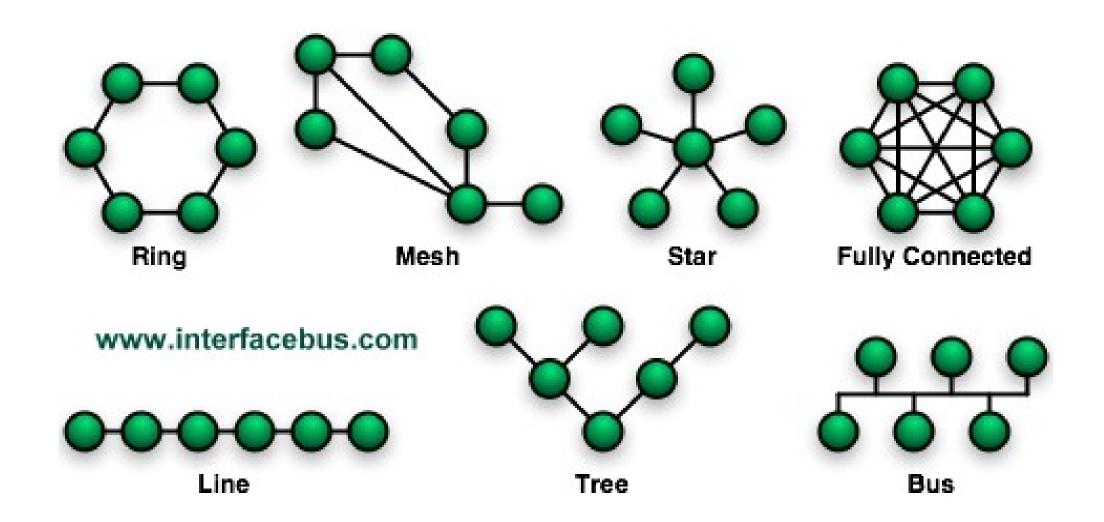

### Topologies of DAQ systems

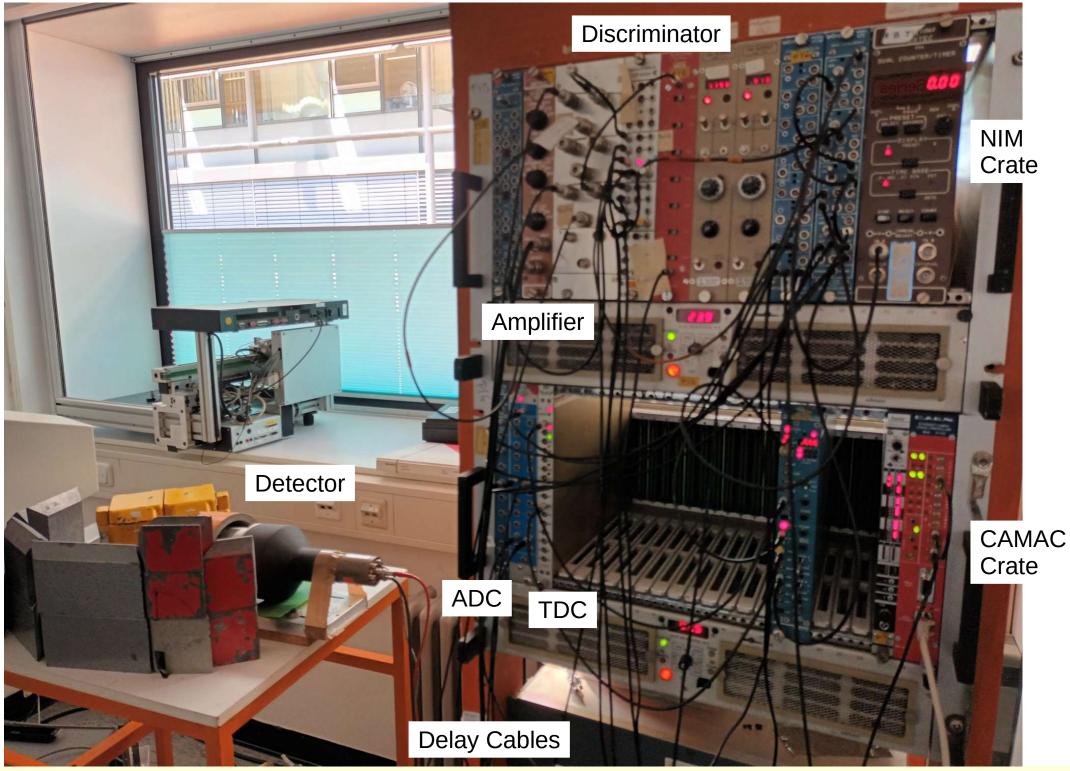

### Crates

#### wiener-d.com

#### **NIM Crates**

12 slots, unintelligent, e.g. for discriminators, amplifiers power on pins (e.g.  $\pm 12$  V)

#### CAMAC Crates

25 slots intelligent (data bus, CNAF) e.g. for TDC, ADC bandwidth 4 Mbytes/s

#### VME Crates

21 slots bandwidth 40 Mbytes/s 2 × 160 pins (many!) Parallel, asynchronous bus industrial standard (cheaper!)

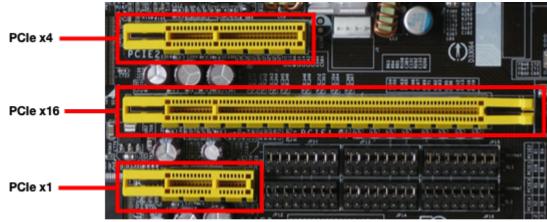

### PClexpress

- Crates are nowadays often slots in a PC

- Not a bus anymore, but a point-to-point link

- Data not transferred on parallel lines but on one or several serial <u>lanes</u> (serial here means:

- 1 byte is transmitted as 8 bits serial)

- Lane: one pair of differential lines per direction (low voltage differential signal)

- 250 MB/s (PCIe 1.0) data transfer rate per lane

- Devices (DAQ boards) support up to 32 lanes

Image: Thomas Ryan/IDG

pcwelt.de

Elektronik-Kompendium.de

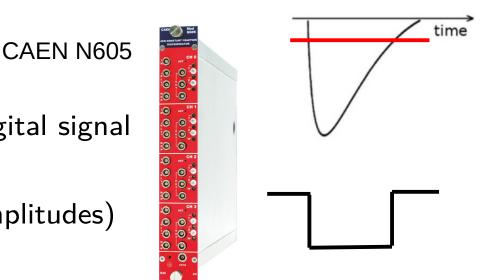

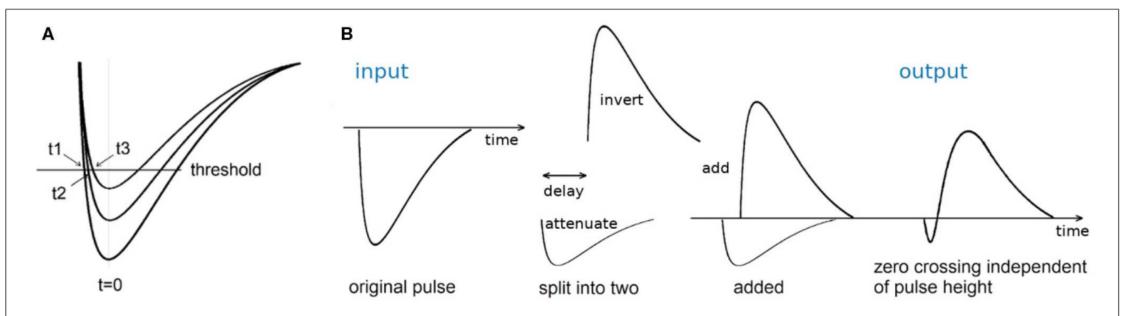

### Discriminator

- Transforming an analog signal into a digital signal

- Type I: Leading edge discriminator "walk" (different t<sub>START</sub> for different amplitudes)

- Type II: Constant fraction discriminator

**FIGURE 8 (A)** Schematic of leading edge discrimination. The fixed threshold times the pulses (all arriving at the same time t = 0) at different times t1, t2, and t3, depending on the pulse height. **(B)** Schematic of constant fraction discrimination. The original input pulse is split into two, one is attenuated, and one is delayed and inverted. The zero-crossing when the two pulses are added is independent of the pulse height.

#### Hirvonen, Suhling, Frontiers in Physics 8 (2020) 161

#### Lange | Lecture TDAQ | EURIZON Wuppertal | 07/2023

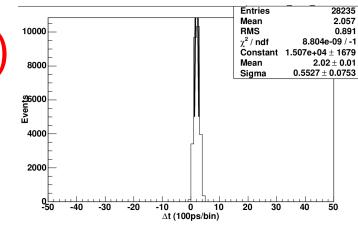

### TDC (Time-to-Digital Converter)

- As a board (CAMAC or VME) or as a chip

- Typical time-of-flight s=3 m  $\rightarrow$  t=10 ns

- Typical time resolution 25 ps

- Needs 2 signals: START, STOP

🗌 / Products / Modular Pulse Processing Electronics / Digital / TDCs / V1290A-2eSST

V1290A-2eSST

32 Channel Multihit TDC (25 ps)

#### Features

- 25 ps LSB

- 21 bit resolution

- 52 μs full scale range

- ECL/LVDS Input Signals

- 5 ns Double Hit Resolution

- Trigger Matching and Continuous Storage acquisition modes

- Leading and/or Trailing Edge detection

- 32 k x 32 bit output buffer

- MBLT, CBLT and 2eSST data transfer

- Multicast commands

Version: 2.2

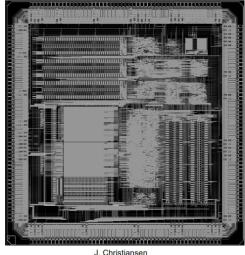

HPTDC High Performance Time to Digital Converter Version 2.2, March 2004

for HPTDC version 1.3

J. Christiansen CERN/EP - MIC Email: jorgen.christiansen@cern.ch

CERN/FP\_MIC

Page 1

#### https://cds.cern.ch/record/1067476/files/cer-002723234.pdf

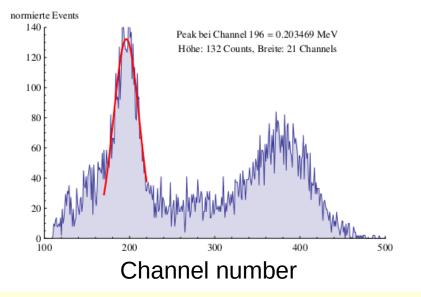

### ADC (Analog-to-Digital Converter)

- As a board (CAMAC or VME) or as a chip

- "8 bit ADC" means amplitude is divided and digitized into 2<sup>8</sup>=256 steps

- Type I: peak sensing ("ADC")

- Type II: charge integrating ("QDC")

- conversion time often order of µs ,,slow''

(needs delay in parallel DAQ path)

| CAEN<br>Tools for Discovery                                           | ABOUT US          | PRODUCTS           |  |  |  |  |  |

|-----------------------------------------------------------------------|-------------------|--------------------|--|--|--|--|--|

| Accessories Dig                                                       | ital Spectroscopy | Digitizer Families |  |  |  |  |  |

| # / Products / Modular Pulse Processing Electronics / Analog / ADCs ( |                   |                    |  |  |  |  |  |

#### V1785

8 Ch Dual Range Multievent Peak Sensing ADC

#### Features

- Two simultaneous ranges: 0 ÷ 4 V / 0 ÷ 500 mV

- 12 bit resolution with 15 bit dynamics

- 🛑 125 μV LSB on low range, 1mV LSB on high range

- 2.8 µs / 8 ch conversion time

- 600 ns fast clear time

- Zero and overflow suppression for each channel

- ±0.1 % Integral non linearity

- ±1.5 % Differential non linearity

- 32 event buffer memory

- BLT32/MBLT64/CBLT32/CBLT64 data transfer

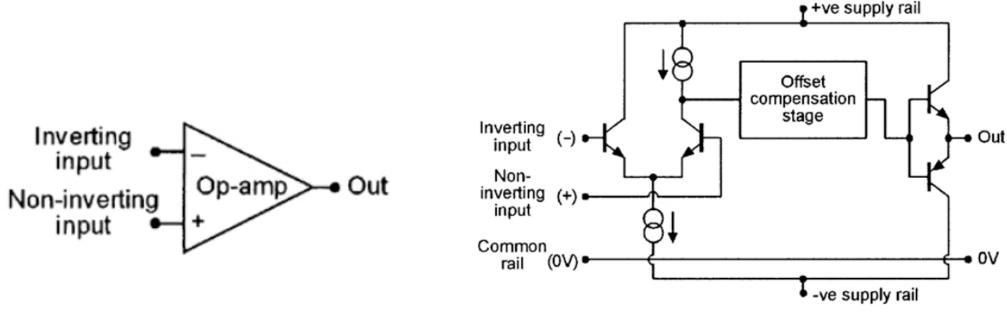

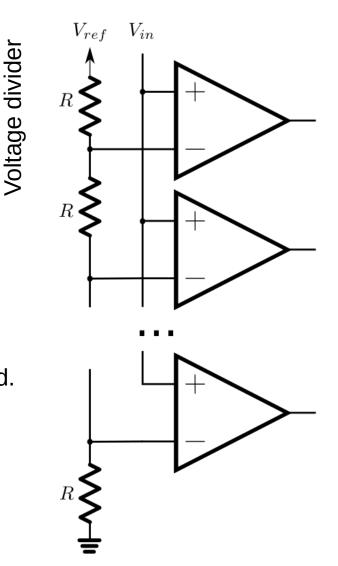

### Central element in an ADC: comparator

Operational amplifier, but without capacitors (used for frequency stabilisation)

FIGURE 1. Simplified op-amp equivalent circuit.

https://www.nutsvolts.com/magazine/article/op-amp-cookbook

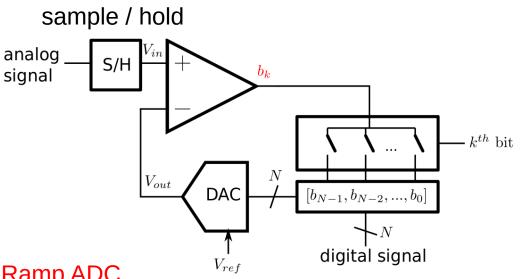

### What is inside an ADC?

SAR (successive approximation register) ADC

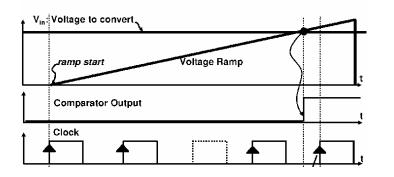

#### Ramp ADC

During sampling phase, a capacitor is charged. While discharging, number of clocks of given frequency are counted.

http://book.itep.ru/depository/ADC/Analog-Digital Converters (ADC) Tutorial.htm https://www.nutsvolts.com/magazine/article/op-amp-cookbook E. Delagnes, IEEE Transactions on Nuclear Science 54 (2007) 1735

Lange | Lecture TDAQ | EURIZON Wuppertal | 07/2023

Flash-ADC

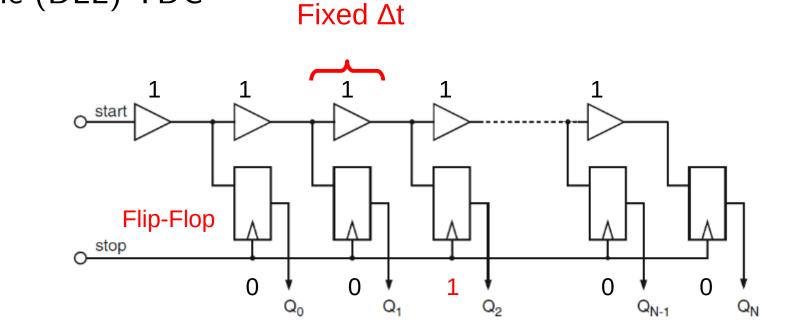

### What is inside a TDC?

Delay line (DLL) TDC

Vernier TDC, 2 delay lines, start & stop with 2 different delays (Trick! Increases the time resolution)

C. Yao, Master Thesis TRITA-ICT-EX-2011:212, Stockholm, 2011

Lange | Lecture TDAQ | EURIZON Wuppertal | 07/2023

### DAQ for many detectors

#### Build a frontend board

### Build your own frontend circuit

- Let's say, we need a circuit with an amplifier and/or ADC, or discriminator and/or TDC

- Let's say, it is a big experiment (many detectors)

- Possible approaches

- PCB (Printed Circuit Board)

FPGA (Field Programmable Gate Array)

ASIC (Application Specific Integrated Circuit)

### 1. PCB

- Components soldered on a board (e.g. resistors, capacitors, transistors, small chips, ...)

- Design and production has 7 steps

- See example (HADES RPC)

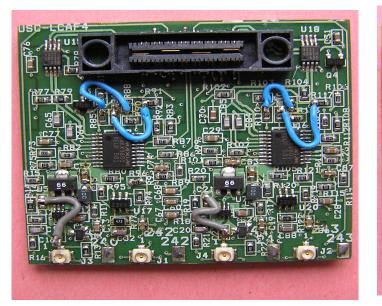

### HADES RPC Frontend Board amplifiers & discriminators 4 channels

LEMO connectors for cable from detector

### 2. FPGA

- Circuit on a chip, programmed

- (empty, non-programmed ) FPGA purchased from a company e.g. XILINX\*, ALTERA\*\*, LATTICE (taken over by \*AMD, \*\*intel)

- programming is in a special, logic-based language e.g. VHDL, VERILOG

- once programmed, can be changed again!

xilinx.com By SparkFun Electronics from Boulder, USA - Xilinx Spartan-3E (XC3S500E), CC BY 2.0, https://commons.wikimedia.org/w/index.php?curid=26785902

Lange | Lecture TDAQ | EURIZON Wuppertal | 07/2023

### 3. ASIC

Circuit on a chip,

designed by electronics expert (member of the collaboration), then submitted to a company (TSMC, IBM)

- Nowadays down to 65 nm silicon process, more radiation tolerant (digital part needs less area)

- Fabrication in 2 steps:

- prototype run, a few ASICs for testing

- then mass production

- Price 50.000+ Euros

- Once produced, cannot be changed anymore

FRICO ASIC (Fermilab)

Supernova/Acceleration Probe (SNAP) space telescope

https://ppd.fnal.gov/eed/asic/ASIC\_images.html

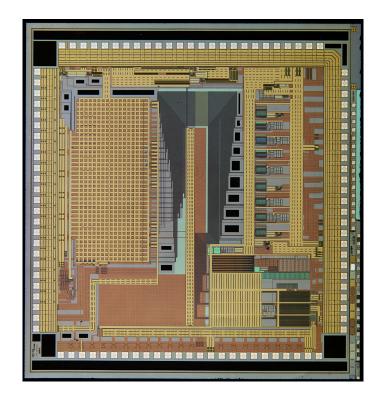

### **ASIC** examples

- NINO ASIC (e.g. ALICE)

250 nm CMOS process

4-stage <u>amplifier</u>, factor 30

<u>discriminator</u> 20 ps resolution

8 channels

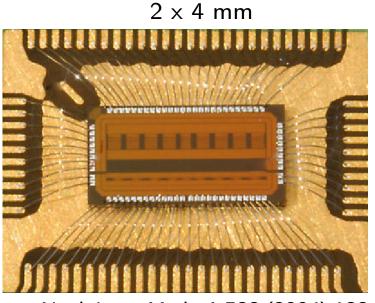

- TOFPET ASIC (e.g. Eurizon Cherenkov)

130 nm CMOS process

<u>TDC</u>, 50 ps resolution

64 channels

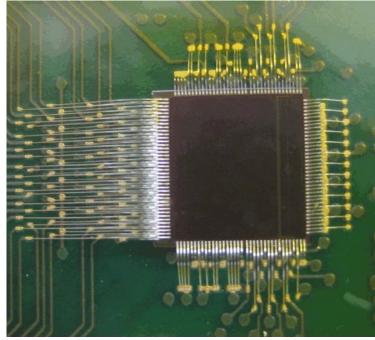

- DCD (e.g. Belle II PXD) UMC 180 nm technology <u>ADC</u> 8-bit

256 channels (continuous data stream 2.56 GBytes/s, needs special DAQ, see next lecture)

Lange | Lecture TDAQ | EURIZON Wuppertal | 07/2023

Nucl. Instr. Meth. A 533 (2004) 183

$2.5 \times 2.5 \text{ mm}$

www.petsyselectronics.com