## EP R&D WP5 extension proposal

CERN EP R&D Day 2023 20 February 2023

Kostas Kloukinas Davide Ceresa

on behalf of the EP R&D WP5

- Maintain activity but at a slower pace

- Advanced processes; access and evaluation

- FinFET (radiation evaluation)

- FD-SOI (non Rad-Tol applications

- Collaborating with external institute

- Specialty Technologies; evaluation, customized developments

- RRAM

- MRAM

- Ultra low leakage SRAM

#### Budget request: 120 kCHF Recourses request

2024-2028

P 5.1

| (FTE)  | Fellows | Students |

|--------|---------|----------|

| year 1 | 0       | 1        |

| year 2 | 0       | 1        |

| year 3 | 0       | 1        |

| year 4 | 0       | 1        |

| year 5 | 0       | 0        |

WP 5

R&D

EΡ

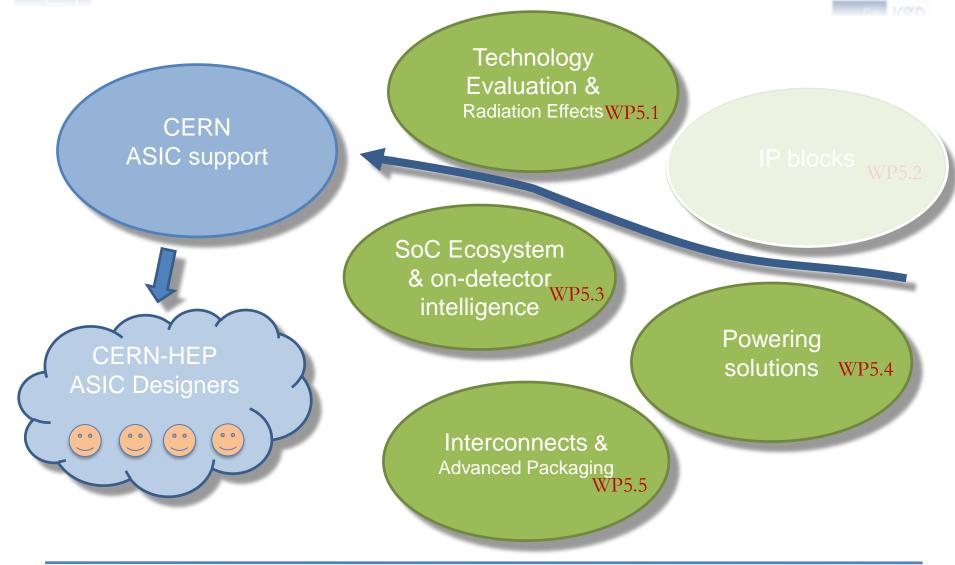

- Rad-Tol IP blocks on 28nm bulk CMOS technology

- Expect to complete and deliver all IP blocks by 2024-25

- Maintain IP block repository by CERN ASIC support service

- No further IP block development is foreseen within the EP R&D WP5

- HEP community is invited to contribute with IP blocks

#### Budget request: Recourses request

| (FTE)  | Fellows | Students |

|--------|---------|----------|

| year 1 | 0       | 0        |

| year 2 | 0       | 0        |

| year 3 | 0       | 0        |

| year 4 | 0       | 0        |

| year 5 | 0       | 0        |

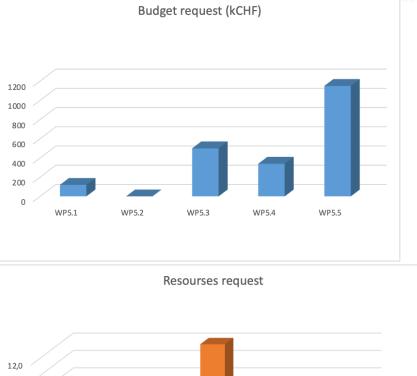

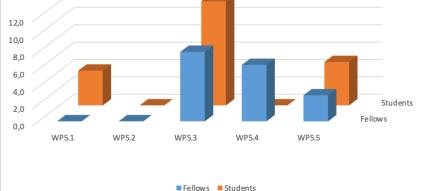

Total Budget: 2,110 kCHF

- Total Recourses (2024-28)

- □ Fellows: 16,5 (17,5)\*

- Students: 17 (21)\*

\* including 2024 top up

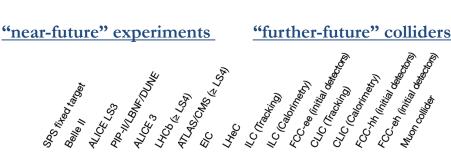

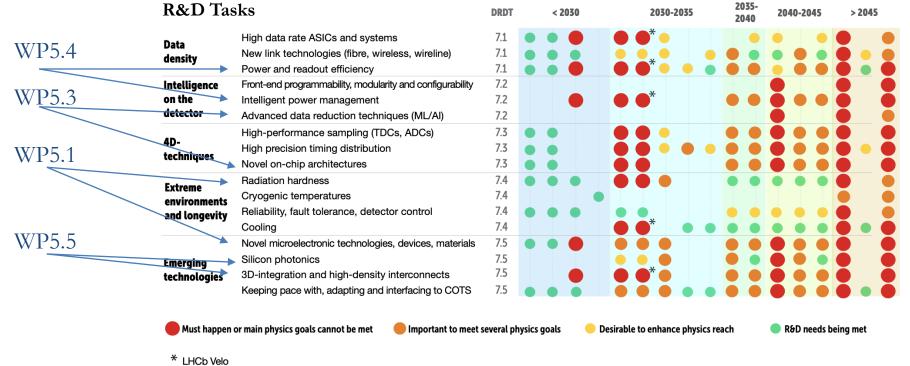

# Coherence with ECFA roadmap

2021 ECFA DETECTOR RESEARCH AND DEVELOPMENT ROADMAP

Chapter 7 Electronics and Data Processing

### EP R&D WP5 provides enablers for next generation experiments

- Technology Choice

- The selection and adoption of the 28nm CMOS technology as a "mainstream" process will "fuel" the developments of <u>"near-future" experiments</u>

- *"Further-future"* collider experiments would require more advanced technologies offering the necessary combination of performance, power efficiency and radiation hardness

- R&D on future state-of-the-art IC technologies would be necessary

- Infrastructure and Organizational issues

- Common Design Platforms & Collaborative Framework

- ASICs evolution and front-end "intelligence"

- Data processing adaptable to changing experimental conditions

- Programmability to facilitate retargeting ASIC blocks to different applications

- Present R&D on core-based SoC design topologies and methodologies will be applicable in <u>"near-future" experiments as well as pave the way</u> for the electronics of <u>"further-future" colliders</u>

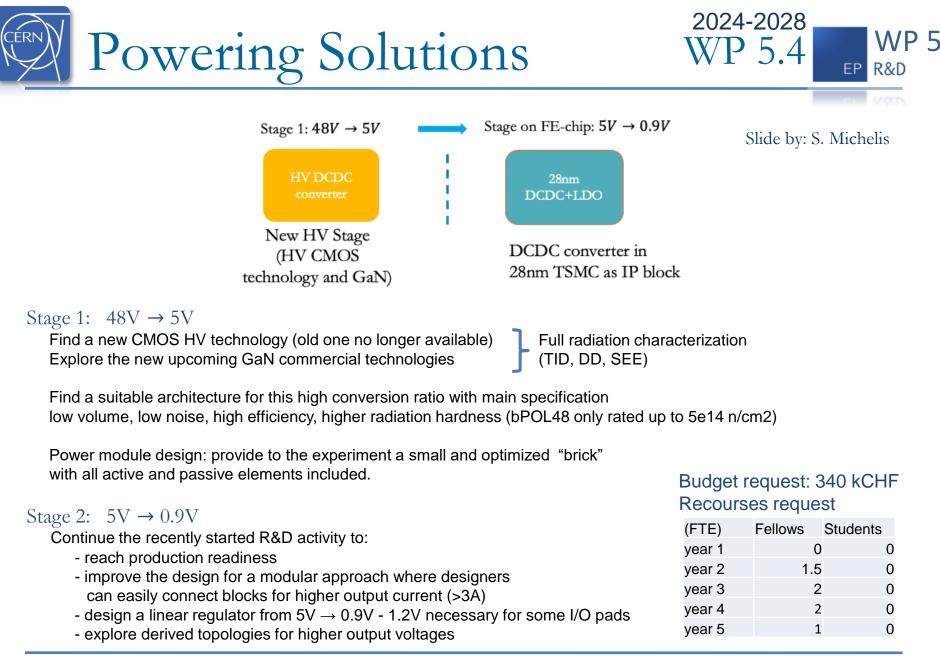

- Power distribution

- Stagged voltage conversion, multiple supply voltages, intelligent power management

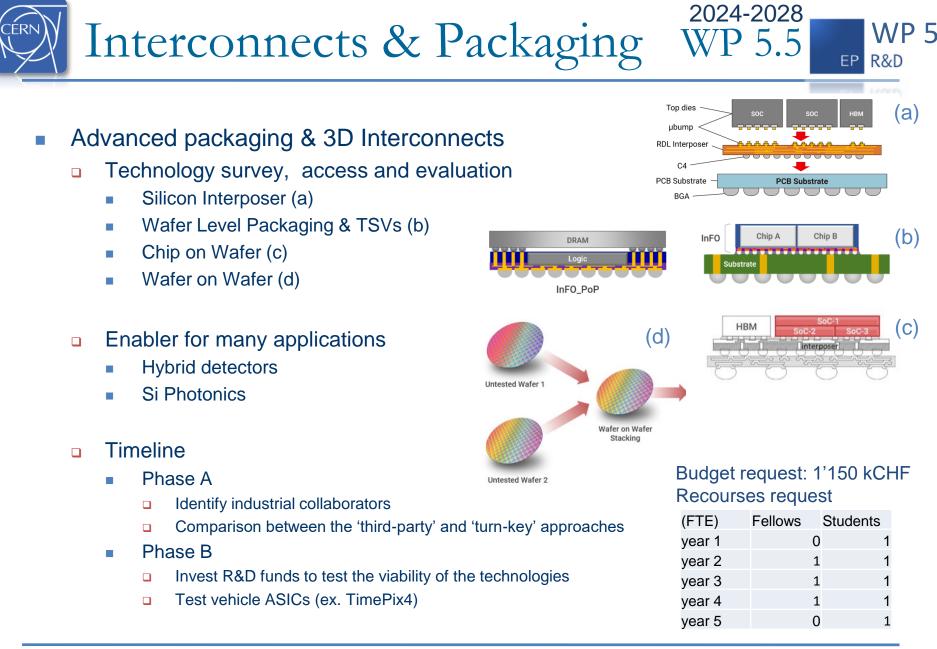

- Advanced packaging and 3D interconnects

- Emerging technologies in industry providing enablers in many applications for HEP detectors

Davide.Ceresa@cern.ch Kostas.Kloukinas@cern.ch

R&D

EΡ

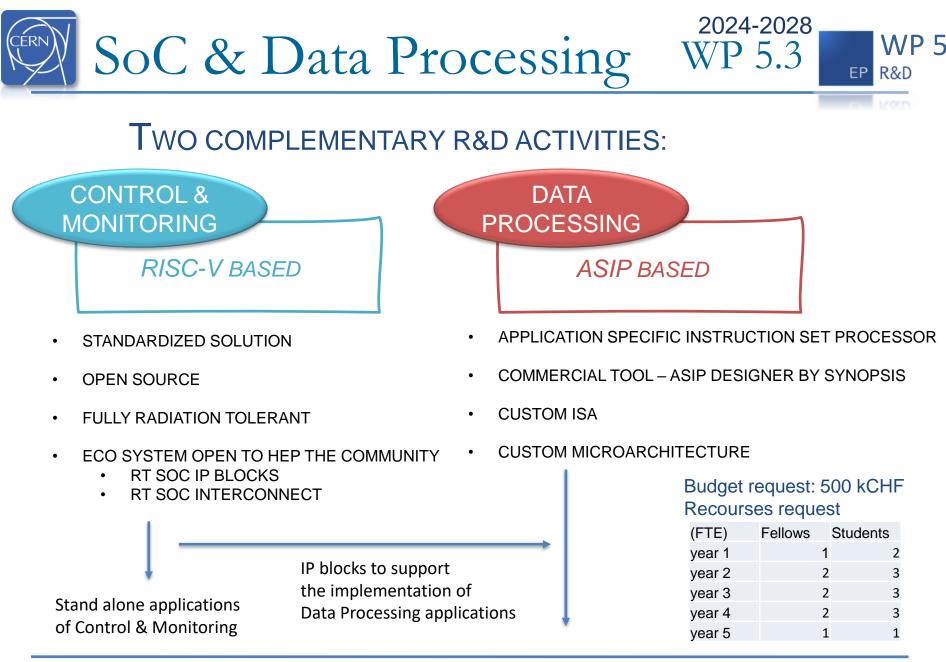

- System-on-Chip Radiation Tolerant Ecosystem (SoCRaTEs)

- Rad-Tol open-source Risc-V based core & interconnect infrastructure

- Rad-Tol peripherals

- Rad-Tol embedded FPGA (eFPGA); commercial or open-source based

- Rad-Tol non-volatile memories (NV-RAM); commercial or open-source based

- Control & Monitoring applications

- Rad-Tol Microcontroller style implementations

- On-Detector data processing applications

- Modeling & Simulation

- Simulation Framework development; Front-End to Back-End

- Application Specific Implementations

- Rad-Tol processing Cores

- Rad-Tol Network on Chip

- Rad-Tol Neural Networks

- Radiation Tolerance evaluation of SoC components

R&D

WP 5.3

**IPs**

**IPs**