# HGCROC chip test

Takahiro Fusayasu Saga University 14/Mar/2023

1

- The HGCROC chip, which was developed for the CMS high-granularity calorimeter, is a good candidate for the ALICE FoCal-E readout.

- Characterization of charge measurement linearity and trigger latency for ALICE FoCal-E.

- For the ALICE FoCal-E, 1980 ( = 90 x 11 x 2 ) HGCROC chips are necessary. Design of a chip test system for the mass-production is necessary.

- For these purposes, we launched a test bench and started elementary tests.

3 HGCROC chip test T. Fusayasu @ Saga-U

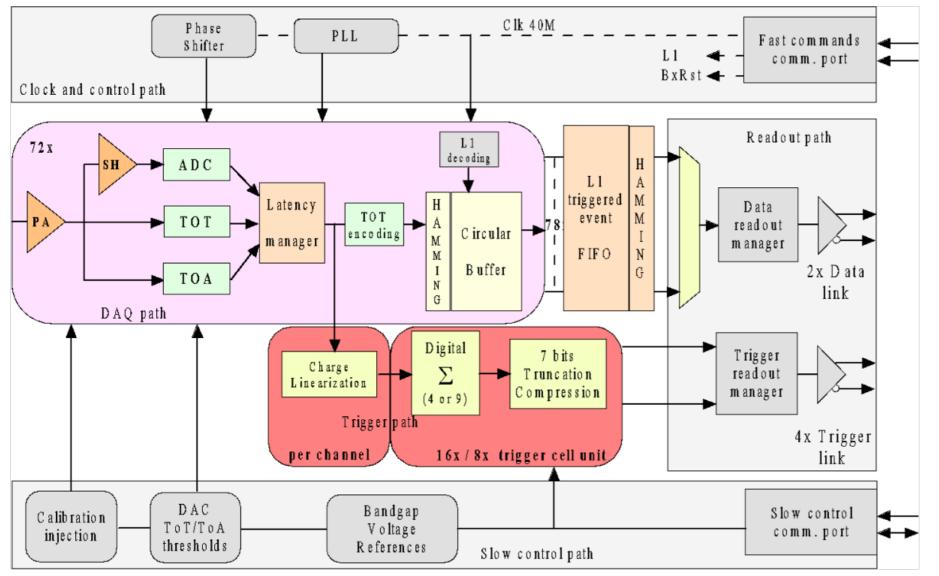

#### HGCROC v2 diagram

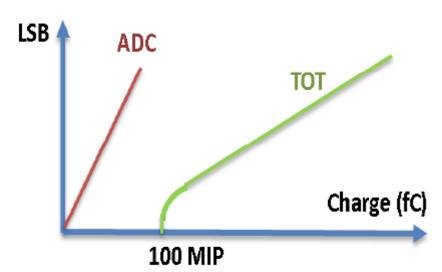

- 72ch ADC (SAR, 10 bit, 40 Msps) up to 100 MIP typ.

- 72ch TOT (50ps, 12 bit) above 100 MIP

- 72ch TOA (25ps, 10 bit) arrival timing

- 2ch common-mode ADC

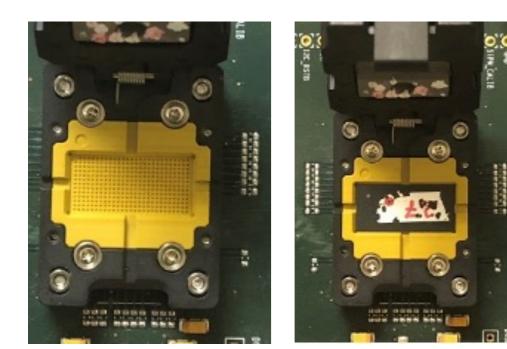

#### HGCROC2 Test bench

4 HGCROC chip test T. Fusayasu @ Saga-U

- We launched a characterization test bench at Saga Univ. with the help of Chujo-san and Abderrahmane-san (Aug/2022) from Tsukuba Univ.

- HGCROC2 test board with a socket and control/DAQ software are provided by the Grenoble group.

- Control and DAQ are performed by a commercial Xilinx board KCU105.

- 23 BGA-packaged HGCROC2 chips at hand.

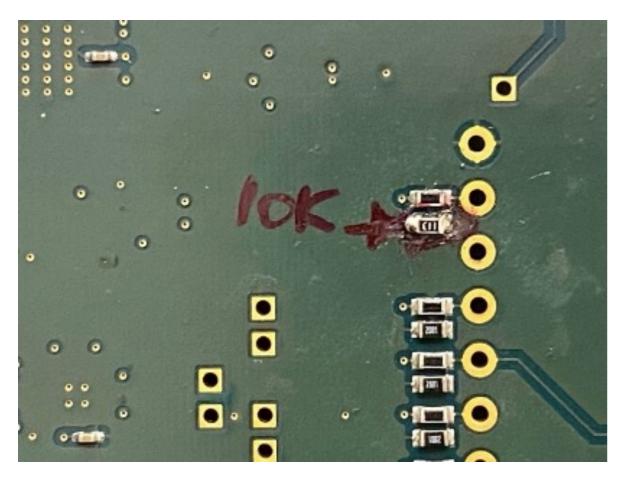

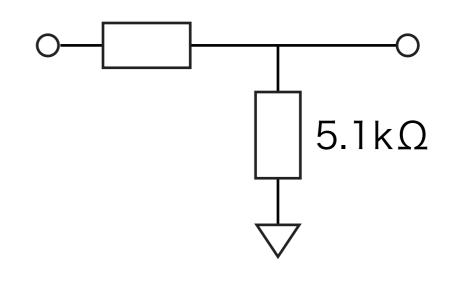

Slow control btw. FPGA and HGCROC is communicated via the I<sup>2</sup>C protocol. In our test, data taking is often interrupted by I<sup>2</sup>C errors. The I<sup>2</sup>C clock line voltage is reduced by series resisters. Original value 1.0 k $\Omega$  was found to be too low and replaced. We tried various values and now 5.1k $\Omega$  is mounted.

Even after the treatment, our measurements were suffered from I<sup>2</sup>C errors. At this moment, the problem is not yet solved.

### I<sup>2</sup>C pass/fail check of 23 chips

6 HGCROC chip test T. Fusayasu @ Saga-U

|           |                  | PhaseNumber      |                  |                  |                  |                  |

|-----------|------------------|------------------|------------------|------------------|------------------|------------------|

|           |                  | 1                | 2                | 3                | 4                | 5                |

|           | 4                | ×                | $\bigtriangleup$ | $\bigtriangleup$ | $\bigtriangleup$ | $\bigtriangleup$ |

|           | 6                | ×                | ×                | $\bigtriangleup$ | 0                | 0                |

|           | 7                | 0                | 0                | 0                | $\bigtriangleup$ | ×                |

|           | 8                | $\triangle$      | $\bigtriangleup$ | $\triangle$      | $\bigtriangleup$ | $\triangle$      |

|           | 10               | ×                | ×                | ×                | $\bigtriangleup$ | $\bigtriangleup$ |

|           | 12               | $\bigtriangleup$ | $\bigtriangleup$ | ×                | ×                | ×                |

|           | 13               | $\bigtriangleup$ | $\bigtriangleup$ | $\triangle$      | $\bigtriangleup$ | ×                |

|           | 14               | $\bigtriangleup$ | $\bigtriangleup$ | ×                | ×                | ×                |

|           | 15               | ×                | ×                | ×                | ×                | ×                |

|           | 16               | -                | -                | -                | 0                | -                |

|           | 19               | $\triangle$      | $\triangle$      | ×                | $\bigtriangleup$ | <b>O</b> %       |

| TipNumber | 20               | ×                | ×                | ×                | ×                | ×                |

|           | 21               | ×                | ×                | $\triangle$      | $\bigtriangleup$ | $\triangle$      |

|           | 22               | ×                | ×                | ×                | ×                | ×                |

|           | 23               | ×                | ×                | ×                | ×                | ×                |

|           | 24               | ×                | ×                | 0                | $\bigtriangleup$ | $\bigtriangleup$ |

|           | 25               | $\bigtriangleup$ | ×                | ×                | ×                | $\bigtriangleup$ |

|           | 26               | -                | -                | -                | 0                | -                |

|           | 27               | ×                | $\triangle$      | $\triangle$      | 0                | 0                |

|           | 29               | $\bigtriangleup$ | ×                | ×                | ×                | ×                |

|           | 30               | ×                | ×                | ×                | ×                | ×                |

|           | 31               | ×                | ×                | $\triangle$      | $\triangle$      | $\triangle$      |

|           | <mark>549</mark> | 0                | $\triangle$      | ×                | ×                | $\triangle$      |

| 0           | DelayScan success               |

|-------------|---------------------------------|

| $\triangle$ | I2C error in delayScan          |

| ×           | Can't even open the application |

| *           | Only one success                |

Phase number

$\rightarrow$  adjustment of I<sup>2</sup>C clock phase

Only 8 chips passed the delay scan test. If we think the chip yield shouldn't be such worse, then there might be a problem in the board or the test environment.

$\rightarrow$  still in investigation.

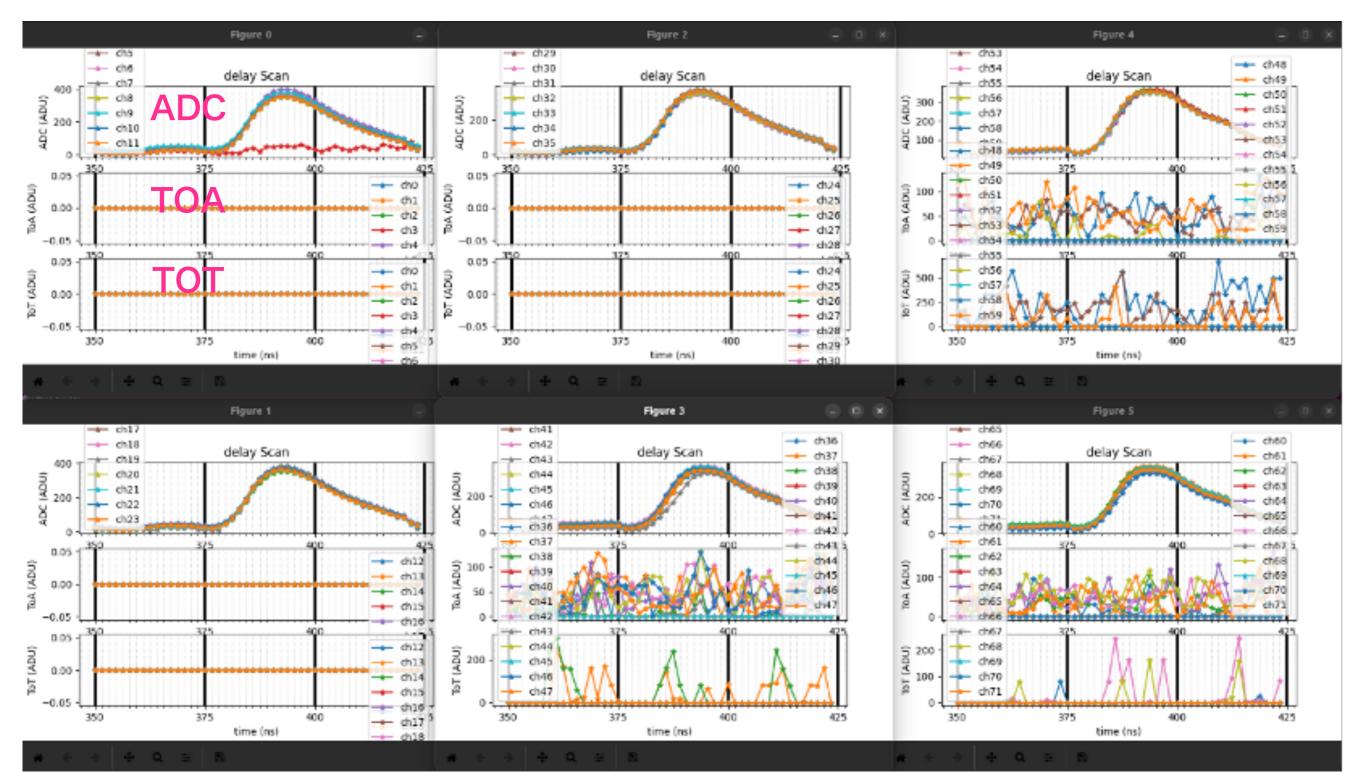

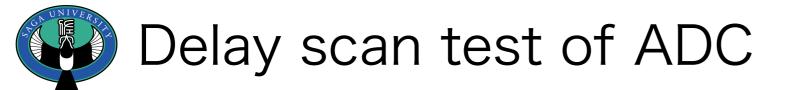

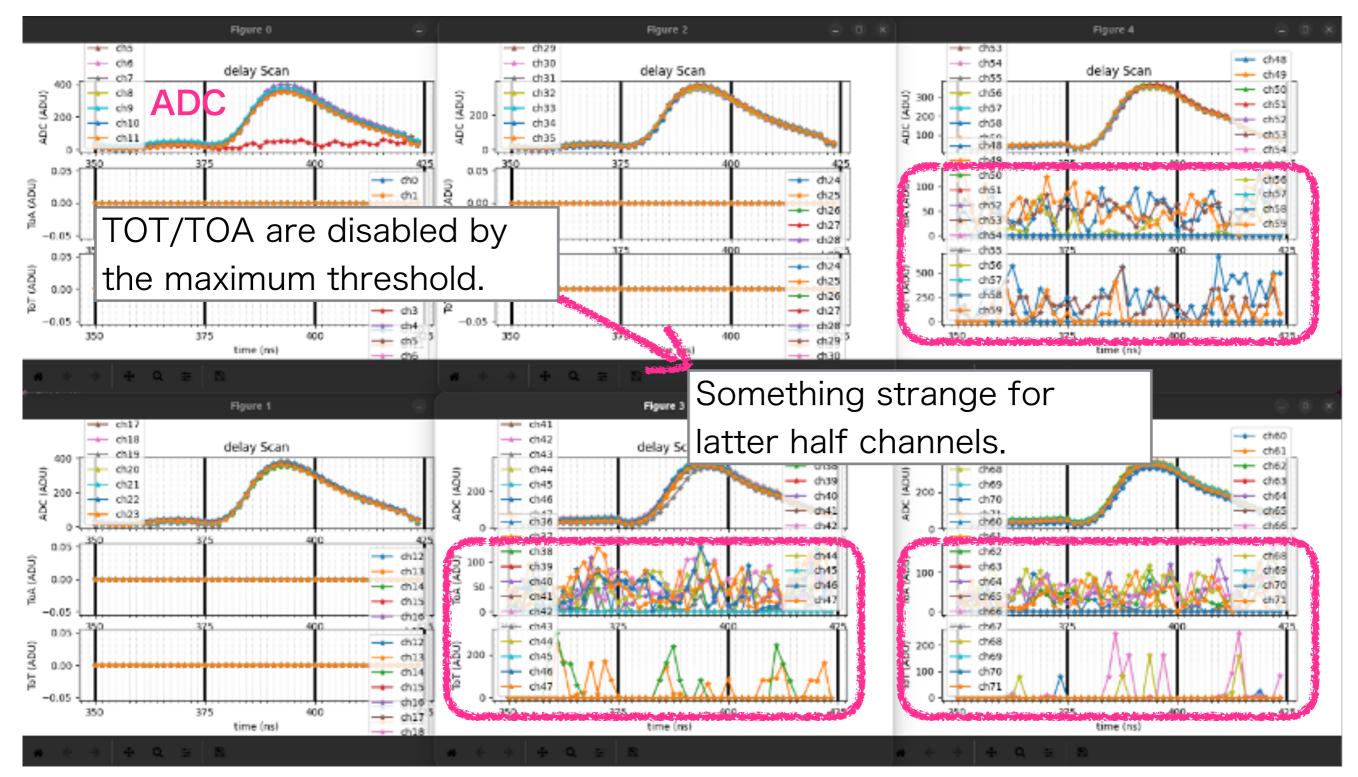

While repeating the test pulse sampling, delay (ADC sampling timing) is increased every time by ~1.56ns, so that we can find the "peak" timing.

Results from all 72 channels

While repeating the test pulse sampling, delay (ADC sampling timing) is increased every time by ~1.56ns, so that we can find the "peak" timing.

#### Results from all 72 channels

9 HGCROC chip test T. Fusayasu @ Saga-U

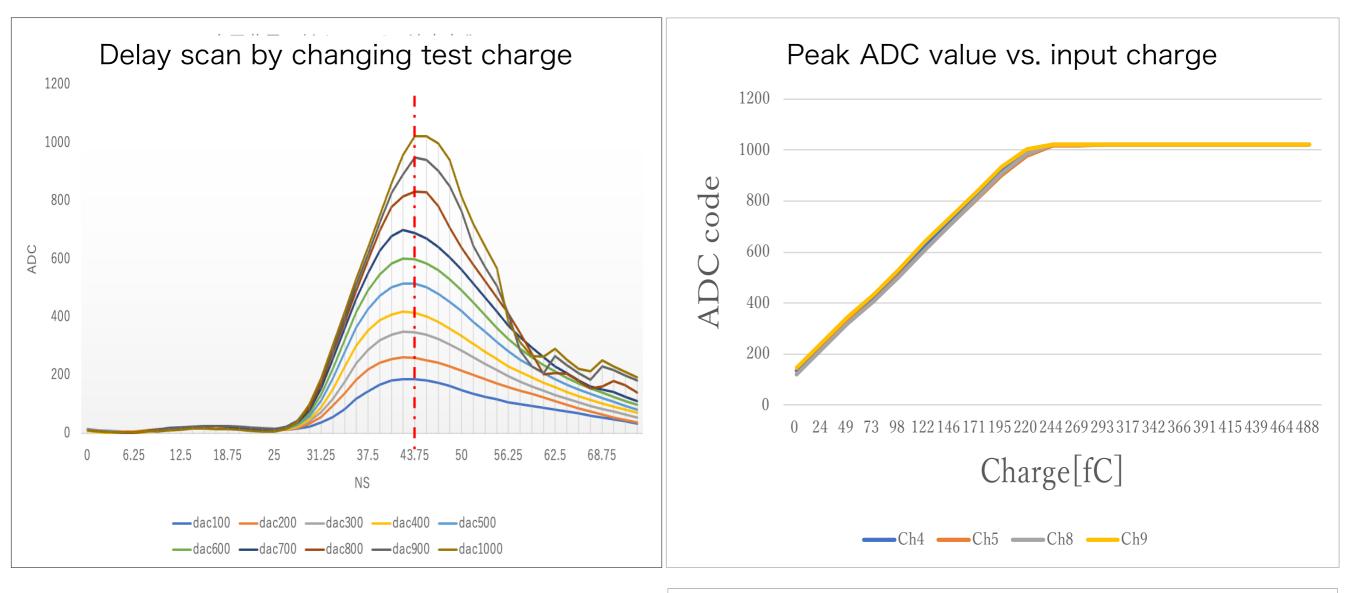

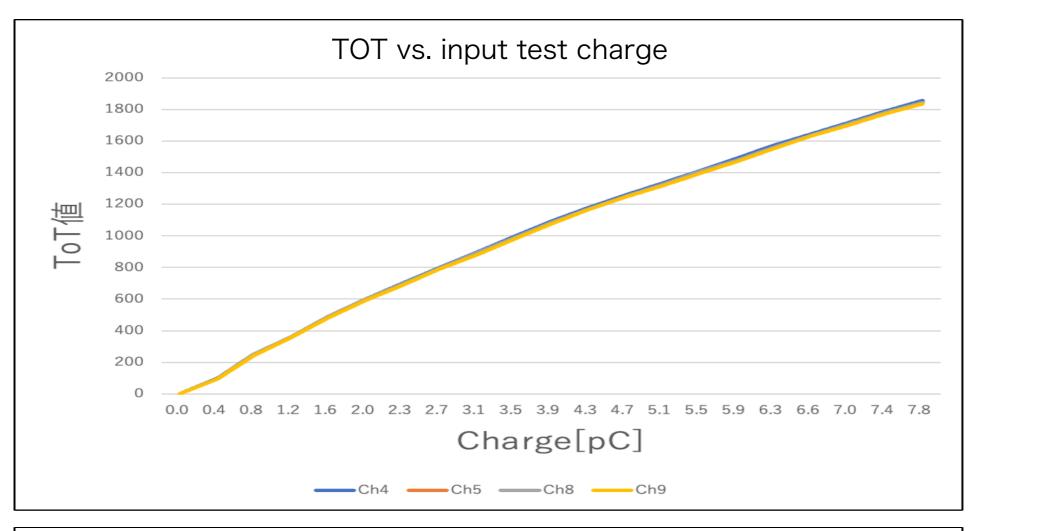

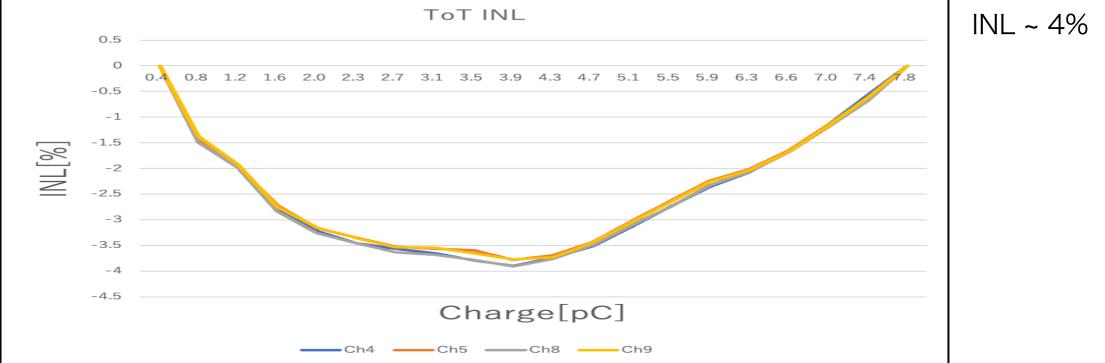

Good linearity is obtained below saturation.

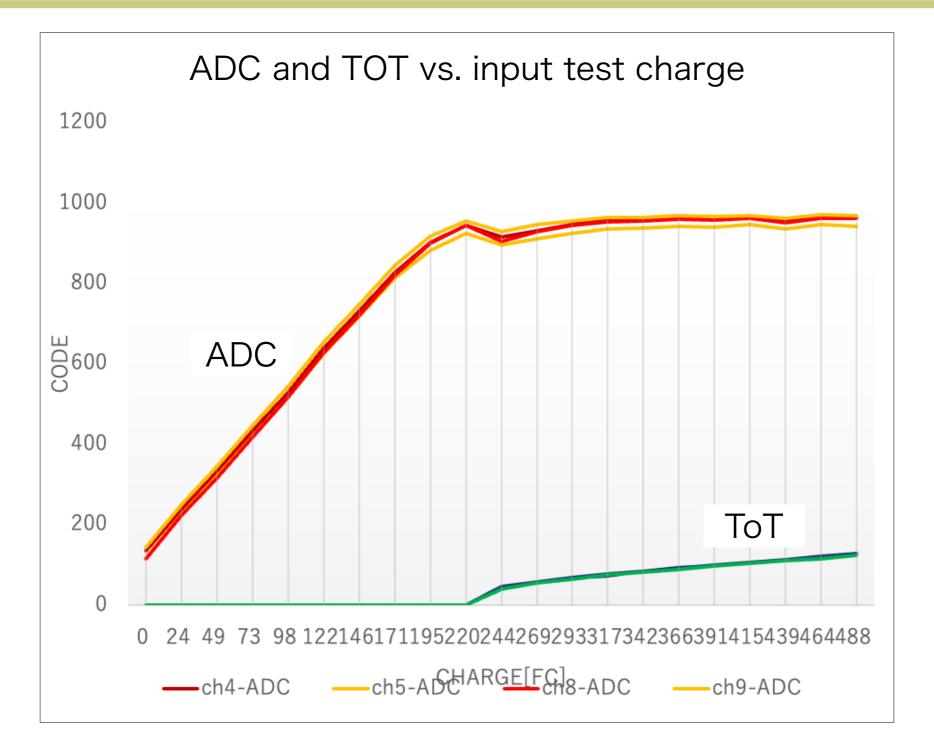

## ADC / TOT connection

11 HGCROC chip test T. Fusayasu @ Saga-U

Except for small non-linear region, large dynamic range is covered.

- $\cdot$  We started the test study of HGCROC v2 for characterization and in preparation for mass production test in future.

- $\cdot$  ADC / ToT linearities are obtained using internal test pulse.

- We need more understandings on the chip characteristics.

(I<sup>2</sup>C error, TOT behavior, …)

- Test equipment will be designed using external test pulse so that I/O circuit failure should be detected.