## DSC – Gaseous trackers

#### ePIC Collaboration meeting – Warsaw, July 27<sup>th</sup> 2023

K. Gnanvo, M. Vandenbourcke

F. Bossù (CEA Saclay)

## Context

- Nice summary in Ernsrt's slides yesterday (<u>link</u>)

- The evolution of the tracking system from the ECCE's reference design

- The SVT will provide most of the momentum resolution

- Micro-pattern gaseous detectors (MPGDs), together with TOF, will provide fast points for pattern recognition and aid tracking into the PID detectors

- In June 2023, new (final?!) configuration of the MPGD systems

CAVEAT: Last minute preparation of these slides. No time to include many details.

## Brycecanyon

## New configuration – June 15th

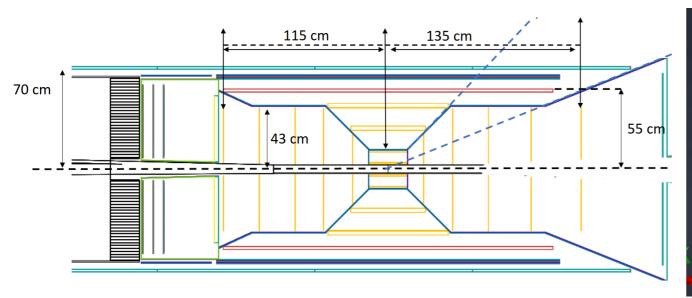

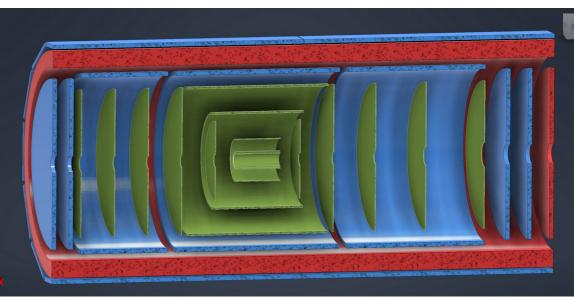

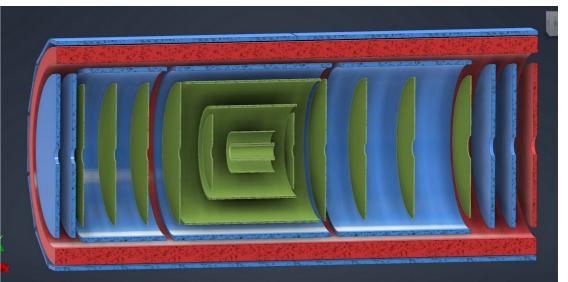

#### Green: MAPS; Blue: MPGDs; Red: TOF fiducial volume

• One cylindrical layer at r=50cm

#### Three subsystems:

- One 3-cylinders barrel layer at R=50cm

- One layer at the inner surface of the DIRC

- Pairs of disks in the forward and backward endcaps

# **Requirements and challenges**

- Time resolution better than 20ns

- Spatial resolutions ~150µm

- Challenges:

- Material budget

- Particles crossings the active areas with large angles

- Space limitations

- Constraints on services (data, HV, LV and cooling) and support structure

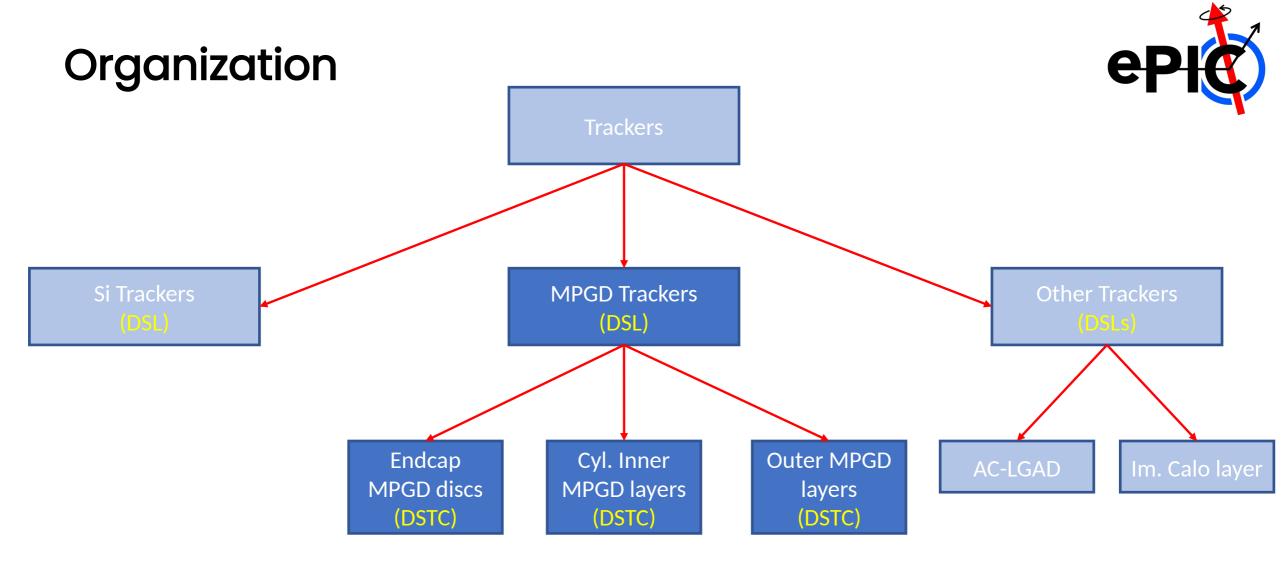

# Technologies Layer at the DIRC: • Flat µRWELL detectors Cylindrical layer Micromegas Disks µRWELL or GEM

#### Ongoing R&D within eRD108 and generic R&D

- 2D readout on large detectors

- Thin drift gap (~1mm) to maintain good spatial resolutions for tracks impinging with large angles **Participating institutes**: JLab, UVa, FIT, Temple U, BNL, INFN, Vanderbilt U, Yale, CEA-Saclay

FE Electronics based on the future SALSA chip (CEA & Sao Paulo U), under development within eRD109

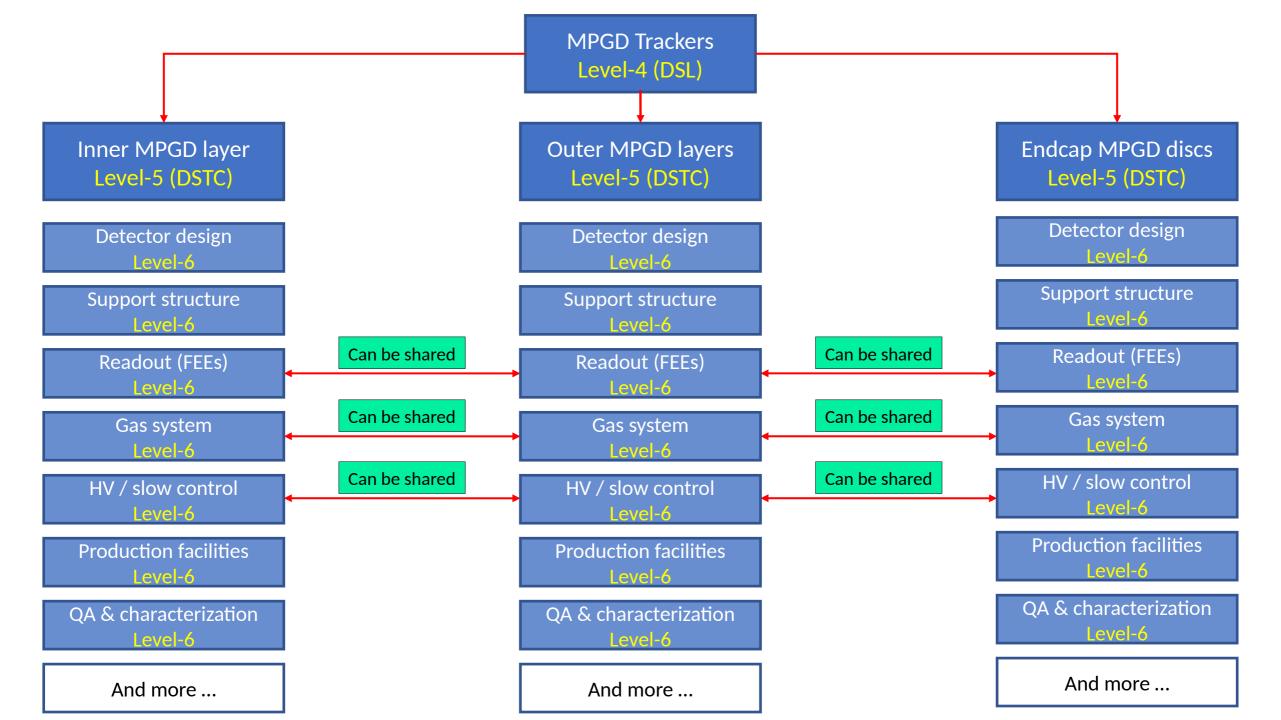

DSL: Kondo Gnanvo (JLab) DSTC:

- Cyl. Inner layer: Maxence Vandenbroucke (CEA Saclay)

- DSTCs for the endcap and the outer layers to be appointed

## Summary

- Recent change of configuration of MPGD layers in ePIC

- Design of the different components at different maturity

- The new configuration brings also new challenges, but with a clearer configuration it is easier to advance on the design

- Close collaboration with the electronic engineers developing the SALSA chip

- Many tanks to the Tracking CC WG conveners and the EIC project for the help and guidance

- Ongoing organization of the teams to speed up the design