### NINO development

P. Jarron 14/02/2011

# Status

- NINO status

- Used successfully connected to HPTDC in ALICE TOF

- Jitter limit

- 2-3 ps rms (Crispin)

- Used for PET TOF (Endotofpet-us EU project) with 220 ps

FWHM coincidence

- with SiPM coupled to LSO crystal, 70 ps rms limited by Poisson statistics, so far the best results

- a version 32 channel has been developed

- A prototype in 130 nm has been developed

### Interest for a new development

- Arguments to continue the development of NINO

- So far it is the best amplifier-discriminator optimized for low jitter and low threshold

- Is ESE is interested to keep this technology alive?

- With a new HPTDC in 130 nm (90 nm) to be developed a front end interfacing a detector is essential.

- Why?

- Because an integrated ASIC has many advantages

- Simplification of the readout system, lower cost, lower power

- It has been verified (Crispin) that the physical connection between NINO and HPTDC increases the jitter,

- not an issue for 30 ps time resolution

- But critical for 10 ps time resolution

- Design effort estimate

- One year of prototype development and design

- ½ year of characterization

- ½ year of contingency, resubmission

- Plus time of design for integration with HPTDC

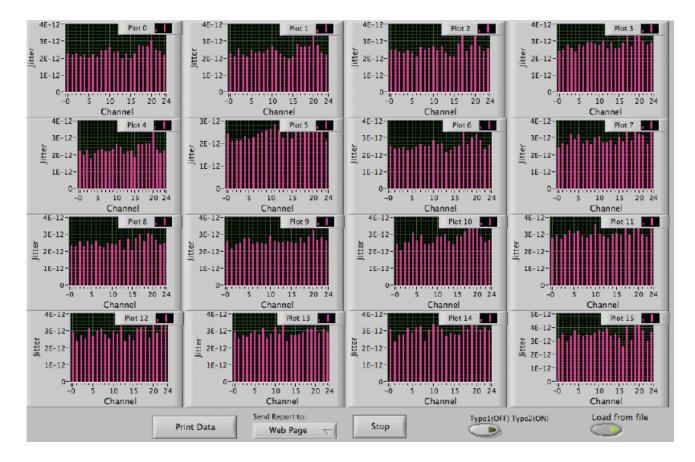

# Time jitter limit from Crispin NINO 25

- 4 different values of injected charge and 4 different values of threshold

- Typical jitter between 2 and 3 ps With LeCroy oscilloscope

- Input signal is 25-100 fC, for lower signal jitter dominated by electronic noise

Jitter of single channel:

Front-end card not connected to anything

#### **7 ps**

Front end card plugged into interface card

#### 14 ps

Front end cards plugged into interface card that is connected to mrpc strip 21 ps

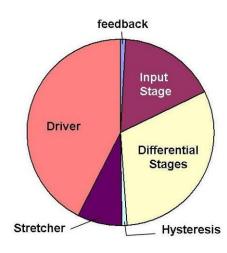

### Power

|                                                     | Input stage                                 | Feedback                                | Differential stage                   | Hysteresis                           | Stretcher                               | Driver                           |

|-----------------------------------------------------|---------------------------------------------|-----------------------------------------|--------------------------------------|--------------------------------------|-----------------------------------------|----------------------------------|

| Channel Rin = $50 \Omega$                           | 1 mA × 2<br><u>2 mA</u>                     | <u>100 μA</u>                           | 920 μA × 4<br><u>3.68 mA</u>         | <u>92 µА</u>                         | <u>Off: 920 µA</u><br><u>On: 950 µA</u> | <u>5 mA</u>                      |

| Channel Rin = $30 \Omega$                           | 1.8 mA× 2<br><u>3.6 mA</u>                  | <u>100 μA</u>                           | 920 μA × 4<br><u>3.68 mA</u>         | <u>92 µА</u>                         | <u>Off: 920 µA</u><br><u>On: 950 µA</u> | <u>5 mA</u>                      |

| Bias Cell<br>Rin = $30 \Omega$<br>Rin = $50 \Omega$ | N1/N2/N3/P1<br><u>2 mA</u><br><u>3.6 mA</u> | Ν4/Ρ2<br><u>140 μΑ</u><br><u>140 μΑ</u> | Ν5<br><u>910 μΑ</u><br><u>910 μΑ</u> | Ν7<br><u>230 μΑ</u><br><u>230 μΑ</u> | Ν8<br><u>230 μΑ</u><br><u>230 μΑ</u>    | N6<br><u>5 mA</u><br><u>5 mA</u> |

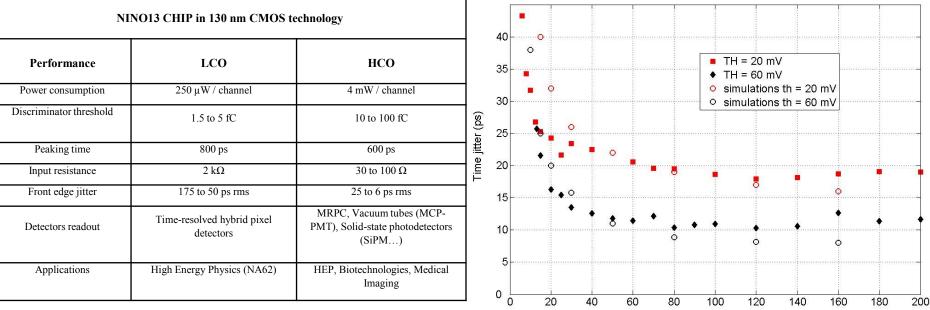

# NINO 130 nm proto not yet fully optimized

Input charge (fC)