# Development of a medium-sized photon counting UFXC-demonstrator at SOLEIL synchrotron

Marie Andrä<sup>1</sup>, El-Houssain Ait-Mansour<sup>1</sup>, Jérôme Bisou<sup>1</sup>, Arkadiusz Dawiec<sup>1</sup>, Pawel Grybos<sup>2</sup>, Brahim Kanoute<sup>1</sup>, Claude Menneglier<sup>1</sup>, Fabienne Orsini<sup>1</sup>

1. SOLEIL Synchrotron, Saint-Aubin, 91192 Gif-sur-Yvette, France

2. Department of Measurement and Electronics, AGH University of Science and Technology, Krakow 30-059, Poland

marie.andrae@synchrotron-soleil.fr

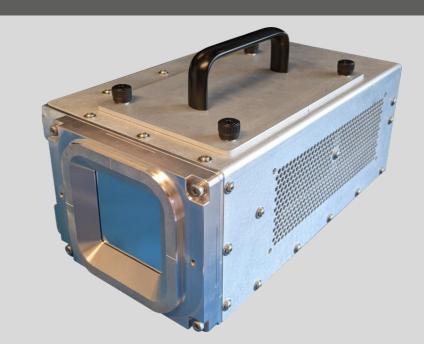

# **ULTRA FAST X-RAY CAMERA DEMONSTRATOR with 8 CHIPS**

A hybrid photon-counting pixel detector of medium size with very high frame rate, high count rate capability and short gating time for time-resolved

pump-probe experiments and other new or existing applications

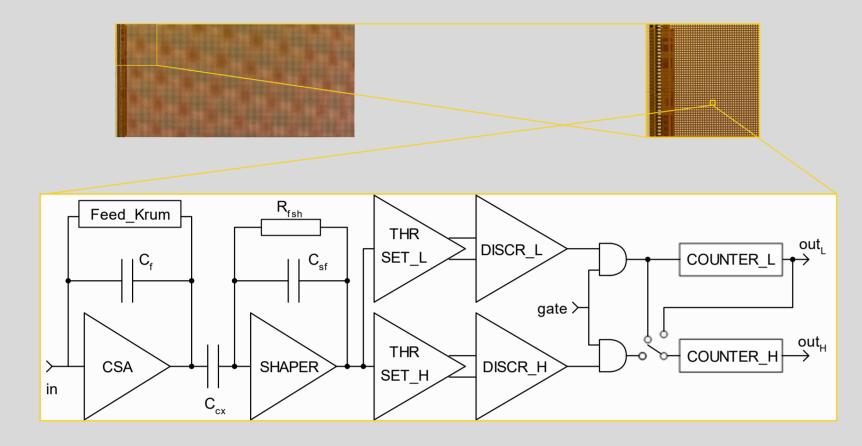

UFXC32k readout chip designed at AGH-UST, Krakow

- 128 x 256 pixels with 75 µm pitch

- Two discriminators with 7 trimbits each and two 14-bit counters per pixel

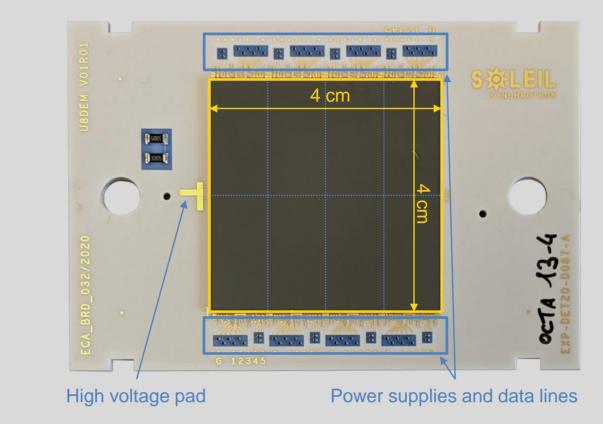

#### **U8DEM** module

- Evolution of the existing 2-chip system tested at SOLEIL

- Single Si-sensor (320 µm or 450 µm thickness), bump bonded to

#### Detector

- Compact (16 x 28 x 11 cm<sup>3</sup>) and light (~3 kg) mechanics

- Efficient water cooling (up to 50 W)

- Adjustable gain and frontend speed

- Selectable readout counter depth (2, 4, 8, 14 or 28-bit)

- Minimum exposure time < 100 ns</li>

- High count rate linearity > 10<sup>6</sup> ph/pix/s (at 90 % counting efficiency)

- eight UFXC32k readout chips

- Detection area: 4 × 4 cm<sup>2</sup> (250k pixels with 75 µm pitch, including single pixel inter-chip spacing)

- Ceramic PCB (LTCC, 88 × 60 mm<sup>2</sup>)

- Single high density connector on the backside

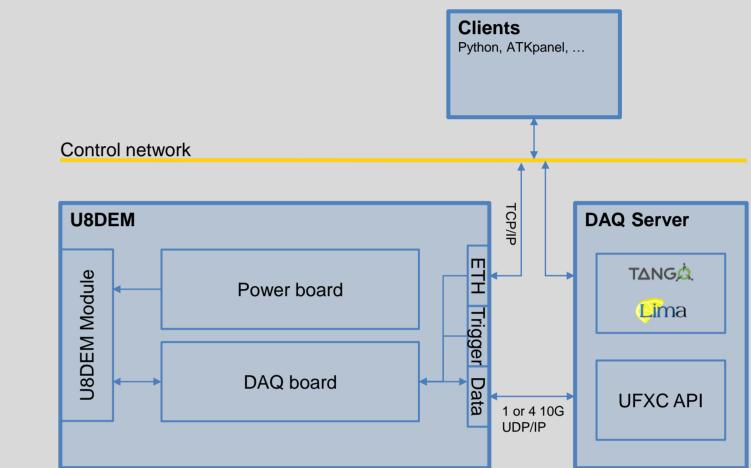

- Power board

- Acquisition board with FPGA

- I or 4 x 10G QSFP connections for data transfer

- Power consumption of the detector head < 25 W</p>

# FIRMWARE AND SOFWARE STATUS

#### Firmware + Library developed for U8DEM

- Based on firmware + decoding library made for the 2-chip system

- Interface to TANGO and LIMA to ease integration into the SOLEIL beamline control system

- Controls 8 chips simultaneously

- Frame rate between 3.4 kHz and 23 kHz (depending on the acquisition mode)

- Based on FEM-II acquisition board (Virtex 6 FGPA + Zynq SoC)

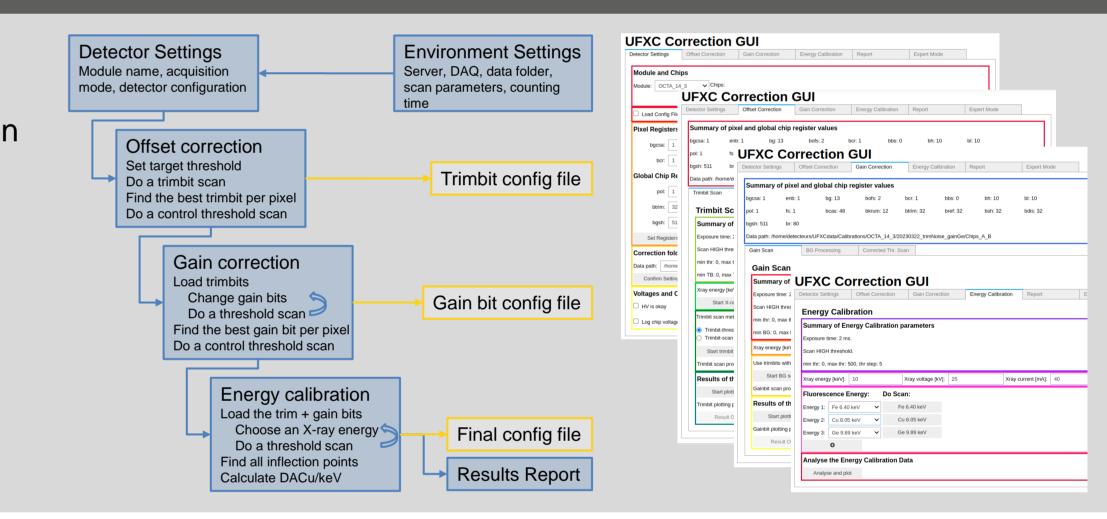

#### **Correction + Calibration Software**

- Semi-automatised offset and gain correction and energy calibration

- Control of the detector and X-ray generator (via TANGO devices)

- Generates the configuration files and pixel mask

- Displays and saves all resulting plots and data

- GUI based on Jupyter-Notebook widgets

- Under finalization

Under finalization

# FIRST CHARACTERISATION MEASUREMENTS

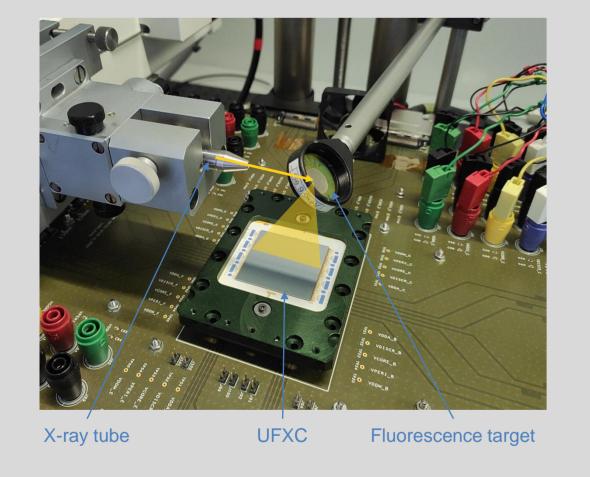

All presented measurements have been acquired with the existing 2-chip readout system and in the laboratory X-ray setup using fluorescence photons. The data of all 8 chips are presented.

#### Laboratory X-ray setup

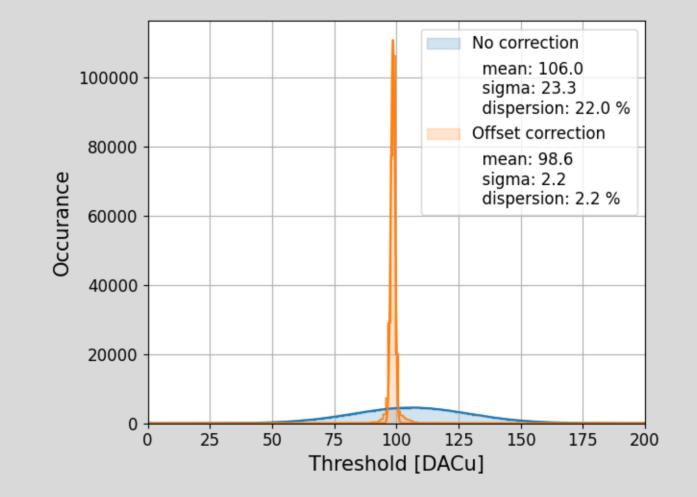

# **Offset spread**

Very low offset spread after the correction

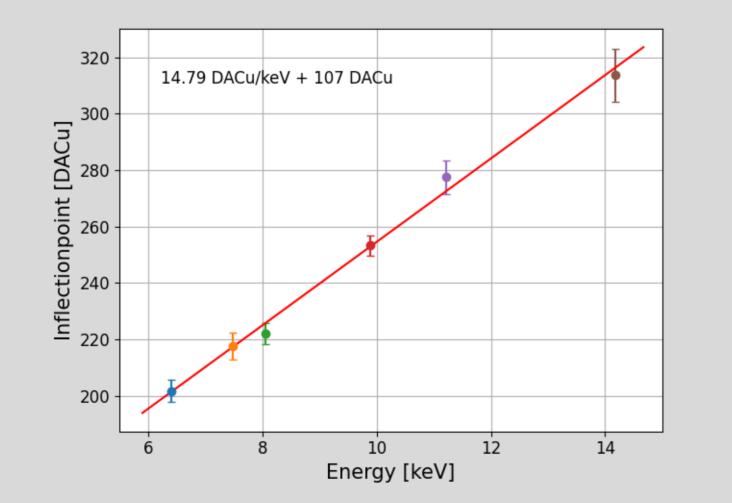

#### **Energy Calibration**

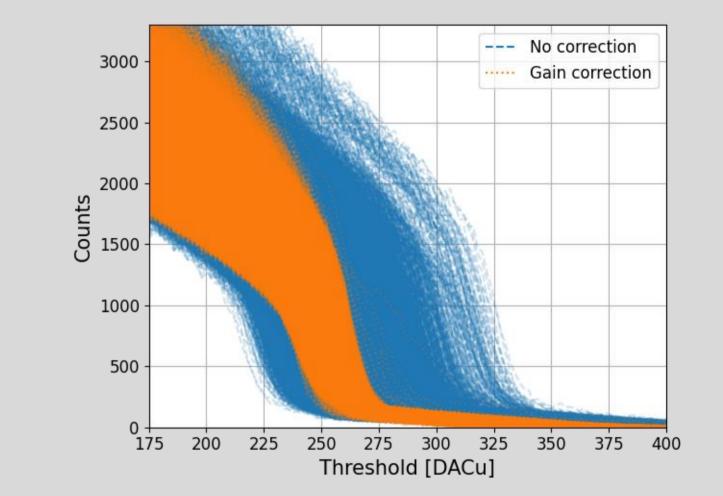

# Threshold dispersion @ 10 keV

#### 30000 No correction mean: 252.1 sigma: 7.5 25000 dispersion: 3.0 % Gain correction mean: 250.0 <u>9</u> 20000 5 sigma: 3.1 dispersion: 1.2 % CC 15000 ŏ 10000 5000 220 240 260 280 300 200 Threshold [DACu]

Reduced threshold dispersion < 2% after gain correction

#### Imaging setup at the beamline

### **Corrected threshold scans @ 10 keV**

Threshold scans before and after gain correction

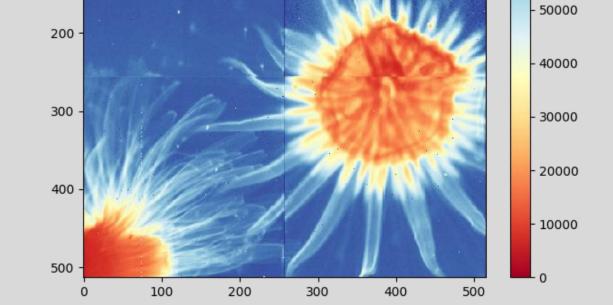

### First imaging @ 10 keV

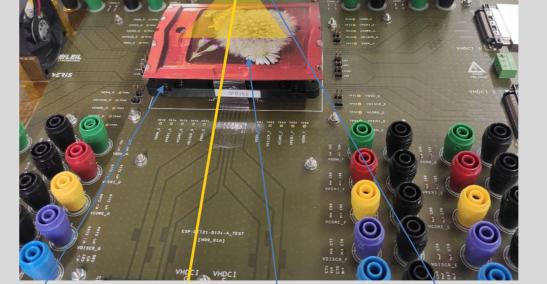

#### Fluorescence setup with temporary readout system

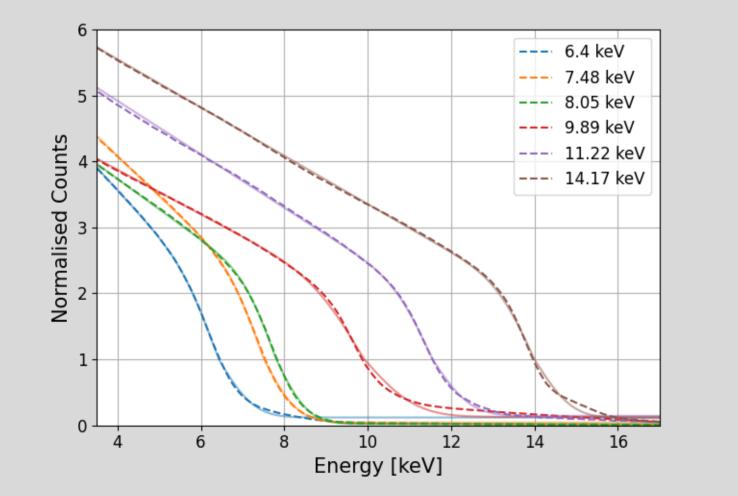

#### Threshold scans at different energies

UFXC X-ray beam Imaging sample Fluorescence target

Median threshold scans after corrections at low gain

Median energy calibration at low gain

UFCX with imaging sample using fluorescence photons

Flatfield and inter-chip gap correction Shifts in the image are due to the composition of four 2-chip images taken one after the other

# SUMMARY AND OUTLOOK

- An 8-chip demonstrator has been developed

- ✓ Offset, gain correction and energy calibration work as expected

- ✓ Validated good quality of several hybrid modules

- Firmware and software are in the final development stage

- Goal: Have the first fully assembled and operational U8DEM detector by end 2023 / beginning 2024

# REFERENCES

[1] A. Dawiec et al., AIP Conf. Proc. 2054, 060067, (2019) [2] P. Grybos et al., IEEE Trans. Nucl. Sci. 63 1155, (2016) [3] D. Bachiller-Perea et al., J. Synchrotron Rad. 27, (2020)

The UFXC32k detector was supported by the National Centre for Research and Development, Poland (PBS1/A3/12/2012).