UNIVERSITÉ DE GENÈVE

FACULTÉ DES SCIENCES Département de physique nucléaire et corpusculaire

## The Monolithic ASIC for the High Precision Preshower Detector of the FASER Experiment at the LHC

CHIARA MAGLIOCCA

on behalf of the FASER Preshower Upgrade Team

Joint SPS and ÖPG Annual Meeting 2023, Basel

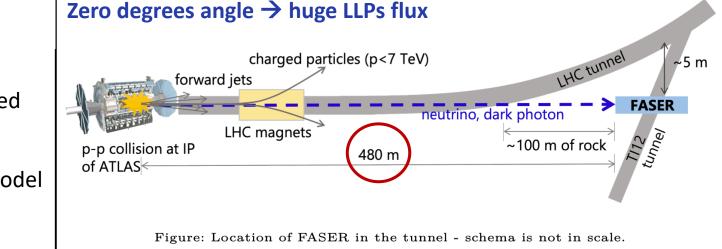

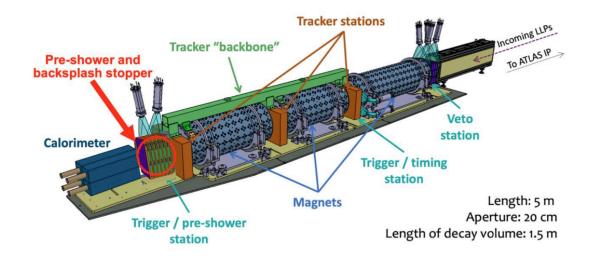

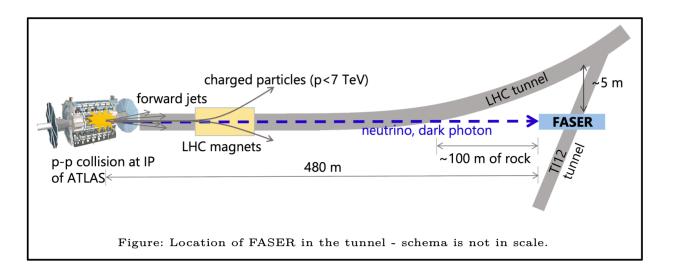

## The FASER Experiment at LHC

- ForwArd Search ExpeRiment

- Designed to search for light and weakly-interacting particles + study the interactions of high-energy neutrinos (FaserNu)

- Fluxes of high-energy SM particles are supressed

- Muons and neutrinos only exception

- FASER can probe Axion-Like-Particles (ALPs) model

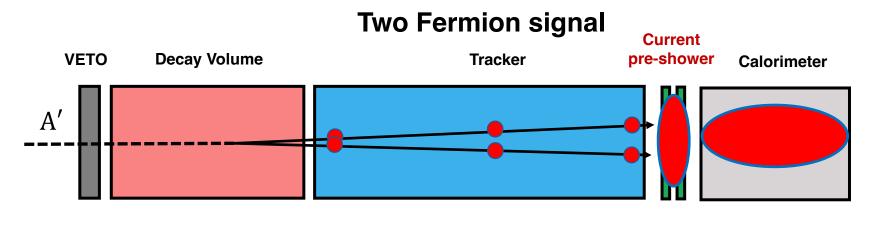

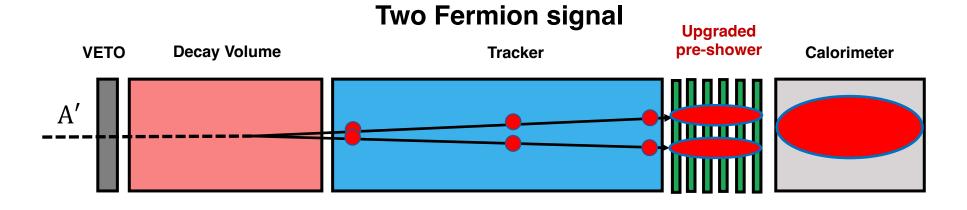

## What Are We Able to Detect Well: Two Fermion Signal

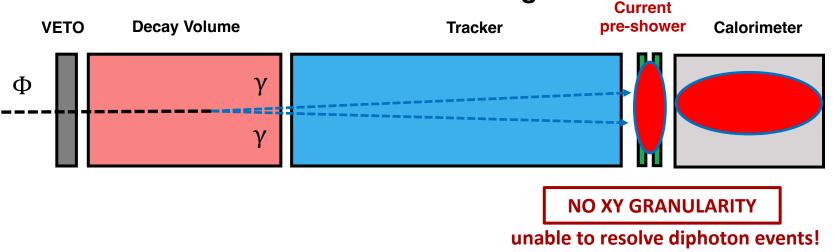

### **Two Photon signal**

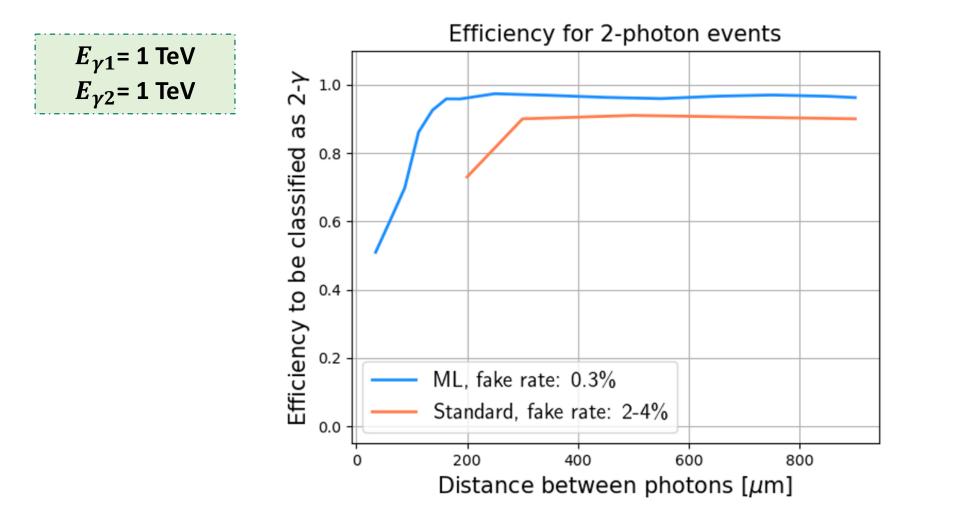

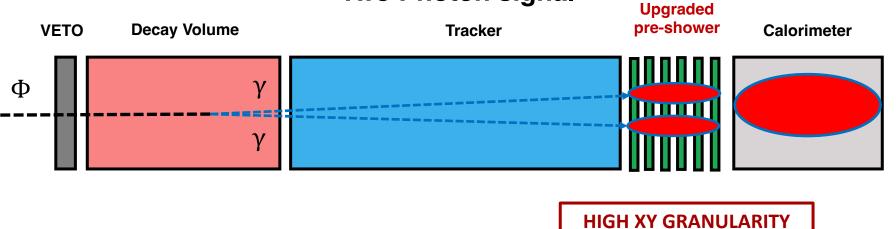

## What Are We Willing to Detect: Two Photon Signal

### **Two Photon signal**

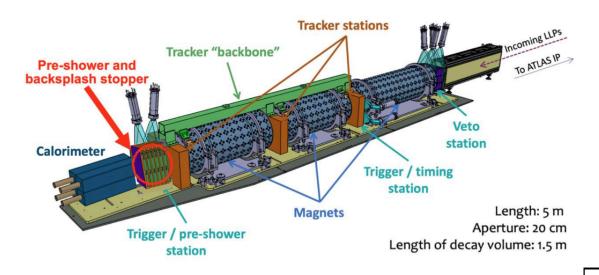

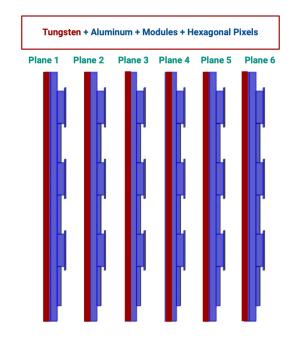

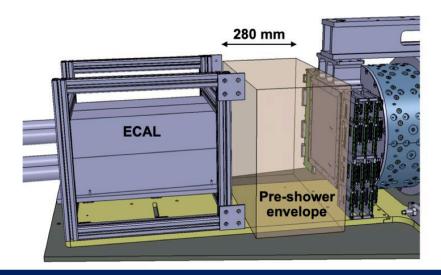

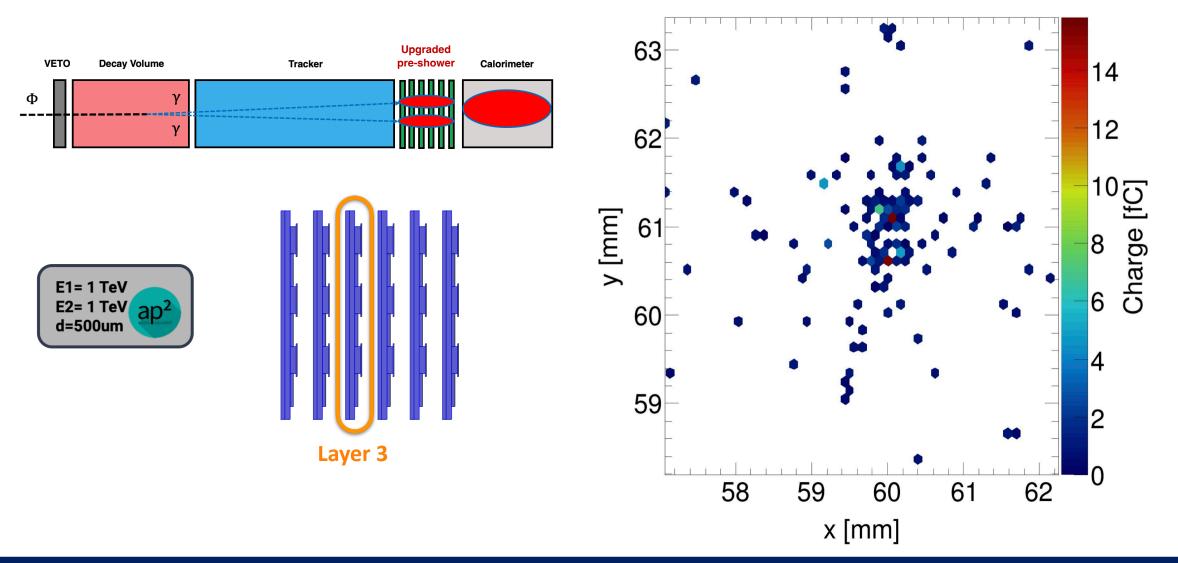

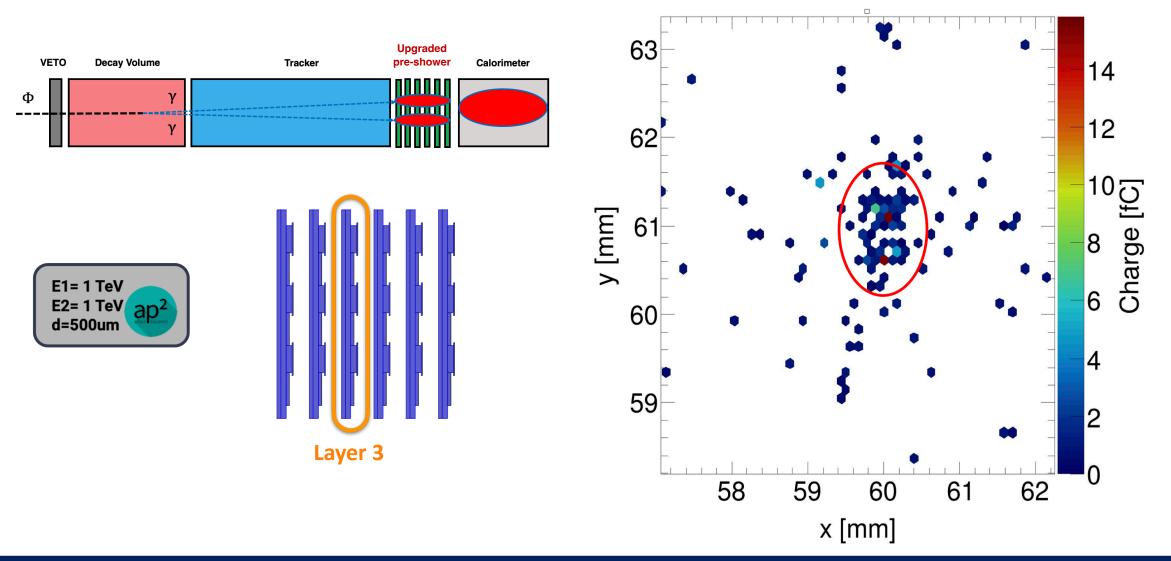

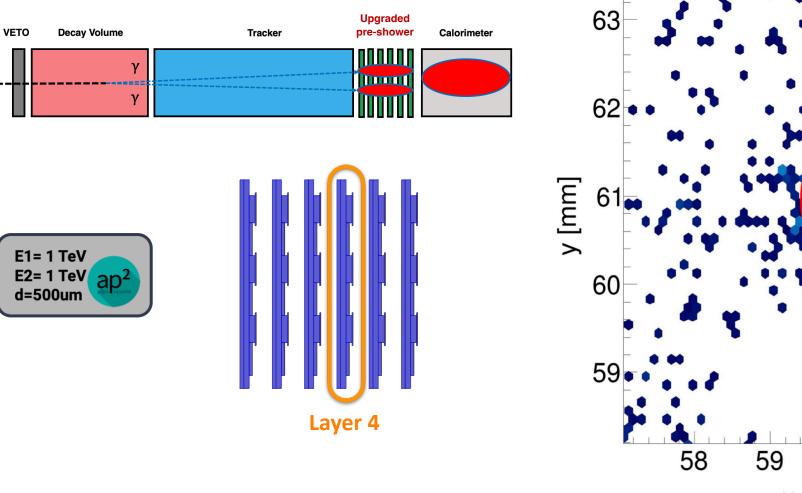

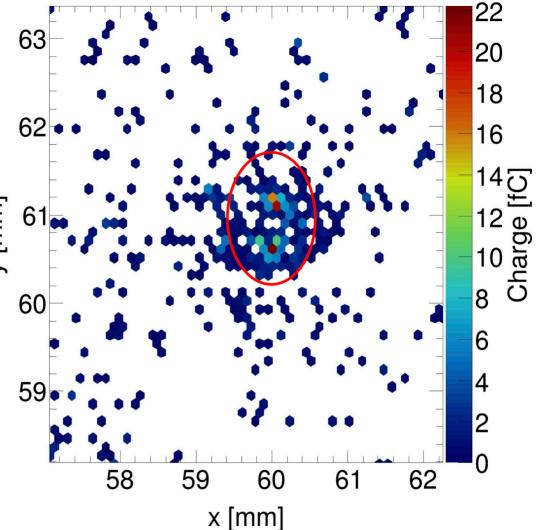

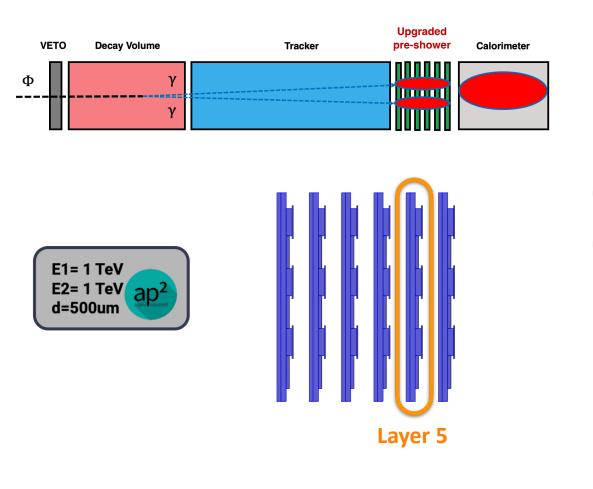

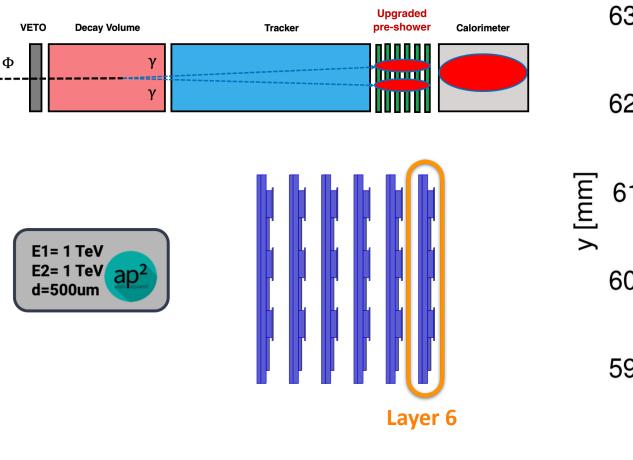

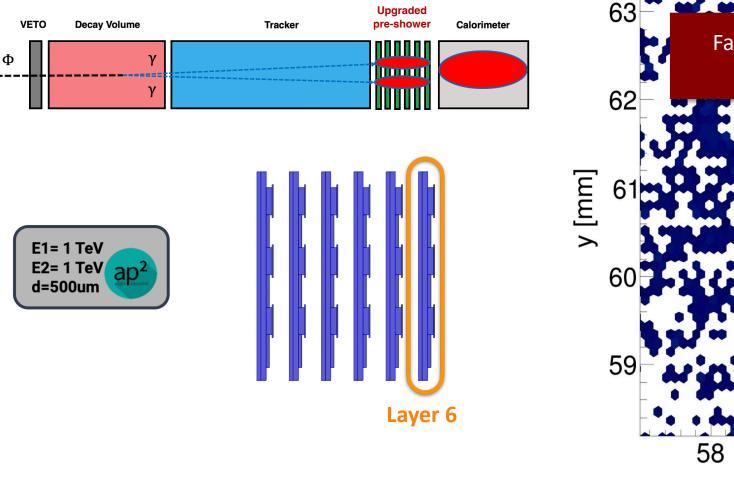

## **The FASER Pre-shower Detector Upgrade**

Main Challenge: Independent measurement of two very collimated high energy photons

### **Current preshower:**

2 layers of tungsten (1X0) + scintillating detectors → no XY granularity

### The upgrade:

- High granularity/high dynamic range pre-shower based on monolithic silicon pixels sensors

- Discriminate **TeV scale electromagnetic showers**

- Targeting data-taking during last year of LHC Run 3 and HL-LHC

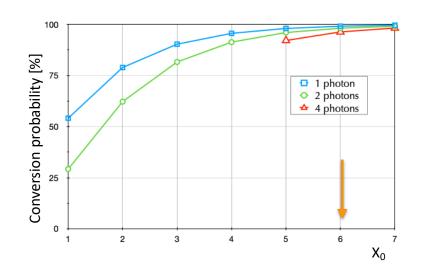

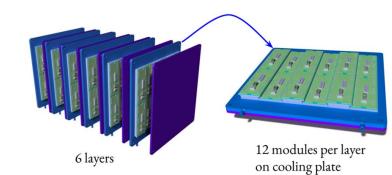

- 6 detector planes

- 6X<sub>0</sub> of tungsten in total

- One plane of **monolithic Si-pixel sensors** after each tungsten layer

2\*(1.70 X<sub>0</sub> of W + Si plane) + 4\*(0.65 X<sub>0</sub> of W + Si plane)

More tungsten in the first two layers to force early photon conversion

Φ

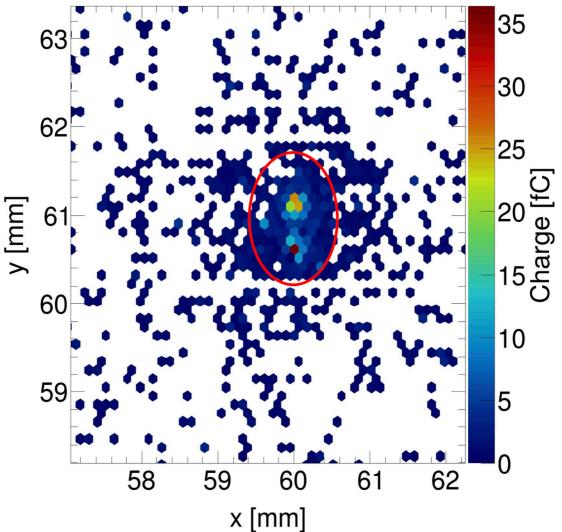

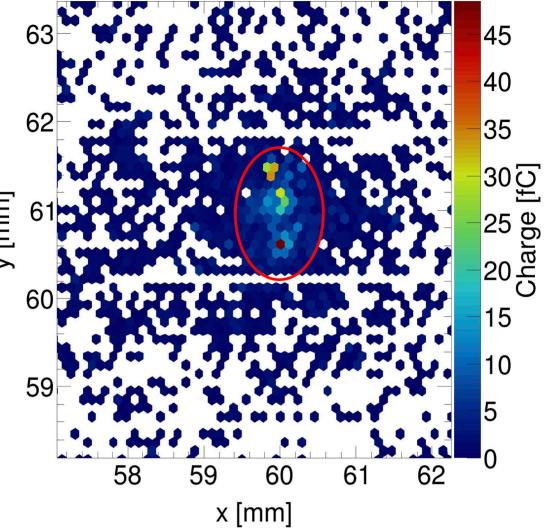

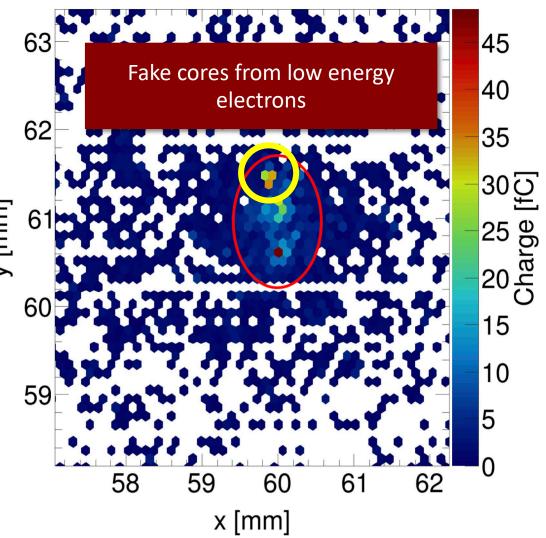

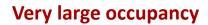

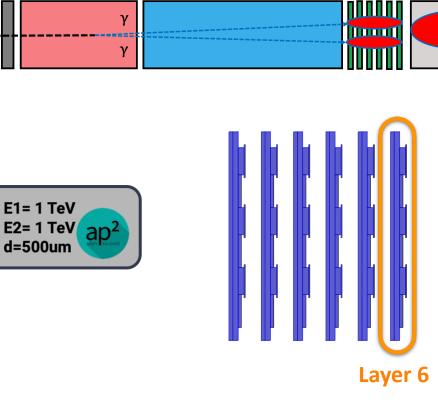

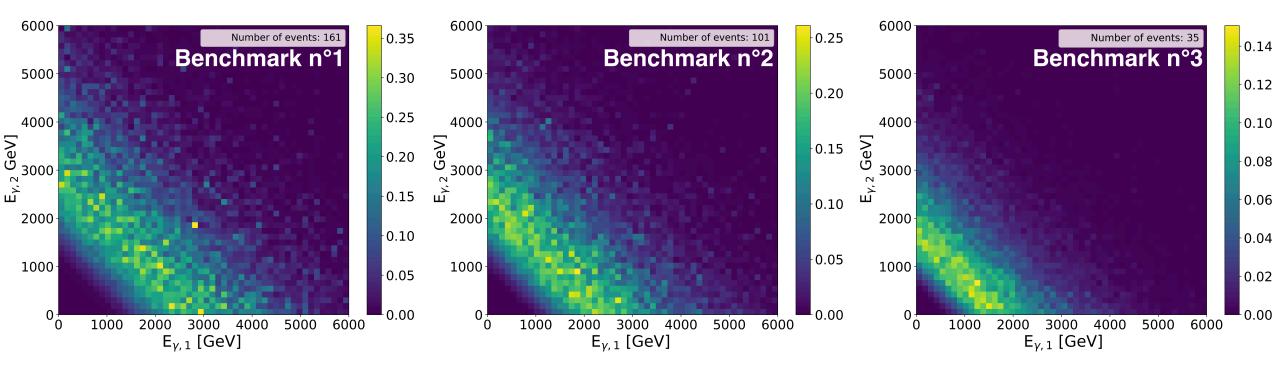

## **Pre-shower Simulation: Diphoton Signature**

### Why 6 planes? Why pixelated sensors?

Why 6 planes? Why pixelated sensors?

Why 6 planes? Why pixelated sensors?

VETO

Φ

**Decay Volume**

## **Pre-shower Simulation: Diphoton Signature**

Upgraded

pre-shower

Calorimeter

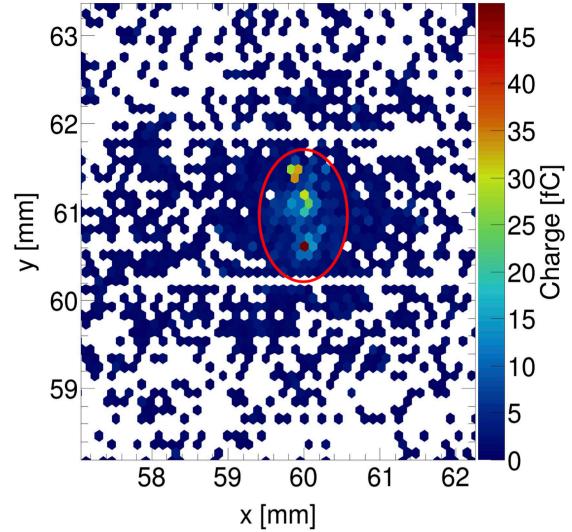

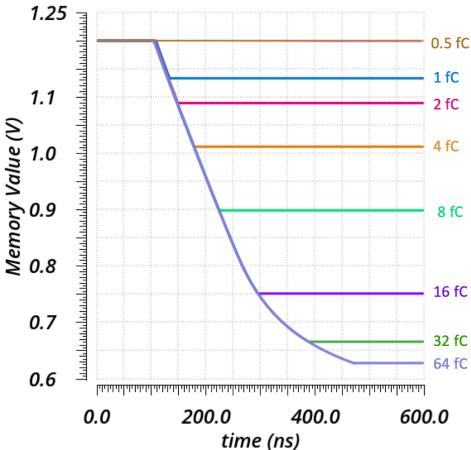

High dynamic range for charge measurements

Tracker

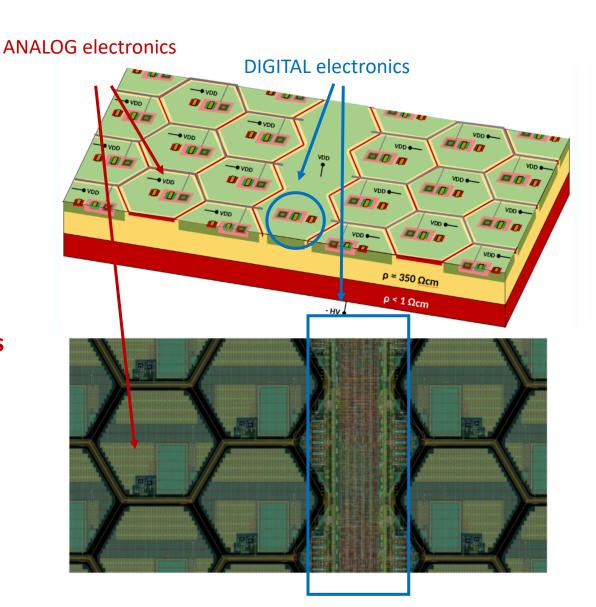

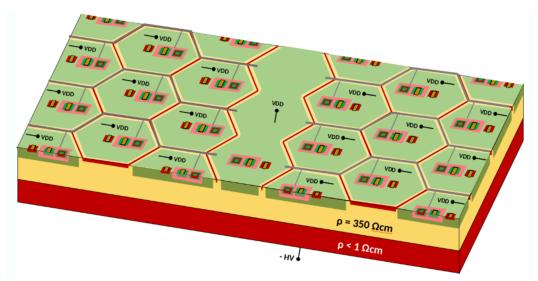

## **Monolithic Pixel ASIC: the Sensor**

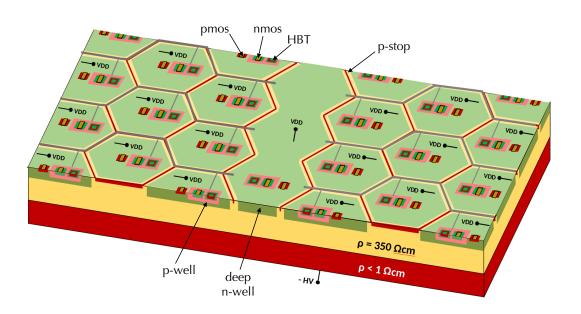

### Monolithic active pixel sensor

- 130 nm SiGe BiCMOS technology (SG13G2 by IHP microelectronics)

- High-resistivity (220  $\Omega$ cm) substrate, about 130  $\mu$ m thickness

- Hexagonal 65 μm side pixels integrated as triple well; 80fF pixel capacitance

- High dynamic range for charge measurement (0.5 ÷ 65 fC)

- Ultra fast readout with no digital memory on-chip (to minimize dead area)

- Local analog memories to store the charge

| Main specifications |                          |  |  |  |

|---------------------|--------------------------|--|--|--|

| Pixel Size          | 65 μm side (hexagonal)   |  |  |  |

| Pixel dynamic range | 0.5 ÷ 65 fC              |  |  |  |

| Cluster size        | O(1000) pixels           |  |  |  |

| Readout time        | < 200 µs                 |  |  |  |

| Power consuption    | < 150 mW/cm <sup>2</sup> |  |  |  |

| Time resolution     | < 300 ps                 |  |  |  |

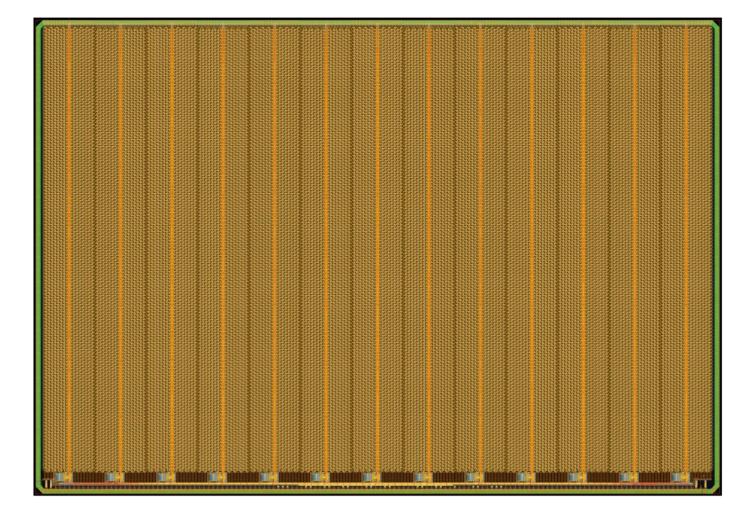

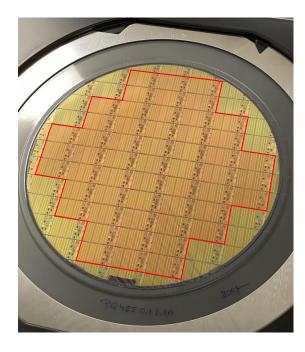

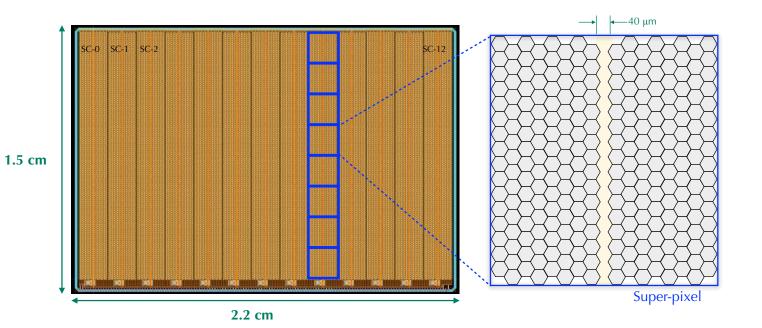

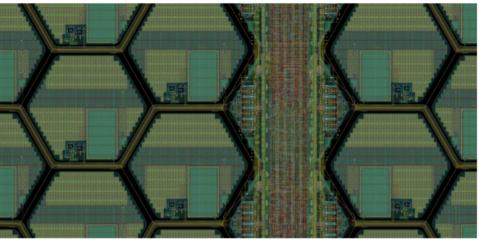

### Final Production Chip submitted in May 2023

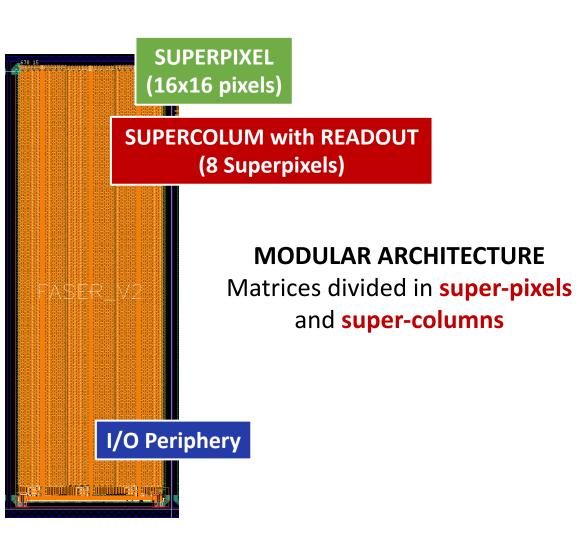

Chip size: 2.2 x 1.5 cm<sup>2</sup> with matrix of 208x128 pixels (26'624 pixels in total)

- Chip size: 2.2 x 1.5 cm<sup>2</sup> with matrix of 208x128 pixels (26'624 pixels in total)

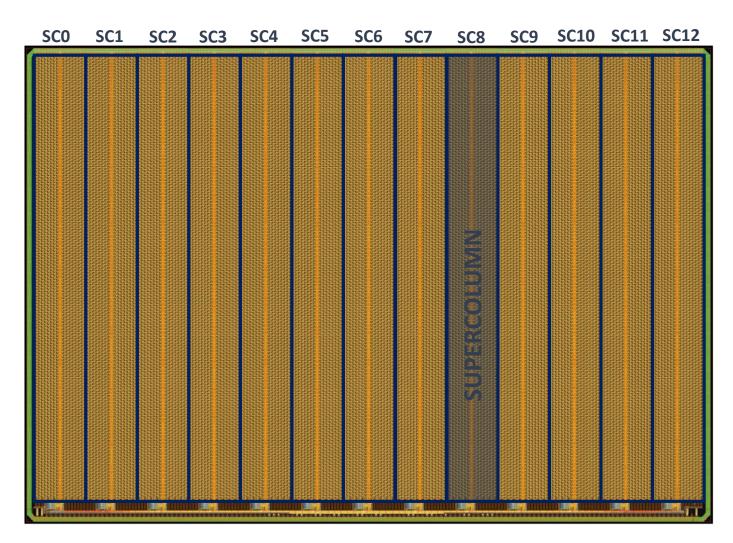

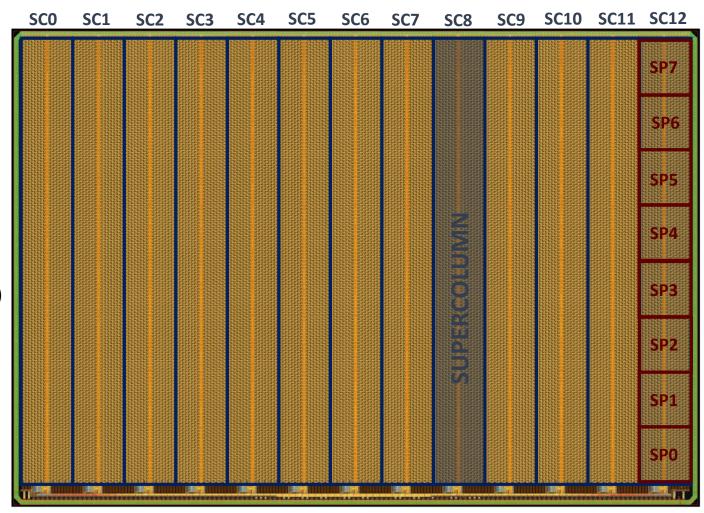

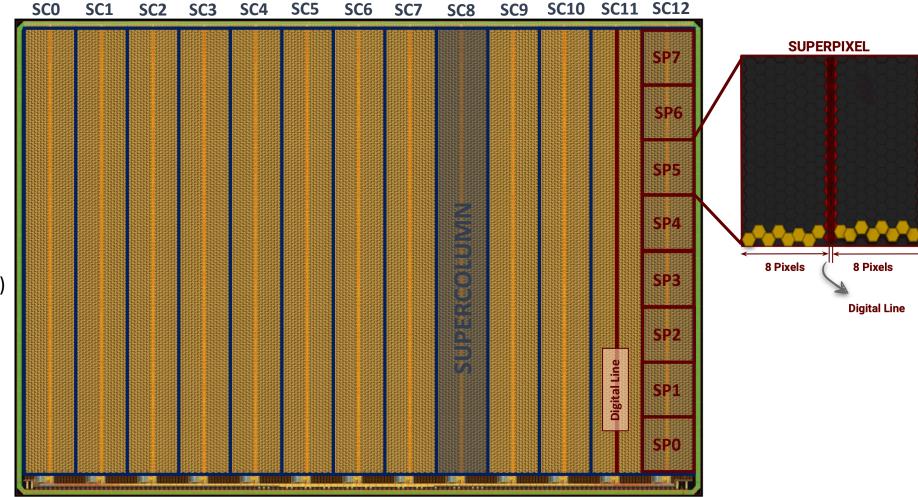

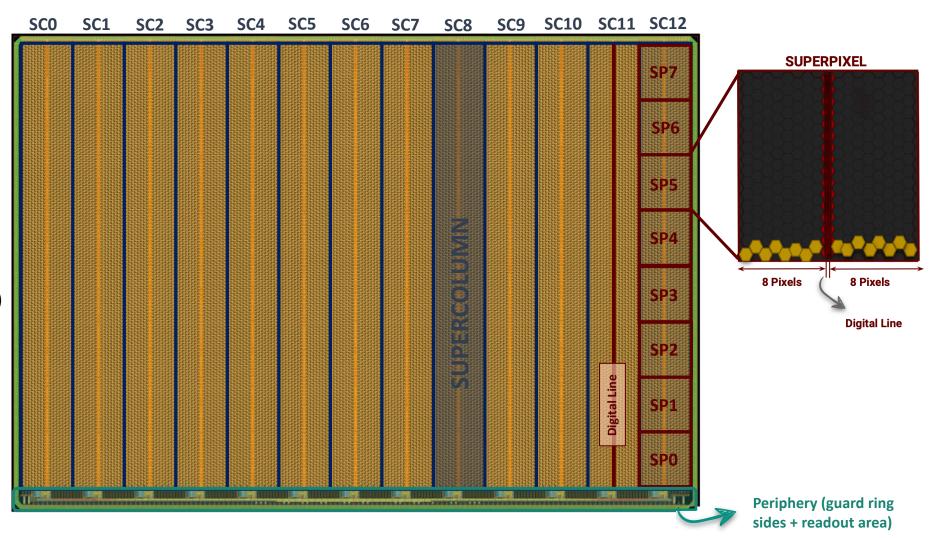

- 13 Supercolumns (SC)

- Chip size: 2.2 x 1.5 cm<sup>2</sup> with matrix of 208x128 pixels (26'624 pixels in total)

- 13 Supercolumns (SC)

- Each Supercolumn has 8

Superpixels (SP) (16x16 pixels)

- Chip size: 2.2 x 1.5 cm<sup>2</sup> with matrix of 208x128 pixels (26'624 pixels in total)

- 13 Supercolumns (SC)

- Each Supercolumn has 8

Superpixels (SP) (16x16 pixels)

- and 1 Digital Line (40 μm)

- Chip size: 2.2 x 1.5 cm<sup>2</sup> with matrix of 208x128 pixels (26'624 pixels in total)

- 13 Supercolumns (SC)

- Each Supercolumn has 8

Superpixels (SP) (16x16 pixels)

- and 1 Digital Line (40 μm)

- **Periphery** (I/O and arbitrary logic) with dead area

- 720 μm on the readout side

- 270 μm for the guard ring

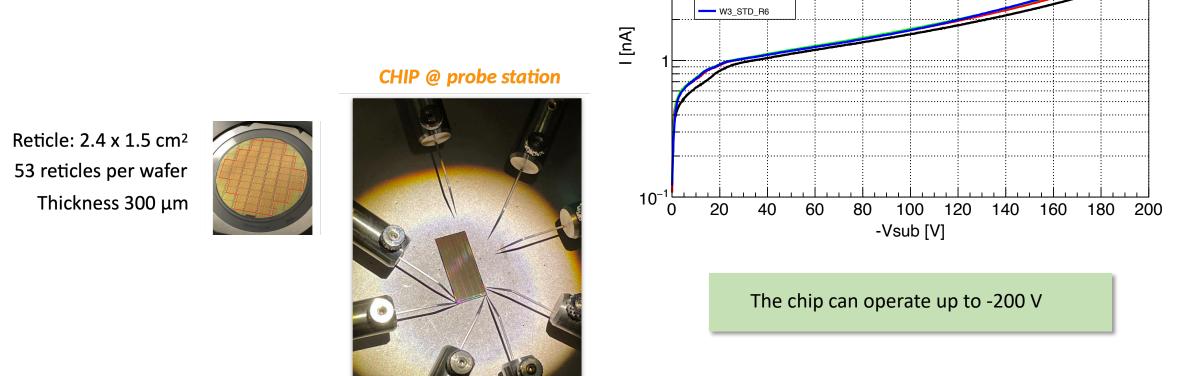

Reticle: 2.4 x 1.5 cm<sup>2</sup> 53 reticles per wafer Thickness 300 μm

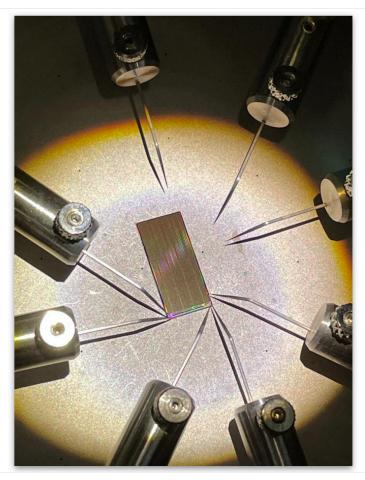

### **CHIP** @ probe station

#### Chiara Magliocca | SPS and ÖPG Annual Meeting 2023

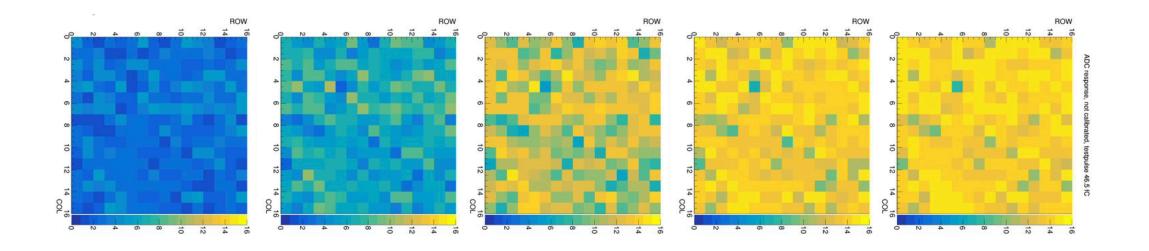

Study of the chip response for different value of injected charge (here one Superpixel)

Injected charge

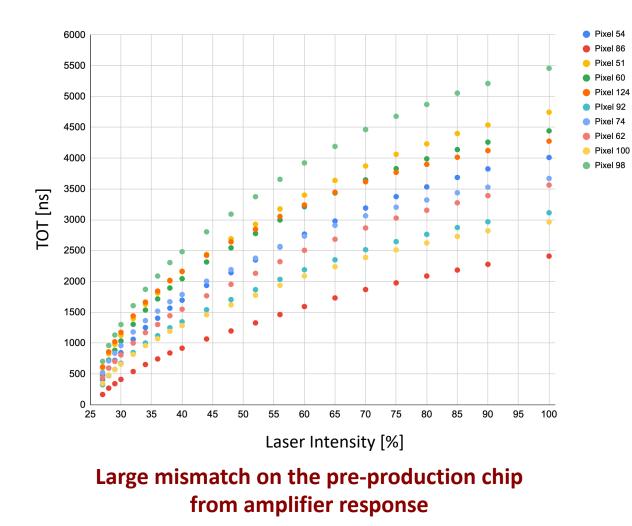

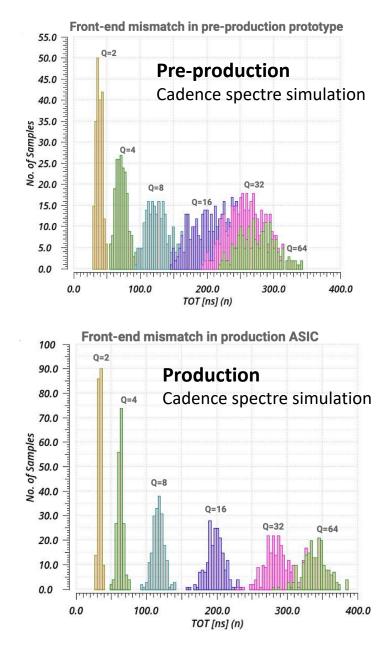

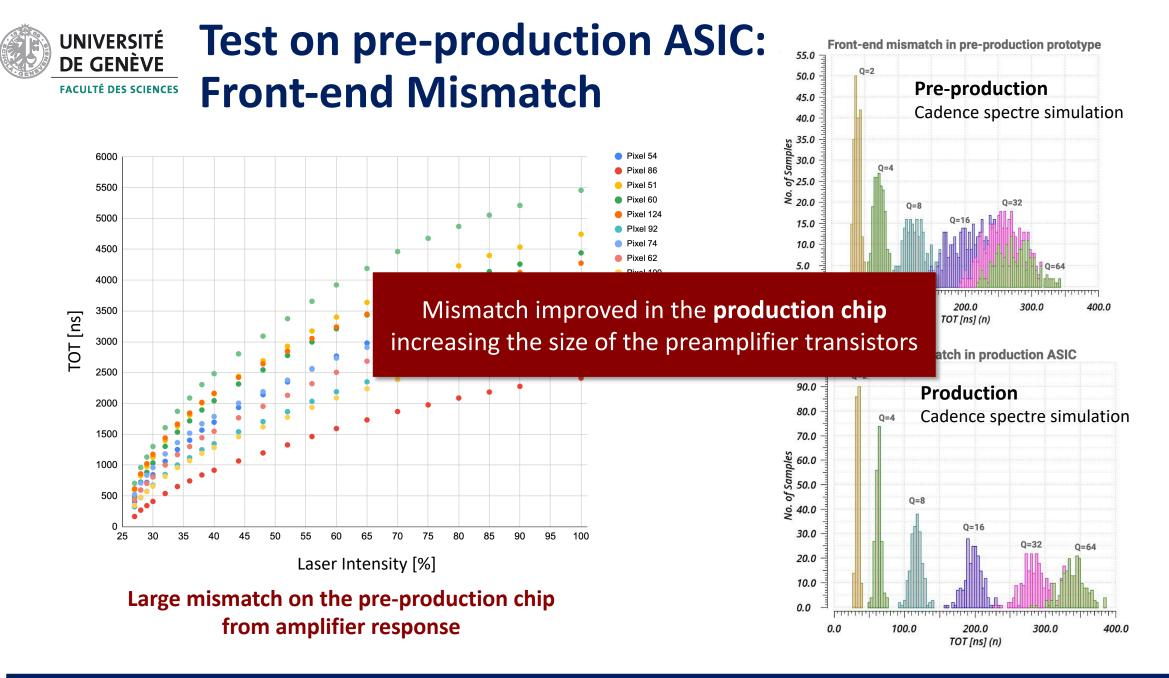

### **Test on pre-production ASIC Front-end Mismatch** FACULTÉ DES SCIENCES

- A new preshower detector is being developed for the FASER experiment at the LHC

- Enabling the discrimination of ultra-collimated TeV diphoton events from LLP decays

- 130 nm SiGe BiCMOS Technology MAPS designed and developed at the University of Geneva, with support from KIT and CERN

- Targeting installation in 2024 and data-taking during last year of LHC Run 3 and HL-LHC

- A new preshower detector is being developed for the FASER experiment at the LHC

- Enabling the discrimination of ultra-collimated TeV diphoton events from LLP decays

- 130 nm SiGe BiCMOS Technology MAPS designed and developed at the University of Geneva, with support from KIT and CERN

- Targeting installation in 2024 and data-taking during last year of LHC Run 3 and HL-LHC

- Pre-production chip delivered in June 2022

- Everything is working fine and we are finalizing the characterization in the Lab

- Minor bugs have been identified and corrections have been implemented in the production chip

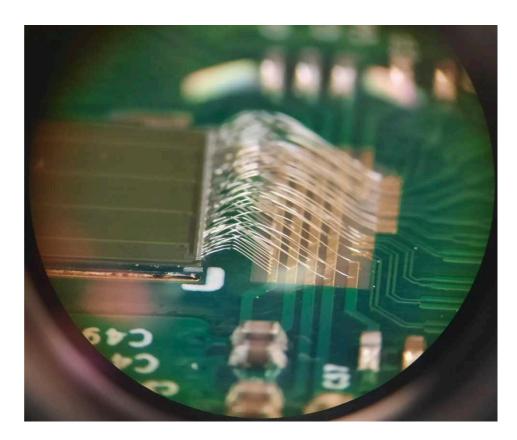

- First assembled modules currently ongoing

- A paper on the characterization of the pre-production chip will be published soon

- A new preshower detector is being developed for the FASER experiment at the LHC

- Enabling the discrimination of ultra-collimated TeV diphoton events from LLP decays

- 130 nm SiGe BiCMOS Technology MAPS designed and developed at the University of Geneva, with support from KIT and CERN

- Targeting installation in 2024 and data-taking during last year of LHC Run 3 and HL-LHC

### • Pre-production chip delivered in June 2022

- Everything is working fine and we are finalizing the characterization in the Lab

- Minor bugs have been identified and corrections have been implemented in the production chip

- First assembled modules currently ongoing

- A paper on the characterization of the pre-production chip will be published soon

- Final production chip submitted in May 2023

- Expected delivery: December 2023

- $\,\circ\,$  Test beam at SPS (CERN) planned for August 2024

### **The FASER Collaboration**

#### **FASER Collaboration Members**

Henso Abreu (Technion), John Anders (CERN), Claire Antel (Geneva), Akitaka Ariga (Chiba/Bern), Tomoko Ariga (Kyushu), Jeremy Atkinson (Bern), Florian Bernlochner (Bonn), Tobias Boeckh (Bonn), Jamie Boyd (CERN), Lydia Brenner (NIKHEF), Franck Cadoux (Geneva), Roberto Cardella (Geneva), Dave Casper (UC Irvine), Charlotte Cavanagh (Liverpool), Xin Chen (Tsinghua), Andrea Coccaro (INFN), Sergey Dmitrievsky (JINR), Monica D'Onofrio (Liverpool), Yannick Favre (Geneva), Deion Fellers (Oregon), Jonathan Feng (UC Irvine), Carlo Alberto Fenoglio (Geneva), Didier Ferrere (Geneva), Stephen Gibson (Royal Holloway), Sergio Gonzalez-Sevilla (Geneva), Yuri Gornushkin (JINR), Yotam Granov (Technion), Carl Gwilliam (Liverpool), Daiki Hayakawa (Chiba), Shih-Chieh Hsu (Washington), Zhen Hu (Tsinghua), Peppe Iacobucci (Geneva), Tomohiro Inada (Tsinghua), Luca Iodice (Geneva), Sune Jakobsen (CERN), Hans Joos (CERN), Enrique Kajomovitz (Technion), Hiroaki Kawahara (Kyushu), Alex Keykan (Royal Holloway), Felix Kling (DESY), Daniela Köck (Oregon), Umut Kose (CERN), Rafaella Eleni Kotitsa (Geneva), Susanne Kuehn (CERN), Thanushan Kugathasan (Geneva), Helena Lefebvre (Royal Holloway), Lorne Levinson (Weizmann), Ke Li (Washington), Jinfeng Liu (Tsinghua), Jack MacDonald (Mainz), Chiara Magliocca (Geneva), Josh McFayden (Sussex), Andrea Pizarro Medina (Geneva), Matteo Milanesio (Geneva), Theo Moretti (Geneva), Mitsuhiro Nakamura (Nagoya), Toshiyuki Nakano (Nagoya), Friedemann Neuhaus (Mainz), Laurie Nevay (Royal Holloway), Ken Ohashi (Bern), Hioki Rokujo (Nagoya), Elisa Ruiz Choliz (Mainz), Jorge Sabater-Iglesias (Geneva), Osamu Sato (Nagoya), Paola Scampoli (Bern), Kristof Schmieden (Mainz), Matthias Schott (Mainz), Anna Sfyrla (Geneva), Savannah Shively (UC Irvine), Yosuke Takubo (KEK), Noshin Tarannum (Geneva), Ondrej Theiner (Geneva), Eric Torrence (Oregon), Svetlana Vasina (JINR), Benedikt Vormvald (CERN), Di Wang (Tsinghua), Eli Welch (UC Irvine), Stefano Zambito (Geneva)

The development and construction of the W-Si pre-shower of the FASER experiment was funded by the Swiss National Science Foundation (SNSF) under the FLARE grant 20FL21-201474 at the University of Geneva. Additional financial contributions from KEK, Kyushu University, Mainz University, Tsinghua University and the Heising-Simons Foundation are also acknowledged

# Thank you !

### Chiara Magliocca chiara.magliocca@unige.ch

List of publications on the Preshower Upgrade:

- The FASER Detector 0 arXiv: 2207.11427: Accepted for publication in JINST

- The FASER W-Si High Precision Preshower Technical Proposal 0 CERN-LHCC-2022-006

- Measurements and analysis of different front-end configurations for 0 monolithic SiGe BiCMOS pixel detectors for HEP applications F. Martinelli et al 2021 JINST 16 P12038

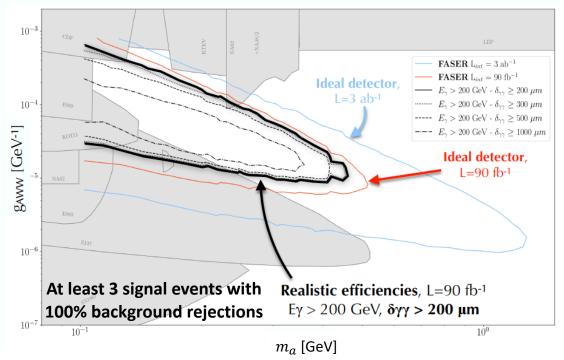

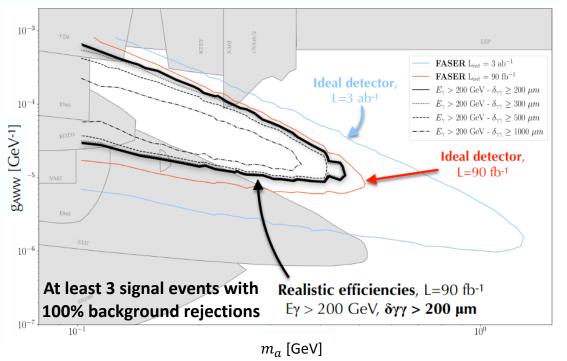

### **Discovery potential for ALP**

# BACKUP SLIDES

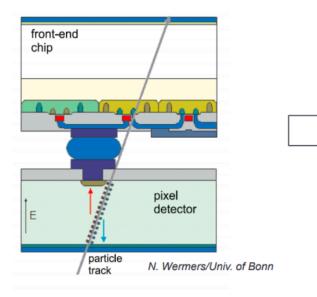

### **Hybrid VS Monolithic Pixel Detectors**

ATLAS

**Hybrid Pixel Detector**

FASER

#### Monolithic Pixel Detector (example)

### cost ratio

Readout chip : sensor chip : bump bonding  $\cong$  1:2:7

**PROS**: better optimization of sensors and electronics **CONS**: generally high production costs

Sensor integrated in the readout, only CMOS processing

**PROS**: lower production costs **CONS**: more difficult design

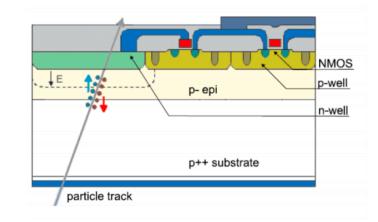

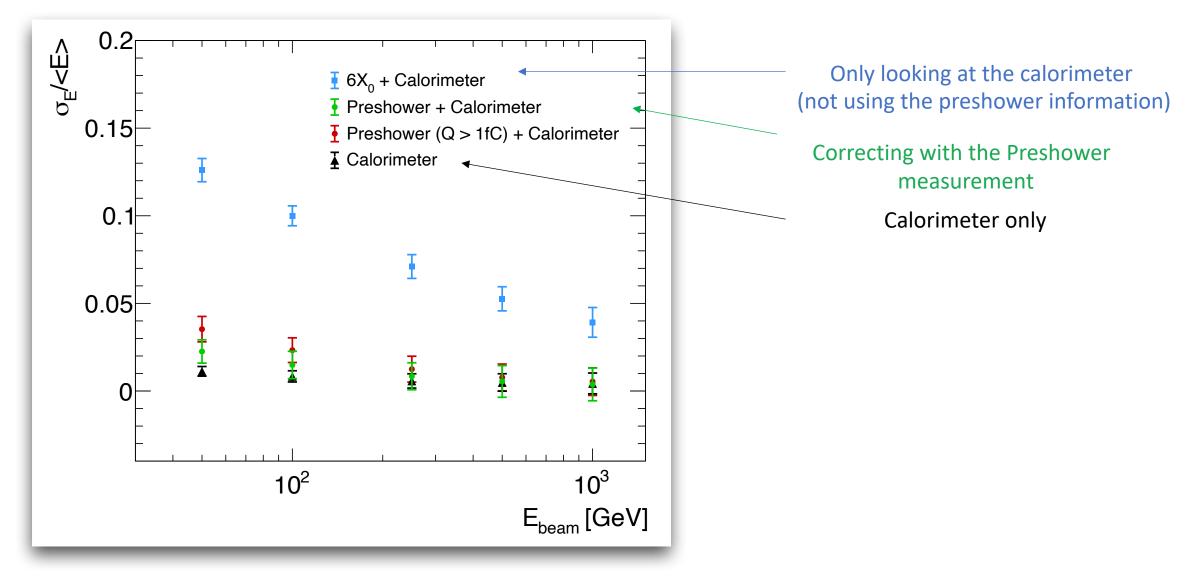

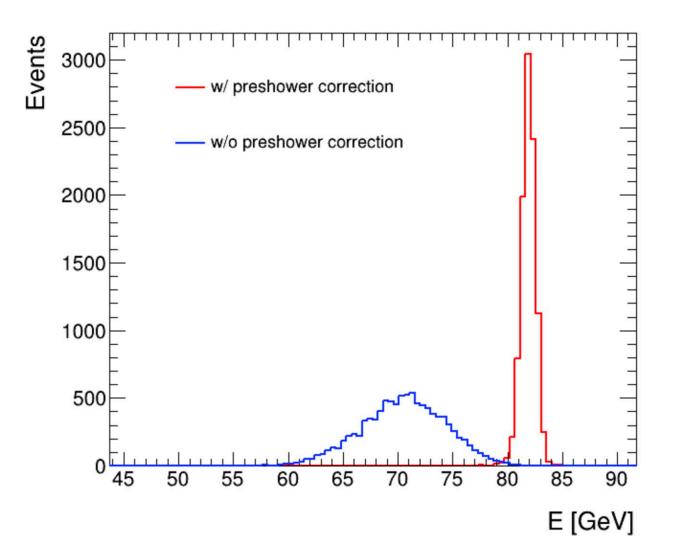

## **Energy resolution**

Chiara Magliocca | SPS and ÖPG Annual Meeting 2023

## **Energy resolution**

For 500 GeV photons

## **Motivations for a new pre-shower detector**

### Discovery potential for ALP

#### • Enables measurements:

- Axion-Like-Particles (ALP) produced via aWW coupling

- LLP with neutral pions in the final state

- Neutrino background suppression

#### Reinforces measurement:

- Dark photon and other LLPs decaying into charged fermions

- LLP with charge and neutral pions in the final state

Detector requirement: Discriminate photons down to 200 μm separation to exploit the full potential of the experiment

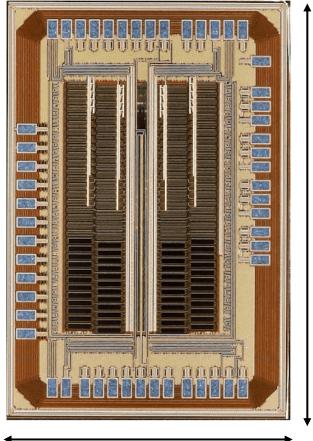

## The FASER Small Prototype Chip (2021)

F. Martinelli et al. 2021 J. Inst. **16** P12038 <u>https://doi.org/10.1088/174</u> 8-0221/16/12/P12038

<u>Purpose</u>

study **different level of INTEGRATION OF THE FRONT-END** electronics inside the sensitive area of the pixels

### Final aim

**identify the BEST FRONT-END CONFIGURATION** for the preproduction chip of the FASER Pre-shower (submitted in June 2021)

### 200 $\mu m$ x 50 $\mu m$ PIXELS

shape to reduce the electric field at the edge of the sensitive areas

Tested in 2021 2 superpixels

16x4 pixels each

1.7 mm

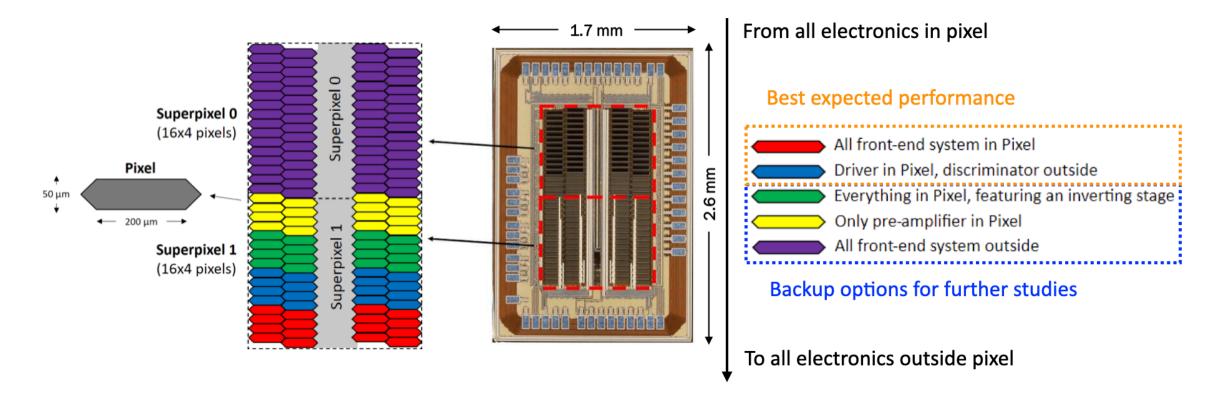

## **Small Prototype: Front-end Configurations**

F. Martinelli et al. 2021 J. Inst. **16** P12038 https://doi.org/10.1088/174 8-0221/16/12/P12038

### First chip prototype tested in 2021

- o designed to study different levels of integration of the front-end electronics

- o simultaneous goals: minimize dead area and routing capacitance, maximize stability

### **Small Prototype: Results and Comments**

F. Martinelli et al. 2021 *J. Inst.* **16** P12038 <u>https://doi.org/10.1088/174</u> 8-0221/16/12/P12038

All front-end system in Pixel

- Driver in Pixel, discriminator outside

- Everything in Pixel, featuring an inverting stage.

- Only pre-amplifier in Pixel

- All front-end system outside

| $\sigma_v [\mathrm{mV}]$ | $G_c$ [mV/fC]                                                    | ENC [e <sup>-</sup> ]                                                                                              | $\sigma_{V_{th}}  [\mathrm{mV}]$                                                                                            |

|--------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| $4.2 \pm 0.2$            | $159 \pm 1.0$                                                    | $165 \pm 9$                                                                                                        | 32.3                                                                                                                        |

| $2.5 \pm 0.1$            | $96.8 \pm 0.5$                                                   | 161 ± 9                                                                                                            | 26.9                                                                                                                        |

| $6.9 \pm 0.5$            | $179 \pm 1.0$                                                    | $241 \pm 19$                                                                                                       | 30.8                                                                                                                        |

| $3.8 \pm 0.2$            | $133.7 \pm 0.6$                                                  | $178 \pm 9$                                                                                                        | 23.4                                                                                                                        |

| $5.4 \pm 0.4$            | $148 \pm 1.0$                                                    | $228 \pm 20$                                                                                                       | 27.1                                                                                                                        |

|                          | $4.2 \pm 0.2$<br>$2.5 \pm 0.1$<br>$6.9 \pm 0.5$<br>$3.8 \pm 0.2$ | $4.2 \pm 0.2$ $159 \pm 1.0$ $2.5 \pm 0.1$ $96.8 \pm 0.5$ $6.9 \pm 0.5$ $179 \pm 1.0$ $3.8 \pm 0.2$ $133.7 \pm 0.6$ | $2.5 \pm 0.1$ $96.8 \pm 0.5$ $161 \pm 9$ $6.9 \pm 0.5$ $179 \pm 1.0$ $241 \pm 19$ $3.8 \pm 0.2$ $133.7 \pm 0.6$ $178 \pm 9$ |

Last two configurations represent a good compromise between *comptacness* and *performance*: adopted for the pre-production prototype

Chiara Magliocca | SPS and ÖPG Annual Meeting 2023

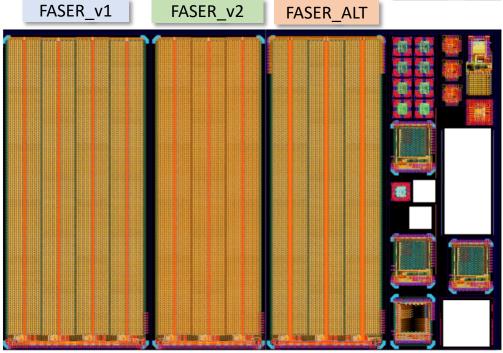

# **Pre-production Chip (2022)**

FASER\_v1 (baseline)

- o 4 supercolumns

- o in-pixel preamplifier and driver

- $\circ$  discriminator outside

#### FASER\_v2

- 128 x 48 pixels

- o 3 supercolumns

- all in-pixel (preamplifier, driver and discriminator)

#### FASER\_ALT

- 128 x 48 pixels

- o 3 supercolumns

- o no analog memories

- o counter for charge measurement

**Engineering run (IHP Microelectronics)** In each reticle three pixel matrices

#### Reticle: 2.4 x 1.5 cm<sup>2</sup>

53 reticles per wafer

Thickness 300 µm

# **Pre-production Chip (2022)**

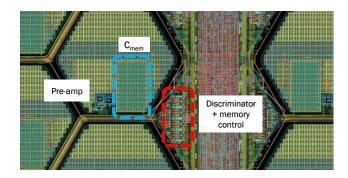

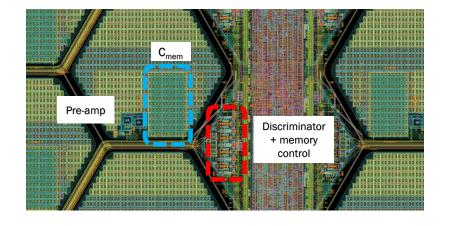

#### Chip organized in 13 Supercolumns, each with

- Active region, subdivided into 8 Superpixels of 16x16 pixels each

- $\circ$  Digital column (40  $\mu$ m) in the middle: sharing of digital electronics

#### Digital periphery on the bottom, and multiple guard-ring structures

#### Superpixel:

- 16 rows of 8+8 pixels

- Analog multiplexer

- o 4-bit flash ADC

- 3 FAST-OR lines

- Local bias circuit

- Programming logic to mask pixels

#### Dead area <5%

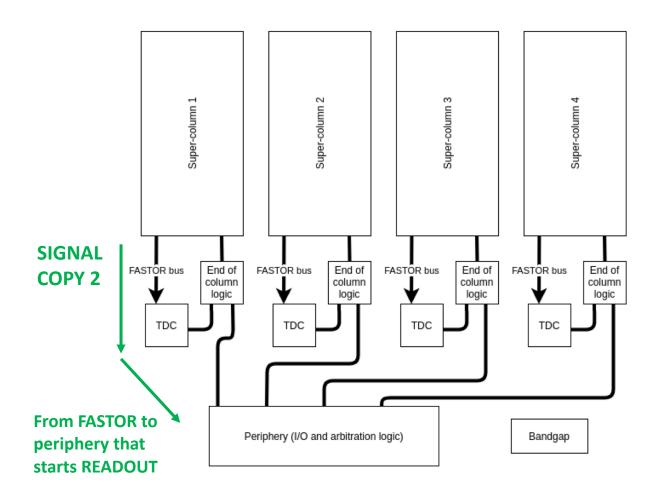

## **The Chip Architecture**

### **Sensor Cross Section**

- Low resistivity heavily p-doped substrate as a support

- Negative high voltage applied to the substrate

- High resistivity 50 µm epitaxial layer

- Triple well design

- Analog electronics inside the pixel

- Digital electronics outside the pixel

- Electronics inside the guard ring isolated from substrate using a deep n-well

- Digital electronics in a separate well

- Positive low voltage applied to pixels and electronics deep nwells

- $\approx$  6% dead area in the pixel matrix

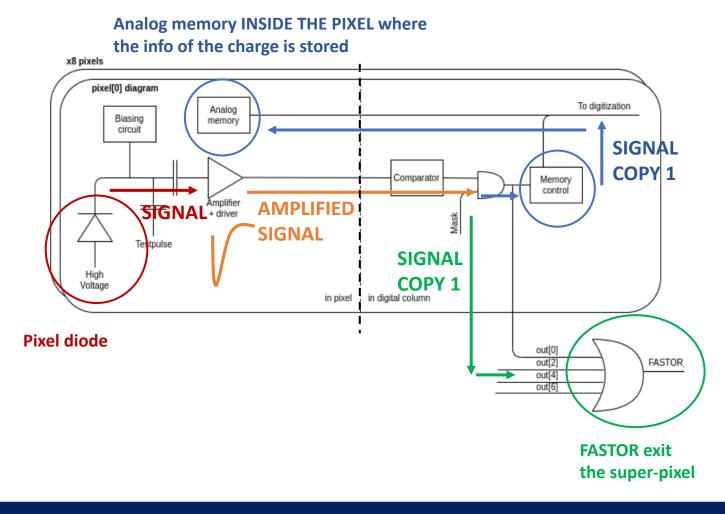

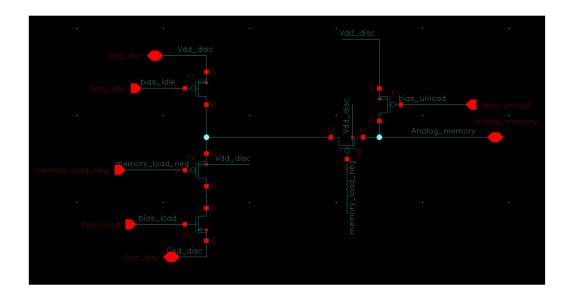

# **Monolithic Pixel ASIC: Pixel Circuitry**

- When an hit arrives a signal is produced

- The signal gets amplified by the PRE-AMPLIFIER

- The signal is sent ouside the pixel to the COMPARATOR

- The output of the comparator is copied:

- **COPY 1** goes to the MEMORY CONTROL

- **COPY 2** goes to the FAST-OR that will give the signal to start the Readout

- Memory Control loads the analog memory inside the pixel if the charge is over threshold

- After some delay, readout starts supercolumn

after supercolumn

## **ASIC Structure and Readout**

- A copy of the signal exit **IMMEDIATELY** the pixel through the FASTOR

- Each FASTOR send a signal to the perifery to start the READOUT

- To be sure we collected the charge entirely, the **perifery waits a bit before starting the READOUT**

- Readout time max 200 µs

- If in a super-pixel zero FASTOR are active, zero bit are sent to the periphery (optimization)

## **Pre-production ASIC Prototype: First Tests**

#### Wafers received in June 2022, tested in the laboratory

- I-V characteristics measured at probe station

- Charge response scrutinised with <sup>109</sup>Cd and IR laser

- Stress-tests for digital electronics and readout

10

FASER V1 W3

W3\_STD\_R1

W3\_STD\_R4

W3\_STD\_R5

# **The LHC Forward Physics**

- Most LHC detectors sensitive to transverse particles coming from head-on pp collisions

- Large forward cross section currently wasted and not probed

- Forward particles are highly collimated: only ~ 1cm spread for 100 m longitudinal travel

- A small detector far away could potentially see a large flux of Long-Lived Particles (LLPs) with very small background

- ForwArd Search ExpeRiment

- Proposal submitted in 2018 and approved by Cern in March 2019

### **Di-photon Signal Energy Distributions**

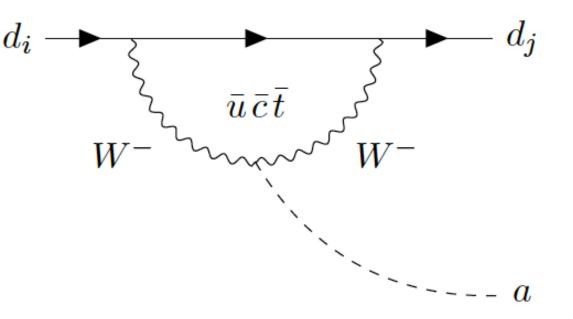

### **ALPs Production: FCNC**

- Down type quark becomes an up type quark

- Emits a charged boson which will itself radiate an ALP

- It then interacts with the up type quark which changes flavor again to become a down type quark

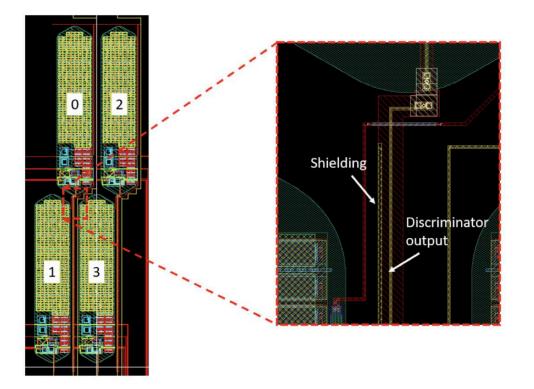

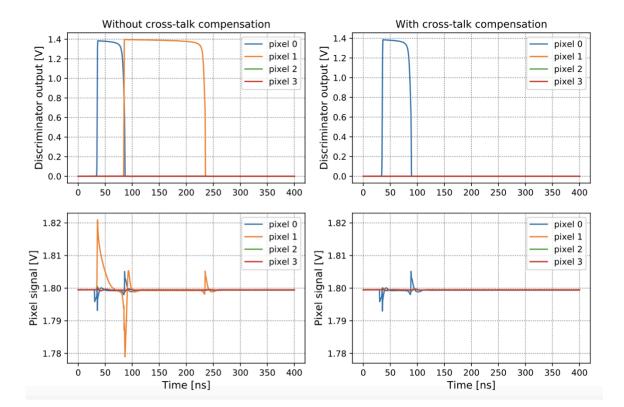

## **Signal Routing and Crosstalk Suppression**

Signal routed in a shielded bus to minimize crosstalk between neighboring pixels

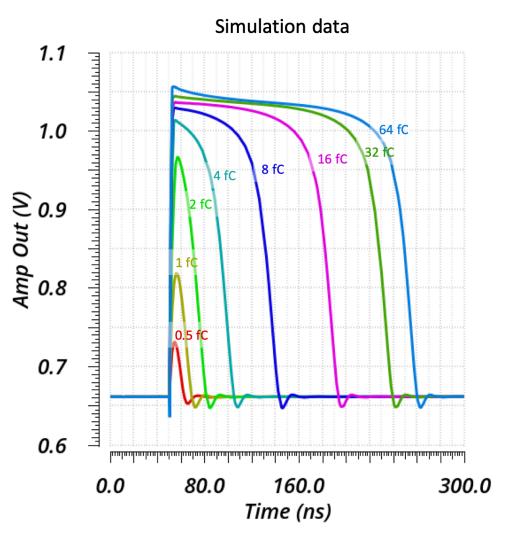

## **Amplification Stage**

- Since we want to measure high charges we convert the charge information to Time Over Threshold

- For different charges, if the charge increases also the TOT increases but not linearly (almost logarithmic relation)

- Saturation at 64 fC (intrinsic saturation of the pixel)

#### Chiara Magliocca | SPS and ÖPG Annual Meeting 2023

### **Memory Control and Analog Memories**

- When signal returns below threshold, memory is disconnected and left floating until read by the flash ADC

- o Current leakage even if the switch is opened

- $\circ$  It takes 200 µs to degradate the memory value of 30 mV (= 1 bin of our ADC)

After 200  $\mu$ s we still measure something but we are less precise

### **Di-Photon Reconstruction Efficiencies**