## Flexible Hough Transform FPGA Implementation for the ATLAS Event Filter. F. Alfonsi (INFN Italy)

- Number of simultaneous collisions (pile-up) per bunch crossing of 140-200. Peak luminosity is planned to reach 5-7.5 x 10<sup>34</sup> cm<sup>-2</sup> s<sup>-1</sup>

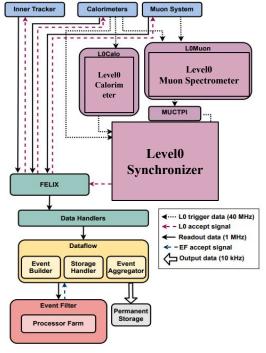

- 10 kHz of output data stream

- Proposed solution: hardware accelerator to filter ITk hits:

Event Filter Tracking;

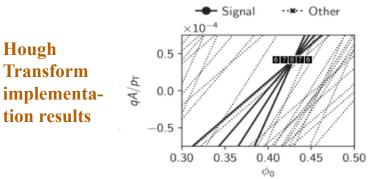

- Alveo U250 AMD accelerator card with ~20 % of resources occupied;

- Running frequency of 400 MHz;

Processing time per event: < 5 μs;</li>

- Processing time per event: < 3 μs,</li>

truth tracks preliminary

performance in  $\phi$  [0.3:0.5] rad;

| Region η  | μ        | $\pi$  |

|-----------|----------|--------|

| 0.1 - 0.3 | > 96.5 % | > 90 % |

| 0.7 - 0.9 | > 97 %   | > 82 % |