## The CMS Barrel Muon Trigger Layer-1 Processor

5.10.2023

3rd CERN System-on-Chip Workshop

CERN

Ioannis Bestintzanos, BMTL-1 team

BMTL-1

GMT

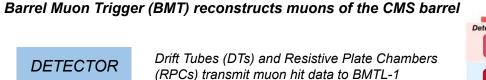

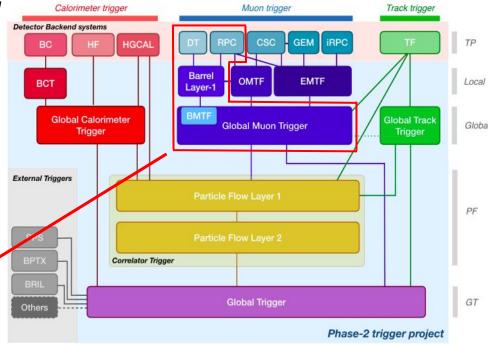

### Phase 2 Barrel Muon Trigger

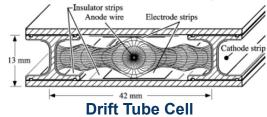

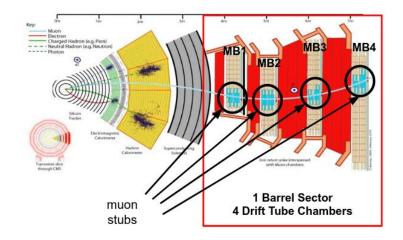

Builds DTs track segments and clusters RPC hits Merges both subsystem information into "super-primitives"

Matches track segments to reconstruct standalone muon objects

# Barrel Muon Trigger

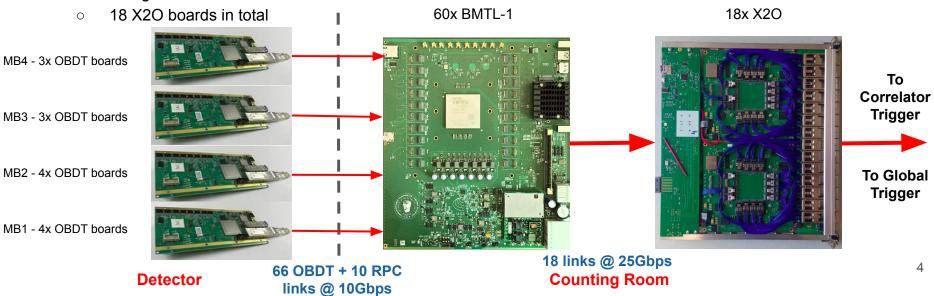

- On detector Board for Drift Tubes (OBDT) transmits detector data to BMTL-1

- Time digitization of DT signals

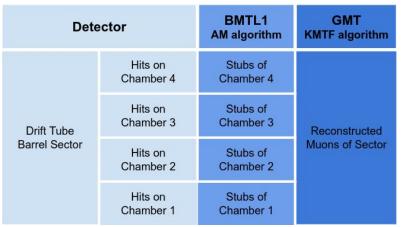

- BMTL-1 processes hit information to produce Muon stubs (track segments)

- Analytical Method (AM) algorithm processes TDC hits and generates Trigger Primitives

- Bunch crossing, Stub Position, Bending Angle

- Stubs of the 4 chambers are received by GMT

- Kalman Muon Track Finder (KMTF) algorithm matches tracks and reconstructs muon candidates

- Assigns position and momentum

- CMS Barrel Muon system consists of 60 DT sectors

- Each sector consists of 4 DT chambers

- OBDT boards transmit TDC hits to BMTL-1

- 14 OBDT boards per sector

- Every BMTL-1 board processes data from 2 Sectors

- 30 BMTL-1 boards needed for the whole barrel

- GMT receives primitives from BMTL-1

- Using TMT18

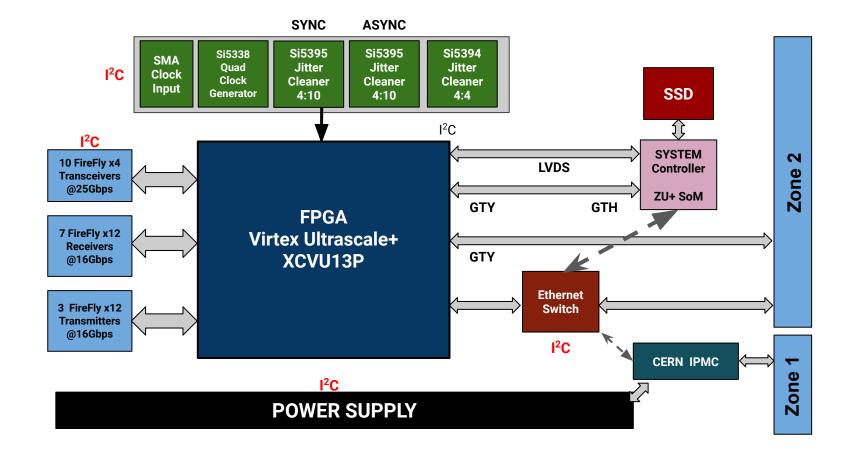

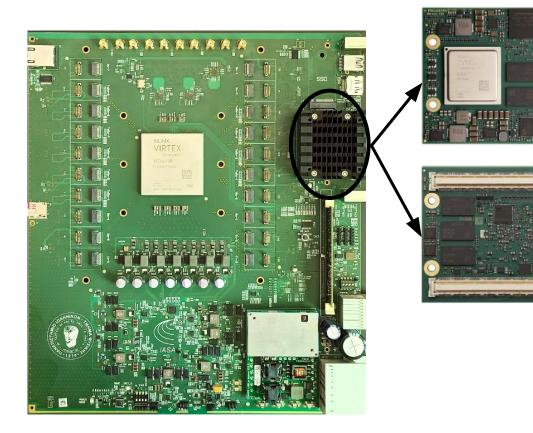

#### BMTL-1 ATCA board architecture

# FPGA / Connectivity

# Xilinx XCVU13P FPGA

- Ultrascale+ architecture  $\cap$

- 16 nm lithography Ο

- 4 SLRs (Super Logic Regions) 0

- 1.728.000 LUTs 0

- 3,456,000 Flip Flops Ο

- 12,288 DSP slices 0

- 128 GTY transceivers @ 28G Ο

- -1 speed grade Ο

#### **Optical connectivity**

- 40 RX @ 25 Gbps 10 x BiDir FireFly Modules 25G

- 40 TX @ 25 Gbps

- 80 RX @ 16 Gbps > 7 x Rx FireFly Modules 16G

- 36 TX @ 16 Gbps

- 3 x Tx FireFly Modules 16G

111 111 111 0 0  $\frown$ 20191123036 N35H64 18 616. 296 C 28 XCVU13P FPGA mounted on the BMTL-1 ATCA board Connector Zone 2 FPGA Ethernet Zone 2 SGMII Switch ZYNQ SoM IPMC Onboard Ethernet switch circuitry provides access to many subsystems on board

**120** RX + **76** TX ~ **3.9** *Tbps*

# System Controller

- Enclustra Mercury XU5

- XCZU5EV-1FSVC784E SoC

- 117k LUTs

- 234k Flip Flops

- 1248 DSP slices

- Zynq Ultrascale+ architecture

- Commercially available

- Quad core Arm Cortex A-53

- Capable of running Linux

- Independent RAM on PS & PL

- 2 GB (PS)

- 1 GB (PL)

- On module storage

- eMMC flash

- o QSPI

- Gigabit Ethernet (2x)

- Processor system

- Programmable logic

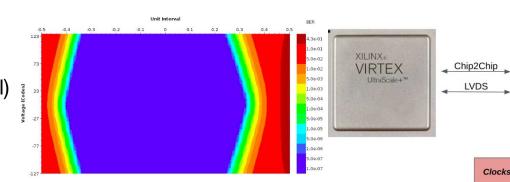

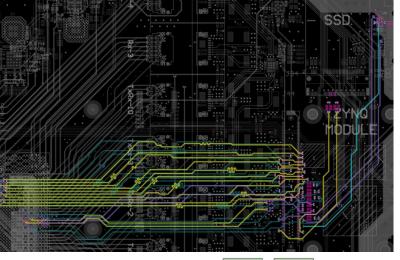

- Direct connections with the FPGA

- 4 GTH MGTs

- 10Gbps

- 1 MGT dedicated to Chip2Chip

- 20 LVDS pairs

- Length matched

- Suitable for high speed data transfer

- On board storage

- Solid State Drive

- SD card

- I2C

- Ethernet

- UART (front panel)

- USB 3.0

- Displayport

Optics

Power

Monitor

8

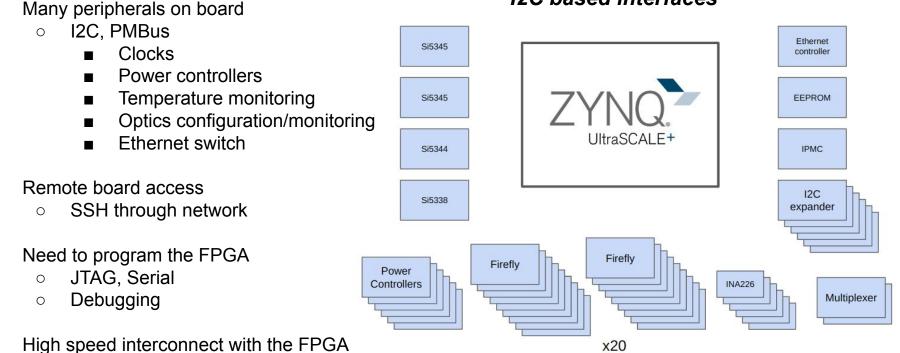

### Why use a SoC

#### **I2C based interfaces**

- AXI Memory Mapped bus

- Real time payload monitoring

#### **Firmware components**

- AXI chip2chip

- ZYNQ-FPGA

- Aurora 64b66b

- AXI firewall

- Debug bridge (XVC)

- FPGA programming

Utilization

LUT

FF

BRAM

DSP

10

GT

7%

13%

25

BUFG

ммсм

PLL

25%

50%

75

100

125

50

LUTRAM -

- Debug

- DDR4 MIG

- PL memory

- AXI interconnect

| • | CentOS operating system                                                                                                                                                                                | root@bmtl1-1:~ _ 🗖                                                                                                                                                                                                                                                                                              | × |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|   | • Runs on arm cores                                                                                                                                                                                    | File Edit View Search Terminal Help<br>[kadamidi@actrl-s1d06-43-01 ~]\$<br>[kadamidi@actrl-s1d06-43-01 ~]\$                                                                                                                                                                                                     |   |

| • | Configuration and monitoring of the on-board peripherals using Python scripts                                                                                                                          | [kadamidi@actrl-sld06-43-01 ~]\$ ssh root@192.168.7.10<br>root@192.168.7.10's password:<br>Last login: Thu Oct 5 01:40:24 2023 from 192.168.40.1                                                                                                                                                                |   |

|   | <ul> <li>Clock synthesizers</li> <li>Firefly modules</li> <li>Power modules</li> </ul>                                                                                                                 | BMTL1 ATCA rev. 0<br>///////////////////////////////                                                                                                                                                                                                                                                            |   |

| • | <ul> <li>Configuration and monitoring of FPGA using IPbus</li> <li>Software <ul> <li>EMPbutler SW to control the firmware framework</li> <li>"DTUP" SW to control the algorithm</li> </ul> </li> </ul> | VCCINT : 0.850 V, 8.663 A, 7.4 W<br>MGTAVTT : 1.199 V 9.190 A, 11.0 W<br>MGTAVCC : 0.897 V 3.390 A, 3.0 W<br>VCC3V3 : 3.301 V 4.495 A, 14.8 W<br>VCC1V8 : 1.795 V 3.750 A, 6.7 W<br>MGTVCCAUX : 1.799 V 0.048 A, 0.1 W<br>Board power : 43.2 W<br>FPGA power : 21.5 W<br>FPGA TEMP : 32.6 C<br>[root@bmtll-1~]# |   |

| • | <ul> <li>Xilinx Virtual Cable server</li> <li>JTAG access to VU13P</li> <li>Programming, ILAs, etc.</li> </ul>                                                                                         | [root@bmtl1-1 ~]#<br>[root@bmtl1-1 ~]#                                                                                                                                                                                                                                                                          |   |

#### • BMTL1 design is under revision

- Need arises mainly from parts becoming obsolete

- Changes in clocks, power supplies, etc.

- Halogen free material

#### Move to Xilinx Kria SoM

- Common across CMS trigger

- Reduce development effort

- Lower cost

- Move configuration commands to C++

- Deploy HERD server & plugin

- High level control of many boards

- BMTL1 ATCA board was designed, produced & tested

- ZYNQ SoM is used as the system controller

- Firmware & software developed to cover requirements

- Current setup has been proven successful in pp collisions slice test

# Thank you