# 28nm mixed-signal workshop

Alessandro Caratelli [CERN ASIC Support] CERN - Feb. 2023

## . Monday \_

- Technology Overview and designer's guidelines

Franco BANDI (CERN)

- Overview of the 28nm common design platform

Marco ANDORNO (CERN)

- Total lonizing Dose response of the 28nm technology

Giulio BORGHELLO (CERN)

Analog simulation with Explorer and Assembler in 28nm

Helga Dornelas

### LAB SESSION

Mixed-signal simulation analog-on-top Helga Dornelas

### LAB SESSION

## Tuesday

Mixed-signal simulation digital-on-top (in Xcelium) Helga Dornelas

LAB SESSION

- Analog Backend VXL Best Practices

Philippe Carriere

LAB SESSION

- IP block characterization Abstract generation

Philippe Carriere

LAB SESSION

DRC, LVS and Extraction using PVS

Philippe Carriere

LAB SESSION

## Wednesday \_

IP block characterization Timing models

Marco Andorno

LAB SESSION

- Digital-on-top flow introduction

Erwan Dekhil

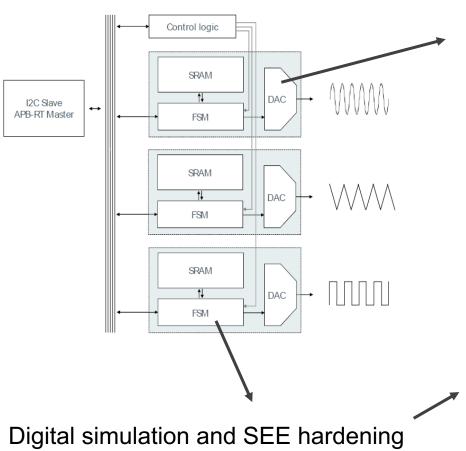

- Single event effects hardening in digital design

Alessandro Caratelli

LAB SESSION

Timing constraints and synthesis

Erwan Dekhil

LAB SESSION

Logic Equivalence Checking

Erwan Dekhil

LAB SESSION

## Wednesday \_

IP block characterization Timing models

Marco Andorno

### LAB SESSION

- Digital-on-top flow introduction

Erwan Dekhil

- Single event effects hardening in digital design

Alessandro Caratelli

### LAB SESSION

Timing constraints and synthesis

Erwan Dekhil

LAB SESSION

Logic Equivalence Checking

Erwan Dekhil

### LAB SESSION

## Thursday

- Block-level implementation

Erwan Dekhil

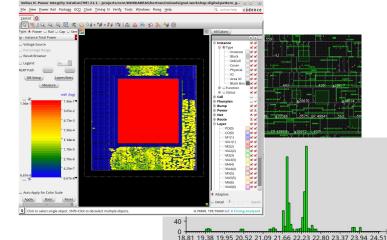

- Run implementation with Innovus

- Power planning

- Placement

- Timing analysis

- Synthesizing the clock tree

- Post CTS timing analysis and optimization

- Routing

### LAB SESSION

- Sygnoff implementation

Erwan Dekhil

- Post route and Signoff timing analysis

- Signoff power analysis

### LAB SESSION

### Friday

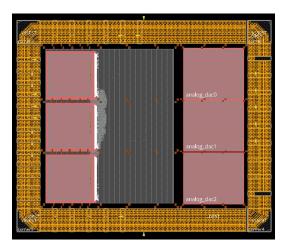

Top-level hierarchical implementation

Erwan Dekhil

- floor-planning and power planning

- Top level implementation

### LAB SESSION

- Top-level signoff analysis

Erwan Dekhil

- Top level signoff IR-drop analysis

- Top level signoff STA

- Top level export data for DRC/LVS

- Gate-level Simulation

- Merging top-level and block script

### LAB SESSION

# Lab sessions

Analog and Mixed-signal design

Digital block implementation and analysis

Analog IP-block characterization

## Top-level chip integration

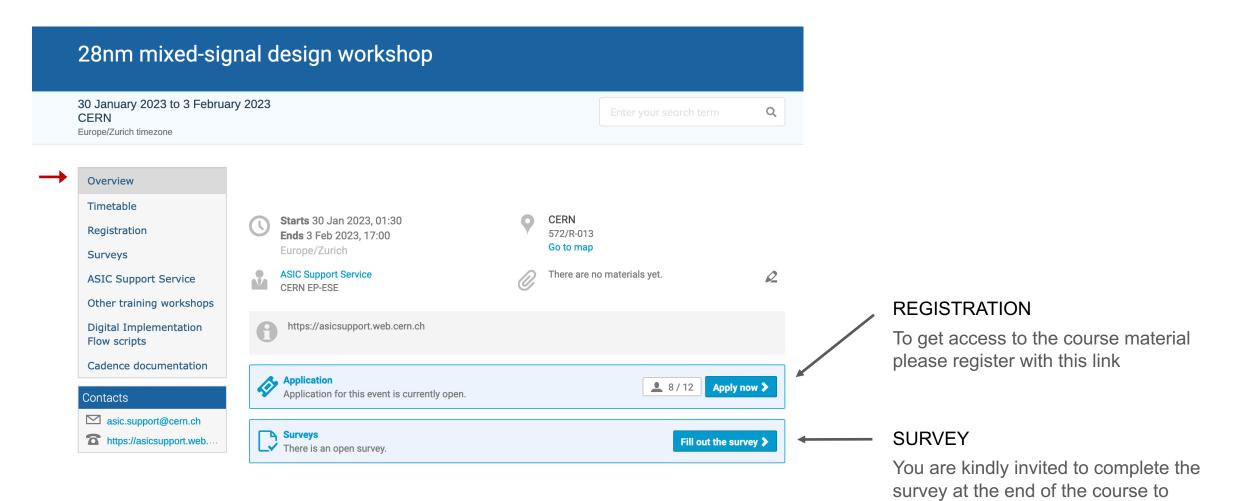

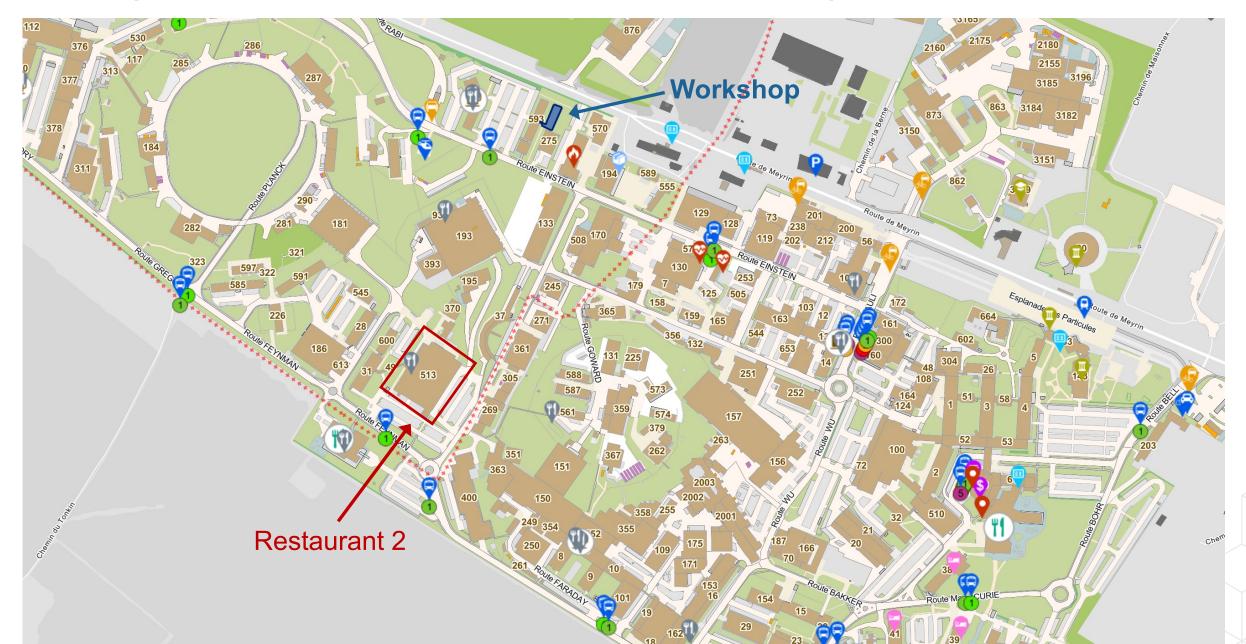

# Some practical information about the workshop

help us improving next session

Link to the workshop material: https://indico.cern.ch/e/28nm-workshop-1

5 © 2021 Cadence Design Systems, Inc. Cadence confidential.

# Some practical information about the workshop

| 28nm mixed-sig                                                                                                                                                                                                                                                                       | gnal des       | sign workshop                                                                                                                                                    |  |                                                 |                                                                                             |                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30 January 2023 to 3 Februa<br>CERN<br>Europe/Zurich timezone                                                                                                                                                                                                                        |                |                                                                                                                                                                  |  |                                                 | Q                                                                                           |                                                                                                                                                      |

| Overview<br>Timetable<br>Registration<br>Surveys<br>ASIC Support Service<br>Other training workshops<br>Digital Implementation<br>Flow scripts<br>Cadence documentation<br>Evaluation<br>Contacts<br>Main asic.support@cern.ch<br>Main asic.support@cern.ch<br>Main asic.support.web | 09:00<br>10:00 | ble<br>V01 Tue 31/01 Wed 01/02<br>gital design<br>Block-level implementation<br>572/R-013, CERN<br>Coffee break<br>572/R-013, CERN<br>Block-level implementation |  | Screen Detailed view Session legend Bertrand GE | Filter         X         NNERE         Ø9:00 - 10:15         L0:15 - 10:30         GENNERET | WORKSHOP MATERIAL DOWNLOAD<br>To download the slides and the lab<br>instruction to follow during the course<br>Material download is protected by NDA |

|                                                                                                                                                                                                                                                                                      | 11:00          |                                                                                                                                                                  |  |                                                 |                                                                                             |                                                                                                                                                      |

# Some practical information about the workshop

# Certificates

- Certificates of attendance will be distributed at the end of the course

- If you need a certificate for ECTS credits please contact asic.support@cern.ch

- 35h training course + mini-exam → usually recognized as 2 ECTS credits

# Training courses catalog

Digital-on-top hierarchical Implementation in workshop

## DoT Workshop (3 days)

- Learn the main concepts for designing in 65nm for the High energy Physics environment

- Learn the main concepts of the digital implementation from the synthesis, physical implementation and signoff (RTL to GDS)

- Perform synthesis, physical implementation and signoff steps

- Exercise bottom-up and top-down hierarchical design approaches

- Co-developed between CERN EP-ESE ASIC Support service and Cadence VCAD

### 2 TIMES PER YEAR FOR THE LAST 3 YEARS

Workshop on Mixed-Signal design in 28nm process

# Designing in 28nm

- Learn the main concepts for designing in 28nm for the High energy Physics environment

- Learn the main concepts of the digital implementation from the synthesis, physical implementation and signoff (RTL to GDS)

- Learn the main concepts of the analog and Mixed-Signal design in 28nm

- Learn main concepts about TIDs and SEUs tolerance design

- Co-developed between CERN EP-ESE ASIC Support service and Cadence VCAD

### **NEW - FIRST SESSION IN JANNUARY 2023**

System Verilog Advanced Verification Environment using UVM workshop

## Verification / UVM (3 days)

- Learn the main concepts of functional verification for the High energy Physics

- Learn the main concepts of digital design verification

- Learn about the Universal Verification Methodology (UVM)

- In the lab sessions you will learn how to build your own UVC and verification environment

- A Cadence Training Course adapted for the High Energy Physics community requirements

### 1 TIME PER YEAR

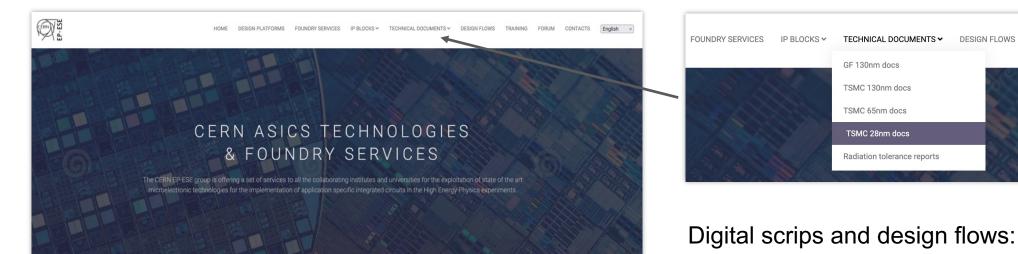

# 28nm Resources <a href="https://asicsupport.web.cern.ch">https://asicsupport.web.cern.ch</a>

$\bigcirc$

IP BLOCKS ACCESS

0

DESIGN FLOWS

https://gitlab.cern.ch/asic-design-support/digital-design-flows

ASIC Design Support > Digital design flows

DESIGN FLOWS

| Digital design flows (#)<br>Group ID: 169897            | New subgroup     New pro | ojeo          |                  |             |

|---------------------------------------------------------|--------------------------|---------------|------------------|-------------|

| Recent activity Merge Requests created<br>ast 30 days O | Issues created           | Members added |                  |             |

| Subgroups and projects Shared projects Arc              | Name ~                   | . 1           |                  |             |

| > Se H HEP-TSMC130 ⊕ Owner                              |                          |               | °•0 (Ĵ) 2 Å8 288 | *           |

| H HEP-TSMC65 🔂 Owner                                    |                          |               | °•0 (Ĵ) 2 Å8 288 | 0<br>0<br>0 |

| HEP-TSMC28                                              |                          |               | °•0 (Ĵ) 2 Å8 62  | •           |

| er en               |                          |               | °∙0 (Ĵ1 ĉ81      | •••         |

| > % H HEP-TPSCO65 ⊕                                     |                          |               | °•0 (Ĵ2 ĉ83      |             |

Developement and maintainance of the Provide technology and EDA tool Distribution and maintenance of HEP Prepare and distribute Digital and common Design Platforms support to designers in the HEP specific radiation tolerant macro Mixed-signal design flows of general community blocks and IPs 0 0 0 0 TRAINING CONTRACTS NDAS SILICON FABRICATION Organize and provide courses and Establish Commercial Contracts with Establish NDAs1 that allow for Organize & coordinate silicon workshop about 3 times per year silicon vendors collaborative work fabrication CONTACTS Foundry Services Design Flows Training Discourse Forum Contacts 469 Design Platforms CERN - EP-ESE - ASICs Technology Support and Foundry Services

0

TECHNCAL SUPPORT

0

COMMON DESIGN PLATFORMS

## 28nm Resources <a href="https://asicsupport.web.cern.ch">https://asicsupport.web.cern.ch</a>

#### DESIGN MANUALS AND GUIDELINES

March 2, 2022 Posted by CERN-EP-ESE ASICs Technology Support Service

Manuals, Foundry, Application Notes

In this section you can access the design manuals and PDK documentation

#### CONTINUE READING

#### LIMITED-ACCESS DOCUMENTS AND DESIGN GUIDELINES

➡ March 1, 2022 ▲ Posted by CERN-EP-ESE ASICs Technology Support Service

➡ Manuals, Foundry, Application Notes

In this section you can access the Limited Access documents and design guidelines

#### CONTINUE READING

#### CALIBRE DRC RULES

February 1, 2022

Posted by CERN-EP-ESE ASICs Technology Support Service

Manuals, Foundry, Application Notes

All Calibre DRC files are in the directory: \$PDK\_PATH/\$PDK\_RELEASE/pdk/1P9M\_5X1Y1Z1U\_UT\_AIRDL/cdsPDK /Calibre/drc For ease of updating, rule definitions and switches are kept in separate files, so that when a new rule update comes, there is no need to change the switches as well.

#### CONTINUE READING

#### CERN MSOA DESIGN KIT ACCESS AND INSTALLATION

🛱 January 1, 2022 💦 💄 Posted by CERN-EP-ESE ASICs Technology Support Service 👘 MSOA Design Kit

The HEP Common Design Platform is built by CERN EP-ESE in collaboration with Cadence around the 65nm foundry PDK to facilitate the collaborative work among the institutes, supporting the interoperability within the HEP community, avoiding incompatibilities across design teams.

#### CONTINUE READIN

Design Manuals And Guidelines

#### DESIGN MANUALS AND GUIDELINES

March 2, 2022 Posted by CERN-EP-ESE ASICs Technology Support Service Manuals, Foundry, Application Notes

#### In this section you can access the design manuals and PDK documentation

#### Main technology documents, design manuals and guidelines

Design Manual v2.0

Tapeout guidelines document

RC Extraction Guidelines

Sign-off Recommendation.pdf

Standard Cell Library Application Note

PDK usage introduction guide

#### Outline

Main technology documents, design manuals and guidelines Design Manual V2.0 Tapeout guidelines document RC Extraction Guidelines N2BHPO-S Sign-Off Recommendation.pdf Standard Cell Liburg Application Note TSMCN28 PDK usage introduction guide

February 1, 2022 Posted by CERN-EP-ESE ASICs Technology Support Service Manuals, Foundry, Application Notes

28nm Reliability Rules

CERN-EP Common Design Platform for the TSMC 65nm technology

1.1 Failure mechanism 1.2. Core devices gate oxide lifetime prediction 1.3. IO devices gate oxide lifetime prediction 1.4. Measurements conditions 1.4.1 Stress condition 1.4.2 Failure Criteria 2.1. Failure mechanism 2.2. DC Lifetime due to Hot Carrier Injection Effect 2.3. Measurements conditions 2.4.1 Stress condition 2.4.1 Failure Criteria 3.1. Failure mechanism 3.2. DC Lifetime due to Negative / Positive Bias Temperature Instability 3.2.1 PMOS DC Lifetime due to Negative Bias Temperature Instability (NBTI) 3.2.2 NMOS DC Lifetime due to Positive Bias Temperature Instability (PBTI) 3.3. Measurements conditions 3.3.1 Stress condition 3.3.2 Failure Criteria

Outline

### 1. Gate Oxide Lifetime prediction

click here to visit the related dicourse topic for more info and discussions

#### 1.1 Failure mechanism

28NM RELIABILITY RULES

When an electron current is passed through gate oxide, defects such as electron traps, interface states, positively charged donor-like traps, and so on, gradually build up in the gate oxide until a conduction path is formed, followed by thermal run away. According to the anode hole injection model, injected electrons generate holes at the anode that can tunnel back inthe oxide. Intrinsib treakdown occurs when a critical hole density is reached.

#### 1.2. Core devices gate oxide lifetime prediction

11 © 2021 Cadence Design Systems, Inc. Cadence confidential.

## Resources

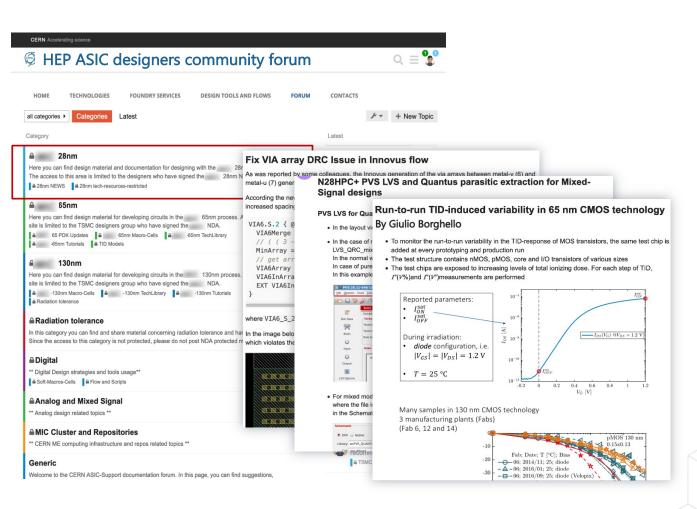

## The HEP designers forum

a place where to share information and search solutions

## https://asicsupport-community.web.cern.ch

- Design and EDA tools Tutorials

- Additional documentation

- Design practices suggestions

- Exchange of information

- Everybody can benefits from the findings, solutions and scripts of the others without having to deal with the same issues

- 28nm dedicated section

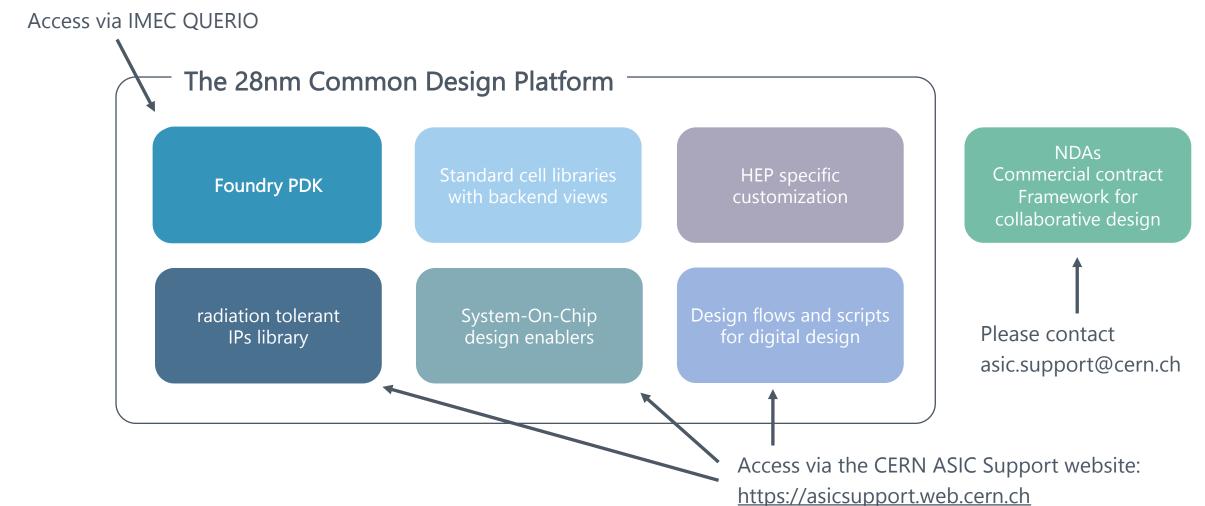

# 28nm HEP Common Design Platforms

An integrated solution that provides the essential instruments, blocks and experience to facilitate the ASICs collaborative design work in 28nm.

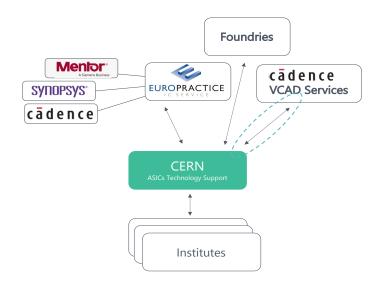

# The CERN ASIC Support Service

Promote the collaborative works and knowledge sharing

Provide support to HEP community for technology and EDA tool usage

Enhance, update and maintain the PDKs for commonly used technologies in HEP environment

Develop and distribute the Common Design Platforms for mixed-signal ASICs design

Distribution and maintenance of common macro blocks

Preparation and maintenance of design flows of general use

Organize training workshops for HEP specific

CORE TEAM: Marco Andorno, Wojciech Bialas, Alessandro Caratelli, Kostas Kloukinas CONTACTS: <u>asic.support@cern.ch</u>

# The CERN Foundry Service

Establish Commercial Contracts with silicon vendors

Establish NDAs that allow for collaborative work

Organize & coordinate silicon fabrication

For silicon fabrication services (MPWs, engineering & production runs) please contact <u>foundry.services@cern.ch</u>

CORE TEAM: Kostas Kloukinas, Maxence Ledoux, Cinzia Pinzoni CONTACTS: <u>foundry.services@cern.ch</u>

# **Technical support**

You can contact <u>asic.support@cern.ch</u> for requests related to:

- Support for the EDA tools usage, Design Flows and the Design Kits

- Support for design specific issues

- Distribution of shared IP blocks (and assistance for design integration).

- Administrative requests (process of signing NDAs, technology information access, PDK requests).

If you are in need of specific design assistance and implementation or verification tasks, please contact instead the chips.service@cern.ch If needed for solving your issue, we can as well:

- put you in contact with CERN designers with experience in the field

- Involve CADENCE VCAD Service with which we have a support contract in place