# Development of monolithic pixel sensor prototypes for the CEPC vertex detector

## Ying Zhang & Wei Wei

On behalf of the CEPC Vertex detector study team

\*Institute of High Energy Physics, Chinese Academy of Sciences

The Circular Electron Positron Collider (CEPC) is a large international scientific facility proposed by the Chinese particle physics community in 2012.

- Efficient tagging of heavy quarks (b/c) and  $\tau$  leptons

- → Excellent impact parameter resolution,

$$\sigma_{r\emptyset} = 5 \oplus \frac{10}{(p \cdot \sin^{3/2}\theta)} (\mu m)$$

## Baseline design parameters for CEPC VTX

|         | D ( )   | 1.17. 3 | 1 01            | ( )             |

|---------|---------|---------|-----------------|-----------------|

|         | R  (mm) | z  (mm) | $ \cos \theta $ | $\sigma(\mu m)$ |

| Layer 1 | 16      | 62.5    | 0.97            | 2.8             |

| Layer 2 | 18      | 62.5    | 0.96            | 6               |

| Layer 3 | 37      | 125.0   | 0.96            | 4               |

| Layer 4 | 39      | 125.0   | 0.95            | 4               |

| Layer 5 | 58      | 125.0   | 0.91            | 4               |

| Layer 6 | 60      | 125.0   | 0.90            | 4               |

|         |         |         |                 |                 |

##

Ref: CEPC Conceptual Design Report, Volume II - Physics & Detector

#### **Sensor specifications**

Small pixel  $\sim 16 \, \mu m$ Thinning to  $50 \, \mu m$ low power  $50 \, mW/cm^2$ fast readout  $\sim 1 \, \mu s$ radiation tolerance  $\leq 3.4 \, Mrad/year$   $\leq 6.2 \times 10^{12} n_{eq}/(cm^2 \, year)$

## Main specifications of the full-scale chip

#### Bunch spacing

Higgs: 680 ns; W: 210 ns; Z: 25 ns

> Max. bunch rate: 40 M/s

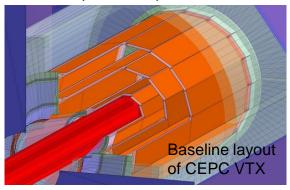

#### Hit density

2.5 hits/bunch/cm² for Higgs/W; 0.2 hits/bunch/cm² for Z

#### Cluster size: ~3 pixels/hit

Epi-layer thickness: ~18 μm

Pixel size: 25 μm × 25 μm

#### Hit Density vs. VXD Radius

Ref: CEPC Conceptual Design Report, Volume II

| For Vertex  | Specs   | For High rate<br>Vertex | Specs.                                | For Ladder<br>Prototype | Specs.                                 |

|-------------|---------|-------------------------|---------------------------------------|-------------------------|----------------------------------------|

| Pixel pitch | ≤ 25 µm | Hit rate                | 120 MHz/chip                          | Pixel array             | 512 row x 1024 col                     |

| TID         | >1 Mrad | Data rate               | 3.84 Gbpstriggerless ~110 Mbpstrigger | Power<br>Density        | < 200 mW/cm <sup>2</sup> (air cooling) |

|             |         | Dead time               | < 500 ns<br>for 98% efficiency        | Chip size               | ~1.4 × 2.56 cm <sup>2</sup>            |

## TaichuPix prototypes overview

- Motivation: a large-size & full functionality pixel sensor for the first 6-layer vertex detector prototype

- Major challenges for design

- Small pixel size → high resolution (3-5 µm)

- → High readout speed (dead time < 500 ns @ 40 MHz ) → for CEPC Z pole

</p>

- Radiation tolerance (per year): 1 Mrad TID

- Completed 3 rounds of sensor prototyping in a 180 nm CMOS process

- Two MPW chips (5 mm × 5 mm )

- TaichuPix-1: 2019; TaichuPix-2: 2020 → feasibility and functionality verification

- > 1st engineering run

- Full-scale chip: TaichuPix-3, received in July 2022 & March 2023

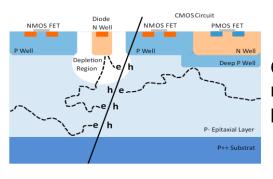

CMOS monolithic pixel sensor

TaichuPix-3  $(15.9 \times 25.7 \text{ mm}^2)$

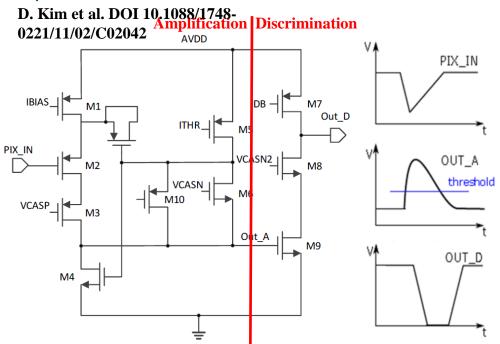

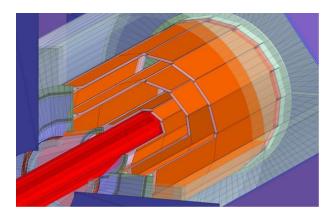

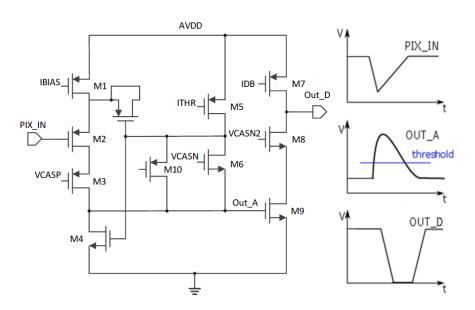

## Pixel architecture – Analog

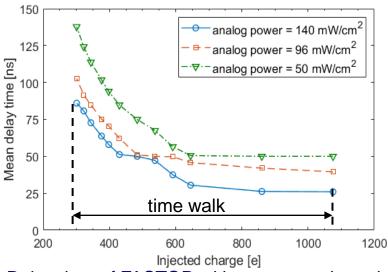

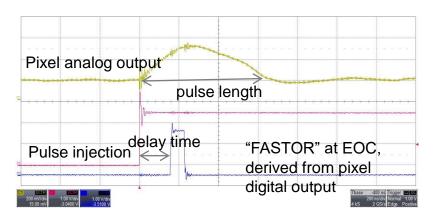

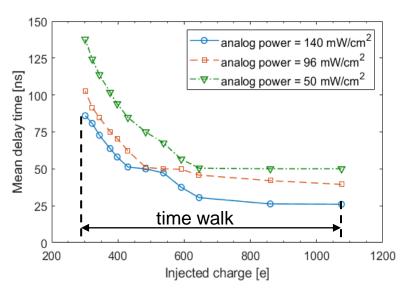

Delay time of FASTOR with respect to the pulse injection vs. injected charge. The delay time was measured by the timestamp of a step of 25 ns.

- Digital-in-Pixel scheme: in pixel discrimination & register

- Pixel analog is derived from ALPIDE (and benefit from MIC4 for MOST1)

- As most of ATLAS-MAPS sensors' scheme

- Biasing current has to be increased, for a peaking time of ~25ns

- ⋄ for 40MHz BX @ Z pole

- Consequence:

- Power dissipation increased

- ⋄ Faster CIS process has to be used

- With faster charge collection time, otherwise only fast electronics is of no meaning

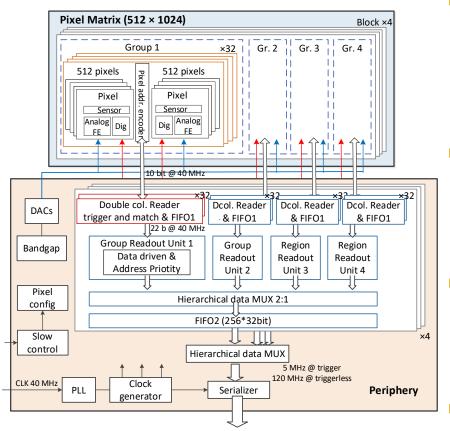

### TaichuPix sensor architecture

#### Pixel 25 μm × 25 μm

- Continuously active front-end, in-pixel discrimination

- Fast-readout digital, with masking & testing config. logic

#### Column-drain readout for pixel matrix

- Priority based data-driven readout

- > Time stamp added at end of column (EOC)

- Readout time: 50 ns for each pixel

#### 2-level FIFO scheme

- L1 FIFO: de-randomize the injecting charge

- L2 FIFO: match the in/out data rate between core and interface

#### Trigger-less & Trigger mode compatible

- > Trigger-less: 3.84 Gbps data interface

- Trigger: data coincidence by time stamp, only matched event will be readout

#### Features standalone operation

On-chip bias generation, LDO, slow control, etc.

## Full size sensor TaichuPix-3

- 12 TaichuPix-3 wafers produced from two rounds

- Wafers thinned down to 150 µm and diced

8-inch wafer

Wafer after thinning and dicing

Thickness after thinning

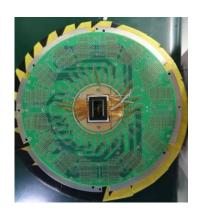

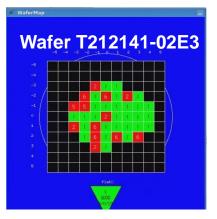

➤ Wafers tested on probe-station → chip selecting & yield evaluation

Probe card for wafer test

An example of wafer test result (yield ~67%)

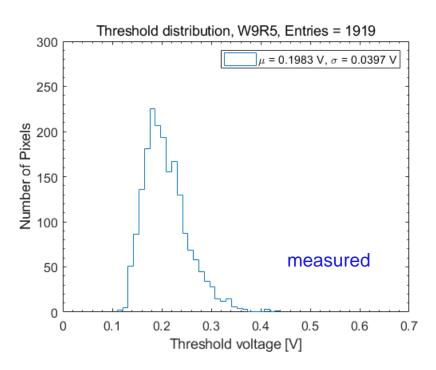

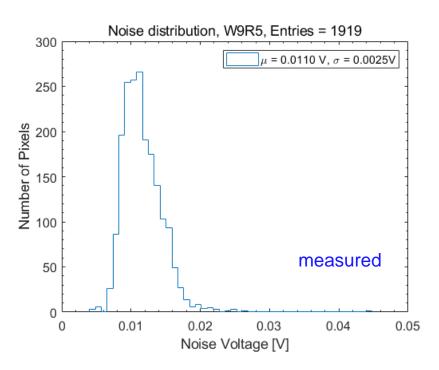

## Threshold and noise of TaichuPix-3

- Pixel threshold and noise were measured with selected pixels

- Average threshold ~215 e<sup>-</sup>, threshold dispersion ~43 e<sup>-</sup>, temporal noise ~12 e<sup>-</sup> @ nominal bias setting

- S-curve method was used to test and extract the noise and the threshold

Power dissipation of 89 ~ 164 mW/cm² tested @ 40MHz clk with different biasing condition

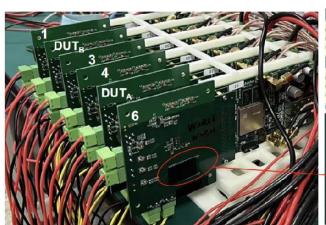

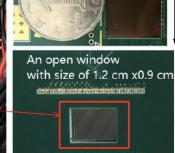

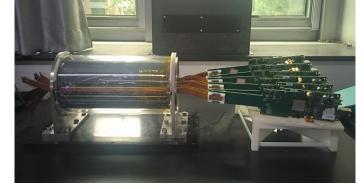

## TaichuPix-3 telescope

#### The 6-layer of TaichuPix-3 telescope built

Each layer consists of a TaichuPix-3 bonding board and a FPGA readout board

25.7 mm

A open window on PCB under TC3 chip to reduce multi-scattering

6-layer TaichuPix-3 telescope

#### Setup in the DESY testbeam

- TaichuPix-3 telescope in the middle

- Beam energy: 4 GeV mainly used

- Tests performed for different DUT(Detector Under Test)

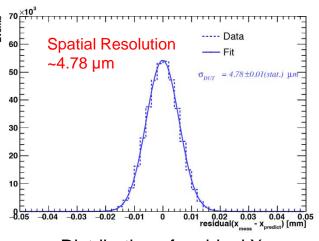

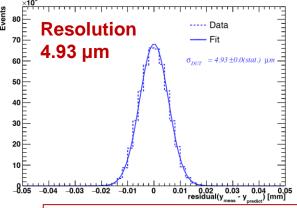

## TaichuPix-3 beam test result

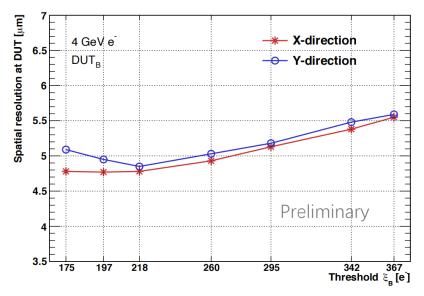

#### Spatial resolution

- Gets better when decrease the pixel threshold, due to the increased cluster size

- A resolution < 5 μm achieved, best resolution is</li>

4.78 μm

#### Detector efficiency

Decreases with increasing the threshold, detection efficiency >99.5% at threshold with best resolution

Distribution of residual X

Spatial resolution vs. pixel threshold

Detection efficiency vs. pixel threshold

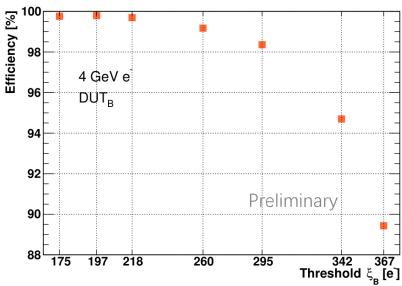

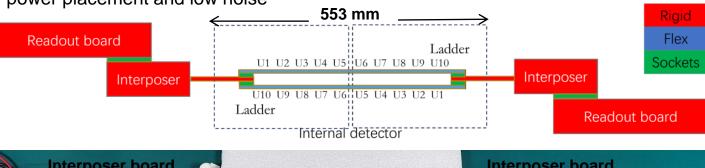

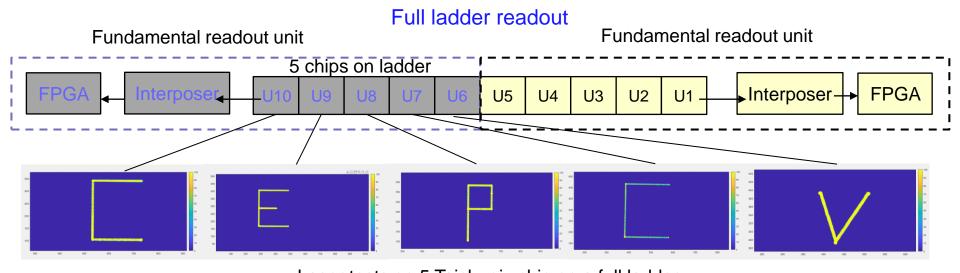

## Ladder readout design

- Detector module (ladder) = 10 sensors + readout board + support structure + control board

- > Sensors are glued and wire bonded to the flexible PCB, supported by carbon fiber support

- > Signal, clock, control, power, ground will be handled by control board through flexible PCB

#### Challenges

- ▶ Long flex cable → hard to assemble & some issue with power distribution and delay

- ▶ Limited space for power and ground placement → bad isolation between signals

#### Solutions

Read out from both ends, readout system composes of three parts, careful design on power placement and low noise

FPGA board

Ladder readout system

FPGA board

### Laser test result of ladder

Laser tests on 5 Taichupix chip on a full ladder ("CEPCV" pattern by scanning laser on different chips on ladder)

- A full ladder includes two identical fundamental readout units

- Each contains 5 TaichuPix chips, a interposer board, a FPGA readout board

- Functionality of a full ladder fundamental readout unit was verified

- Configuring 5 chips in the same unit

- Scanning a laser spot on the different chips with a step of 50 μm, clear and correct letter imaging observed

- ▶ Demonstrating 5 chips working together → one ladder readout unit working

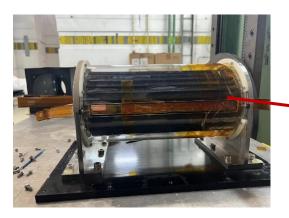

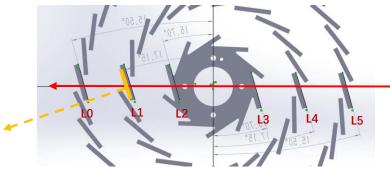

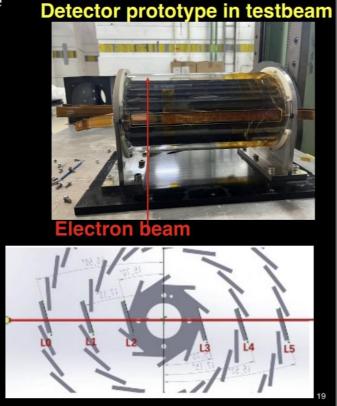

## **Detector prototype**

#### 6 double-sided layers assembled on the detector prototype

- 12 flex boards with two TaichuPix-3 chips bonded on each flex

- Readout boards on one side of the detector

|       | L0-L1 | L1-L2 | L2-L3 | L3-L4 | L4-L5 |

|-------|-------|-------|-------|-------|-------|

| L(mm) | 21.2  | 20.6  | 37.46 | 20.6  | 21.2  |

Preliminary offline results indicate a good performance for the vertex detector prototype.

Details find in poster "Beam test of a baseline vertex detector for the CEPC", 5 Oct

## **Summary**

- The full-scale and high granularity pixel prototype, TaichuPix-3, has been designed and tested for CEPC VTX R&D

- Spatial resolution of 4.78/4.85 µm measured with 4 GeV electron beam in DESY

- Total ionization dose (TID) > 3 Mrad

- Readout electronics for the sensor test and the ladder readout were developed

- Performed the sensor characterization in the lab successfully

- Completed beam tests for the pixel sensor prototype and the vertex detector mechanical prototype

**Concept (2016)**

1<sup>st</sup> Vertex detector prototype (2023)

## Thank you very much for your attention!

# TaichuPix-3 specification & performance

|                     | Design specs.                              | Measured                                |

|---------------------|--------------------------------------------|-----------------------------------------|

| Spatial resolution* | 3~5 μm                                     | 4.8 µm (best)                           |

| TID*                | > 1 Mrad                                   | > 3 Mrad                                |

| Pixel pitch         | ≤ 25 µm                                    | 25 μm                                   |

| Chip size           | ~1.4 × 2.56 cm <sup>2</sup>                | $1.59 \times 2.57 \text{ cm}^2$         |

| Dead time           | < 500 ns                                   | ~ 300 ns                                |

| Data rate           | 110 Mbps (trigger) 3.84 Gbps (triggerless) | Not tested<br>Currently 160 Mbps tested |

| Power density       | < 200 mW/cm <sup>2</sup>                   | 89 – 164 mW/cm <sup>2</sup>             |

<sup>\*</sup>project indicator

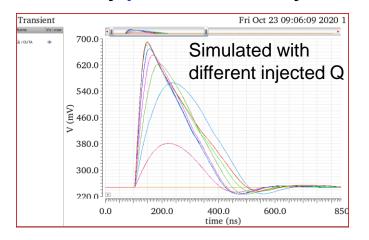

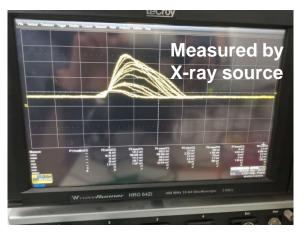

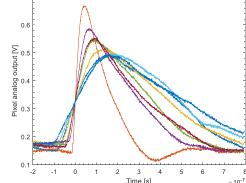

## Functionality of complete signal chain

Functionality of the complete signal chain (including sensor, analog front-end, in-pixel logic readout, matrix periphery readout and data transmission unit) was firstly proved with X-ray, electron and laser sources.

Measured results consistent with simulations in term of shape, amplitude

Pixel analog signals from simulation (left) and measurement (right)

Analog output of one pixel under 90Sr exposure

from the X-tube for 5 min.

# CEPC

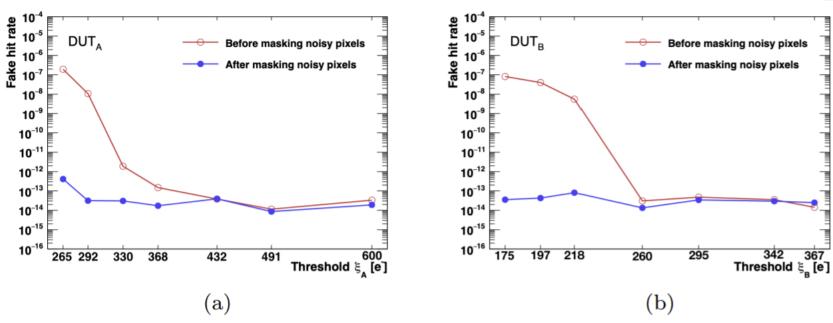

## Fake hit rate

Figure 3: Fake hit rate of  $DUT_A$  (a) and  $DUT_B$ (b) as a function of threshold.

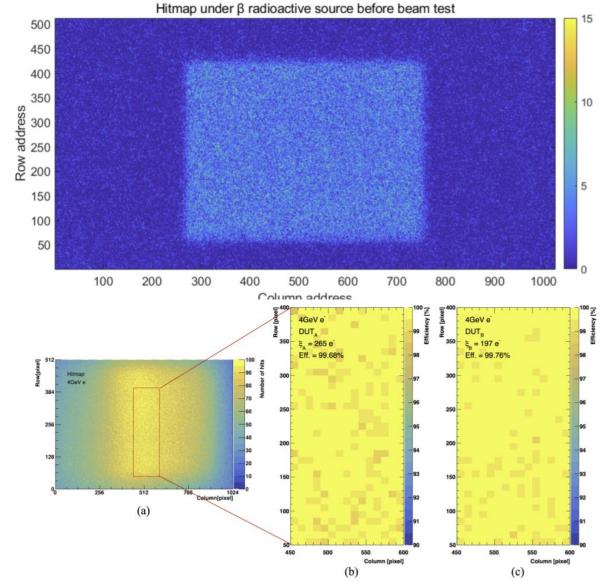

## **Hitmap**

Figure 12: (a) The hitmap of one example DUT under 4 GeV electron beam. The pixels inside the red box are used to calculate the average efficiency of every  $10 \times 10$  pixels. (b) (c) The efficiency map of DUT<sub>A</sub> and DUT<sub>B</sub> at the minimum threshold.

## **Cluster size**

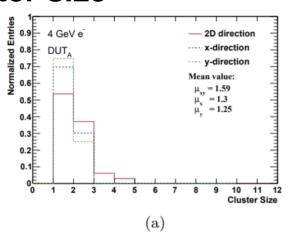

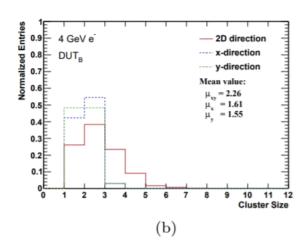

Figure 6: The cluster size distribution for  $DUT_A$  with  $\xi_A = 265e^-$  (a) and  $DUT_B$  with  $\xi_B = 175e^-$  (b), shown in the 2D detector plane direction and 1D projections along the x-direction (row direction of the sensor) and y-direction (column direction of the sensor).

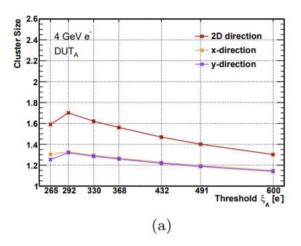

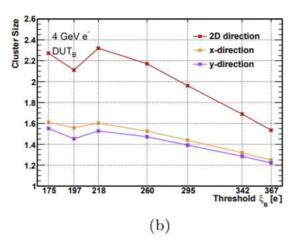

Figure 7: Average cluster size of  $DUT_A$  (a) and  $DUT_B$  (b) as a function of threshold  $\xi$ , shown in the 2D detector plane and 1D projections along x-direction and y-direction.

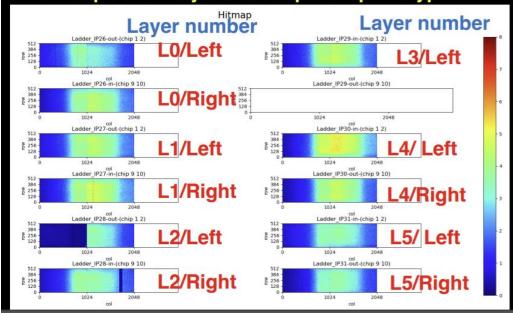

## Test beam @ DESY for detector prototype

- Six double-side ladders installed on the vertex detector prototype for DESY testbeam

- 12 flex PCB, 24 Taichupix chips installed on detector prototype

- Beam spot ( $\sim$ 2×2cm) is visible on detector hit map

- Record about one billion tracks in two weeks

#### Hit maps of all layers taichupix on prototype

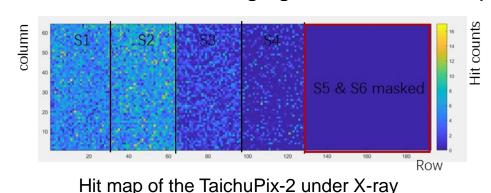

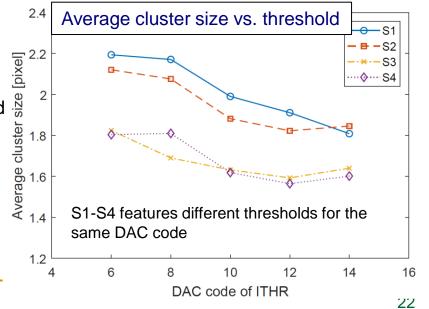

## TaichuPix-2 test with 90Sr

#### Four pixel sectors with different analog front-end variations for design optimization, S1 used in the full-scale chip due to the lowest ENC

| Sectors    | Front-end design features                                    |

|------------|--------------------------------------------------------------|

| S1         | Reference design, inherited from TaichuPix-1                 |

| S2         | PMOS in independent N-wells                                  |

| <b>S</b> 3 | One transistor in an enclosed layout                         |

| S4         | Increased transistor size to reduce the threshold dispersion |

#### Threshold and noise of different pixel sectors

| Sec-<br>tors | Threshold<br>Mean (e <sup>-</sup> ) | Threshol<br>d rms (e <sup>-</sup> ) | Temporal<br>noise (e <sup>-</sup> ) | Total equiv.<br>noise (e <sup>-</sup> ) |

|--------------|-------------------------------------|-------------------------------------|-------------------------------------|-----------------------------------------|

| <b>S</b> 1   | 267.0                               | 49.8                                | 29.3                                | 57.8                                    |

| S2           | 293.4                               | 54.5                                | 26.9                                | 60.8                                    |

| S3           | 384.9                               | 58.4                                | 24.4                                | 63.3                                    |

| S4           | 411.9                               | 56.6                                | 26.5                                | 62.5                                    |

#### TC2 exposure to <sup>90</sup>Sr source

- Average cluster size decreases with threshold as expected

- Average cluster size for S1-S4 larger than 1, → benefits the spatial resolution (better than the binary resolution,  $25/\sqrt{12} \approx 7.2 \ \mu m$ )

## Pixel analog front-end

#### Based on ALPIDE\* front-end scheme

- modified for faster response

- 'FASTOR' signal delivered to the EOC (end of column) when a pixel fired, timestamps of hit recorded at pos. edge of 'FASTOR'

Schematic of pixel front-end

\*Ref: D. Kim et al. DOI 10.1088/1748-0221/11/02/C02042

Delay time of FASTOR with respect to the pulse injection vs. injected charge. The delay time was measured by the timestamp of a step of 25 ns.