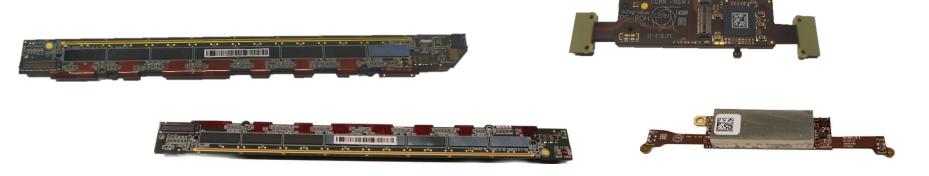

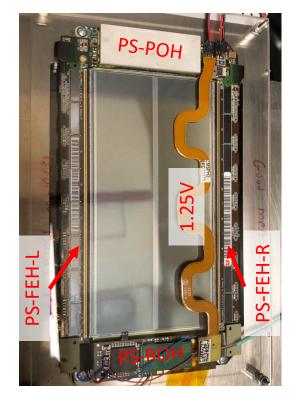

A PS-FEH-L16 kick-off hybrid

Mark Istvan Kovacs, Georges Blanchot, Irene Mateos Dominguez, Kevin Schleidweiler, Patryk Szydlik Angelos Zografos

Contact: mark.istvan.kovacs@cern.ch

### **Outline:**

- 1. Introduction of CMS Phase-2 upgrade and the procurement of hybrids

- 2. Introduction of the front-end hybrid concepts, architecture and design practices

- 3. Kick-off hybrid designs and test results

- 4. Quality issues, lessons learnt and yield

- 5. Conclusion

Hybrid circuit: Unpackaged dies are mounted on a substrate with passive components.

CMS: Compact Muon Solenoid; PS: Pixel-Strip type module; PS-FEH-L16: PS Front End Hybrid, left 1.6 mm spacing

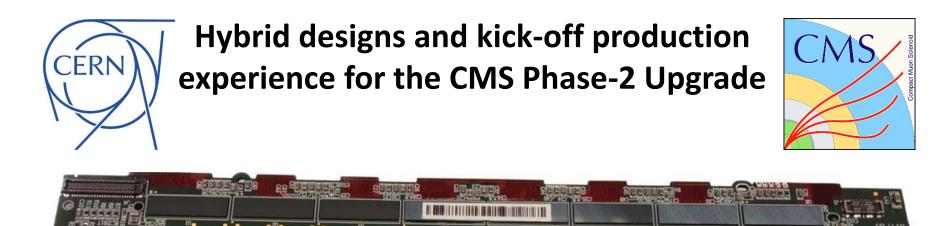

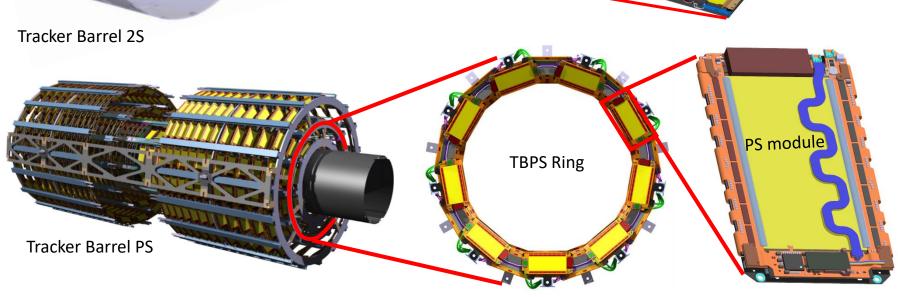

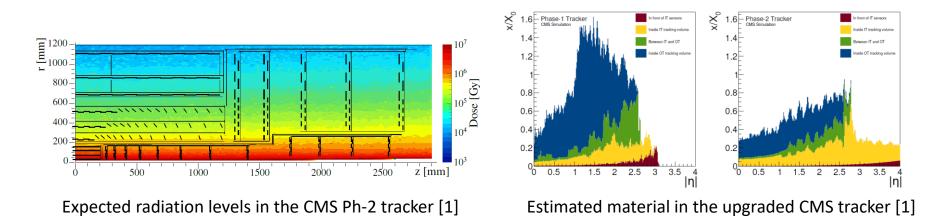

#### **1. Introduction of CMS Phase-2 upgrade and the Tracker outer barrel**

The CMS Tracker Phase-2 Upgrade is required to adapt the CMS detector to the 3000 fb<sup>-1</sup> total integrated luminosity and 14 TeV centre-of-mass energy of the HL-LHC.

TB2S Ladder

HL-LHC: High Luminosity Large Hadron Collider; TB – Tracker Barrel; 2S – Strip-strip module; PS – Pixel-Strip module

25 module

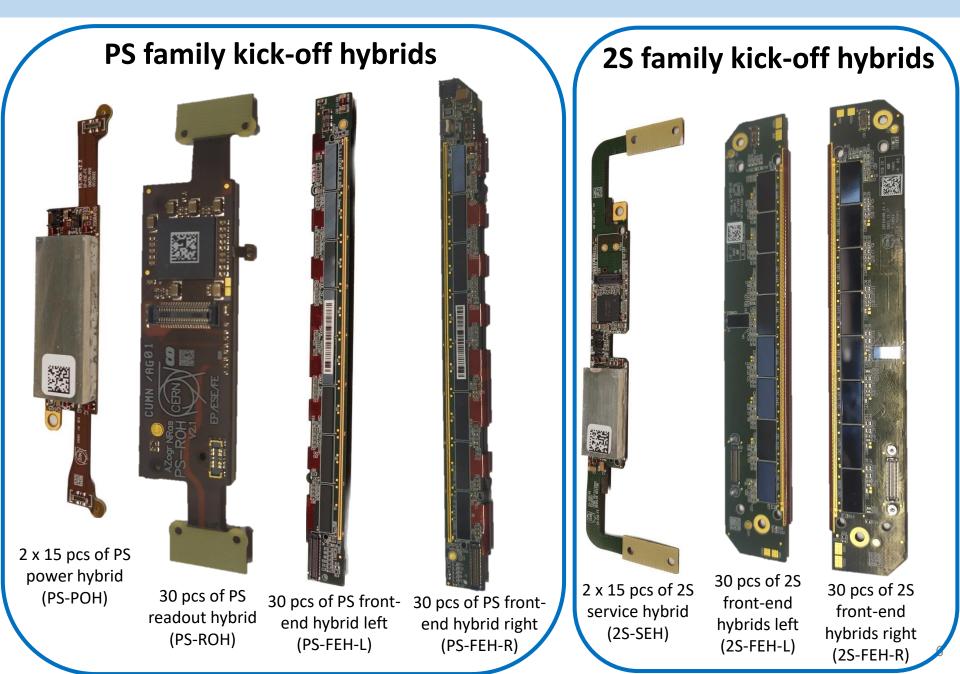

Sensor module prototypes are assembled from multiple pieces, including hybrids, sensors, spacers and stiffeners. Modules from kick-off hybrids are currently under construction.

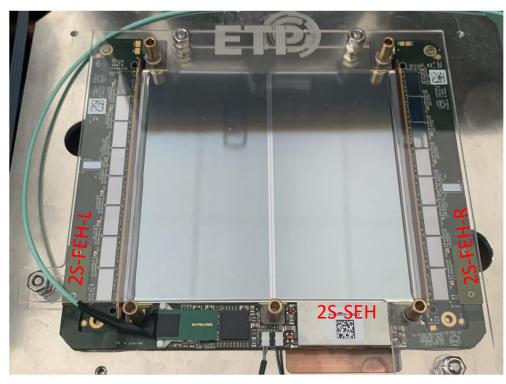

A Strip-Strip (2S) module prototype constructed from the latest hybrid prototypes.

A Pixel-Strip (PS) module prototype constructed from the latest hybrid prototypes.

SEH: Service Hybrid; ROH – Read-Out Hybrid; POH – Power Hybrid; FEH – Front-End Hybrid

### The requirements for the electronics are the following:

- Tolerate radiation (max. 56 and 9 Mrad expected for PS and 2S respectively [1]).

- Reduce mass and size as much as possible.

- Operation in cold, minimize heat transfer to sensors.

- Reliable operation for 15 years.

- Low power consumption (~5.4W per 2S module; 7.8W per PS module[1]).

- Total number of modules planned: 2S: 9140; PS: 6730;

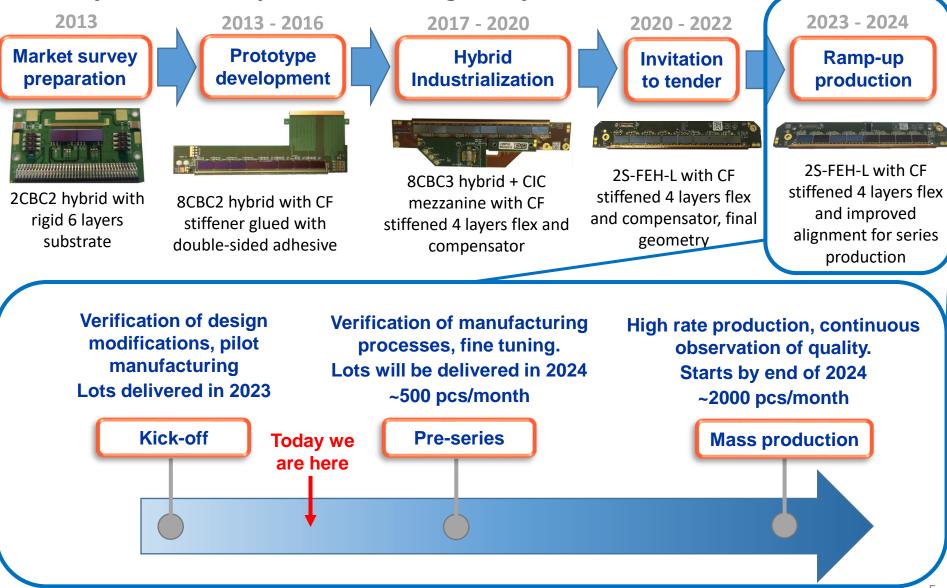

#### **1.** Introduction – History of the development project

### The hybrid development is a long story:

#### 2. Kick-off hybrids

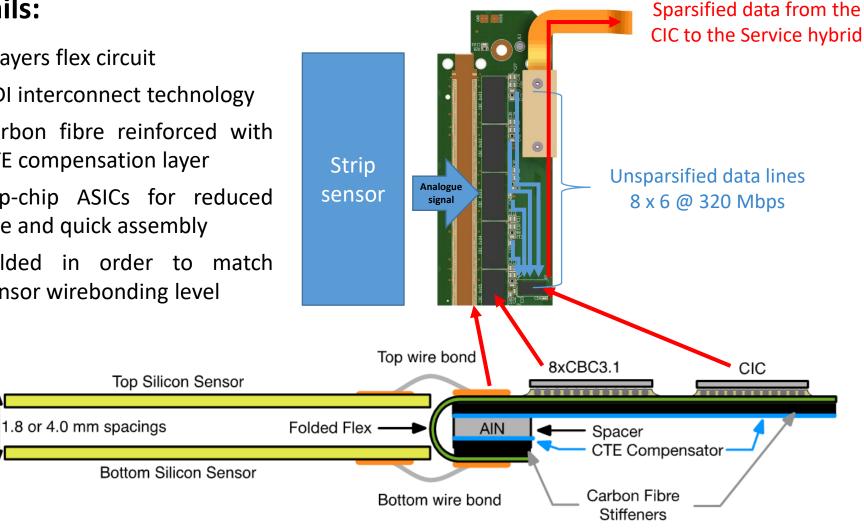

#### 2. 2S-FEH construction and architecture

### **Details:**

- 4 layers flex circuit

- HDI interconnect technology ٠

- Carbon fibre reinforced with CTE compensation layer

- Flip-chip ASICs for reduced ٠ size and quick assembly

- Folded sensor wirebonding level

Cross section view of the 2S front-end hybrid construction in a module

HDI – High Density Interconnect; CTE – Thermal Expansion Coefficient; CIC – Concentrator ASIC;

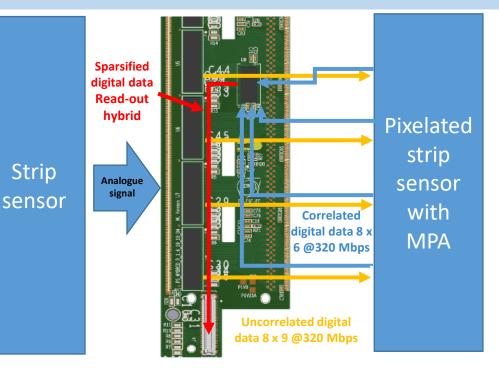

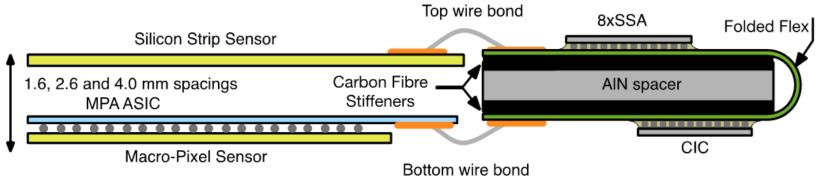

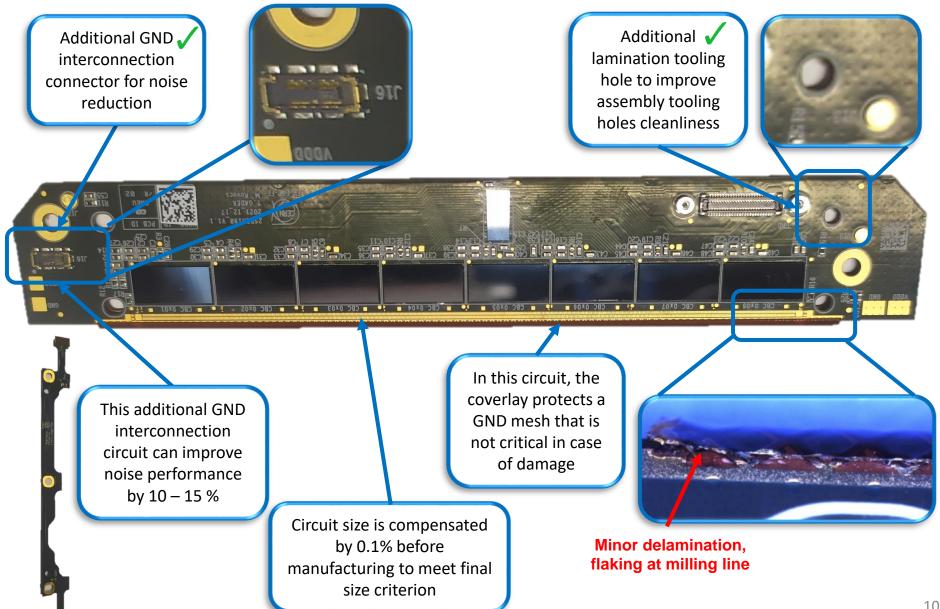

#### 2. PS-FEH construction and architecture

# **Details:**

- 5 layers HDI flex

- Circuit area is smaller than for the 2S hybrids

- No compensator is needed as the circuit is symmetric

- Smallest line and spacing is 45/45 μm respectively

- Very thin build-up, 125 μm total

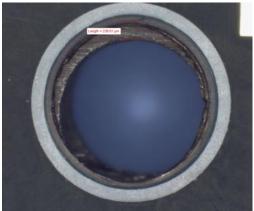

Cross section view of the PS front-end hybrids construction in a module

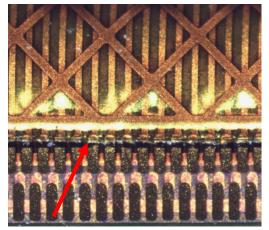

### Few important HDI design practices for flex circuits:

- Use crosshatched copper pattern to improve flexibility.

- Use "teardrops" at trace to pad connections to increase reliability.

- Avoid stacked µvias to further increase reliability.

- Balance copper area to achieve a flat surface, fill unused areas.

- Use "vent holes" to speed-up circuit drying process.

- Use silkscreen or solder mask barriers to control underfill flow.

- Use simulation tools with small size conductors to estimate impedance.

Underfill "barrier"

"vent holes" placed every mm

X-hatch can improve flexibility

Teardrop will decrease stress

#### **3. 2S-FEH kick-off design - test results**

#### 4. PS-FEH kick-off design - test results

#### 4. 2S-SEH kick-off design - test results

#### 4. Reliability of stacked vs staggered microvias

| Description           | Flex stacked BV +100 µm<br>de-stacking   | Flex stacked BV +100 µm<br>de-stacking | Flex stacked BV        |  |

|-----------------------|------------------------------------------|----------------------------------------|------------------------|--|

|                       | 1 50 50 50 50 50 50 50 50 50 50 50 50 50 | 1<br>2<br>50<br>3<br>50<br>4           | 1<br>2<br>3<br>50<br>4 |  |

| Picture               |                                          |                                        | 150                    |  |

| Pad size layer 1      | 150                                      | 150                                    | 150                    |  |

| BV 1-2                | 50                                       | 50                                     | 50                     |  |

| Pad size layer 2      | 150x250 oval                             | 150x250 oval 150                       |                        |  |

| BV 2-3                | 50                                       | 50                                     | 50                     |  |

| Pad size layer 3      | 150x250 oval                             | 150                                    | 150                    |  |

| BV 3-4                | 50                                       | 50                                     | 50                     |  |

| Pad size layer 4      | 150                                      | 150                                    | 150                    |  |

| De-stacking           | 100                                      | 100                                    | 100                    |  |

| IST cycles<br>average | >1000 cycles                             | ∾130 cycles                            | ∾40 cycles             |  |

**IST:** Interconnect Stress Test

**Source:** Design guidelines – Dyconex AG. IST cycles according to IPC-TM-650 2.6.26 @ maximum temperature of 210 °C 13

#### 4. 2S-SEH and PS-POH split-plane and regular designs comparison

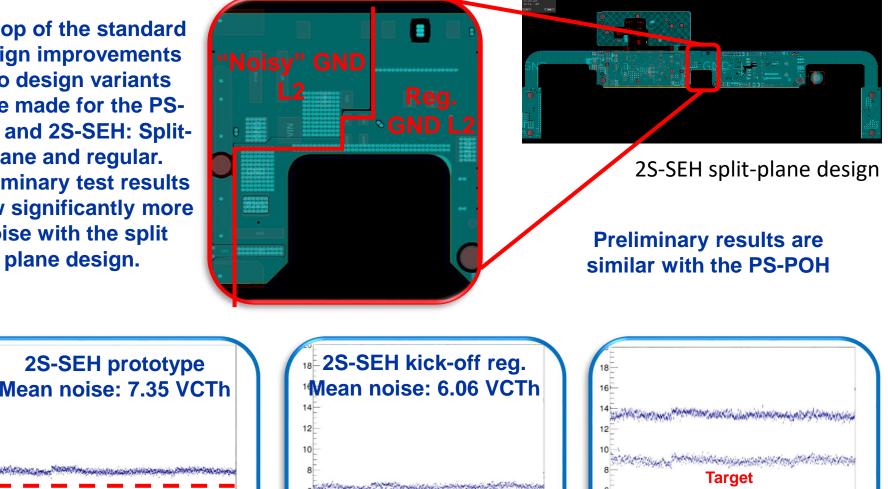

On top of the standard design improvements two design variants were made for the PS-POH and 2S-SEH: Splitplane and regular. **Preliminary test results** show significantly more noise with the split plane design.

Target

1000

500

2000

500

More info on noise studies: https://iopscience.iop.org/article/10.1088/1748-0221/17/12/C12008 Noise target: 1000e approx. equivalent to 6 VCTh (preamp threshold) units. 1 VCTh ~ 167e

500

Target

1000

1500

2000

2000

2S-SEH kick-off split plane

Mean noise: >10 VCTh

#### 4. Quality issues and lessons learnt

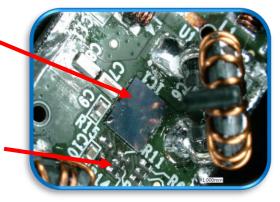

### Cleanliness

# Some circuits arrive with contaminated wire bond pads.

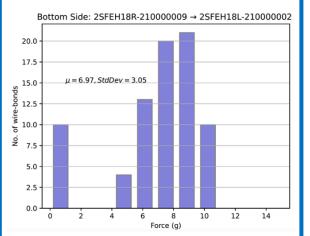

Contaminations are leading to poor wire bonding pull force (below 8g mean).

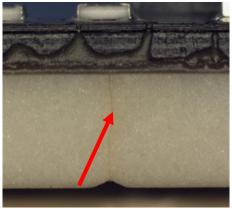

### Misalignment

Alignment of fold-over is out of tolerance and the hole diameter is reduced.

Misaligned coverlay is covering wirebond pads.

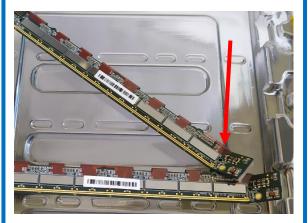

### Mechanical damage

A cracked aluminium nitride spacer in the PS-ROH circuits.

Circuits broken due to wrong orientation in packaging.

#### 4. Other issues and yield

### **Problems with lead time:**

- Flex lead time 60 -> 100 working days (WD)

- Assembly lead time 30 -> 50 WD

Bpol 2V5

2S-SEH was returned for repair to replace resistors in the voltage setting divider.

| PCB yield is 50 - 70 % | Hybrid type  | No. ordered | received | Tested good | Yield |

|------------------------|--------------|-------------|----------|-------------|-------|

|                        | 2S-FEH 1.8 R | 30          | 29       | 24          | 83%   |

|                        | 2S-FEH 1.8 L | 30          | 26       | 22          | 85%   |

|                        | 2S-SEH split | 15          | 23       | 12          | 52%*  |

|                        | 2S-SEH reg.  | 15          | 17       | 9           | 53%*  |

|                        | PS-FEH 2.6 R | 30          | 32       | NO DATA     | -     |

|                        | PS-FEH 2.6 L | 30          | 33       | NO DATA     | -     |

|                        | PS-ROH       | 30          | 34       | NO DATA     | -     |

|                        | PS-POH split | 15          | 18       | 18          | 100%  |

|                        | PS-POH reg.  | 15          | 20       | 20          | 100%  |

\* Preliminary data, numbers might improve slightly with further tests. Yield includes visual inspection results in all cases. 16

### Hybrid designs

- All hybrid designs were successfully produced during the kick-off production.

- The 2S-FEH, PS-POH and PS-ROH hybrids were produced without major issues.

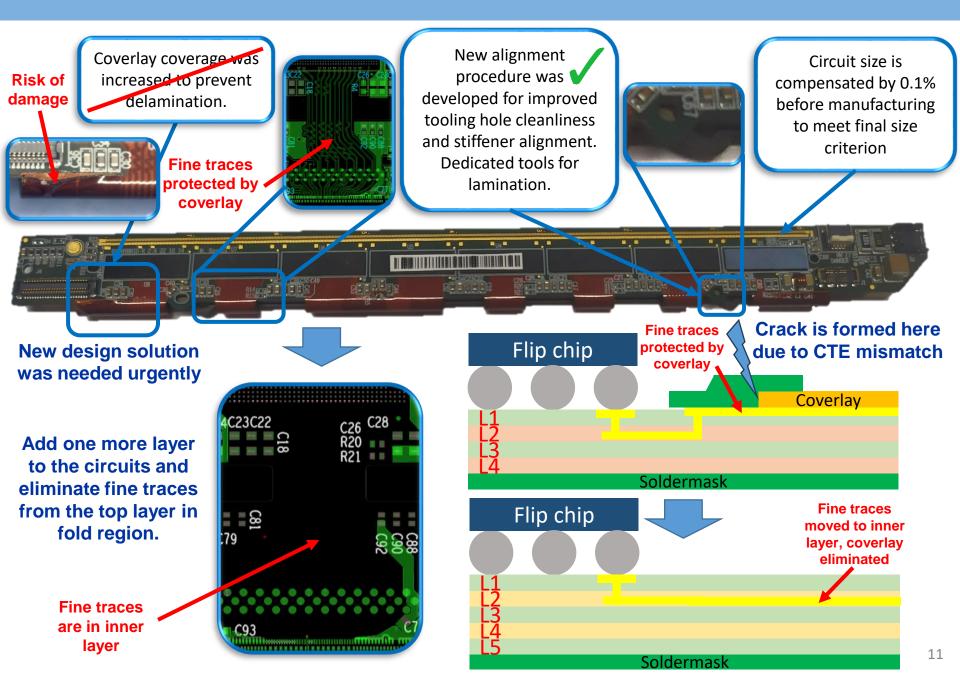

- The PS-FEH had to be redesigned to 5 layers in order to eliminate coverlay use.

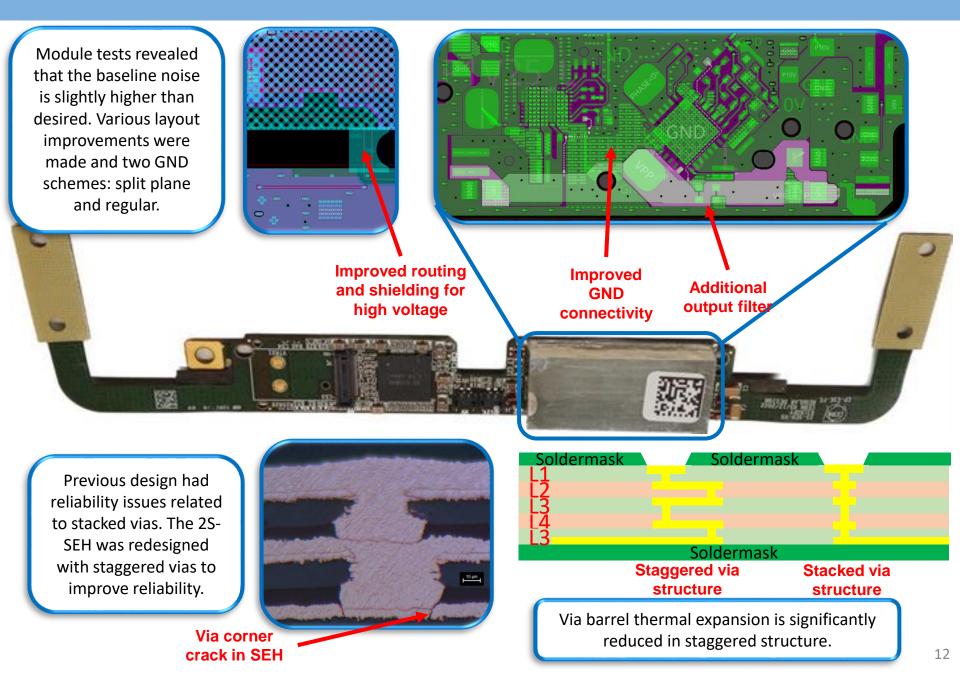

- The 2S-SEH was redesigned before the kick-off production to avoid stacked vias. Two design variants were produced, preliminary test results show better noise performance in the case of the regular design.

- Two versions were made of the PS-POH circuits as well. Preliminary results are showing better performance in the case of regular design.

- Most of pre-series circuits are launched, in some cases further tests are needed.

Production:

- Lead times are much longer than expected and range up to half year.

- Yield is good in some cases, but improvement is needed for a few hybrid types.

- Cleanliness of wire-bond pads and precision need to be improved.

- Small details can be very important and can cause big problems if not mitigated in time. A good example is the coverlay issue.

- It might not be a good idea to change a design that is close to the specified performance. A good example is the split-plane POH and SEH design.

- Trying to hurry can lead to more mistakes from the suppliers, which can cause further delays. A good example is the resistor divider issue in the 2S-SEH.

- Open communication with the suppliers is extremely important to resolve issues or misunderstandings.

# Thank you for your attention!

### Please follow the next presentations of our working group:

- Angelos Zografos CMS Outer Tracker Phase-2 Upgrade on-module powering: today 11:40 Sirocco room

- **Patryk Szydlik** Commissioning of the Test System for the Phase-2 Upgrade of the CMS Outer Tracker: Thursday 17:40 poster session