Institute for Particle Physics and Astrophysics

# CMS ECAL VFE design, production and testing

D. Abadjiev, G. Dissertori, M. Dejardin, T. Gadek, **W. Lustermann**, L. Martin, K. Stachon On behalf of the CMS collaboration TWEPP2023, Geremeas, Italy Design, production and testing for reliabili

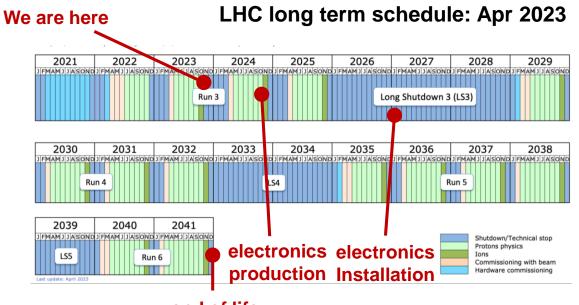

**Production** pla

lest set

Environmental stress screening

Summary

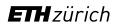

## **CMS Electromagnetic Calorimeter upgrade**

#### ECAL barrel installed: July 27, 2007

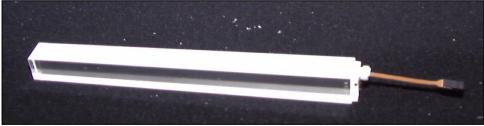

#### Lead Tungstate (PbWO<sub>4</sub>) crystal with Avalanche Photo-Diode attached

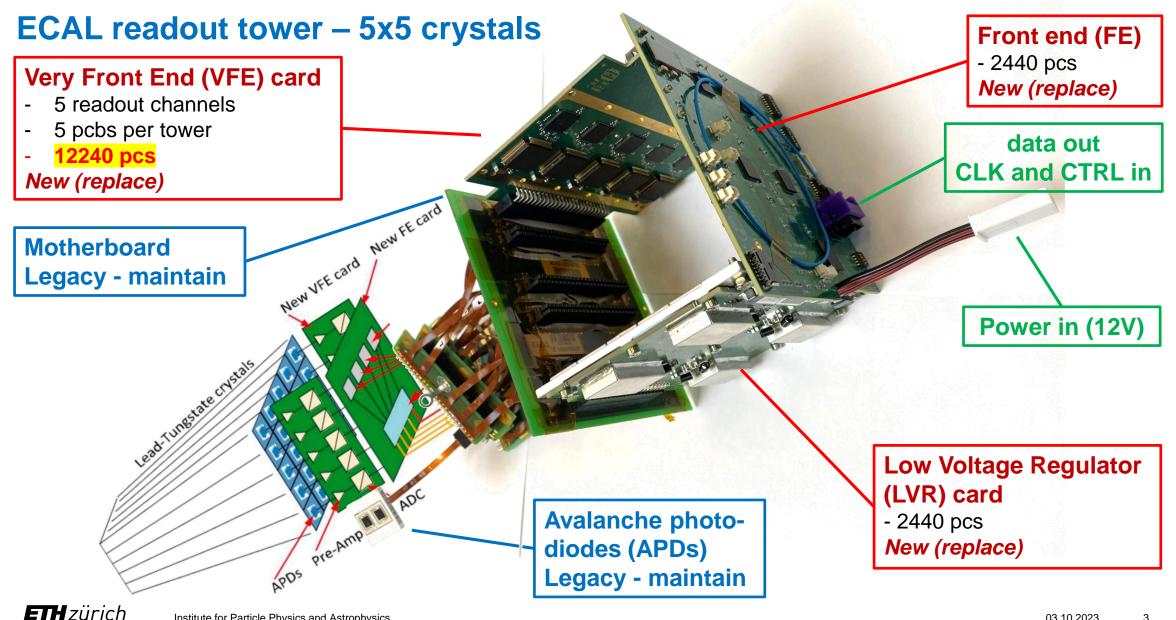

## 1 ECAL Barrel (EB) on detector parts – readout tower (RT)

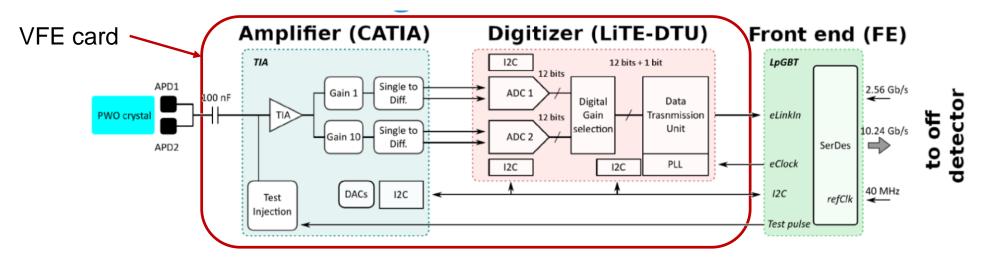

## **VFE card functionality - ASICs**

#### New electronics – why:

- Longer level 1 trigger latency (12.5µs)

- Mitigates problems induced by high radiation levels at HL-LHC

- Introduces precision time measurement into ECAL: resolution 30 ps for E > 50 GeV

- Introduces data streaming: trigger primitives generation off-detector

#### CATIA (CEA Saclay)

- Trans-impedance amplifier ~35 MHz bandwidth

- Two gains differential outputs: 1 and 10

- Pedestal adjustment

- Internal test-pulse generator

- Internal temperature sensor

- I2C interface

#### LITE-DTU (INFN Torino, LIP Lisbon)

- Dual 12bit ADC, sampling at 160 MS/s

- 160 MHz CLK and fast control input

- internal PLL

- Lossless data compression

- Data streaming at 1.28 Gbit/s

- I2C interface

#### **ETH** zürich

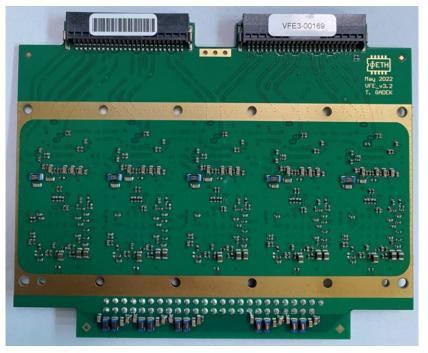

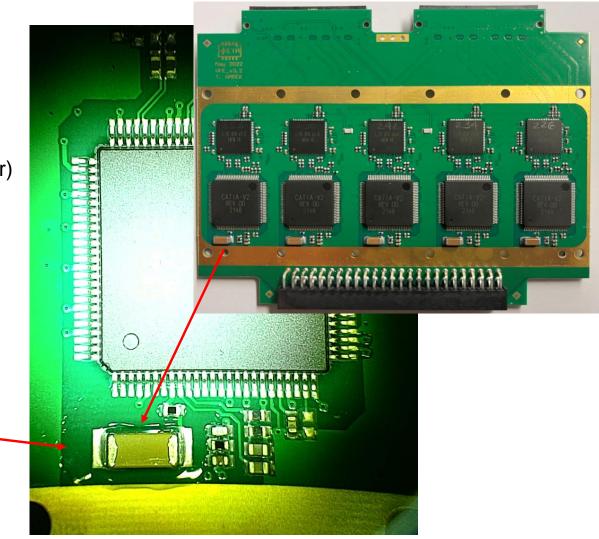

## **VFE card**

- 5 identical channels: CATIA + LiTE-DTU

- 12240 pieces for CMS

- 340 pieces (spare supermodule)

#### Production: 14600 cards

#### Including pre-series: 400-500 cards

Samtec connector

- 8 layers, 35µm

- 626 components, thereof:

- 10 active (CATIA and LiTE-DTU)

- Two SMD connectors (ERNI, TE connectivity)

- One through hole connector (Samtec)

- Connectors fit legacy system

#### **ERNI** connectors

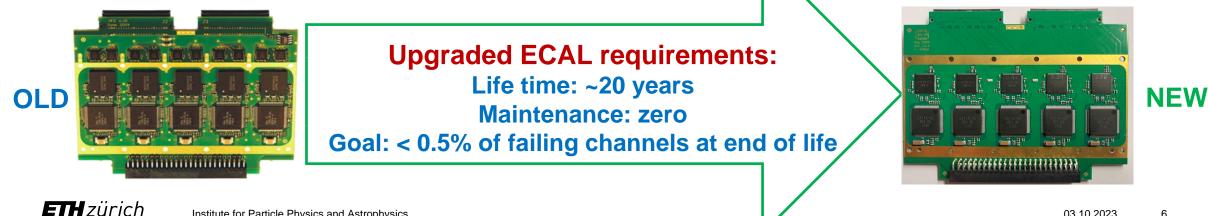

## VFE life time and reliability desire

From (my) slide in 2005:

Life time: ~10 years Maintenance: zero

Legacy electronics operational since 18 years 2 more years to come  $\rightarrow$  total: 20 years

Just a miracle? How do we make it happen again?

#### **ECAL** barrel:

- Single layer detector

- Missing channels impact energy resolution

- Missing readout towers permit electrons, photons to escape unidentified

- Repair practically impossible not foreseen

end of life http://lhc-commissioning.web.cern.ch/schedule/LHC-long-term.htm

## **Design for reliability and manufacturing**

#### **Quality and Reliability start with the Design: PCB, PCB materials**

#### **Choice of PCB class standard:**

#### Classes (IPC-6011)\*: require Class 3

- Higher class: higher level of inspection and testing

- class 3/A (IPC-6012) expensive (not used)

- Follow layout rules (or further relax), such as

- Min. trace width and gap

- Min. Via drill and pad diameter

- Etc.

- More stringent requirements on annular rings

- Requirements on PCB dielectric

- Cross-sections of PCBs

#### **IPC-A-600** Acceptability of Printed Circuit Boards

#### PCB design and fabrication:

- Surface finish: **ENIG** (for solderability)

- Core and prepreg materials with TG of 170°C

- Transmission line impedance: ±10%

- Tuned to standard materials

- Control with test-coupons

- High speed signal guarding with Via stitching: CLK 160 MHz, 1.28 Gbit data, fast command

- Through hole Vias only

- Standard copper layers: **35µm**

- Design PCB panels (tbd with the assembler)

- Add test coupons for impedance test

## **Design for reliability and manufacturing**

#### **Quality and Reliability start with the Design: components**

#### **Components:**

#### Automotive grade or better (AEC-Q200)

- SMD components: smallest **0402**, **0603** where possible

- Gold plated connector pins

- No through hole technology (expect SAMTEC connector)

- Packaging for machines: **ESD trays, reels**

- **Derating** of components:

- ~80% for voltage, current

- ~50% for power

- **Coating** of higher voltage parts

#### **Decoupling capacitor:**

- 500V → 630V

- Coating

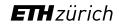

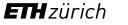

## Production for reliability of the VFE card

#### Quality and Reliability continue with: assembly standards, assembler and procedures

#### Choice of PCB assembly standard: Class 3

- Higher class: more stringent criteria on solder joints

- Less displacement of components tolerated:

- <25% of component terminal off pad (class 3) vs <50% (class 2)</li>

- Through hole filling >75% (class 3) vs >50% (class 2)

IPC-A-610 Acceptability of Electronic Assemblies

#### **Required certification of Assembler**

- ESD safe environment

- Assembler certified for quality assurance and control ISO 9001 (or 13485)

- Trained personal for assembly following IPC 610

- Trained personal for rework and repair IPC 7711/7721

- Components management system

#### PCB assembly:

- Specified solder: SAC305 (standard, lead-free)

- Bake-out of components

- Production in batches (500/week):

- Metallurgic cuts of few samples per batch

- Avoid (systematic) failure of large number of PCBs →

Factory Acceptance Tests: follows production pace

- Automatic Optical inspection (AOI)

- Electrical testing by the Assembler

- Continuous monitoring of first pass yield: >95%

- Appropriate, established cleaning

#### Last but not least → Environment protection

- **RoHS compliant** materials

- ISO 14001 compliant

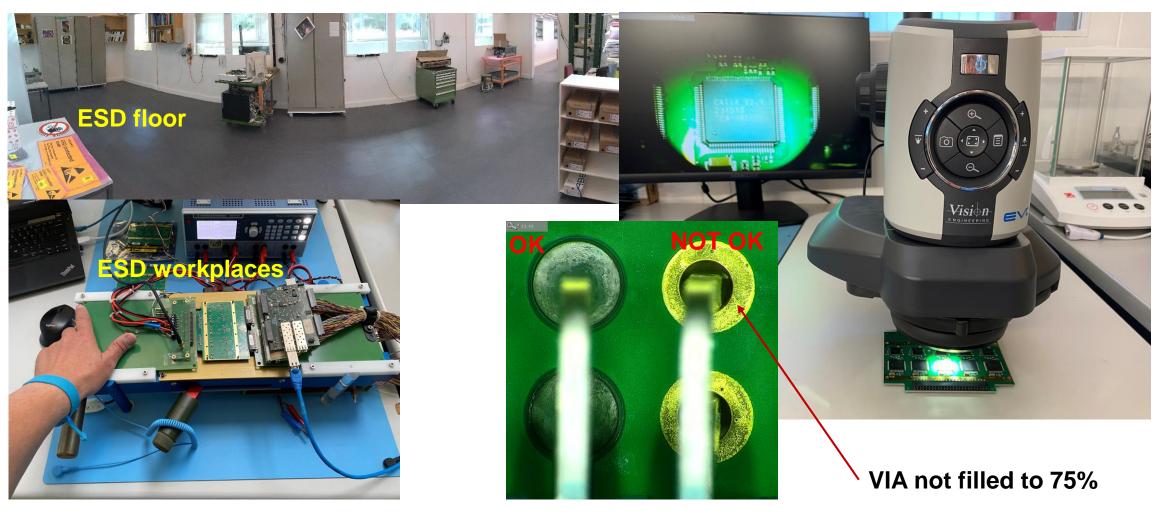

## **Testing for reliability**

#### Quality and Reliability continue with: reception, testing and installation

#### Ensure ESD until the installation of the cards

**Optical inspection tool – in house**

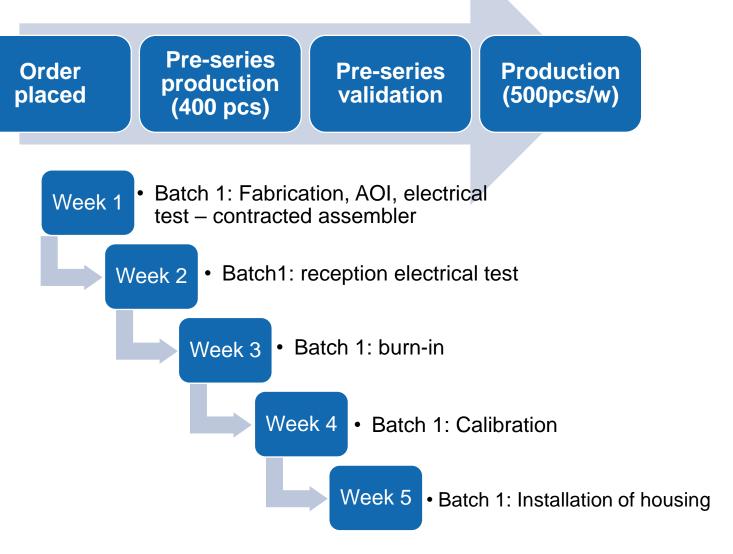

## 2 VFE production plan – fabricate 14600 pcs

#### First there is a plan:

- Components:

- All passives purchased by assembler, including PCB

- Except: connectors, long lead time, already purchased

- Electrical Test-setups

- Manpower

- Pre-series qualification up to 3 months

- ASIC testing done by industry:

- Launch VFE production with 10000

CATIA and 10000 LiTE-DTU in hand (4 weeks contingency)

- Testing, environmental stress screening, calibration and finalization follow the production pace

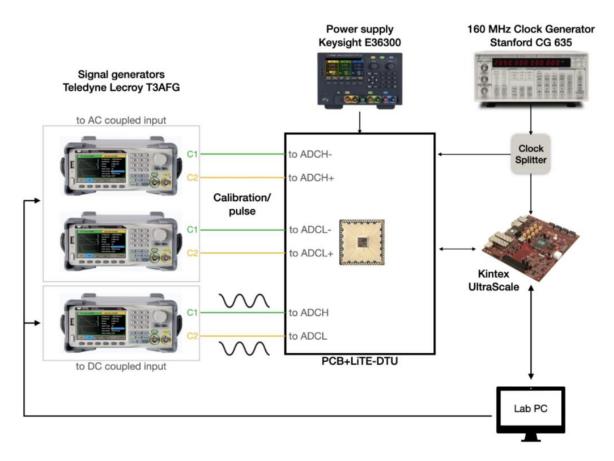

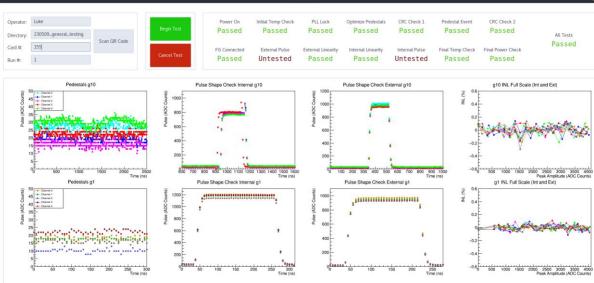

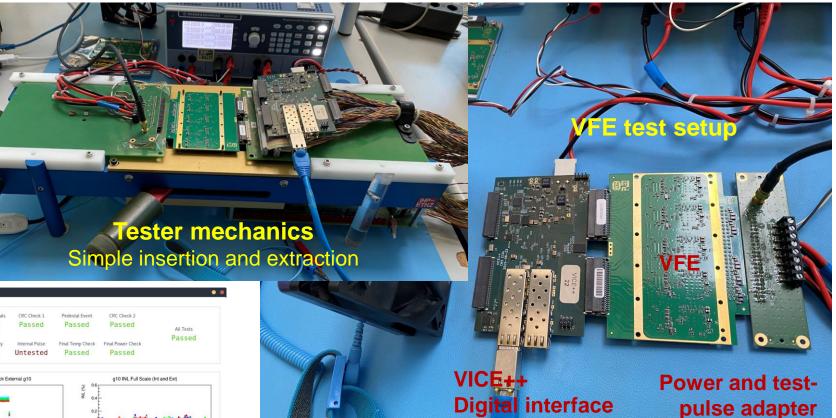

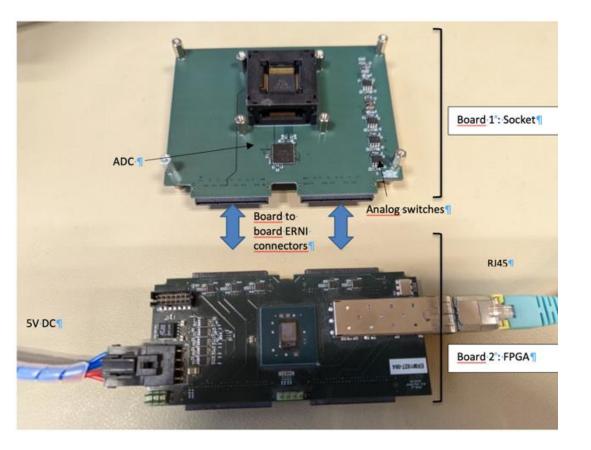

## 2 VFE test setup – easy to handle – fast test

#### **Test setup: 4 copies**

- Test by assembler

- Reception test at CERN

- Calibration in Torino

- spare

#### **Features**

- Fully automatized

- Data stored in DB

#### Test program GUI

#### **Testing full functionality**

- PLL locking, CRC errors

- Pedestals, Test pulse

- More...

#### Test duration: ~1 min.

#### ETH zürich Institute for F

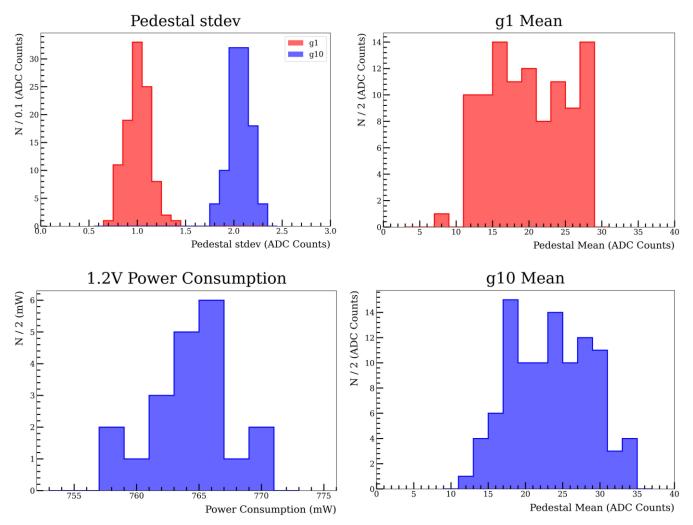

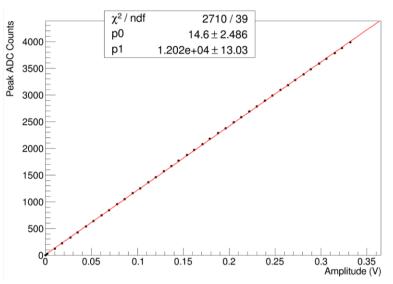

## 2 VFE test setup – results statistics - calibration

#### **Measurement statistics identifies outliers**

• Adjustment of pass/fail criteria

#### **Optional pulse generator**

- precise calibration:

- Tektronix AFG31252

- 250MHz 14bit 2GS/s

## 6 Environmetal stress screening (burn-in)

#### Active burn-in setup for 500 VFE cards

- LVR and VFE cards simultaneously in the same setup:

- safe powering of VFE

- Correct load for LVR

#### Safety

**ETH** zürich

- Siemens PLC system

- Two temperature sensors per box

- Interlock of power supplies

#### 10V, 40A supplies Keithley DAQ 6510

#### Stable temperature ~70°C reached

#### Test box

- PCB housing with extra fans

- 9 towers

- Total: 12 boxes

#### **Monitoring and control** Monitoring: Keithley DAQ 6510

- Two temperatures per tower

- T\_stability: ±1.5°C

- T\_spread: ~5°C

#### Arduino microcontroller:

- Power good of LVRs

- Fan speed control

#### Laptop

- Power supply control

- Software

#### Dedicated aging study (50 VFE, 10 LVR):

- Temperature cycles: ambient 70°C (power OFF ON)

- Identify end of infantile mortality and end of life

- Age all cards until after infantile mortality

## Summary

Keys to success, for high quality high reliability VFE cards in a large scale production:

### **Design for Reliability and Manufacturing**

Application of appropriate standards

**Components selection and ASIC testing**

#### Production and testing have to go hand in hand

- Production, reception and qualification plan

- Selection of appropriate assembly company

- Production yield monitoring

- Factory acceptance tests

#### In house reception and qualification testing:

Electrical testing, environmental stress screening, calibration

Dr. Werner Lustermann Werner.Lustermann@cern.ch

ETH Zurich Institute for Particle Physics and Astrophysics HPK D29 Otto-Stern-Weg 5 8093 Zurich, Switzernland

ipa.phys.ethz.ch

c/o CERN PH Departement 1211 Geneva 23, Switzerland

## **Additional material**

## 2 Testing of ASICs

- CATIA: CEA-Saclay

- Test setup prepared

- To be done in industry

- LiTe-DTU: INFN Torino

- Test concept defined,

- Testing and setup preparation by industry partner