Fig. 1 RD50-MPW3 prototype in the Mimosa-26 telescope at the CERN 2022 test beam.

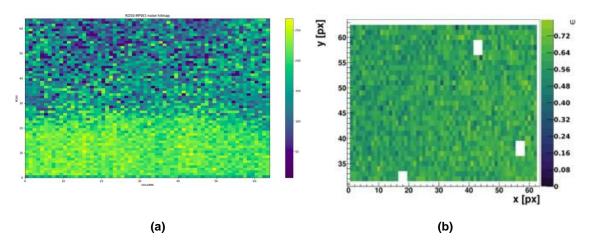

**Fig. 2** RD50-MPW3 noise hit map with a threshold voltage of 300 mV above the baseline voltage and a measuring time of 2 s (a), and efficiency measured at the CERN test beam (b).

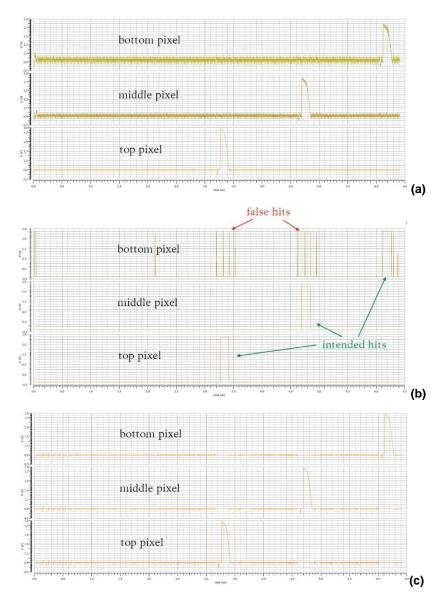

**Fig. 3** Post-layout simulations of the amplifier (a) and comparator (b) for several pixels and part of the digital periphery when having joint digital in-pixel and digital peripheral power and ground domains, and of the amplifier (c) when having separate power and ground domains.

**Table 1** Main design details and performance parameters of the RD50-MPW pixel chips. <sup>(1)</sup>Half of the chip has a pixel matrix for applications beyond physics; <sup>(2)</sup>anticipated values for RD50-MPW4.

| Parameter                     | RD50-MPW1                   | RD50-MPW2                         | RD50-MPW3                                                                                    | RD50-MPW4                                                                                   |

|-------------------------------|-----------------------------|-----------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Device size [mm x mm]         | 5 x 5 <sup>(1)</sup>        | 3.2 x 2.1                         | 5.1 x 6.6                                                                                    | 5.4 x 6.3                                                                                   |

| Pixel matrix size             | 40 x 78                     | 8 x 8                             | 64 x 64                                                                                      | 64 x 64                                                                                     |

| Pixel size [µm x µm]          | 50 x 50                     | 60 x 60                           | 62 x 62                                                                                      | 62 x 62                                                                                     |

| P-n spacing [µm]              | 3                           | 8                                 | 8                                                                                            | 8                                                                                           |

| In-pixel electronics          | Analogue<br>Digital         | Analogue                          | Analogue<br>Digital                                                                          | Analogue<br>Digital                                                                         |

| Output data                   | Pixel address<br>Time-stamp | Binary                            | Pixel address<br>Time-stamp                                                                  | Pixel address<br>Time-stamp                                                                 |

| Digital periphery             | 78 EOCs<br>2 LVDs lines     | 8 EOCs                            | 32 EOCs, with 32-events 24-bit FIFOs 128-events 32-bit TX FIFOs I2C Wishbone bus 1 LVDs line | 32 EOCs, with 16-events 24-bit FIFOs 64-events 32-bit TX FIFOs I2C Wishbone bus 1 LVDs line |

| Chip guard ring frame         | None                        | 1 n-ring<br>6 p-rings             | 1 n-ring<br>6 p-rings                                                                        | 1 n-ring<br>5 n-/p-rings                                                                    |

| Substrate biasing             | Through p-stop contacts     | Through p-stop contacts           | Through p-stop contacts                                                                      | Through chip<br>edge or<br>backside                                                         |

| Substrate resistivity [kΩ·cm] | 0.5 – 1.1<br>1.9            | Standard<br>0.2 – 0.5<br>1.9<br>3 | Standard<br>1.9<br>3                                                                         | Standard<br>3                                                                               |

| Device thickness [µm]         | 280                         | 280                               | 280                                                                                          | 280                                                                                         |

| V <sub>BD</sub> [V]           | 56                          | 120                               | 120                                                                                          | > 400 <sup>(2)</sup>                                                                        |

| I <sub>LEAK</sub> [µA/pixel]  | 1                           | 1E-4                              | 1E-6                                                                                         | 1E-6 <sup>(2)</sup>                                                                         |

| Depletion depth [µm]          | 118                         | 110                               | Not tested                                                                                   | Fully depleted <sup>(2)</sup>                                                               |

| ENC [mV]                      | 50                          | 2                                 | < 140, > 50                                                                                  | 50 <sup>(2)</sup>                                                                           |

| Efficiency [%]                | Not tested                  | Not tested                        | 60                                                                                           | > 99(2)                                                                                     |