Karlsruhe Institute of Technology

# AstroPix – A novel HV-CMOS pixel sensor for spacebased experiments

Nicolas Striebig\*<sup>a</sup>, R. Leys<sup>a</sup>, I. Peric<sup>a</sup>, R. Caputo<sup>b</sup>, A.L. Steinhebel<sup>b</sup>, Y. Suda<sup>c</sup>, M. Jadhav<sup>d</sup>, D. Violette<sup>b</sup>, C. Kierans <sup>b</sup>, H. Tajima <sup>e</sup>, Y. Fukazawa <sup>c</sup>, J. Metcalfe <sup>d</sup>, J.S. Perkins <sup>b</sup>

\*nicolas.striebig@kit.edu

## **Motivation: Gamma-ray Astrophysics**

**AstroPix3: First full reticle size prototype**

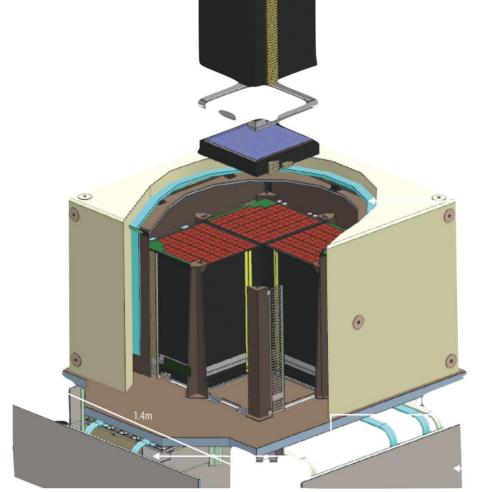

- Developed for AMEGO-X mission concept proposed by NASA

- Multi-messenger astronomy

- HV-CMOS based Tracker:

- 4 Towers with each 40 layers

- 64000 sensors and 25 m<sup>2</sup> active area

## **Requirements:**

- Fully depleted 500 um thick sensors

- Low power 1.5 mW/cm<sup>2</sup>

- High dynamic range 20 700 keV

Caputo, R. et al. "The All-sky Medium Energy Gamma-ray Observatory eXplorer (AMEGO-X) Mission Concept"

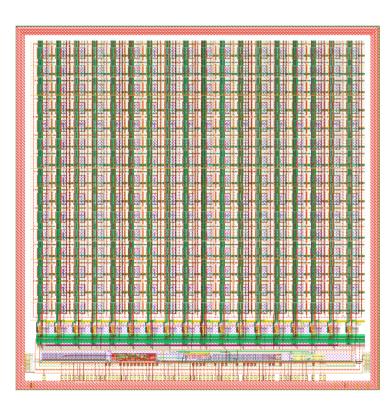

- Implemented in TSI 180 nm process

- Submitted in May 2022

- Chip size: 2 cm × 2 cm

- Pixel matrix: 35 columns, 35 rows

- Pixel size: 300 µm × 300 µm

- OR'd row/column-based readout

- ToA: 8 bit counter (2.5 MHz external clock)

- -un, currently being characterized ToT: 12 bit counter (200 MHz external clock)

## AstroPix4

**Specifications**

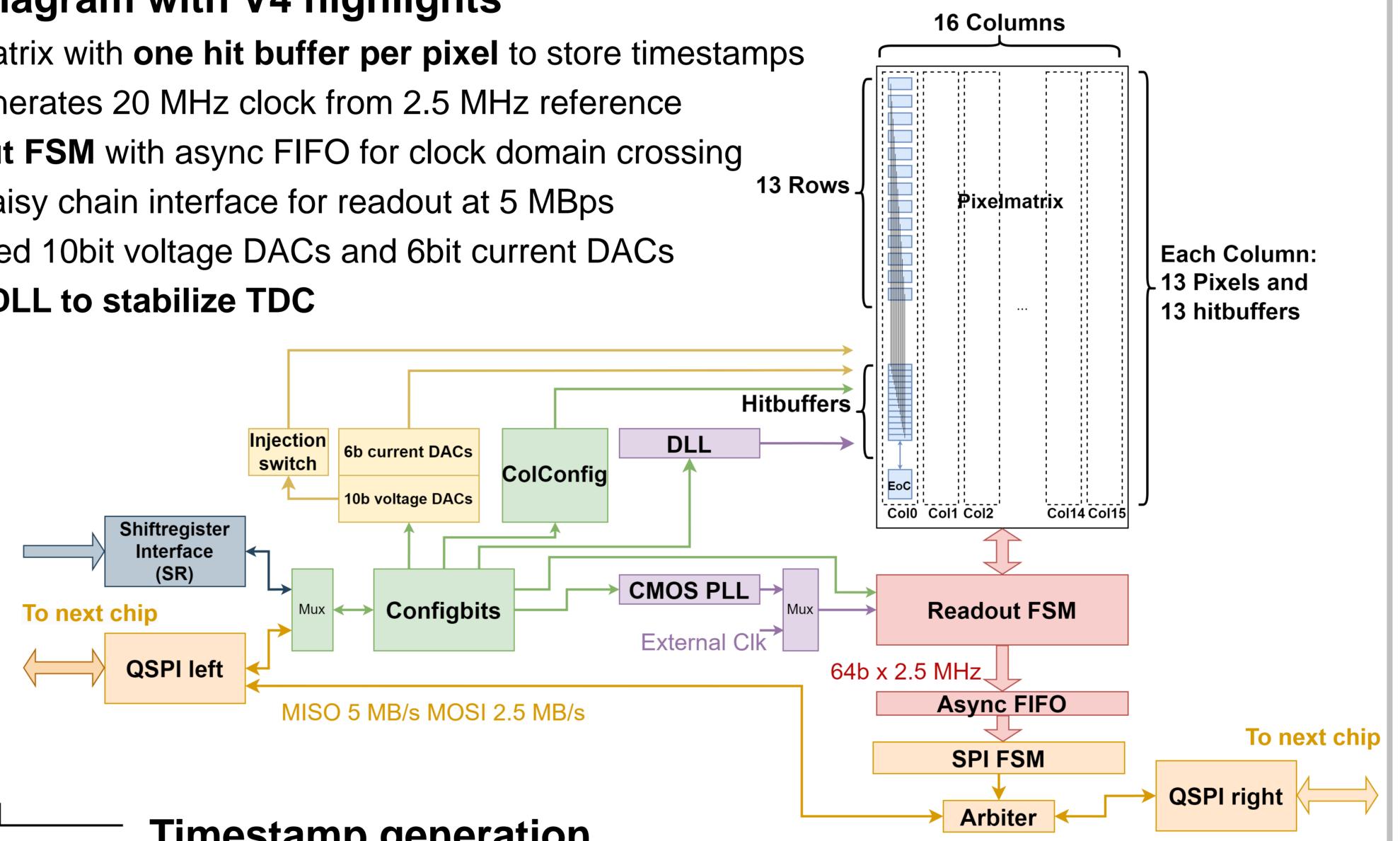

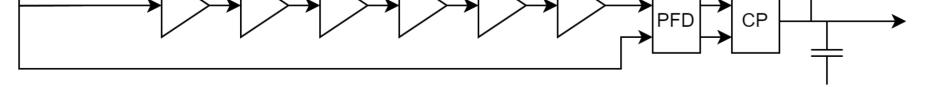

## **Block diagram with V4 highlights**

- Pixel matrix with one hit buffer per pixel to store timestamps

- PLL generates 20 MHz clock from 2.5 MHz reference

- Readout FSM with async FIFO for clock domain crossing

- QSPI daisy chain interface for readout at 5 MBps

- Integrated 10bit voltage DACs and 6bit current DACs

- Global DLL to stabilize TDC

- 1 x 1 cm<sup>2</sup> chip in TSI 180nm process

- Pixel matrix: 16 columns, 13 rows

- Pixel size: 300 μm × 300 μm

- Pixel pitch: 500 µm

## Improvements over V3

- Per-pixel readout architecture

- Reduced pixel capacitance by 30% 3 bit TuneDAC per pixel

#### clk20 20 MHz Hit TDC DRAM DRAM DRAM DRAM RAM clk20 Vctrl\_del

## **Timestamp generation**

- Coarse timestamps saved in DRAM at leading and trailing edge of a hit

- 17 bit x 20 MHz generated by global counter

- 1 bit x 20 MHz negative edge timestamp

- 17 bit Flash-TDC measures time from both edges to next rising clock edge with 3 ns resolution

- Delay elements based on two current starved inverters

- Connected to DRAM cells

### 50 ns total delay controlled by global DLL

## Summary

- Submitted new AstroPix4 design in May 2023, currently in production

- Should fulfil AMEGO-x requirements, plan to build balloon prototype (ComPair)

- Improved time-of-arrival resolution from 400 ns and ToT resolution from 5 ns to 3 ns

- Reduced module complexity and power consumption by removal of ext. 200 MHz ToT clock Implemented per-pixel readout and tuning capability

#### Affiliations

- IPE-ADL, Karlsruhe Institute of Technology a.

- NASA Goddard Space Flight Center b.

- Hiroshima University C.

- Argonne National Laboratory d.

- Institute for Space-Environment Research, e. Nagoya University