### DESIGN OF THE OBELIX MONOLITHIC CMOS PIXEL SENSOR ( ) FOR AN UPGRADE OF THE BELLE II VERTEX DETECTOR

Dr. Thanh Hung PHAM (On behalf of Belle II VTX Collaboration) hung.pham@iphc.cnrs.fr

Abstract: The Belle II collaboration has initiated a program to upgrade its detector in order to address the challenges set by the increase of the SuperKEKB collider luminosity, targeting 6x10<sup>35</sup> cm<sup>2</sup>s<sup>-1</sup>. A monolithic CMOS pixel sensor named OBELIX (Optimized BELLe II pIXel) is proposed to equip 5 detection layers upgrading the current vertex detector. Based on the existing TJ-Monopix2, OBELIX is currently designed in 180 nm CMOS process.

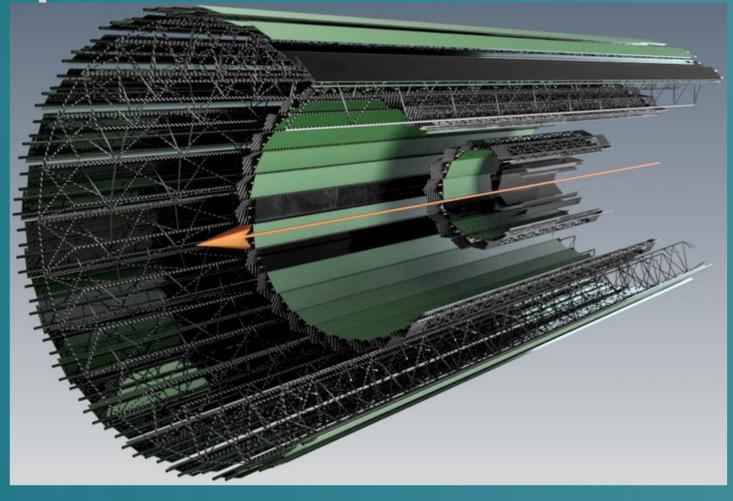

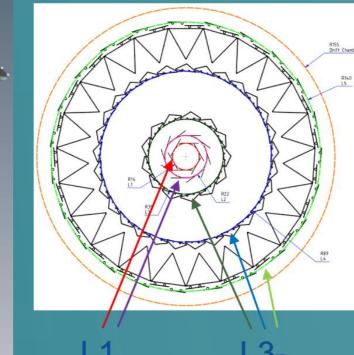

### Belle II Vertex VTX Detector Upgrade Proposal

Radii from 1.4cm to 14cm Angular acceptance 17 to 160 degrees ~1 m<sup>2</sup> silicon surface equiped with OBELIX sensor

oVTX

**iVTX**

| From simulations                         | Belle II VTX                                             |

|------------------------------------------|----------------------------------------------------------|

| Spatial res.                             | <10-15µm                                                 |

| Total material budget Inner-outer layers | 0.1 - 0.8 %Xo                                            |

| Max hit rate                             | 120MHz/cm <sup>2</sup>                                   |

| Time precision                           | <100ns                                                   |

| Trigger (freq)<br>(delay)                | 30 kHz<br>5-10µs                                         |

| Rad.hard. (TID)                          | <100 kGy/year                                            |

| (fluence)                                | $<50$ x $10^{12}$ n <sub>eq</sub> cm <sup>-2</sup> /year |

| Power                                    | <200mW/cm <sup>2</sup>                                   |

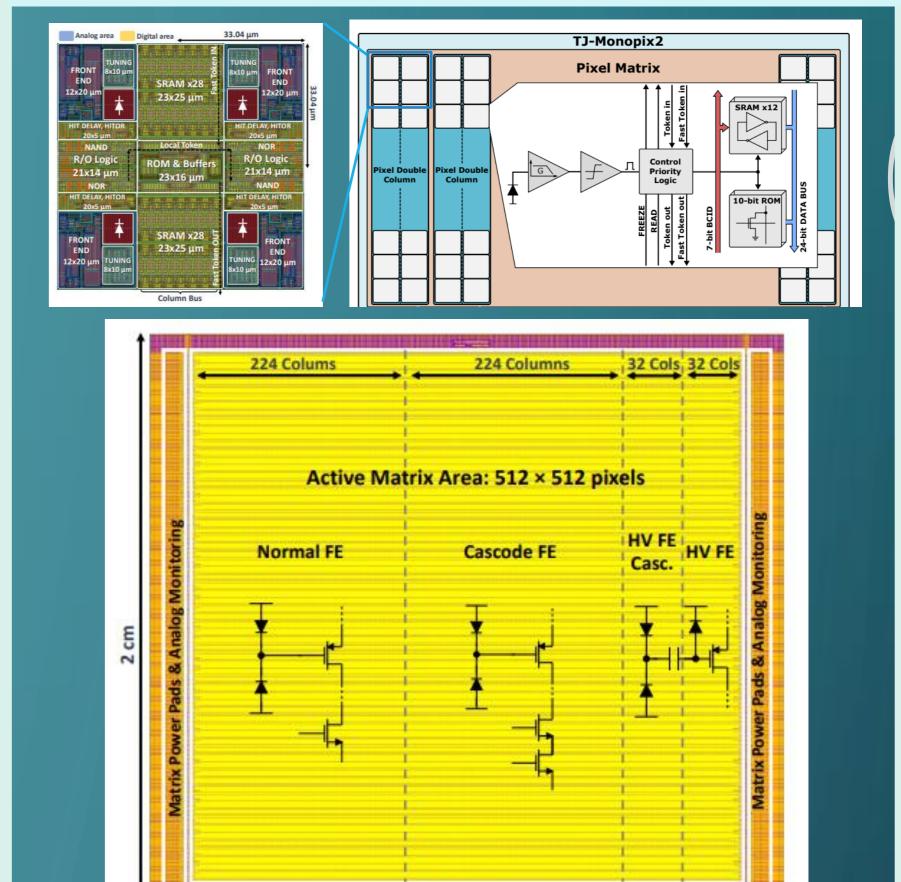

#### TJ-Monopix2 sensor

(Developed for ATLAS-ITK:

doi: 10.1016/j.nima.2020.164460)

Operation demonstrated with average threshold ~200e- and threshold spread < 20e-

TJ-Monopix2 pixel performances fit Belle II VTX specifications  $\rightarrow$  forerunner for OBELIX

#### **Analog & Integration**

Additional analog functionalities:

- Increase pulsing calibration pulse dynamic from ~1700e- to 2400e-

- Temperature sensor

- 10-b Monitoring ADC

- PowerOn Reset (Y. Degerli IRFU Institut)

Total width =  $30040 \, \mu m$

- 464x896 pixels of 33.04x33.04µm<sup>2</sup>

- Column-drain architecture

9

$\infty$

$\infty$

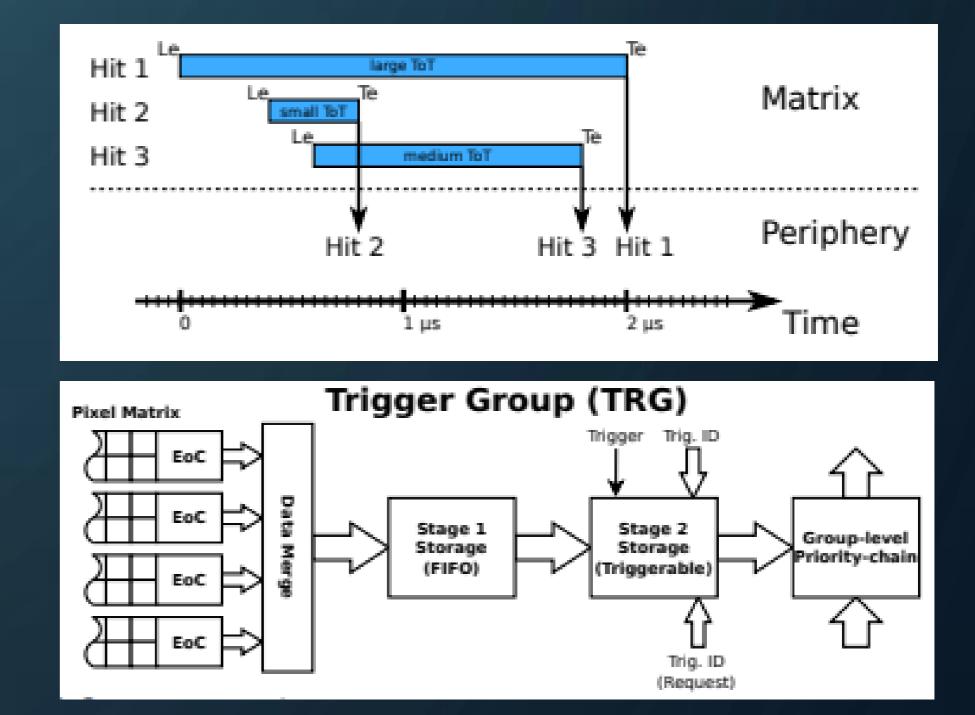

- 7-b LE (Leading Edge) & TE (Tailing Edge) of 50n timing bin

- 3-b Threshold trimming per pixel

- Sensitive area +30%: 17x17mm<sup>2</sup>  $\rightarrow$  15x25mm<sup>2</sup>.

- Narrow LDO regulators (270µm) to compensate for the voltage drop on the ladder

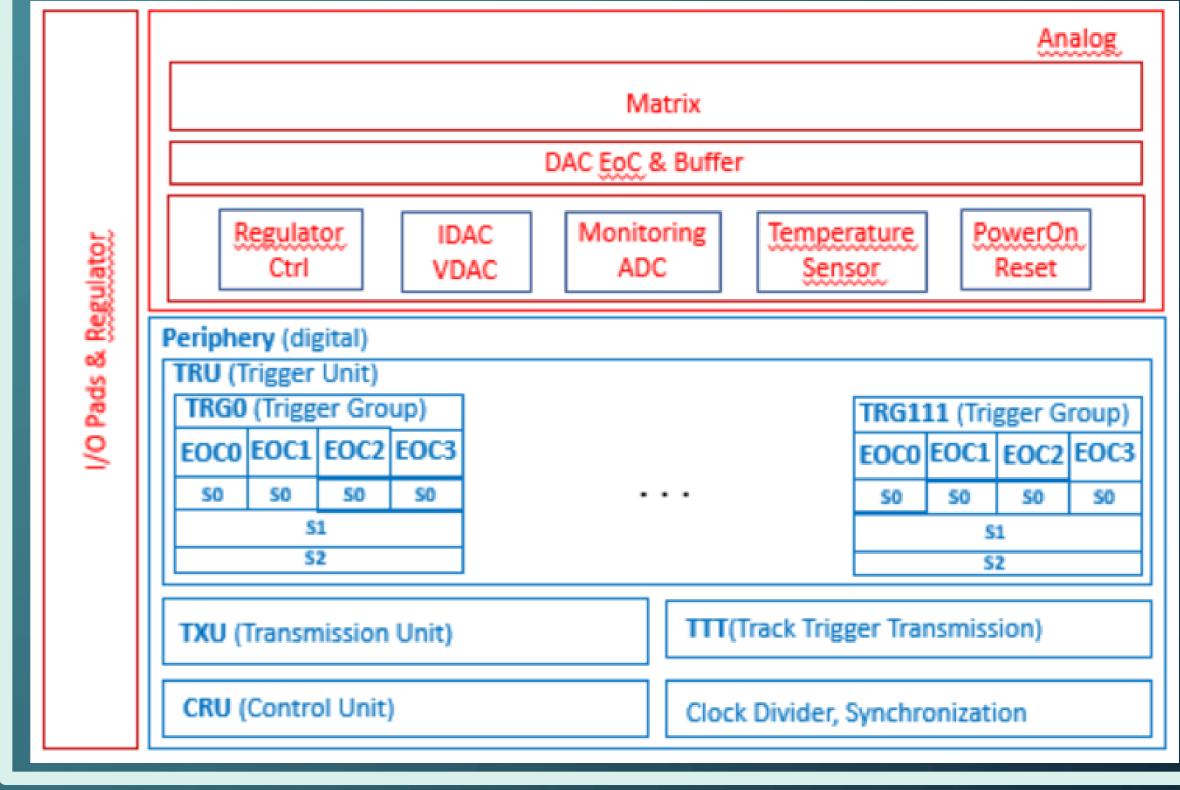

# **OBELIX Functional blocs**

Preminilary IR Drop estimation

Digital On Top (DoT) integration flow

- Early power distribution analysis

- Flexible floorplan implementation & further modification

- Re-adaptation of matrix and DAC EoC layout from Analog On Top (AoT) flow

## Digital functionalities

New digital functionalities:

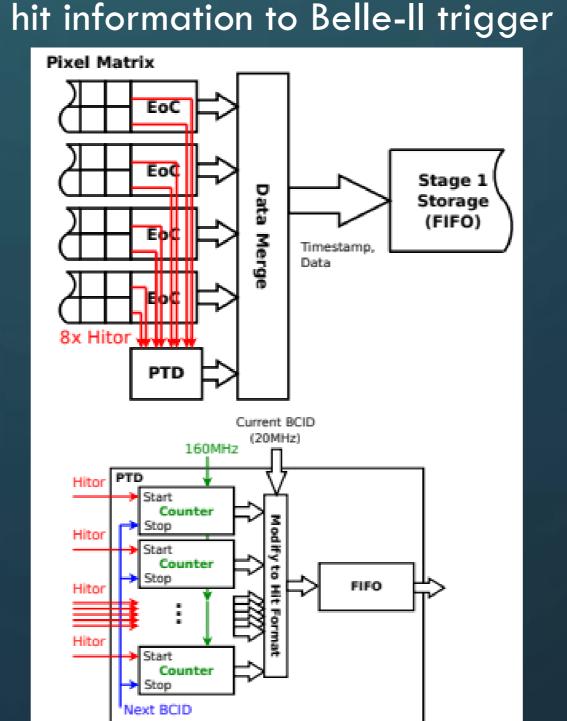

- 2-stages trigger logic

- Peripheral Time To Digital (PTD) converter based on HitOr signal from matrix & 160MHz clock  $\rightarrow$  better resolution than 50ns

- Track Trigger Transmission (TTT): 2 to 8 logical macro pixel for whole matrix to provide coarse

Peripheral Time To Digital Converter

2-stages trigger logic to handle VTX trigger & disorder peripheral event arrival times

TWEPP 2023 Geremeas, Sardinia, Italy