# An open-sorce IP-Core for Multi-Voltage Thresholding signal acquisition with FPGAs

03.10.2023 - TWEPP 2023

**Dmitry Eliseev**

**III. Physikalisches Institut A; RWTH Aachen**

SPONSORED BY THE

Federal Ministry of Education and Research

#### **Basic principle of Multi-Voltage Thresholding (MVT)**

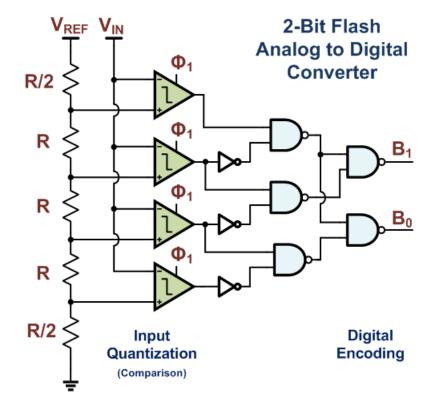

The basic principle of the presented concept is the same as with Flash-ADCs:

- Voltage ladder (providing ref. Voltages),

- **Comparators** (compare the input voltage to successive reference voltages),

- **Digital encoding circuit** (digital output)

#### Pro:

- Concept enables very fast digitization Drawback:

- Higher resolution demands a huge number of comparators  $(2^n-1)$

2-bit flash-ADC with digital encoding circuit (source: Wikipedia)

### **FPGA-intern comparators**

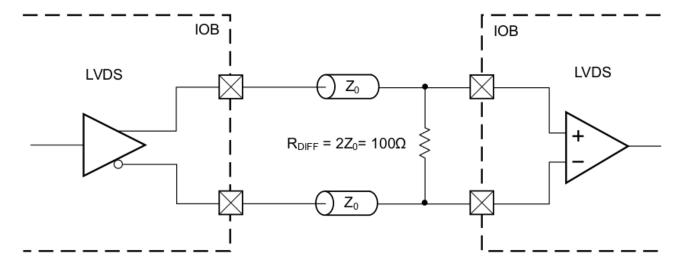

Most of the FPGA pin pairs are capable of Low-Voltage Differential Signaling (LVDS)

Input-Output Block. Source: Xilinx Datasheet UG571.

3

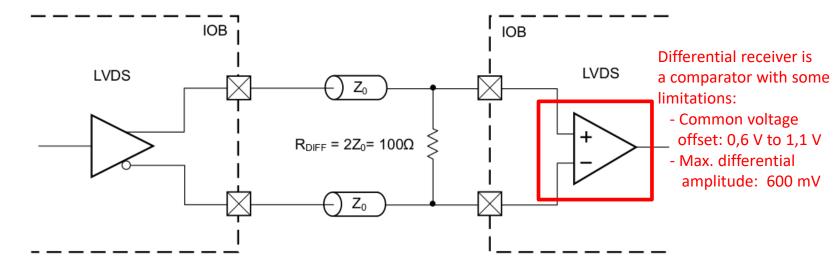

## **FPGA-intern comparators**

Typically most FPGA pins can work in differential mode. Let's use FPGA's diferential receivers for implementing a flash-ADC

Source: Xilinx Datasheet UG571. Abbreviation IOB stands for Input-Output Block

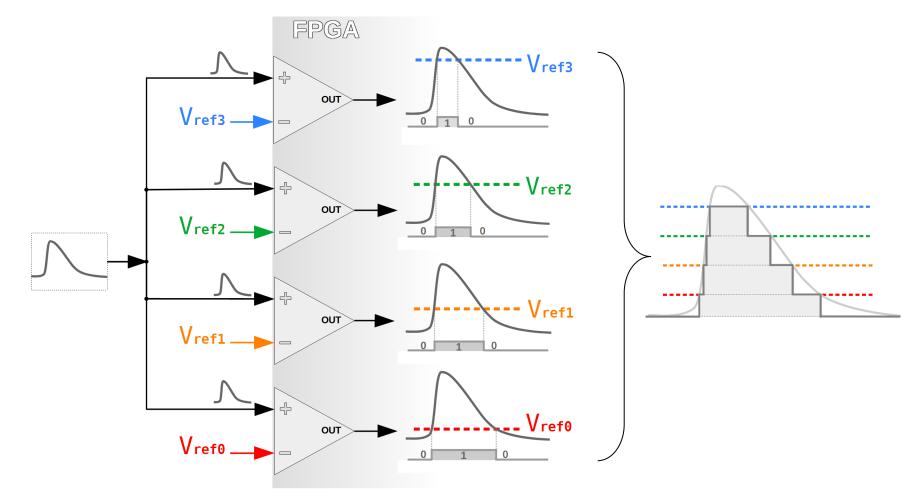

### **MVT-Quad IP-Core**

Our IP-Core enables implementation of four LVDS-comparators. Sampling rate tested: 800MSPS

An eight-channel FMC-module and an implementation example are present in the poster as well

5

TWEPP 2023