# CMS ECAL Upgrade Front End card Design and performance tests

A.Dolgopolov, A.Singovski, University of Notre Dame, USA

On behalf of the CMS Collaboration

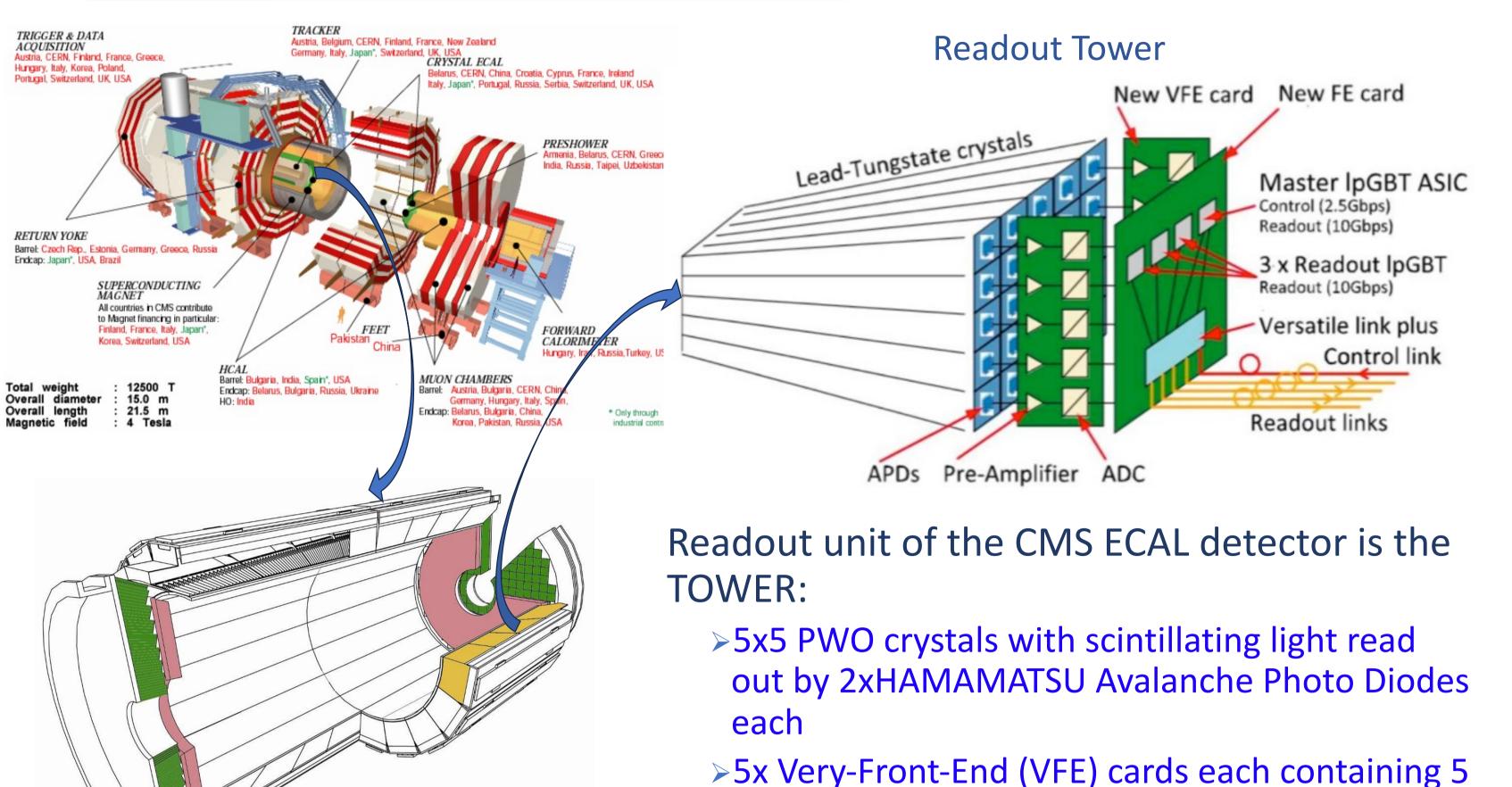

# Phase II ECAL on-detector electronics Upgrade

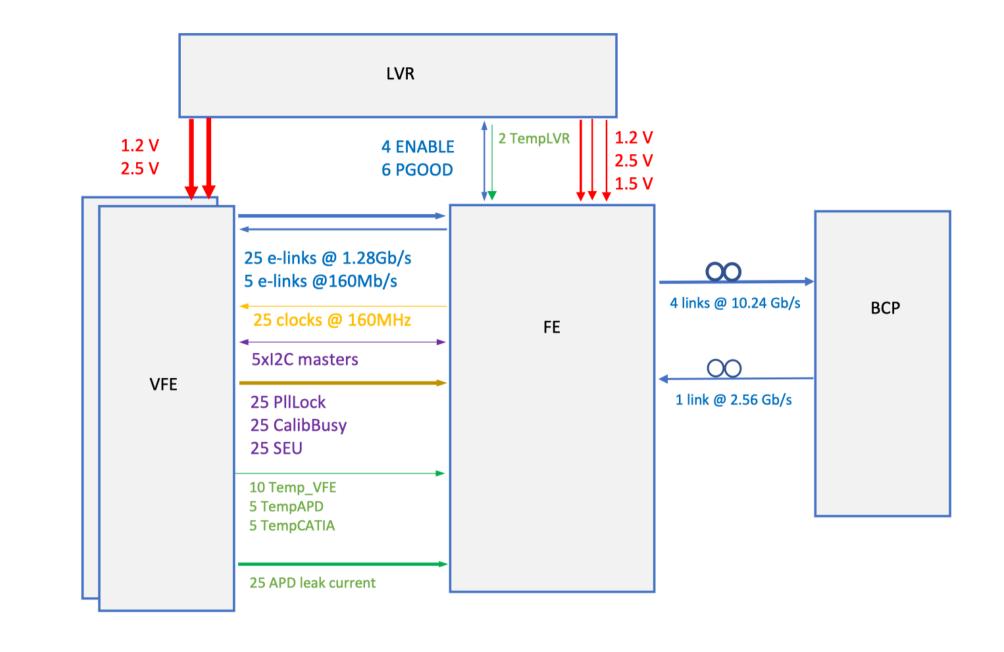

FE powering

# Upgrade FE card functionality

Upgrade FE card is the interface between intelligent VFE chips, CATIA and LiTE-DTU and powerful FPGA – based Barrel Calorimeter Processor (BCP). It provides:

- ✓ 160MHz clock distribution to the VFE readout channels

- ✓ VFE, LVR and FE chips configuration and control via I2C interfaces, one per VFE and LVR board

- ✓ Lossless data streaming from VFE readout channels via 1.28Gb/s serial links (lpGBT – links mechanism)

- ✓ Data transmission to BCP via four 10.24Gb/s optical links

- ✓ Chips status, temperature, power voltage, APD dark current readout via I2C interface and lpGBT optical up-link at 2.56Gb/s

# Implementation

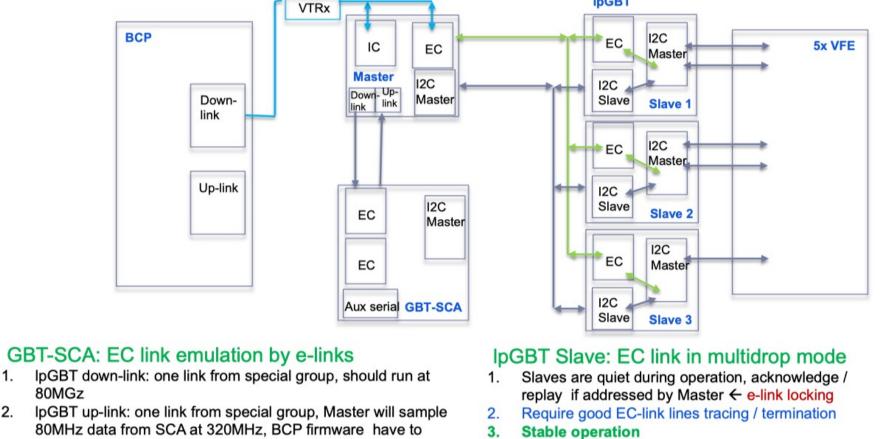

FE – VFE slow control

Electromagnetic Calorimeter

(ECAL)

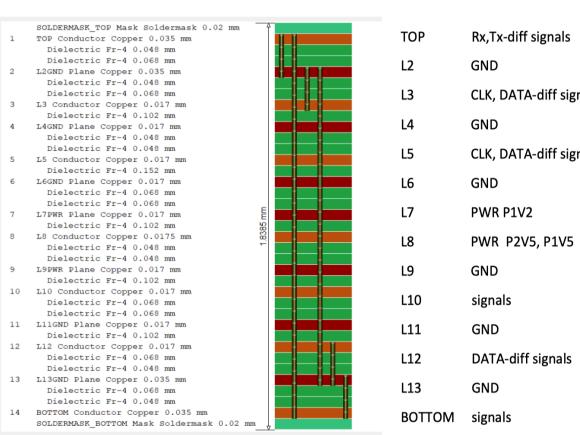

FE PCB stack out

- Class 3 PCB

- 14 layers

- Micro-vias between layers 1-2, 2-3, 14-13, and 13-12

double gain pre-amplifiers (CATIA) and 5 ADC

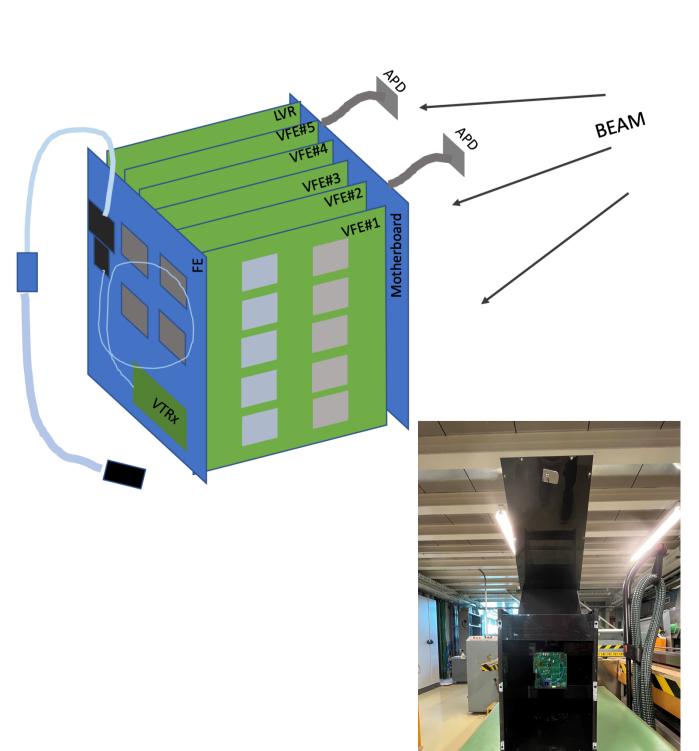

> 1x Front-End (FE) card with 4x lpGBT 1x GBT-

➤ 1x Low Voltage Regulator (LVR) card for VFE and

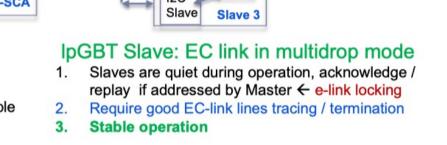

4x lpGBT chips, one in TRx mode (Master) and three

1x GBT-SCA chip for the APD dark current readout

1x 4T1Rx Versatile link optical transceiver

and data management chips (LiTE-DTU)

SCA and 1x 4T1Rx optical transceiver

in Tx mode (Slaves)

Serial lines impedance control with 10% precision

# Functionality tests

### Stand-alone test

- Will be performed by the assembly company

- Electrical I2C control via PiGBT interface

- Electrical system clock from external clock generation

- lpGBT chips configuration

- 12C registers read/write

### Functional test

- Will be performed at CERN upon reception Clock, control and readout via optical links from BCP

- Production LVR and VFE board for power, control and

- readout

- Full configuration of FE chips

- Full configuration of VFE chips

- Data alignment, PED and test pulse readout

# Thermocycling and burning-in

- Climatic chamber

- Power to FE from external source

- Electrical I2C via PiGBT and Keithley switch

- Burning-in at 70C during 72 hours Periodic thermocycling 70C→9C→70C

- Periodic I2C initialization configuration

- Full functional test at the end of operation

- Special thanks to T. Gadek and C. Haller, ETH Zurich, for providing the VFE and LVR cards and

for preparing the test setup for the readout tower test, respectively.

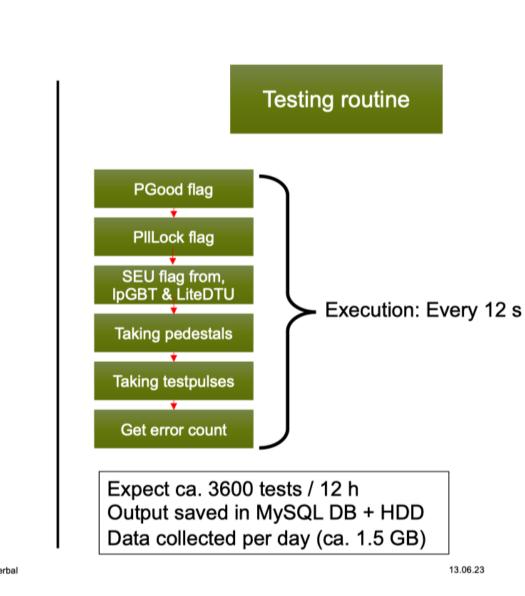

# Full readout tower validation in radiation environment

- A complete tower with the latest versions of VFE and FE

- Five APD capsules connected to VFE 0

- Continues Reset/Config/Readout cycles by ECAL off-detector readout board (BCPv1)

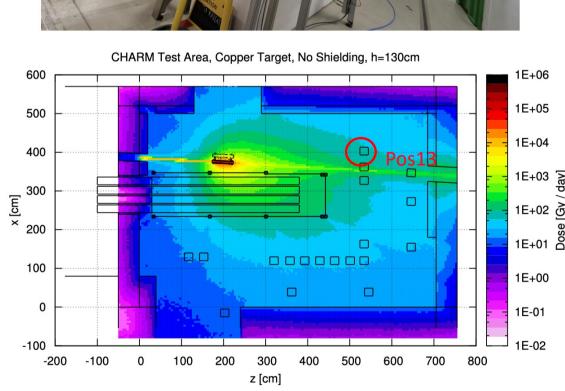

**CERN CHARM facility**

Tower at  $\eta$ =1.41 vs CHARM pos13

|                      | HL-LHC (3000 fb <sup>-1</sup> )            | CHARM (17 days)                              |

|----------------------|--------------------------------------------|----------------------------------------------|

| Dose rate            | $9.57e-05 \; \text{Gy s}^{-1}$             | $7.84e-04 \; \mathrm{Gy} \; \mathrm{s}^{-1}$ |

| Charged hadron flux  | $7.38e + 04 \text{ cm}^{-2} \text{s}^{-1}$ | $1.48e+06 \text{ cm}^{-2}\text{s}^{-1}$      |

| Total dose           | 5'740 Gy                                   | 1'380 Gy                                     |

| Total Hadron fluence | 4.43e+12 cm <sup>-2</sup>                  | 5.48e+12 cm <sup>-2</sup>                    |

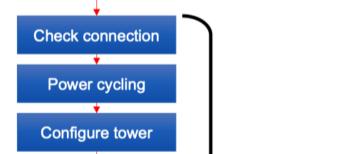

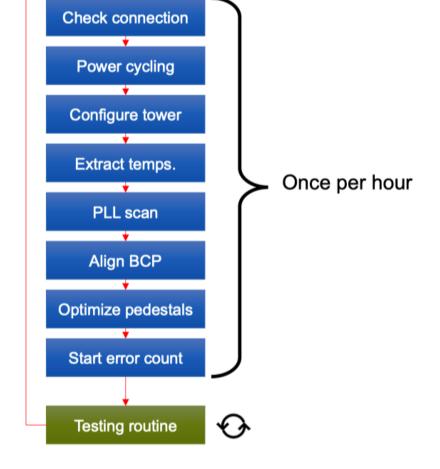

Readout routine

- Stable operation in hostile radiation conditions (Charged hadrons flux 20 times higher than max. expected for ECAL tower at HL-LHC at  $\eta = 1.41$ )

- SEU cases detected and handled by chips

- Good APD dark current readout by GBT-SCA ADC

1WEPP-23 **Topical Workshop on Electronics for Particle Physics** Geremeas, Sardinia, Italy, 2 – 6 October 2023