## **Digital Processing Prototype** for the SPS BLM System at CERN

M. Saccani<sup>\*</sup>, E. Effinger, F. Martina, JM. Meyer, W. Viganò, and C. Zamantzas, CERN, Geneva, Switzerland

## TWEPP-23

**Topical Workshop on Electronics for Particle Physics** Geremeas, Sardinia, Italy, 2 – 6 October 2023

## Abstract

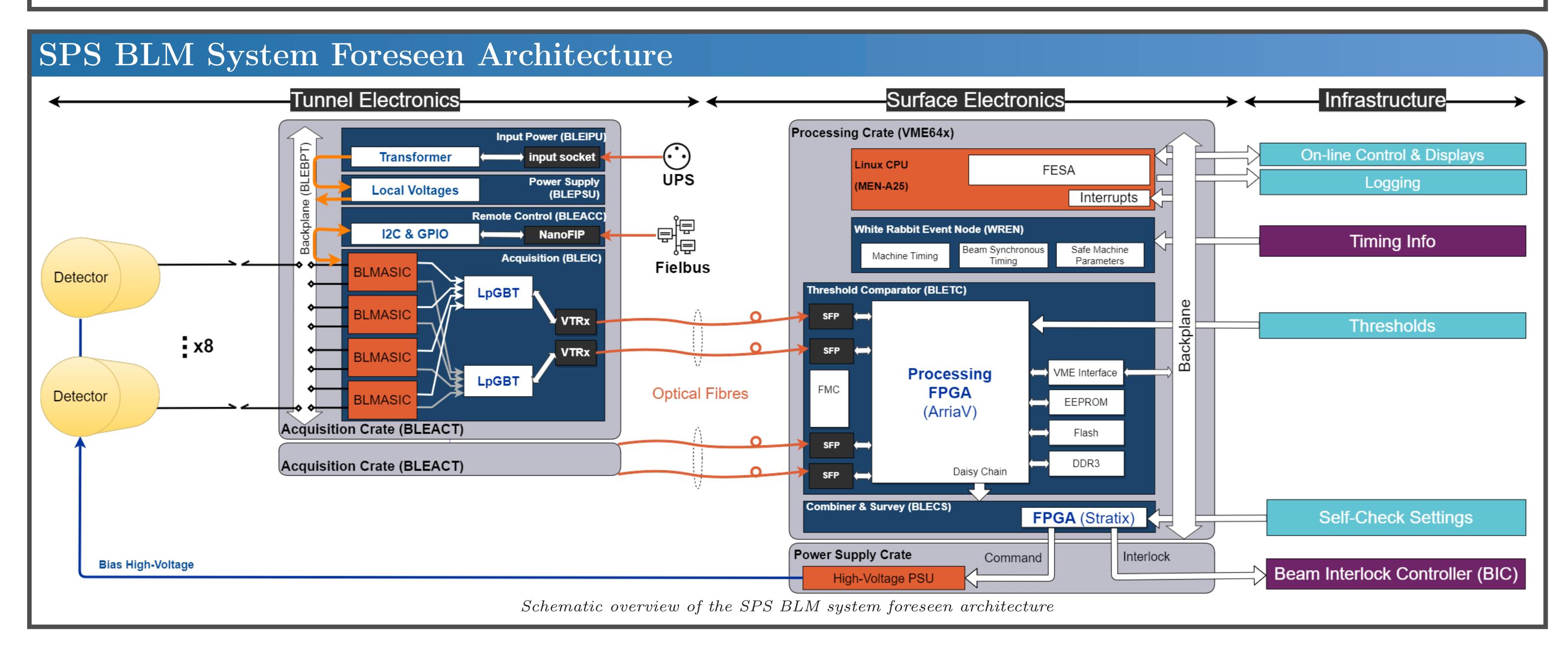

The Beam Loss Monitoring system plays a crucial role in the CERN's Super Proton Synchrotron beam monitoring and machine protection. With the upcoming renovation of the system, the acquisition electronics can be based on an innovative ASIC designed by CERN. This paper presents the development of the control and digital processing electronics for this BLMASIC, reviews the architecture and design choices, discusses implementation details, including the controls and redundancy schemes, and highlights some preliminary results. The conclusion outlines the future development steps, and emphasises the interest of this simple and robust architecture using LpGBT and VTRx for critical systems.

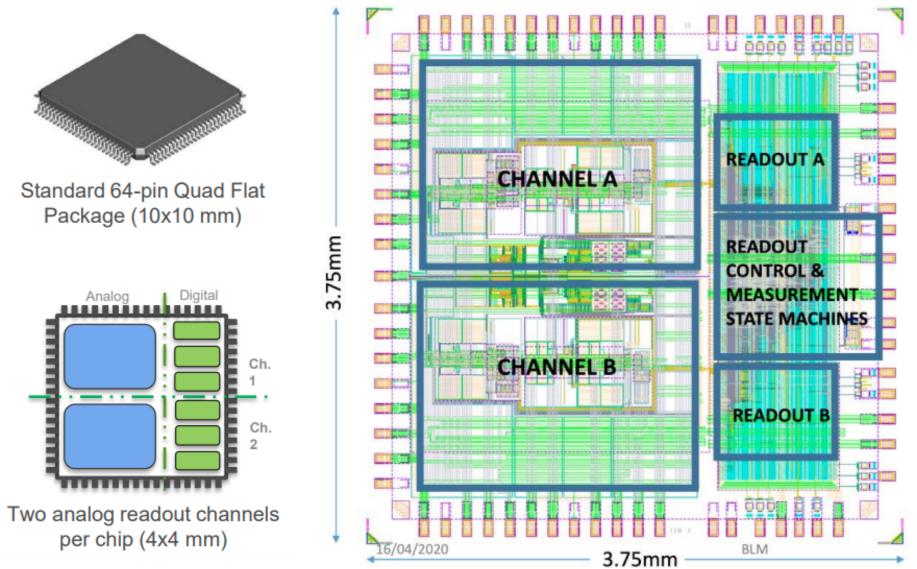

BLEIC Architecture and Layout Top View

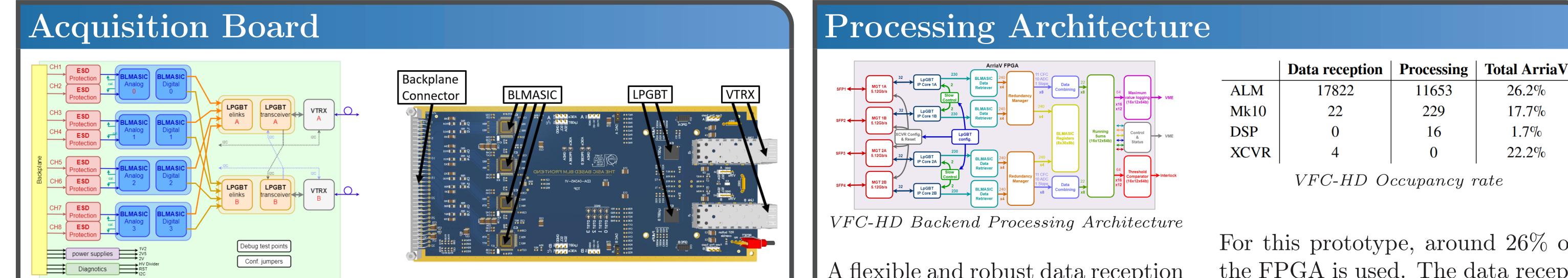

The BLM SPS Acquisition electronics (BLEIC) is fully based on radiationhard components designed at CERN by EP-ESE:

| Component | Description                         | Tested TID |

|-----------|-------------------------------------|------------|

| BLMASIC   | current to frequency conversion     | 3 kGy      |

| LpGBT     | high-speed serial & and I2C control | 3M Gy      |

| VTRx      | optical transceiver                 | 10 kGy     |

A flexible and robust data reception module was developed on VFC-HD to reliably receive the BLMASIC data through two redundant pairs of optical links. An embedded FSM automatically connects, configures the remote electronics and continuously checks the link quality to select the best one.

|                       |   |    | 17.770 |  |  |  |  |  |

|-----------------------|---|----|--------|--|--|--|--|--|

| DSP                   | 0 | 16 | 1.7%   |  |  |  |  |  |

| XCVR                  | 4 | 0  | 22.2%  |  |  |  |  |  |

| VFC-HD Occupancy rate |   |    |        |  |  |  |  |  |

For this prototype, around 26% of the FPGA is used. The data reception block for 4 optical links utilizes 15% of the logic, with potential for optimization of diagnostics. Meanwhile, the measurement processing module accounts for approximately 10%, with plans to better meet the operator's requirements and add new features.

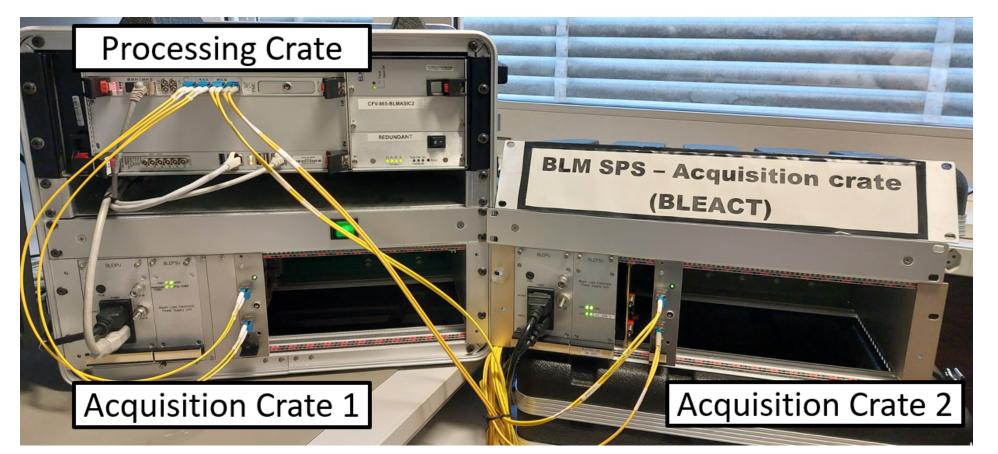

## Prototype Setup & BLMASIC

A standard VME crate, the BLEACT acquisition crate and a NUC for storing raw data, have been integrated into a movable box to ease installation and change of location. A second crate was added in the lab to test the acquisition of 16 channels (4 optical links in parallel). This prototype will be installed in the SPS in 2024 to get data with beam and real monitor and cabling and real beam data.

the first time on this project. Although not a real-time tool, this interface uses the full power of Python and enables rapid debugging by simply deploying the new EDGE reader on the debelow 1% in the range [35 µA;1 mA]. sired FEC, and provides graphics, logging and read/write register polling.

The BLMASIC, developed at CERN by EP-ESE, The EDGE GUI is a new BI tool, used first was fully characterized and tested up to 3 kGy. It uses a current-to-frequency converter combined with an ADC, to provide a 10 µs readout and loss measurements down to 1 pA with an error

Prototype setup in the lab

| ettings <u>T</u> ools <u>T</u> heme <u>F</u> ont    |                                         | hi himteene           | ;/3/rxStatLink1A             | _ 🗆 🗙  | bi blmtcsps/3/rxSt                            | atLink1A             | bi blmtcsps/3/rxs                             | Statlink1A               |         |

|-----------------------------------------------------|-----------------------------------------|-----------------------|------------------------------|--------|-----------------------------------------------|----------------------|-----------------------------------------------|--------------------------|---------|

| Module :                                            | bi_blmtcsps 💽 🔍 🧧                       | 2023-09-22 09:34:08   |                              |        | Di_Diritcsps/3/x50<br>2023-09-22 09:34:07.480 | dt:1030 ms           | Di_Dimtcsps/3/13 2023-09-22 09:34:34.064      |                          |         |

| Lun :<br>Block instance :                           | 3 💌<br>statusReg 🔽                      |                       | StatLink1A                   |        | 2023-09-22 09:34:07.480<br>rxStatLi           |                      | 2023-09-22 09:34:34.064                       |                          |         |

|                                                     |                                         | V                     | Filter :                     |        |                                               | ilter :              |                                               | Filter :                 |         |

|                                                     | Status_sfpPresent RO scalar 32          | ✓ ✓ sfpPresent        |                              |        | V 🛃 lpgbtTxCnt1Hz                             |                      | ✓ 🛃 asic4RegChanges                           | [0 0 0 0]                |         |

|                                                     | p1Status_sfpTemp RO scalar 32           | ✓ ✓ sfpLos            | 0                            |        | V Z lpgbtRxCnt1Hz                             | 39999999             | ✓ ✓ asic4Reg30                                | [ 842150450 37]          | 391479  |

|                                                     | 1Status_sfpTxBias RO scalar 32          | ✓ ✓ mgtTxCalBusy      | 0                            |        | V 🖉 lpgbtRxUplinkReady                        | 1                    | ✓ 🛃 asic4Reg30_asic0Reg                       | <b>j8b</b> [50 222 0 200 | 0 0 1 5 |

|                                                     | status_sfpTxPower RO scalar 32          | ✓ ✓ mgtRxCalBusy      |                              |        | V 🖉 lpgbtTxDownlinkRead                       | y 1                  | 🗸 🛃 asic0BitEarlyCnt                          | 15179509                 |         |

| sfp1S                                               | tatus_sfpRxPower RO scalar 32           | ✓ ✓ mgtTxReady        |                              |        | ✓ ✓ latchRxFec98b                             | [0 0 0 0]            | 🗸 🛃 asic0BitLateCnt                           | 15181555                 |         |

| si                                                  | fp1Status_sfpSctc RW scalar 32          | ✓ ✓ mgtRxReady        |                              |        | V 🗹 lpgbtFecCnt1Hz                            |                      | 🗸 🛃 asic0PhaseDly                             | 32768                    |         |

|                                                     | ssfpSctc_dataRdy RW scalar 32           | ✓ ✓ mgtTxAnaRst       |                              |        | V 🛃 lpgbticDataCorr                           |                      | 🗸 🛃 chan8RawCfc                               | [14 0 0 0 0 0            | 0 0]    |

| sfp1State<br>X maxValCh1Rs5@cfv-865-blmasic2.cem.ch | us_sfpSctc_sfpLos RW scalar 32          | ✓ ✓ mgtTxDigRst       |                              |        | ✓ 🛃 lpgbtEcDataCorr                           |                      | 🗸 🛃 chan8RawAdc                               | [316 395 574 12          | 2 60 1  |

|                                                     |                                         | ✓ ✓ mgtRxAnaRst       |                              |        | ✓ 🛃 lpgbtScaCmdCnt                            |                      | 🗸 🛃 chan8RawSlope                             | [11010001]               |         |

|                                                     | dt:836 ms 🚺 🖍 🚯                         | ✓ ✓ mgtRxDigRst       |                              |        | ✓ 🛃 asic4ElinkGood                            | [1 1 1 1]            | 🗸 🛃 chanRawCnt                                | 100000                   |         |

| Chart Table Label                                   |                                         | ✓ ✓ mgtRxLockData     |                              |        | ✓ 🜌 asic4FrameGood                            | [1 1 1 1]            |                                               |                          |         |

|                                                     |                                         | ✓ ✓ mgtGood           |                              |        | ✓ 🛃 asic4Decod8b10bErrC                       | nt [0000]            |                                               |                          |         |

|                                                     |                                         | ✓ ✓ mgtGoodFallCnt    | : 0                          |        | ✓ 🛃 asic4Sof1Hz                               | [100000 100000 10000 | Get Set                                       | Poll 📃 Cle               | ear )   |

| 29816 VUVV                                          | V Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y | ✓ ✓ IpgbtGood         | ✓ asic412CAddr [16 17 18 19] |        | bi_blmtcsps/3/statusReg                       |                      |                                               |                          |         |

|                                                     | ע אן איז עאן די                         | V Z lpgbtGoodFallCr   | nt 4                         |        | ✓ 🗹 asic4l2CAddrCnt                           | [0 0 0 0]            | 0 2023-09-22 09:38:51.457                     |                          |         |

| 29814                                               |                                         |                       |                              |        | v 🛃 asic4FrameId                              | [122 101 132 138]    | statu                                         |                          |         |

| 29813                                               | <u> </u>                                |                       | os/3/maxValReg               |        | ✓ 🛃 asic4SkipId                               | [0 0 0 0]            |                                               | Filter :                 |         |

|                                                     |                                         | 2023-09-22 09:38:51   | .761 dt:836 ms               |        | ✓ 🛃 asic4SkipIdCnt                            | [0 0 0 0]            | 🗸 🛃 boardTemp                                 | 524                      |         |

| X maxValCh1Rs6@cfv-865-blmasic2.cern.ch             | - 🗆 ×                                   |                       | Filter :                     |        | ✓ ∠ asic4FrameParByte                         | [99 12 171 55]       |                                               | 40                       |         |

| 0 2023-09-22 09:38:51.769                           | dt:836 ms 🛛 🔢 🎤 😗                       | www.waxValCh1Rs1      |                              |        | ✓ ✓ asic4ParErr                               | [0 0 0 0]            |                                               | 247                      |         |

| Chart Table Label                                   |                                         | w waxvalCh1Rs1        |                              | _      | ✓ ✓ asic4FrameParErrCnt<br>bi_blmtcsps/3/0    |                      |                                               | [543 605 614 561 6       |         |

| 119190                                              |                                         | v w maxvalCh1Rs2      |                              |        | 0 2023-09-22 09:38:22.844                     | dt:962 ms            |                                               | [20 4 11 5 10 12 1]      |         |

| 119180 -                                            |                                         | v w maxvalCh1Rs3      |                              | _      | ctriR                                         | eg                   |                                               | [563 609 625 566 6       |         |

|                                                     |                                         |                       |                              | ⊔      | V                                             | Filter :             | ✓ ✓ CfcDataValidCnt<br>✓ ✓ CfcDataValidCnt1Hz | [61377087 6137708        |         |

| N N N N N                                           | SMA ALAAM AAL                           | www.maxValCh1Rs5      |                              |        | 🗸 🛃 sysRst                                    | 0                    |                                               | [100000 100000 10        | 1 0000  |

| 119160 - V V                                        |                                         | www.maxValCh1Rs6      |                              |        | 🗸 🛃 clearStatus                               | 0                    |                                               |                          |         |

|                                                     |                                         | ✓ MaxValCh1Rs7 952955 |                              |        | ✓ 🛃 lpgbtForceI2cConfig 0                     |                      |                                               |                          |         |

| 0 20 40                                             | 60 80 100                               | Get Set               | Stop 📕 Cle                   | ar 000 | Get Set                                       | Poll Clear           | Get Set                                       | Stop Cle                 | ear )   |

|                                                     |                                         |                       |                              |        |                                               |                      |                                               |                          |         |

| g Console                                           |                                         |                       |                              |        |                                               |                      |                                               |                          |         |

EDGE GUI example

Overview of the BLMASIC chip architecture

Presented at the Topical Workshop on Electronics for Particle Physics, TWEPP23, Geremeas, Sardinia, Italy, 2–6 October 2023.