# Digital Verification for FPGA and ASIC Designers

**Delivering KnowHow**

# Digital Verification for FPGA and ASIC Designers

www.doulos.com

# Digital Verification for FPGA and ASIC Designers

Copyright © 2015-2023 by Doulos. All Rights Reserved

All intellectual property rights, including copyright, patents, design rights and know-how in or relating to the course or course materials provided or made available in connection with the course remain the sole property of Doulos Ltd or their respective owners and no copies may be made of course materials unless expressly agreed in writing by Doulos Ltd.

All trademarks acknowledged.

Doulos takes great care in developing and maintaining materials to ensure they are an effective and accurate medium for communicating design know-how. However, the information provided on a Doulos training course may be out of date or include omissions, inaccuracies or other errors. Except where expressly provided otherwise in agreement between you and Doulos, all information provided directly or indirectly through a Doulos training course is provided "as is" without warranty of any kind.

Doulos hereby disclaims all warranties with respect to this information, whether express or implied, including the implied warranties of merchantability, satisfactory quality and fitness for a particular purpose. In no event shall Doulos be liable for any direct, indirect, incidental special or consequential damages, or damages for loss of profits, revenue, data or use, incurred by you or any third party, whether in contract, tort or otherwise, arising for your access to, use of, or reliance upon information obtained from or through a Doulos training course. Doulos reserves the right to make changes, updates or corrections to the information contained in its training courses at any time without notice.

Doulos Limited Church Hatch, 22 Market Place, Ringwood, Hampshire, BH24 1AW, UK

Tel: +44 (0) 1425 471223

Email: info@doulos.com

www.doulos.com

Doulos 6203 San Ignacio Avenue, Suite 110, San Jose, CA 95119, USA

Tel: 1-888-GO DOULOS Email: info.usa@doulos.com

# Contents

| Contents                                    | 7    |

|---------------------------------------------|------|

| Current Verification Landscape              | 9    |

| Verification Approaches                     | 9    |

| Simulation and Testbenches                  | . 13 |

| Coverage                                    | . 20 |

| Formal Verification                         | . 23 |

| Class-Based SystemVerilog Verification      | . 26 |

| What is SystemVerilog?                      | . 26 |

| SystemVerilog Classes                       | . 31 |

| Virtual Interfaces                          | . 38 |

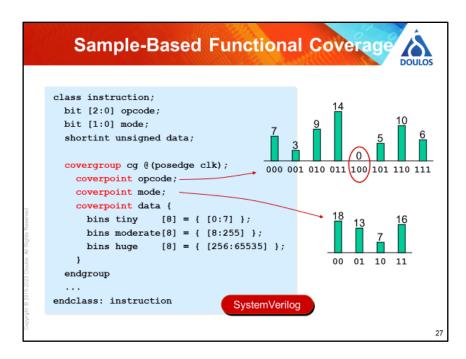

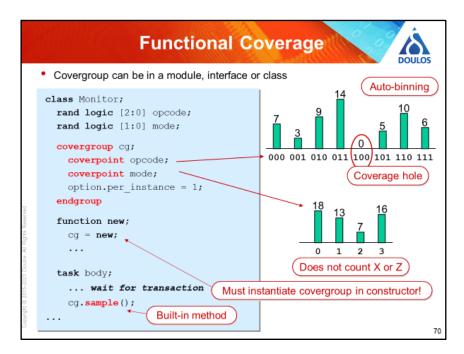

| Constraints and Functional Coverage         | . 41 |

| Universal Verification Methodology (UVM)    | . 44 |

| What is UVM?                                | . 44 |

| UVM Hello World                             | . 48 |

| DUT Interface                               | . 53 |

| Sequencer-Driver Communication              | . 57 |

| Formal Verification for Non-Specialists     | . 62 |

| Learning to use Formal                      | . 62 |

| Writing Properties                          | . 63 |

| Tackling State Space                        | . 67 |

| Under-constraining versus Over-constraining | .71  |

| Using Formal                                | . 76 |

| Conclusions and Recommendations             | . 77 |

Notes

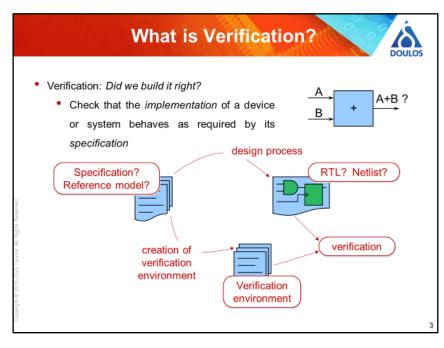

# **Current Verification Landscape**

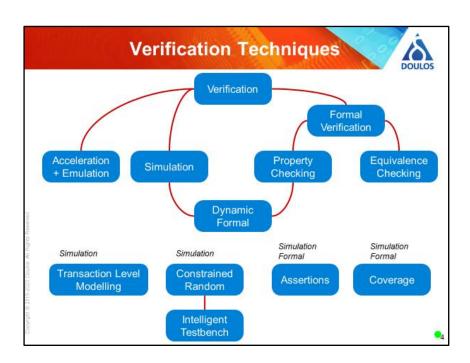

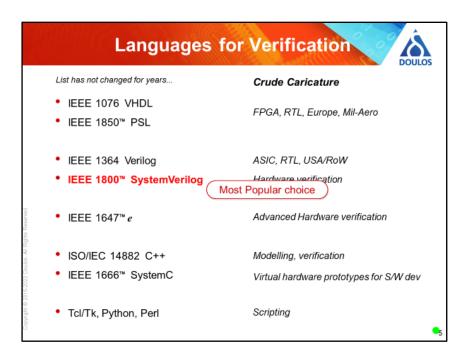

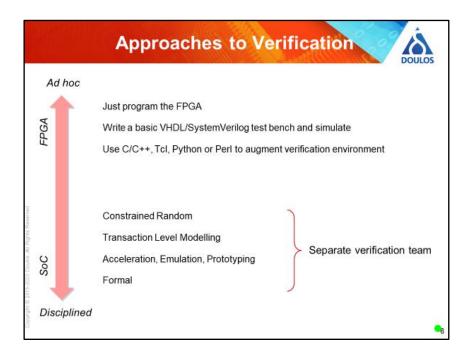

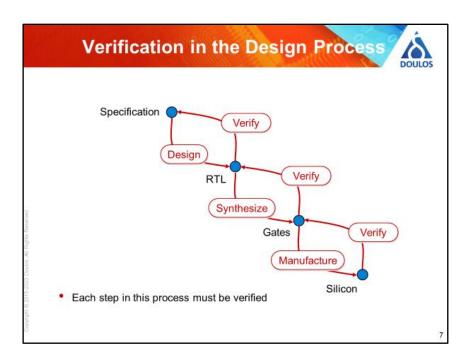

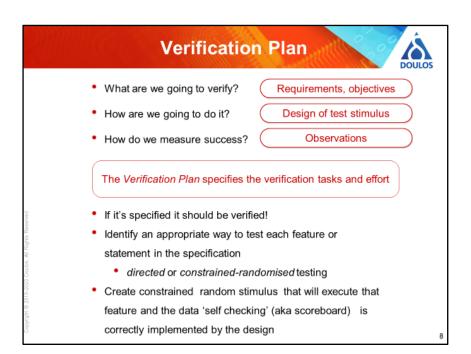

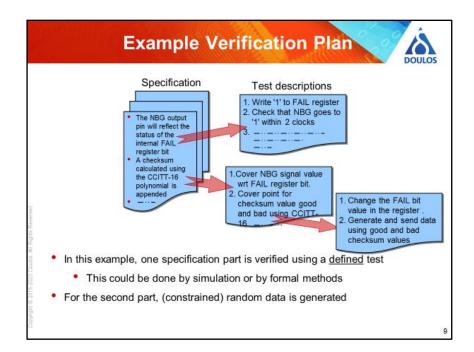

### Verification Approaches

| <ul> <li>Locating errors or potential error<br/>verification effort later</li> </ul>                   | rs in HDL code can save a lot of                                  |

|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| <ul> <li>Simulators and formal tools sho</li> </ul>                                                    | uld find errors eventually                                        |

| <ul> <li>A Linting Tool finds common er</li> </ul>                                                     | ors quickly and automatically                                     |

| • Example:                                                                                             |                                                                   |

| <pre>always @(Select)     if (Select)     Y= A;     else     Y=B; Warning: Incomplete event list</pre> | <ul> <li>Verilint</li> <li>HAL</li> <li>LEDA</li> <li></li> </ul> |

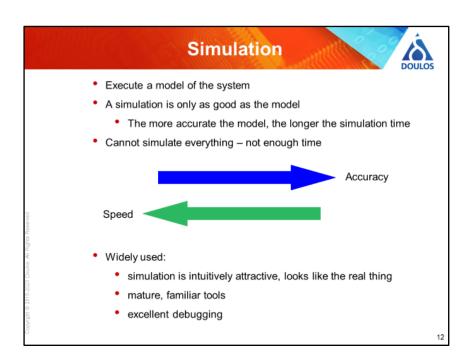

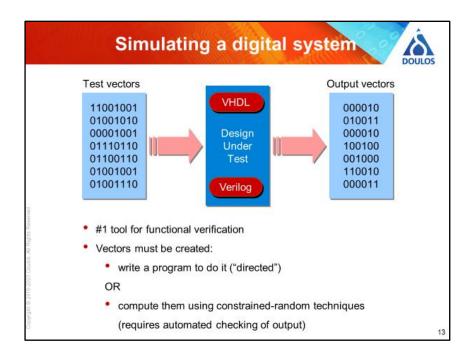

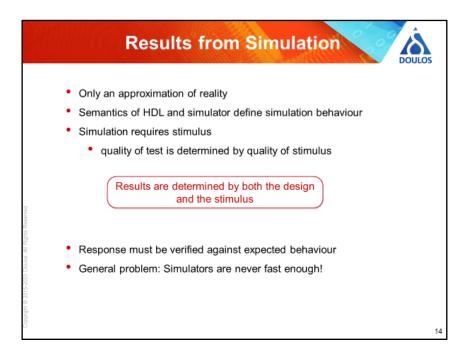

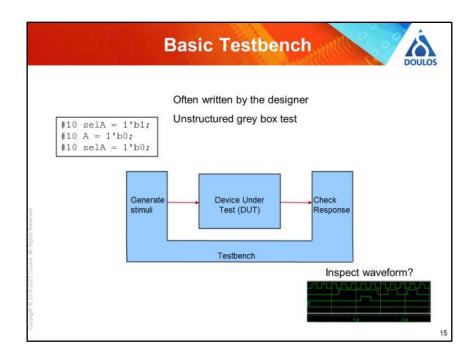

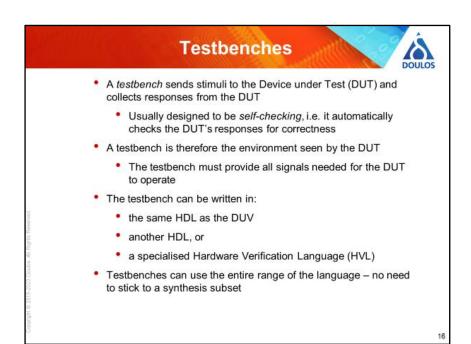

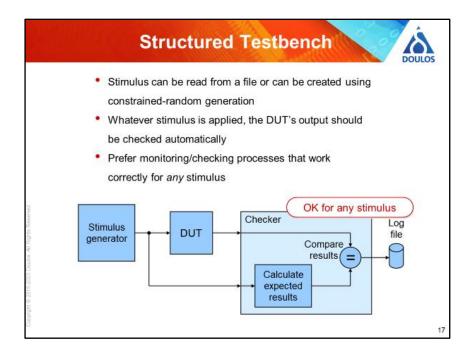

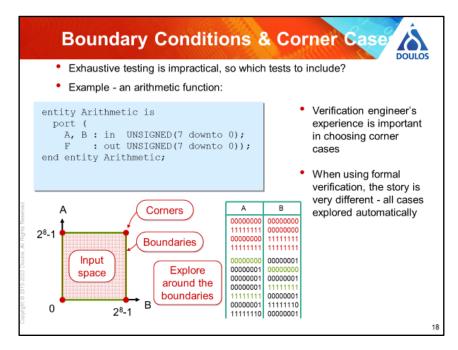

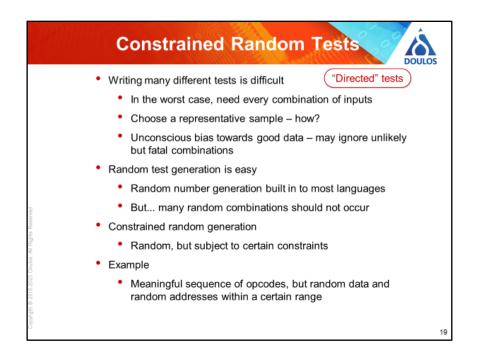

# Simulation and Testbenches

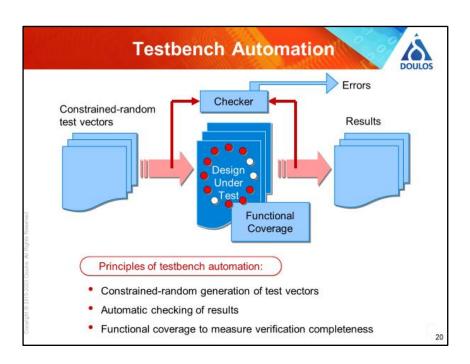

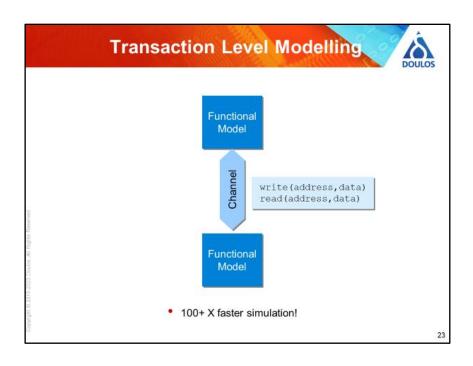

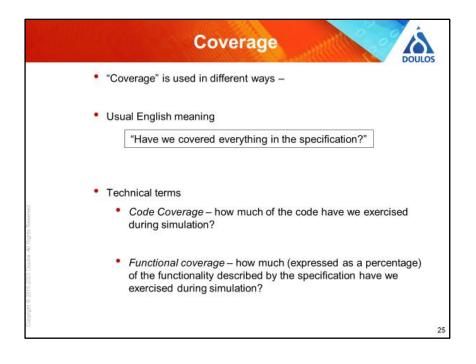

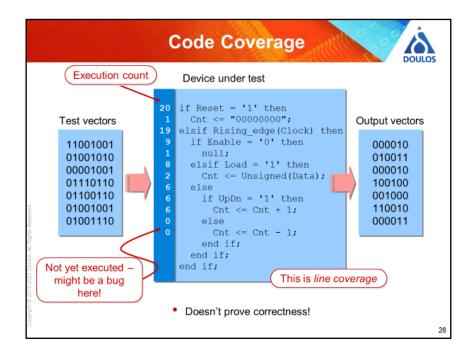

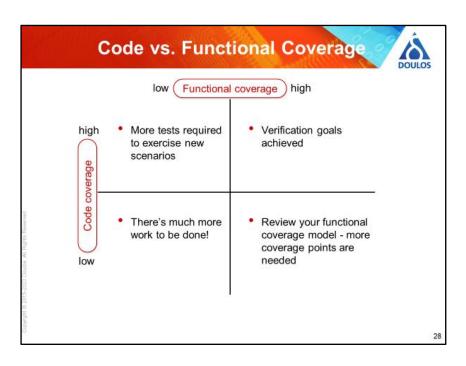

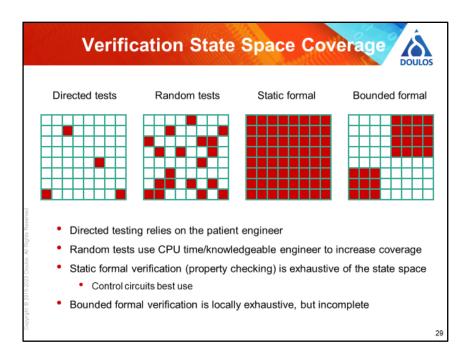

#### Coverage

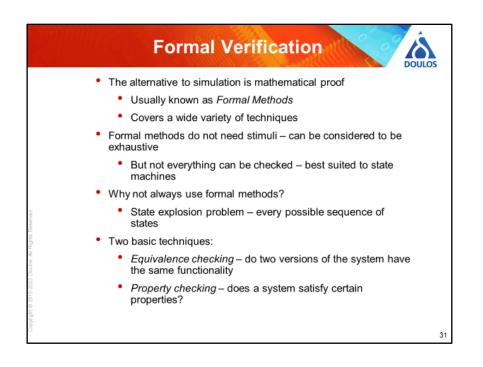

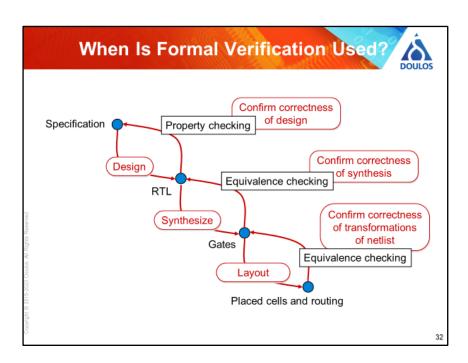

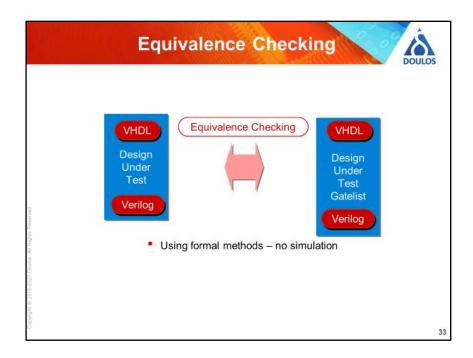

### Formal Verification

|                                            | Property Checkin                                                  | g            | DOULOS |

|--------------------------------------------|-------------------------------------------------------------------|--------------|--------|

|                                            |                                                                   | Properties   |        |

| VHDL<br>Design<br>Under<br>Test<br>Verilog |                                                                   | assert A > B |        |

|                                            | Using formal methods – no simu<br>Exhaustive state space coverage |              |        |

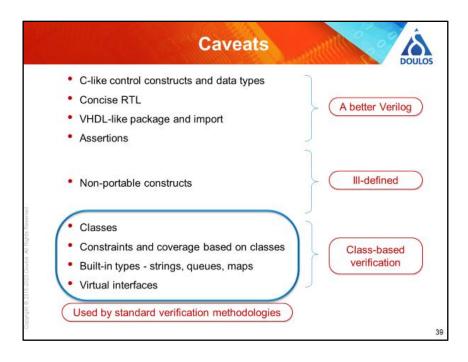

## **Class-Based SystemVerilog Verification**

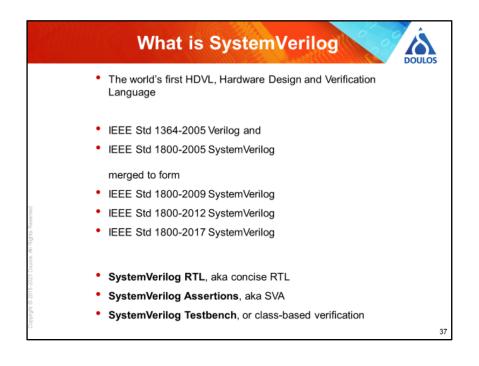

### What is SystemVerilog?

|                 | SystemVerilog Language Features                                                                                                                                                                                                            |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ATL BOOM BORNER | C-style data types & control - enum, struct, typedef, ++, break, return<br>Synthesis-friendly "concise" RTL notation<br>Packages<br>Interfaces                                                                                             |

| Assertions      | SystemVerilog Assertions                                                                                                                                                                                                                   |

| 1estenut        | Clocking blocks (synchronization between DUT and test bench)<br>Object-oriented programming - classes<br>Constrained random stimulus generation<br>Functional coverage<br>Dynamic processes, dynamic arrays, queues, mailboxes, semaphores |

|                 | Direct Programming Interface (DPI) - calling C from SystemVerilog<br>Extensions to VPI                                                                                                                                                     |

|            | 4-State a                                        | and 2-State                                   | Types                     |

|------------|--------------------------------------------------|-----------------------------------------------|---------------------------|

| 4-state ty | pes<br>Signed                                    | Unsigned                                      | Width                     |

|            | logic signed                                     | logic                                         | 1 bit                     |

|            | logic signed [n:m]                               | logic [n:m]                                   | N bits                    |

| 2-state ty | pes (variables only,                             | not wires)                                    |                           |

| 2-state ty | pes (variables only,<br><i>Signed</i>            | not wires)<br>Unsigned                        | Width                     |

| 2-state ty |                                                  | ,                                             | <i>Width</i><br>1 bit     |

| 2-state ty | Signed                                           | Unsigned                                      |                           |

| 2-state ty | Signed bit signed                                | Unsigned                                      | 1 bit                     |

| 2-state ty | Signed<br>bit signed<br>bit signed [n:m]         | Unsigned<br>bit<br>bit [n:m]                  | 1 bit<br>N bits           |

| -state ty  | Signed<br>bit signed<br>bit signed [n:m]<br>byte | Unsigned<br>bit<br>bit [n:m]<br>byte unsigned | 1 bit<br>N bits<br>8 bits |

| Interfaces                                                                                                                                                | Â         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| <ul> <li>Simple interface = bundle of w</li> </ul>                                                                                                        | ires/vars |

| <pre>interface APB;<br/>logic PCLK, PSEL, PENABLE, PWRIT<br/>logic [15:0] PADDR;<br/>logic [31:0] PWDATA;<br/>logic [31:0] PRDATA;<br/>endinterface</pre> | E;        |

| <pre>module Master (APB iport,);</pre>                                                                                                                    |           |

| Immediate and Concurrent Assertion                                                                                                   | ULOS           |

|--------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Procedural assertion – sampled procedurally                                                                                          |                |

| always assert ( EXPRESSION );                                                                                                        |                |

| Ordinary SystemVerilog expression                                                                                                    |                |

| <b>Concurrent assertion - condition is usually sampled on clock edge</b><br><b>assert property (</b> @(posedge Clock) CONDITION );   |                |

| SystemVerilog property                                                                                                               | $\overline{)}$ |

|                                                                                                                                      |                |

| Condition is only tested when pre-condition has been matched                                                                         |                |

| Condition is only tested when pre-condition has been matched<br>assert property (<br>@ (posedge Clock) PRECONDITION  -> CONDITION ); |                |

| Concurrent Assertions                           | Â     |

|-------------------------------------------------|-------|

| Check or prove the property                     | DOULO |

| label: assert property (PROPERTY) ACTION_BLOCK; |       |

| Collect functional coverage information         |       |

| label: cover property (PROPERTY) STATEMENT;     |       |

| Make the property an assumption for formal      |       |

| <pre>label: assume property (PROPERTY);</pre>   |       |

|                                                 |       |

|                        | ices describe temporal behaviour                                      |

|------------------------|-----------------------------------------------------------------------|

| Temporal means the     | sequence spans more than one clock cycle                              |

| Concurrent assertion   | ) ( Sequences )                                                       |

| @ (posedge Clock<br>); |                                                                       |

|                        | Property                                                              |

|                        | hrough matching a sequence<br>erty's obligation to hold for PROPERTY) |

|                        |                                                                       |

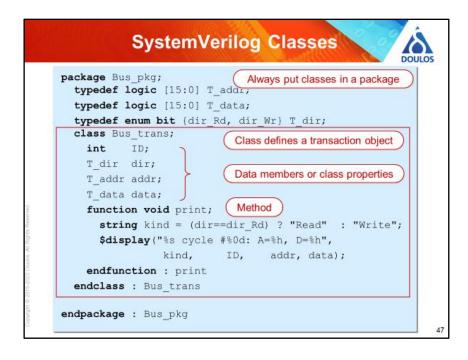

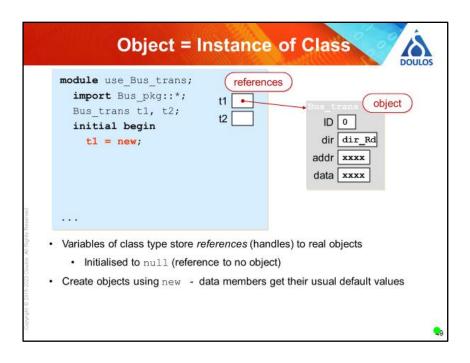

## SystemVerilog Classes

| <b>im</b><br>Bu | le use_Bus_<br>port Bus_pk<br>s_trans t1,<br>itial begin | t2;          | t1           | nces                                     |             |  |

|-----------------|----------------------------------------------------------|--------------|--------------|------------------------------------------|-------------|--|

|                 | T                                                        |              |              |                                          |             |  |

|                 |                                                          |              |              |                                          |             |  |

|                 |                                                          |              |              |                                          |             |  |

|                 | oles of class ty                                         | 8            |              | an a | eal objects |  |

| • 1             | nitialised to nu                                         | ill (referer | nce to no ob | ject)                                    |             |  |

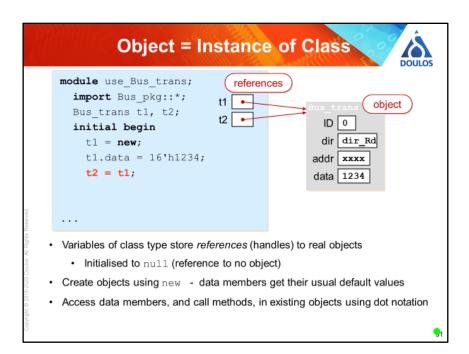

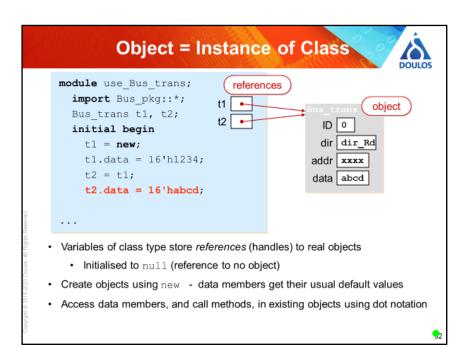

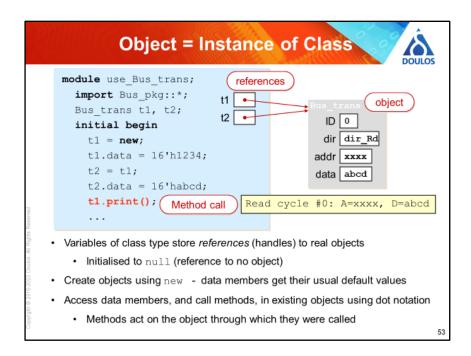

| Object = Instance                                                                                                                                                                                                               | of Class                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| <pre>module use_Bus_trans; import Bus_pkg::*; Bus_trans t1, t2; initial begin t1 = new; t1.data = 16'h1234;</pre>                                                                                                               | Bus_trans object<br>ID 0<br>dir dir_Rd<br>addr xxxx<br>data 1234 |

| <ul> <li>Variables of class type store <i>references</i> (har</li> <li>Initialised to null (reference to no obje</li> <li>Create objects using new - data members</li> <li>Access data members, and call methods, in</li> </ul> | ect)<br>get their usual default values                           |

-

|                                                                               | D                                   |

|-------------------------------------------------------------------------------|-------------------------------------|

| module use_Bus_trans                                                          |                                     |

| <pre>import Bus_pkg::*; Bus trans t3 = new</pre>                              | C.                                  |

|                                                                               |                                     |

| class Bus_trans;<br>                                                          |                                     |

| <br>function new;                                                             | Explicit constructor new. No return |

| function new;<br>addr = 0;                                                    | Explicit constructor new. No return |

| <br>function new;                                                             |                                     |

| <pre>function new;<br/>addr = 0;<br/>dir = dir_Wr;</pre>                      |                                     |

| <pre>function new;<br/>addr = 0;<br/>dir = dir_Wr;<br/>\$write("Created</pre> | new ");                             |

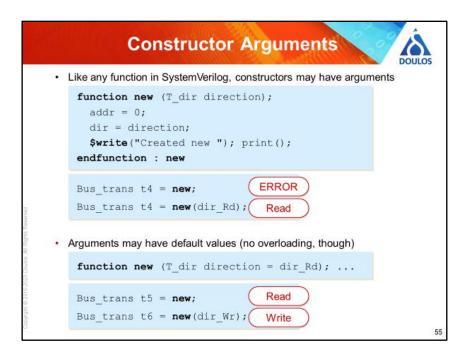

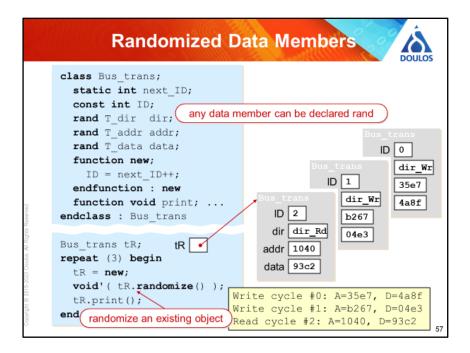

| Randomized Data Members                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>class Bus_trans;<br/>static int next_ID;<br/>const int ID;<br/>any data member can be declared rand</pre>                                                               |

| rand T_addr addr;<br>rand T_addr addr;<br>rand T_data data;<br>function new;                                                                                                 |

| ID = next_ID++;       unique serial number       Bus_trans       dir_Wr         endfunction : new       ID 1       35e7         function void print;       dir_Wr       4a8f |

| endclass : Bus_trans addr b267<br>Bus_trans tR; tR •<br>data 04e3                                                                                                            |

| <pre>repeat (3) begin tR = new; void'(tR.randomize()); tR.print(); </pre> Write cycle #0: A=35e7, D=4a8f                                                                     |

| end randomize an existing object                                                                                                                                             |

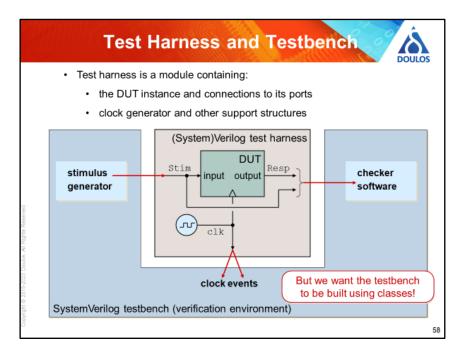

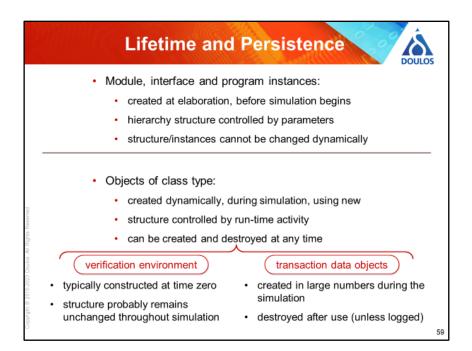

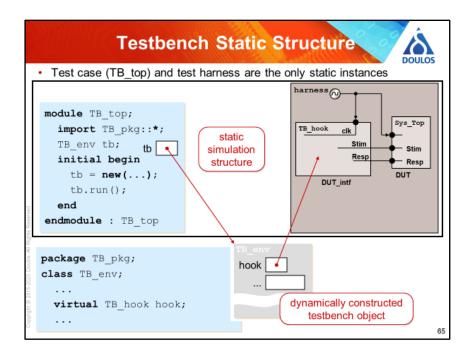

| Creating the Te                                                                                                                                                                                            | estbench                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>module TB_top;<br/>import TB_pkg::*;<br/>TB_env tb; tb<br/>initial begin<br/>tb = new;<br/>tb.run();<br/>end<br/>endmodule : TB_top<br/>class TB_env;<br/><br/>task drive_Stim(input bit data);</pre> | <pre>module harness;<br/>logic Stim, Resp;<br/>bit clk;<br/>Sys_Top DUT (.*);<br/><br/>endmodule<br/>Test harness modul<br/>Stim input output<br/>Resp<br/>clk</pre> |

| <pre>@ (posedge harness.clk)     harness.Stim &lt;= data; endtask</pre>                                                                                                                                    | Our entire testbench class is hard-coded for the name of the test harness!                                                                                           |

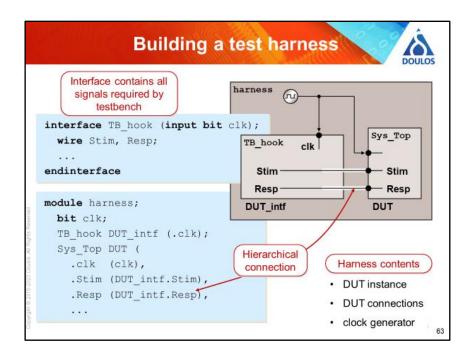

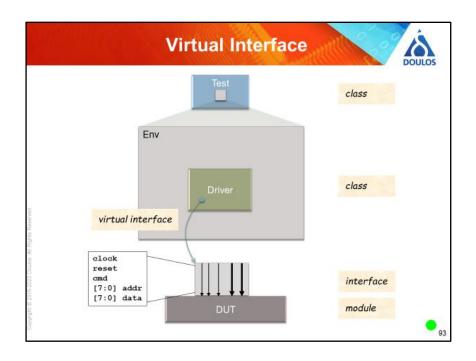

## Virtual Interfaces

| Virtual Interf                                                                                                                                                                                                                           | ace                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| <pre>class TB_env;<br/>virtual TB_hook hook;<br/>function new(virtual TB_hook h);<br/>hook = h;<br/><br/>endfunction : new<br/>task drive_Stim(input bit data);<br/>@(posedge hook.clk)<br/>hook.Stim &lt;= data;<br/>endtask<br/></pre> | <ul> <li>How does it link</li> </ul> |

| Copyri                                                                                                                                                                                                                                   | 6                                    |

| Connecting the virtual interface                                                                                                       | DOULOS |

|----------------------------------------------------------------------------------------------------------------------------------------|--------|

| <pre>class TB_env;<br/>virtual TB_hook V;<br/>function new (virtual TB_hook V,);<br/>this.V = V;<br/>constructor<br/>endfunction</pre> |        |

| <pre>module TB_top; TB_env tb; initial begin tb = new(harness.DUT_intf,);</pre>                                                        |        |

| <pre>bit clk;<br/>TB_hook DUT_intf (.clk);<br/>Sys_Top DUT (<br/></pre>                                                                | 64     |

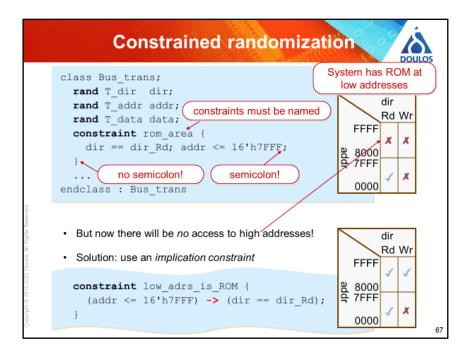

#### **Constraints and Functional Coverage**

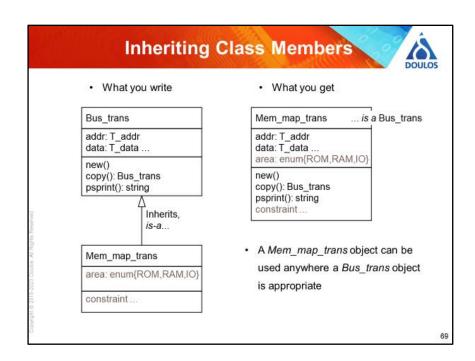

| <pre>class Bus_trans;<br/>rand T_dir dir;<br/>rand T_addr addr;<br/>rand T_data data;<br/>constraint low_adrs_is_ROM {<br/>(addr &lt;= 16'h7FFF) -&gt; (dir == dir_Rd);<br/>}<br/>Don't modify the original class definition<br/>lnstead, extend it:<br/>Class Mem_map_trans extends Bus_trans;<br/>constraint low_adrs_is_ROM {<br/>(addr &lt;= 16'h7FFF) -&gt; (dir == dir_Rd);<br/>}<br/>}<br/></pre> | Creating an I                        | Extended Class    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------|

| <pre>constraint low_adrs_is_ROM {    (addr &lt;= 16'h7FFF) -&gt; (dir == dir_Rd); }  Don't modify the original class definition Instead, extend it:    Everything in the base class, plus class Mem_map_trans extends Bus_trans;    constraint low_adrs_is_ROM {</pre>                                                                                                                                   | rand T_dir dir;<br>rand T_addr addr; | Better not to mix |

| <ul> <li>Instead, extend it: Everything in the base class, plus</li> <li>class Mem_map_trans extends Bus_trans;<br/>constraint low_adrs_is_ROM {</li> </ul>                                                                                                                                                                                                                                              |                                      | ROM {             |

| constraint low_adrs_is_ROM {                                                                                                                                                                                                                                                                                                                                                                             | , ,                                  |                   |

|                                                                                                                                                                                                                                                                                                                                                                                                          | constraint low_adrs_is_F             | ROM {             |

| EDA playground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | @Run @Copy                                                                     | KnowHOw<br>Weblinars Dealing with Complexity<br>FREE L hour weblinar - Ju                                           | ne 23,2023           | STER 🖉 🕑 🕈 Playgrounds Log I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Starget year by the<br>Apoluto's<br>Langunges &<br>Langunges &<br>L                                                                                                                                                                                                                                                                                                                                                                                                                                 | <pre>Numeric TL_App. * Numer * * ''''''''''''''''''''''''''''''''''</pre>      | Practice - Share - Learn<br>Simulate your code in a web<br>browser                                                  | Briveriga Testhernin | Internet in state in the second state in the second state in the second state is the s |

| Rus Time: Time<br>Coore ready Table<br>Other Readward and Except<br>Open EXPlane after an<br>Ownersaal files after ann<br>Ownersaal files after a | Log     SystemWorking interface to     Connecting a SystemWorking interface to | 2002 over and 2 likes<br>a class-based welfcation eministration using a visual interface<br>https://www.edaplaygrou | nd.com/              | $\supset$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

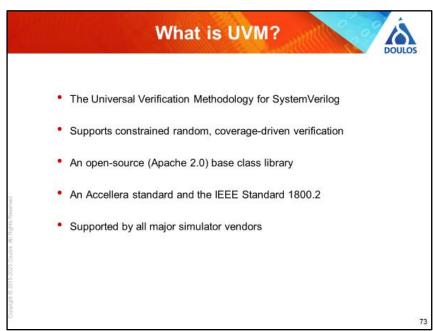

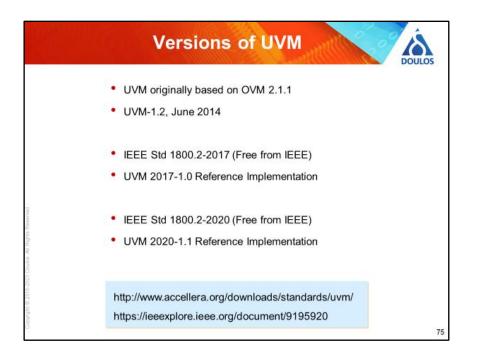

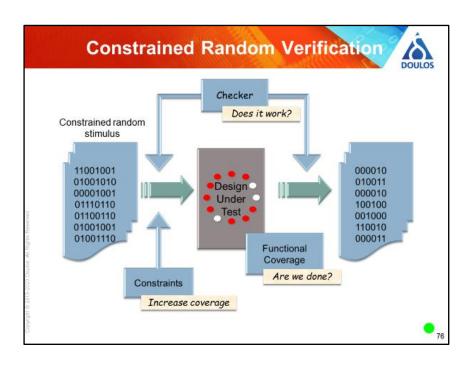

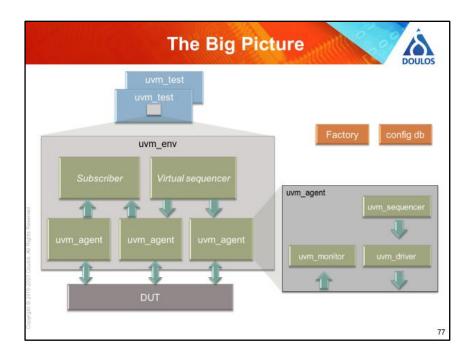

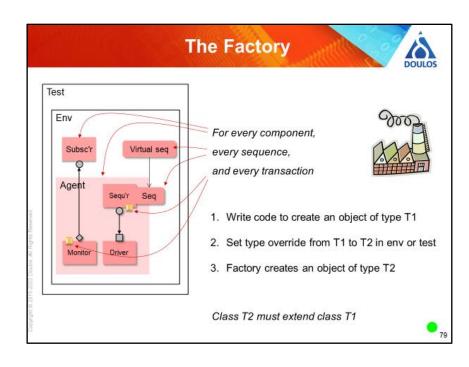

# **Universal Verification Methodology (UVM)**

### What is UVM?

| build<br>connect<br>end_of_elaboration<br>start_of_simulation<br>run<br>run<br>check<br>report<br>final | pre_reset<br>reset<br>post_reset<br>pre_configure<br>configure<br>post_configure<br>pre_main<br>main<br>post_main<br>pre_shutdown<br>shutdown<br>post_shutdown<br>post_shutdown | Env<br>Subsc'r<br>Agent<br>Monitor | Virtual seq<br>Sequ'r Seq<br>Driver |

|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------------------------|

|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------------------------|

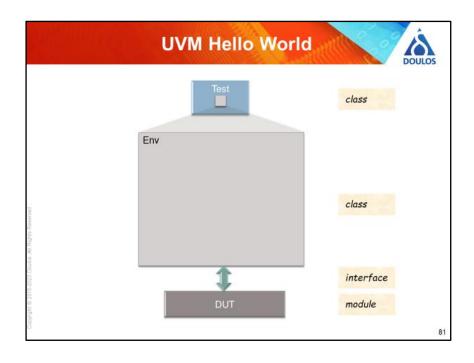

### **UVM Hello World**

| interface dut_if;                                | module top;                                               |

|--------------------------------------------------|-----------------------------------------------------------|

| endinterface                                     |                                                           |

| <pre>module dut(dut_if dif);<br/>endmodule</pre> | <pre>dut_if dut_if1 (); dut dut1 ( .dif(dut_if1) );</pre> |

|                                                  | endmodule                                                 |

| class my_e | nv extends uvm_env;                                                      |

|------------|--------------------------------------------------------------------------|

| `uvm_com   | <pre>ponent_utils(my_env)</pre>                                          |

|            | <pre>new(string name, uvm_component parent) new(name, parent); ion</pre> |

| endclass   |                                                                          |

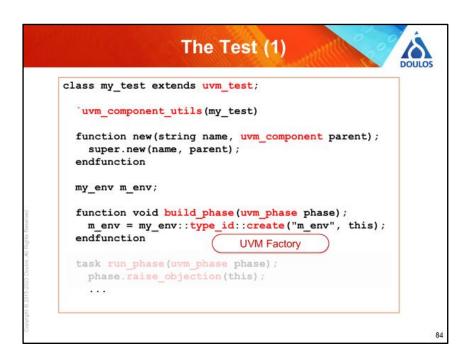

| <pre>m_env = my endfunction</pre> | y_env::type_id::cre            | <pre>ate("m_env", this);</pre> |

|-----------------------------------|--------------------------------|--------------------------------|

| task run ph                       | ase (uvm phase phase           | );                             |

| phase.rai                         | <pre>se_objection(this);</pre> | UVM Objection                  |

| #10;                              |                                |                                |

| `uvm_info                         | ("my_test", "Hello )           | World", UVM_MEDIUM)            |

| phase.dro                         | <pre>objection(this);</pre>    |                                |

| endtask                           | and the second second          |                                |

| dclass                            |                                |                                |

| `include "uvm_macros.svh"                                                 |  |

|---------------------------------------------------------------------------|--|

| <pre>package my_pkg;</pre>                                                |  |

| <pre>import uvm_pkg::*;</pre>                                             |  |

| <pre>class my_env extends uvm_env;<br/>`uvm_component_utils(my_env)</pre> |  |

| endclass                                                                  |  |

| class my_test extends uvm_test;                                           |  |

| <pre>`uvm_component_utils(my_test)</pre>                                  |  |

| endclass                                                                  |  |

| endpackage                                                                |  |

| interface dut_if;                  | module top;                            |

|------------------------------------|----------------------------------------|

| endinterface                       | <pre>import uvm pkg::*;</pre>          |

| endincerrace                       | <pre>import my_pkg::*;</pre>           |

|                                    |                                        |

|                                    | <pre>dut_if dut_if1 ();</pre>          |

| <pre>module dut(dut_if dif);</pre> |                                        |

|                                    | <pre>dut dut1 ( .dif(dut_if1) );</pre> |

| endmodule                          | initial                                |

|                                    | begin                                  |

|                                    | <pre>run test("my test");</pre>        |

|                                    | end                                    |

|                                    |                                        |

|                                    | endmodule                              |

| Hello Wo                                                                                                                           | rld Source Code                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>interface dut_if;<br/>endinterface<br/>module dut(dut_if dif);</pre>                                                          | <pre>package my_pkg;<br/>import uvm_pkg::*;<br/>class my_env extends uvm_env;<br/>'uvm_component_utils(my_env)<br/>function new(string name, uvm_component parent);<br/>super.new(name, parent);<br/>endfunction</pre>                                                                                          |

| <pre>endmodule module top; import uvm_pkg::*; import my_pkg::*;</pre>                                                              | <pre>endclass class my_test extends uvm_test; 'uvm_component_utils(my_test) my_env m_env; function new(string name, uvm_component parent); super.new(name, parent); endfunction</pre>                                                                                                                           |

| <pre>dut_if dut_if1 ();<br/>dut dut1 ( .dif(dut_if1) );<br/>initial<br/>begin<br/>run_test("my_test");<br/>end<br/>endmodule</pre> | <pre>function void build_phase(uvm_phase phase);<br/>m_env = my_env::type_id::oreate("m_env", this);<br/>endfunction<br/>task rum_phase(uvm_phase phase);<br/>phase.raise_objection(this);<br/>#10;<br/>'uvm_info("", "Hello World", UVM_MEDIUM)<br/>phase.drop_objection(this);<br/>endtask<br/>endolass</pre> |

| endmodule                                                                                                                          | endpackage: my_pkg                                                                                                                                                                                                                                                                                              |

| UVM Si                                                                                                                                                                                                                     | mulation Output                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| CDNS-UVM-1.2 (20.09-5003)<br>(C) 2007-2014 Mentor Graphics Corporat<br>(C) 2007-2014 Cadence Design Systems,<br>(C) 2006-2014 Synopsys, Inc.<br>(C) 2011-2013 Cypress Semiconductor Co<br>(C) 2013-2014 NVIDIA Corporation | Inc.                                                                                                                                        |

| <pre>@ 10: reporter [TEST_DONE] 'run' phase<br/>UVM_INFO /xcelium20.09/tools//methodol</pre>                                                                                                                               | <pre>st_top [] Hello World<br/>logy/UVM/CDNS-1.2/sv/src/base/uvm_objection.svh(1271)<br/>s is ready to proceed to the 'extract' phase</pre> |

| ** Report counts by severity<br>UVM_INFO: 4<br>UVM_WARNING: 0<br>UVM_ERROR: 0                                                                                                                                              | https://www.edaplayground.com/x/GjxC                                                                                                        |

| UVM_FATAL: 0<br>** Report counts by id<br>[] 1<br>[[RNTST] 1<br>[TEST_DONE] 1<br>[UVM/RELNOTES] 1                                                                                                                          |                                                                                                                                             |

| Simulation complete via \$finish(1) at                                                                                                                                                                                     | time 10 NS + 58 **********************************                                                                                          |

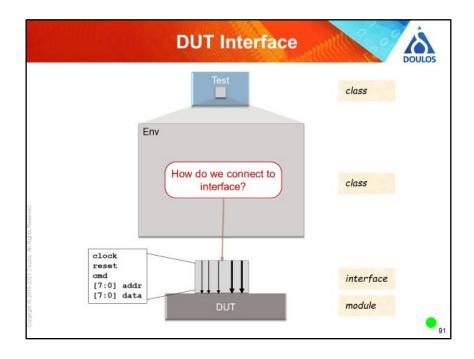

## **DUT Interface**

| Interfac                                                  | e and DUT                                                                                  |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------|

| <pre>interface dut_if;<br/>logic clock, reset;</pre>      | <pre>module top;<br/>import uvm_pkg::*;<br/>import my_pkg::*;</pre>                        |

| logic cmd;<br>logic [7:0] addr;<br>logic [7:0] data;      | <pre>dut_if dut_if1 (); dut dut1 ( .dif(dut_if1) );</pre>                                  |

| endinterface                                              | <pre>initial begin run test("my test");</pre>                                              |

| <pre>module dut(dut_if dif);<br/>import uvm_pkg::*;</pre> | end<br>endmodule                                                                           |

| _ dif.c                                                   | T received cmd=%b, addr=%d, data=%d"<br>md, dif.addr, dif.data), <mark>UVM_MEDIUM</mark> ) |

| end<br>endmodule                                          | nplementation                                                                              |

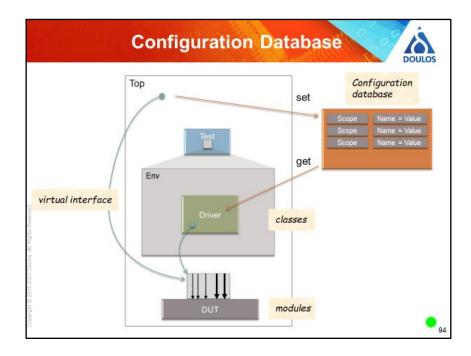

|                               |                        | fig Set                    | 1994   |                | DOULO                        |

|-------------------------------|------------------------|----------------------------|--------|----------------|------------------------------|

|                               |                        |                            |        |                | figuration<br>base           |

| module top;                   |                        |                            |        |                | (income in the second        |

| <pre>import uvm_pkg::*;</pre> |                        |                            |        | Scope          | Name = Value                 |

| <pre>import my_pkg::*;</pre>  |                        |                            | -      | Scope<br>Scope | Name = Value<br>Name = Value |

| <pre>dut_if dut_if1 ();</pre> |                        |                            |        | Scope          | Name - Value                 |

| dut dutl ( .dif (             | <pre>dut_if1) );</pre> |                            |        |                |                              |

| ••••                          | Туре                   | Caller                     | Path   | Name           | Value                        |

| initial                       |                        | 1                          | 1      | 1              | 1                            |

| begin                         | 4                      | *                          | 4      | *              | *                            |

| <pre>uvm_config_db #(v</pre>  |                        | ):: <mark>set</mark> (null | , "*", | "dut_if        | ", dut_if1)                  |

| <pre>run_test("my_test</pre>  | :");                   |                            |        |                |                              |

| end                           |                        |                            |        |                |                              |

| endmodule: top                |                        |                            |        |                |                              |

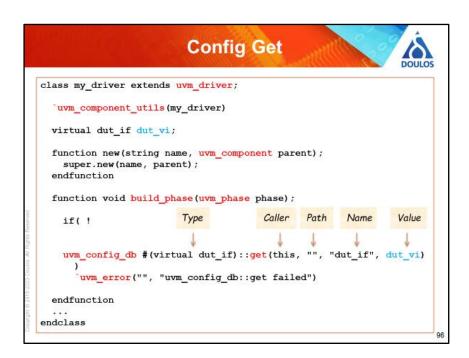

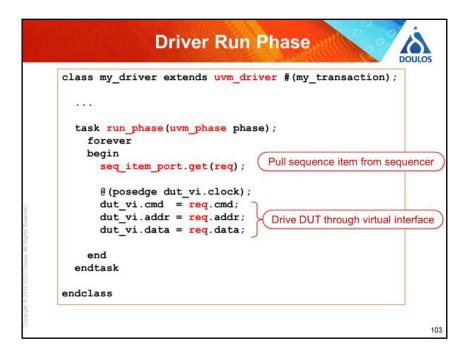

| Pin Wiggling                                                                                                                                                            | DOULO |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| <pre>class my_driver extends uvm_driv<br/>`uvm_component_utils(my_driver<br/>virtual dut_if dut_vi;<br/><br/>task run_phase(uvm_phase phase<br/>forever<br/>begin</pre> | r)    |

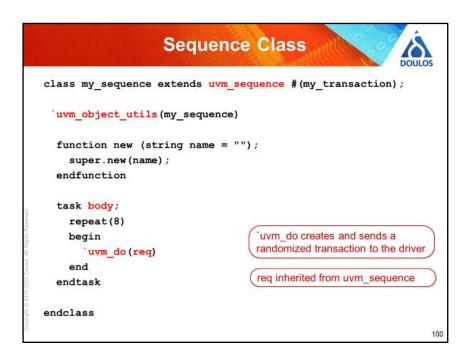

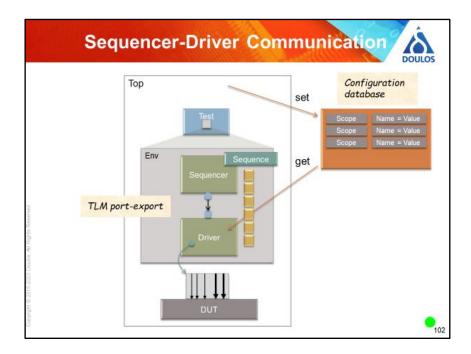

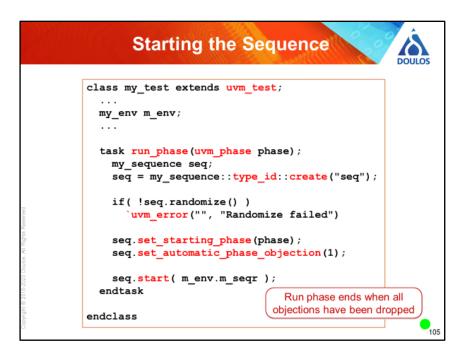

#### Sequencer-Driver Communication

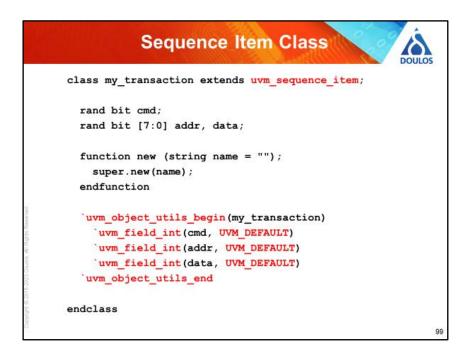

| Sequence versus Sequencer                                                                                           | ULOS |

|---------------------------------------------------------------------------------------------------------------------|------|

| <pre>class my_sequence extends uvm_sequence #(my_transaction)  endclass</pre>                                       | ;    |

| <pre>typedef uvm_sequencer #(my_transaction) my_sequencer;</pre>                                                    |      |

| A sequence runs on a sequencer                                                                                      |      |

| uvm_sequence extends uvm_sequence_item extends uvm_object<br>uvm sequencer extends uvm component extends uvm object |      |

Workbook

Sequencer-Driver Connection  $\mathbf{i}$ class my\_env extends uvm\_env; `uvm\_component\_utils(my\_env) my\_sequencer m\_seqr; my\_driver m\_driv; function new(string name, uvm\_component parent); super.new(name, parent); endfunction function void build\_phase(uvm\_phase phase);

m\_seqr = my\_sequencer::type\_id::create("m\_seqr", this);

m\_driv = my\_driver ::type\_id::create("m\_driv", this); endfunction function void connect\_phase(uvm\_phase phase);

m\_driv.seq\_item\_port.connect( m\_seqr.seq\_item\_export ); endfunction endclass 104

Digital Verification for FPGA and ASIC Designers Workbook 1.0

|                                      | Next Steps                                                        |

|--------------------------------------|-------------------------------------------------------------------|

|                                      | Test<br>Test                                                      |

|                                      | Env                                                               |

| 115-2023 Daules Jei Frigris Reserved | Checking<br>and<br>Coverage Agent Sequence Sequence Driver Driver |

| Copyright 00                         |                                                                   |

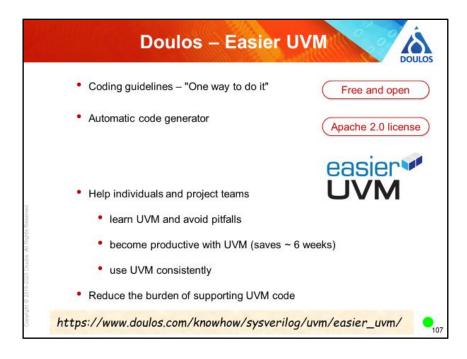

## **Formal Verification for Non-Specialists**

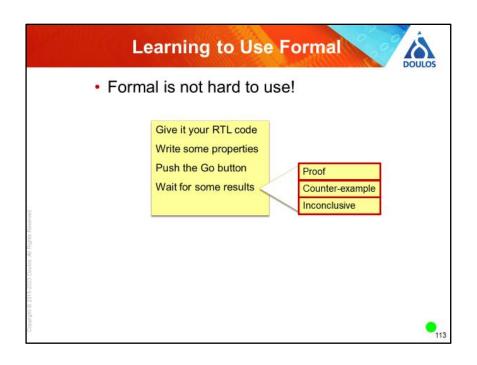

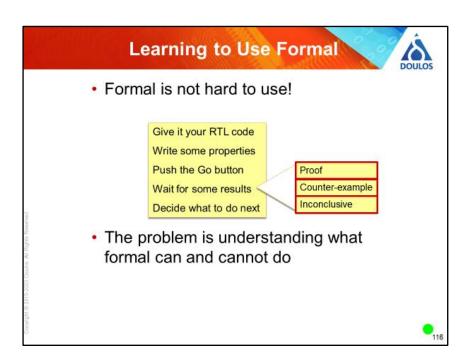

#### Learning to use Formal

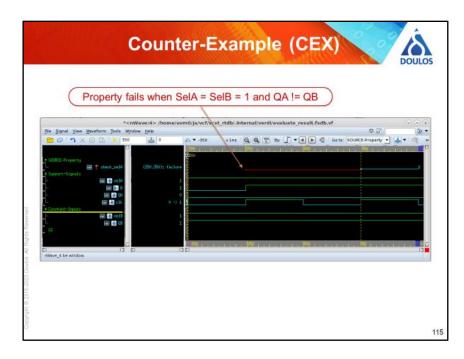

## Writing Properties

|                            |                                        | RTL         |            |            |

|----------------------------|----------------------------------------|-------------|------------|------------|

| module selAB<br>input logi | 22 A A A A A A A A A A A A A A A A A A |             |            |            |

|                            | .c QA, selA, QB,                       | selB.       |            |            |

| output logi                |                                        | ,           |            |            |

|                            |                                        |             |            |            |

| always @(po                | sedge clk)                             |             |            |            |

| begin                      | -                                      |             |            |            |

|                            | Q <= QA;                               |             |            |            |

| end (selb)                 | Q <= QB;                               |             |            |            |

| end                        |                                        |             |            | Properties |

| check selA:                | assert propert                         | у (         |            |            |

| -                          | @(posedge cl                           | k) selA  => | Q == \$pas | st(QA) );  |

| check_selB:                | assert propert                         |             |            |            |

|                            | @(posedge cl                           | k) selB  => | Q == \$pas | st(QB));   |

|                            |                                        |             |            |            |

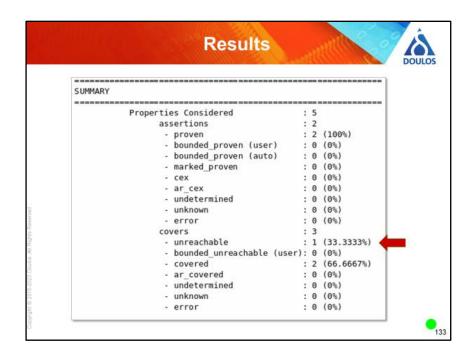

| SUMMARY |                                                                      |   |        |         |

|---------|----------------------------------------------------------------------|---|--------|---------|

|         | Properties Considered :                                              | 4 |        |         |

|         | assertions                                                           | 2 |        |         |

|         | - proven                                                             | 1 | (50%)  |         |

|         | <ul> <li>bounded_proven (user) :</li> </ul>                          | θ | (0%)   |         |

|         | <ul> <li>bounded proven (auto)</li> </ul>                            | θ | (0%)   |         |

|         |                                                                      |   | (0%)   |         |

|         |                                                                      |   | (50%)  |         |

|         | - ar_cex :                                                           |   | (0%)   |         |

|         | - undetermined :                                                     |   | (0%)   |         |

|         | - unknown :                                                          |   | (0%)   |         |

|         | - error :                                                            |   | (0%)   |         |

|         | covers :<br>- unreachable :                                          | 2 | (0%)   |         |

|         | <ul> <li>unreachable</li> <li>bounded unreachable (user):</li> </ul> |   |        |         |

|         |                                                                      |   | (100%) | <b></b> |

|         |                                                                      |   | (0%)   |         |

|         |                                                                      |   | (0%)   |         |

|         |                                                                      |   | (0%)   |         |

|         |                                                                      |   | (0%)   |         |

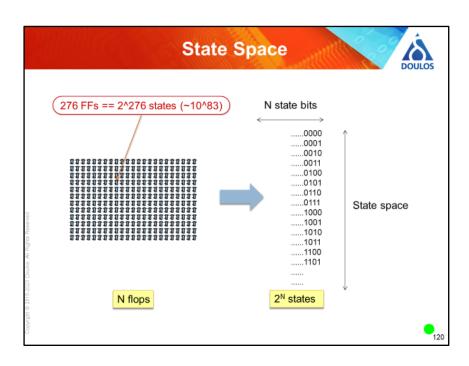

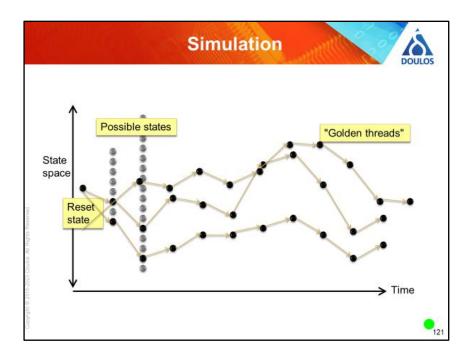

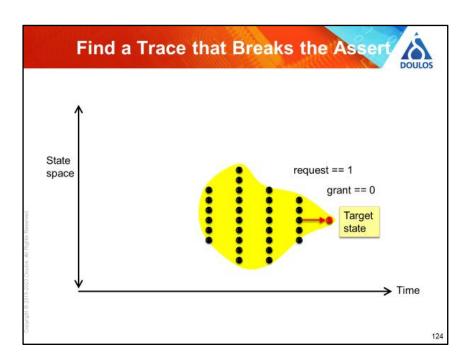

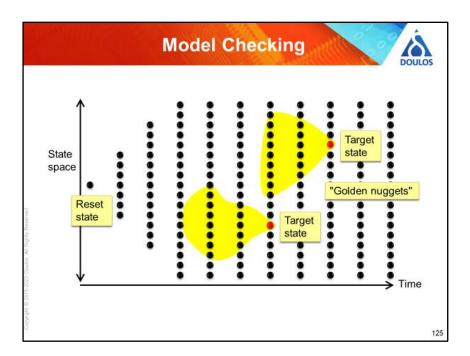

### Tackling State Space

| ,              | <b>•</b> | • | • | • | • | • | • | •       | • | •       | •         |

|----------------|----------|---|---|---|---|---|---|---------|---|---------|-----------|

|                |          | i | i | i | i |   |   | e repre |   | ed symb | olically, |

| State<br>space | :        | i | i | i | i | : | : | :       | : | :       | :         |

|                | :        | : | : | : | : | : | : | :       | : |         | :         |

|                |          |   | i | i | i |   | i | i       |   | Target  |           |

|                |          | i | i | i | i | i | i | i       |   | state   |           |

|                | :        | : | : | : | : | : | : | :       | : | :       | :         |

| ,              | .:       | : | : | : | : | : | : | :       | : | :       | → Time    |

|                        | Target State                                                          |

|------------------------|-----------------------------------------------------------------------|

|                        | <pre>assert property ( @(posedge clk) request  =&gt; grant );</pre>   |

|                        | request • grant                                                       |

| nds Rosserved          | Try to find a sequence of states that would make the assertion "fire" |

| 5-2020 Daulos: All Ruj | request == 1 • grant == 0                                             |

| Copyright 0, 201       | 9123                                                                  |

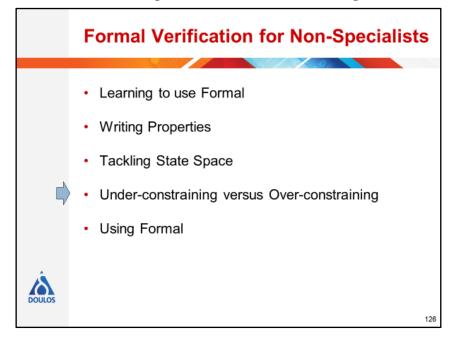

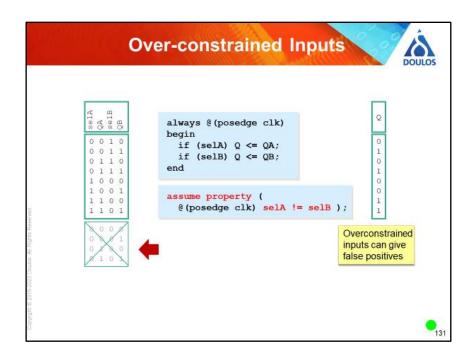

## Under-constraining versus Over-constraining

| Source Pane | - visualize:5                                                    |                                                                                                                 |                    | +8         |

|-------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------|------------|

| 9+Search th | e Source Code Pa 💠 🌳 🗐 🕤 🚺 of 2                                  | 🚯 D L 🕃 🔝 COI                                                                                                   |                    | V 🖬 🖬 (    |

| 1 800       | dule selAB (                                                     |                                                                                                                 |                    |            |

| 2 3         | input logic clk.<br>1'bl @                                       |                                                                                                                 |                    |            |

|             | input logic QA, selA, QB, selB,<br>1'bl1'bl 1'b01'b1             |                                                                                                                 |                    |            |

|             | output logic 0);<br>1'b0                                         |                                                                                                                 |                    |            |

| 5           | always @iposedge clk)                                            |                                                                                                                 |                    |            |

| 7 t         | 1'bl_0                                                           |                                                                                                                 | Inputs are under-c | onstrained |

|             | if (selA) 0 <= 0A;<br>1'b1 1 b0 1'b1                             |                                                                                                                 | inpato are analy   |            |

| 9           | if (selB) 0 <= QB;<br>1'b1 1 b0 1'b0                             |                                                                                                                 |                    |            |

| 11          | end <b>Lease</b>                                                 |                                                                                                                 |                    |            |

| 12 O        | neck celA: assert property (<br>'b0<br>@(posedge clk) sel# (=> ) | to a second s |                    |            |

|             | theck_selB: assert property (                                    | .po 1.pl                                                                                                        |                    |            |

| 15          | @(posedge clk) selB (=> 0                                        | Enact (OR)                                                                                                      |                    |            |

| 16          | erporeage that sets 100 t                                        | 1.00 1.00                                                                                                       |                    |            |

|             | inodule                                                          |                                                                                                                 |                    |            |

| 11 010      |                                                                  |                                                                                                                 |                    |            |

| Under-constrained Inputs                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Image: constrained inputs often give false negatives       Image: constrained inputs often give false negatives       Image: constrained inputs often give false negatives |

| 1 1 1 1                                                                                                                                                                    |

| mp             | ut Assume Statement                                      |

|----------------|----------------------------------------------------------|

| module selAB ( |                                                          |

| input logic    | clk,                                                     |

|                | QA, selA, QB, selB,                                      |

| output logic   | Q) ;                                                     |

| always @(pose  | edge clk)                                                |

| begin          |                                                          |

| if (selA) (    | 2 <= QA;                                                 |

| if (selB) (    | Q <= QB;                                                 |

| end            |                                                          |

| check selA:    | assert property (                                        |

|                | (posedge clk) selA  => Q == (QA) ;                       |

| check selB:    | assert property (                                        |

| -              | <pre>@(posedge clk) selB  =&gt; Q == \$past(QB) );</pre> |

| assume not 11  | : assume property (                                      |

|                | @(posedge clk) !(selA & selB) );                         |

| endmodule      |                                                          |

| Results                                     |            |          | Ì   |

|---------------------------------------------|------------|----------|-----|

|                                             |            |          |     |

| SUMMARY                                     |            |          |     |

| Properties Considered                       | : 4        |          |     |

| assertions                                  | : 2        |          |     |

| - proven                                    | : 2        | (100%) 👌 |     |

| - bounded_proven (user)                     |            | (0%)     |     |

| - bounded_proven (auto)                     | : 0        | (0%)     |     |

| - marked_proven                             | : 0        | (0%)     |     |

| - cex                                       | : 0        | (0%)     |     |

| - ar_cex                                    | : 0        | (0%)     |     |

| - undetermined                              | : 0        | (0%)     |     |

| - unknown                                   |            | (0%)     |     |

| - error                                     | : 0        | (0%)     |     |

| covers                                      | : 2        |          |     |

| - unreachable                               |            | (0%)     |     |

| <ul> <li>bounded_unreachable (us</li> </ul> |            |          |     |

| - covered                                   |            | (100%)   |     |

| - ar_covered                                |            | (0%)     |     |

| - undetermined                              |            | (0%)     |     |

| - unknown                                   | - 183 D.D. | (0%)     |     |

| - error                                     | : 0        | (0%)     | - 1 |

|                                                      | DOU                                                                            |

|------------------------------------------------------|--------------------------------------------------------------------------------|

| always @(pose<br>begin<br>if (selA) (<br>if (selB) ( | 2 <= QA;                                                                       |

| end                                                  |                                                                                |

| check_selA:                                          | <pre>essert property @(posedge clk) selA =&gt; Q == \$past(QA) );</pre>        |

| check_selB:                                          | <pre>assert property (     @(posedge clk) selB  =&gt; Q == \$past(QB) );</pre> |

| assume_not_11                                        | l: assume property (<br>@(posedge clk) selA != selB);                          |

| cover_00:                                            | cover property (<br>@(posedge clk) !selA & !selB );                            |

|                                                      | Check input not over-constrained                                               |

| Verifying Assumptions with Cover                                                                                                             | DOULOS  |

|----------------------------------------------------------------------------------------------------------------------------------------------|---------|

| <pre>always @(posedge clk) begin   if (selA) Q &lt;= QA;   if (selB) Q &lt;= QB; end</pre>                                                   |         |

| check_selA: assert property (<br>@(posedge clk) selA  => Q == \$past(QA) );                                                                  |         |

| <pre>check_selB: assert property (     @(posedge clk) selB  =&gt; Q == \$past(QB) ); assume_not_11: assume property (     Fix the ass </pre> | umption |

| <pre>@(posedge clk) !(selA &amp; selB)); cover_00: cover property (           @(posedge clk) !selA &amp; !selB );</pre>                      |         |

|                                                                                                                                              | 13      |

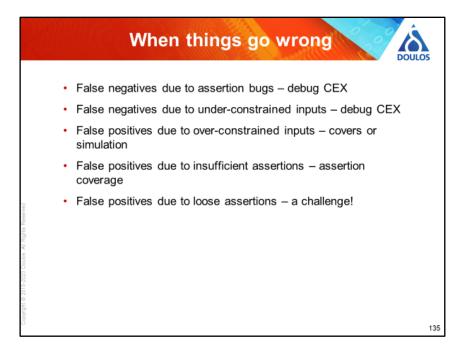

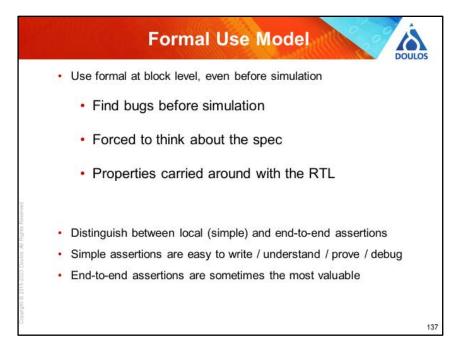

## Using Formal

## **Conclusions and Recommendations**

| UVM o                                                                                                              | or Formal?              |

|--------------------------------------------------------------------------------------------------------------------|-------------------------|

| Test<br>Reusside ventication environment<br>Vatual<br>sequence<br>Register Layer<br>Agent<br>Agent<br>Agent<br>DUT |                         |

| Simulation (UVM)                                                                                                   | Formal                  |

| Of course!                                                                                                         | Target pain points      |

| But maybe not everything                                                                                           | Complement simulation   |

|                                                                                                                    | Include in verification |

www.doulos.com