### The DMAPS Upgrade of the Belle II Vertex Detector

S. Bettarini – on behalf of the Belle II VTX Upgrade Group

Università di Pisa

Topical Seminar on Innovative Particle and Radiation Detectors (IPRD23) Siena, 25 - 29 September 2023

### OUTLINE

- Upgrade motivations

- All-pixel VTX design

- Vertexing/Tracking performances

- The OBELIX chip

- Chip TJ Monopix2:

- Lab. Test Results

- Test Beam Results

- Mechanics: iVTX & oVTX concepts:

- Low-mass ladder R&D

- support structure&cold-plate prototypes

- Conclusions

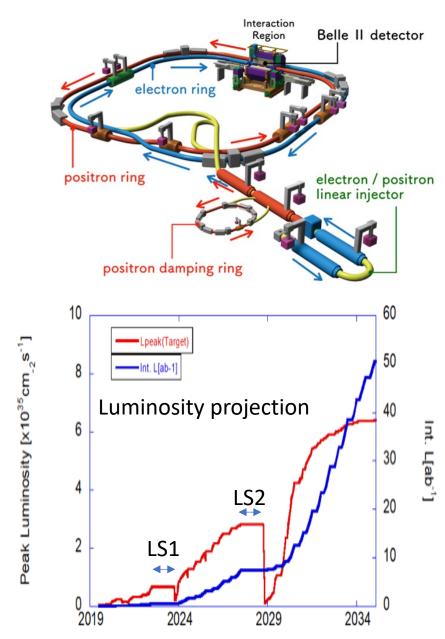

### SuperKEKB and Belle II Upgrade Motivation(s)

The **SuperKEKB** upgrade is planned during the Long Shutdown 2 (around 2027): a major redesign of the I.R. needed to reach the target luminosity  $(L = 6 \ 10^{35} \text{ cm}^{-2} \text{ s}^{-1})$  to increase the sensitivity of the Belle II experiment in searches for possible effects beyond the SM in flavor, tau, EW and dark

sector physics.

The current VXD (PXD + SVD)

has quite limited safety margins for running at higher luminosity:

• Performance degradation expected for higher occupancy

**LS2** provides the opportunity to install an upgraded detector to cope with the expected change of the experimental conditions. The new pixel vertex detector (VTX) should improve:

- robustness against harsh machine backgrounds, predicted at the higher luminosity with large extrapolation uncertainties

- resolution and track finding efficiency

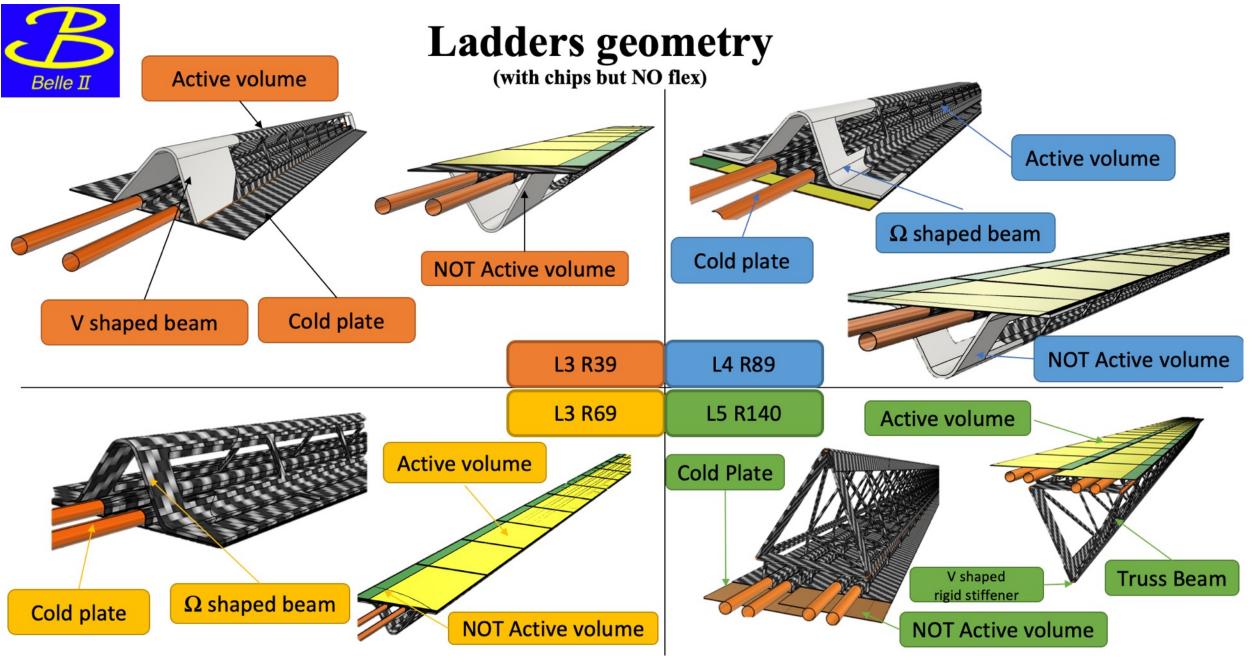

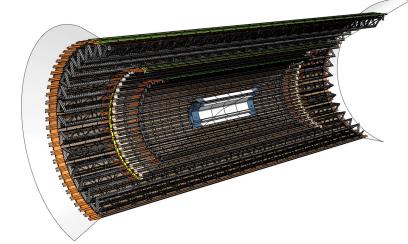

# The VTX baseline Concept

L1, L2:

Low material budget (~50 μm thin sensors): 0.1% X<sub>0</sub> (L1-2), 0.3-0.5% X<sub>0</sub> (L3-4), 0.8% X<sub>-</sub> (15)

### • Requirements:

- Radiation levels for L1 (r=1.4 cm)

- TID: ~10 Mrad/year

- NIEL:  $\sim 5 * 10^{13} n_{eq}/cm^2/year$

- Hit-rate up to 120 MHz/cm<sup>2</sup>

- Resolution < 15 um

- Fast integration time 50-100 ns

- Operation simplicity and reduced services

- 5 straight fully pixelated barrel layers

Same sensor chip for all layers

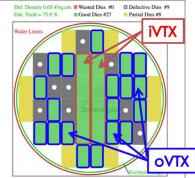

- iVTX: Innermost section (2 layers), self-supporting, air cooled

- oVTX: Outer sections (3 layers), CF structure, water cooled

- L3@3.9 cm (alternative @6.9 cm)

- L4@90 cm, L5@13.5 cm

- L3->L5: Power dissipation ~200 mW/cm<sup>2</sup> oVTX

- WTXOVTX

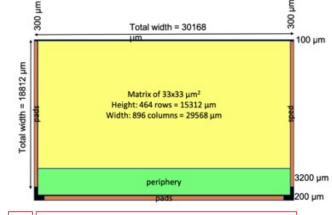

- Depleted monolithic active CMOS pixel sensors

- Chip size: 2x3 cm<sup>2</sup>

- Moderate pixel pitch 33  $\mu m^2$

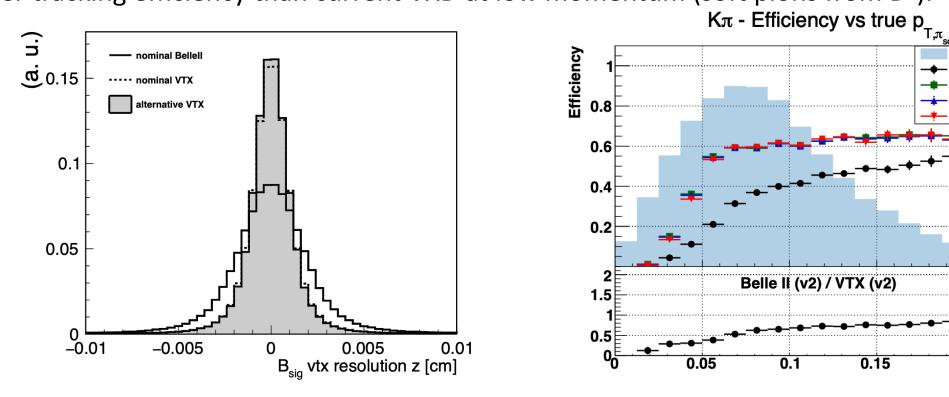

### VTX: Vertex/Tracking Performance

• Performance studies using benchmark channels, based on simulations of signal events with 3 possible cases of overlaid background (best:v1, intermediate:v2, worst:v3):

nominal Belle II (v2)

nominal VTX (v1 ominal VTX (v2)

ominal VTX (v3)

0.15

0.2

0.25

- Possibility to include all layers in the tracking

- A factor 200 in reduction in occupancy due to the faster integration time (and smaller pitch)

- VTX provides 35% better vertex resolution than the current VXD in the channel  $B^0 \rightarrow J/\psi K_s^0$ and it is insensitive to the level of background

- Better tracking efficiency than current VXD at low momentum (soft pions from D<sup>\*</sup>).

### The OBELIX (Optimized BELle II pIX chip)

OBELIX MAPS design is based on the existing TJ-Monopix2<sup>(\*)</sup> chip (TowerJazz 180 nm), developed for ATLAS, with core spec's on readout speed & max. rate matching Belle II needs. OBELIX will include: (\*) NIMA 978 (2020) 164460

- a new digital periphery for the trigger logic

- a trigger signal & finer time resolution on external layers, to improve BG rejection.

#### **Design features:**

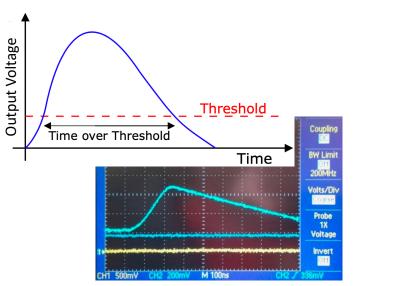

- Signal digitization: ToT (7 bits, 20 MHz)

- Threshold value set at single pixel level

- End-of-Column Logic trasmits ToT and timestamp (Bunch Crossing Id), Timestamp precision: 50 ns

- Matrix r.o. logic sustains a hit-rate > 600 MHz/cm<sup>2</sup>. Sensor peripheral logic able to trasmit data up to a hit-rate of 120 MHz/cm<sup>2</sup> (340 Mbps throughput).

Extensive tests on TJ-Monopix2 as a "proof of principle" of prototype sensor for Belle II VTX:

- Full chacterization on bench: threshold scans, calibrations

- Test-beams@DESY: Efficiency/Resolution measurements

- Radiation hardness (NIEL and TID irradiation campaigns in progress)

The submission of the chip to the foundry is expected at the end 2023.

# Analog Pixel Matrix DAC EoC & Buffer DAC EoC & Buffer Regulator IDAC VDAC Monitoring Temperatur Periphery (digital) Functional layout TRG0 (Trigger Group) E000 E001 E002 E003 So so so so so So State State TXU (Transmission Unit) TTT (Track Trigger Transmission) CRU (Control Unit) Clock Divider, Synchronization

Chip size optimized to maximize the number of 4 contiguous sensors

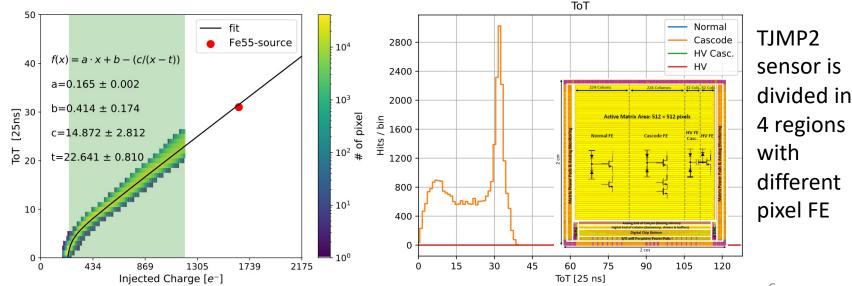

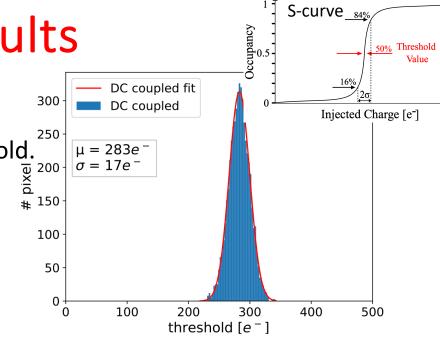

# TJ Monopix2 Lab test results

- Tests done in in Bonn, Pisa, HEPHY, CPPM, Gottingen

- S-curve tests with internal  $C_{injection}$  to determine threshold. Sensor tuned for low threshold and low dispersion: Threshold: (280 ± 17)e-, Noise: 8e-

- Calibrate Time-over-Threshold with injection test: (ToT in units of 25 ns 7-bit encoded)

Absolute calibration with Fe<sup>55</sup> source agrees with design, measurements ranging 8.5 - 10 e-/DAC

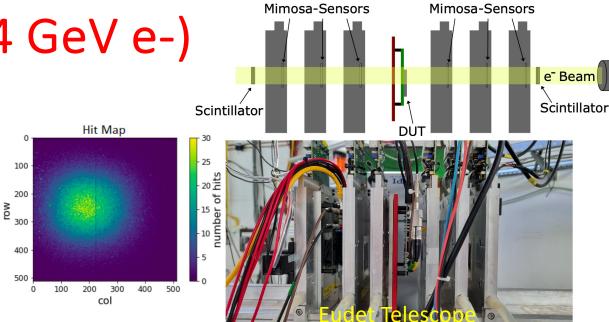

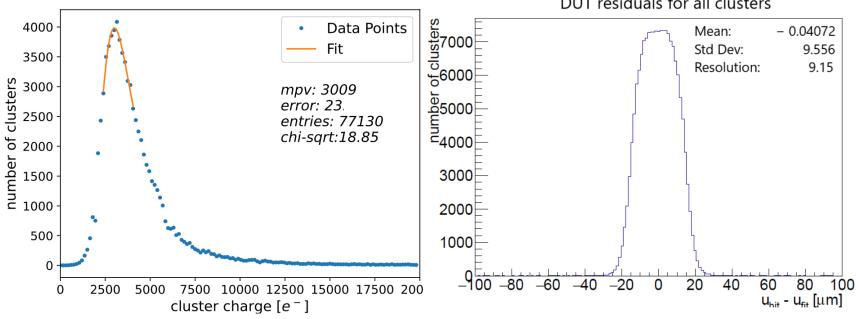

## Test-Beam campaign (Desy: 4 GeV e-)

In June '22: e- perpendicular to DUT

- Unirradiated chip

- Preliminary settings: used very high thr ~ 500e-

- Hit efficiency: 99.54 +- 0.04 %

- Cluster position residuals: 9.15 um  $(< pitch / \sqrt{12} = 9.5 um)$

DUT residuals for all clusters

New test beam in July 2023:

- Lower thr settings

- Angle scan

- Efficiency for irradiated chip  $(10^{14} - 10^{15} n_{eq}/cm^2)$

- Data analysis ongoing: (encouraging preliminary results!)

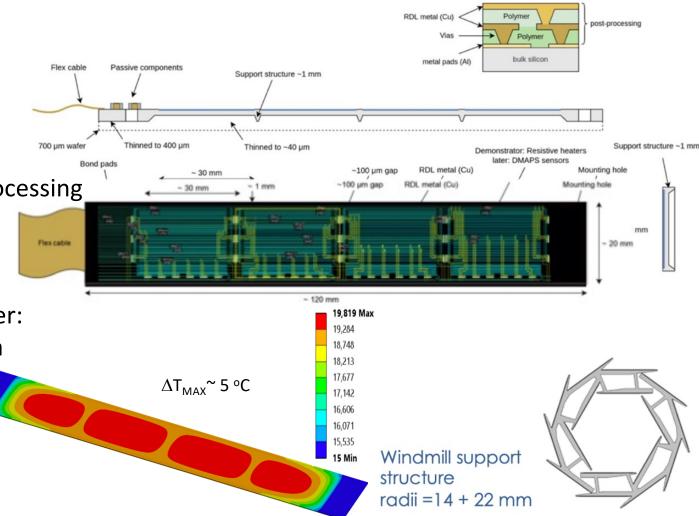

### iVTX Demonstrator

All-Silicon module concept:

- 4 contiguous sensor block diced

- Hetherogeneous thinning for stiffness

- To interconnet sensors on the ladder, a post processing step etches metal strip on the redistribution layer (prototypes in production by IZM-Berlin)

Results from air-cooling simulations on a single ladder: air at 15°C with speed ~10 m/s needed to evacuate a uniform power density of 200 mW/cm<sup>2</sup>, reaching a max. temperature of 20°C.

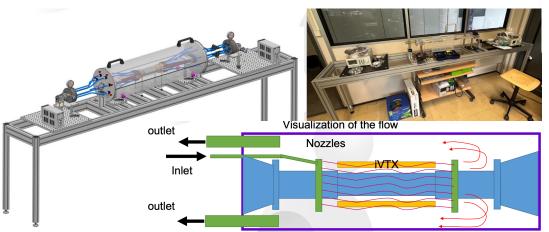

Under set-up @IJCLab (Paris) a test-bench facility to evaluate the efficiency of an air-cooling system for the whole iVTX detector (P~80 W):

- heat exchange by convection

- air flow through the actual iVTX geometry

- mechanical vibrations with v<sub>air</sub>~10 m/s to be measured.

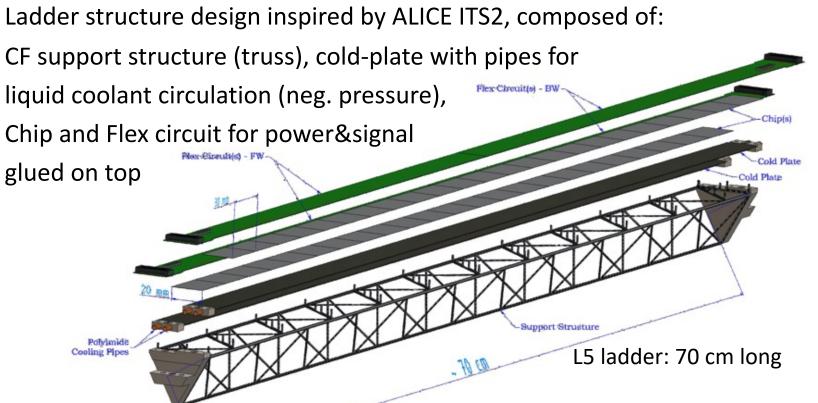

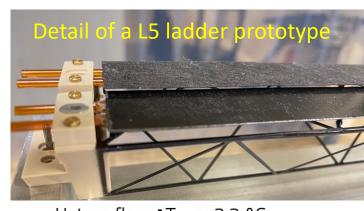

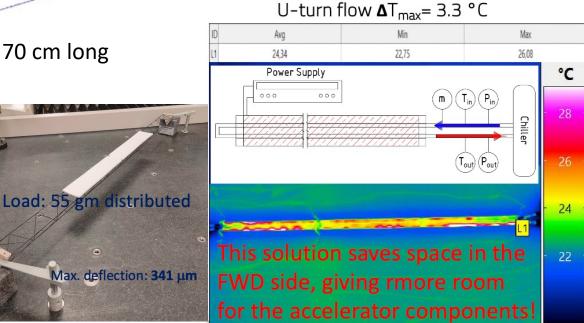

## oVTX Thermomechanics

Performed mechanical characterization of the L5 prototype:

- Distortion: measurements of sagitta (~340 um)

- Vibration: 1<sup>st</sup> resonance frequency (~250 Hz) (<< earthquake f.)</li>

Thermal characterization:

- Used Kapton heaters, inlet (T=10°C) and outlet on one side

- Uniform temperture along the ladder  $\Delta$ T max=3.3 °C

### oVTX

## Conclusions

• The SuperKEKB collider is planning a major upgrade of the I.R. to reach the design luminosity.

- All-layer monolithic vertex detector upgrade (VTX) to be installed in LS2 in ~2027:

- More performant and resilient against higher machine backgrounds

- Defined target spec's in terms of material budget, spatial resolution and integration time window

- Baseline chip technology TJ180 nm, evolving from TJ-Monopix2:

OBELIX: First steps towards a Belle II CMOS sensor, submission in Q4 2023/Q1 2024

- Realization of prototypes of inner/outer layers ongoing, submitted to the mechanical, thermal and electrical characterization.

- In the finalization phase the CDR of the Belle II Upgrade.