### Upgrade of ATLAS Hadronic Tile Calorimeter for the High Luminosity LHC

### Sandra Leone (INFN Pisa) on behalf of the ATLAS Tile Calorimeter system

16<sup>th</sup> Topical Seminar on Innovative Particle and Radiation Detectors (IPRD23) 25-29 September 2023 Siena, Italy

Sandra Leone, INFN Pisa

### The ATLAS Tile Calorimeter

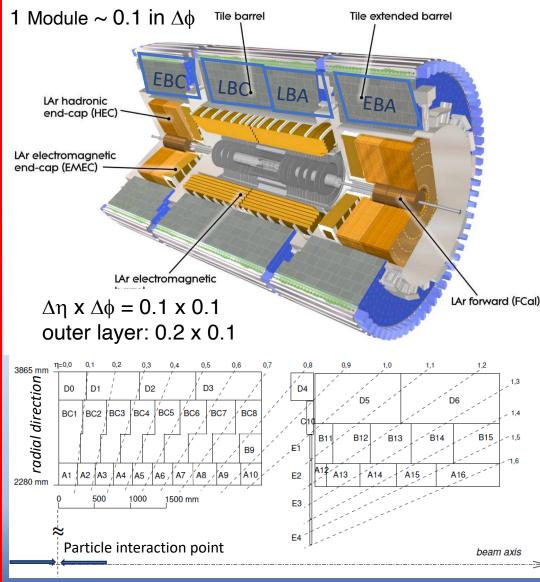

Tile Calorimeter (TileCal) is the central section ( $|\eta| < 1.7$ ) of ATLAS hadron calorimeter

- Four partitions: one Long Barrel (LBA+LBC) and two Extended Barrels (EBA, EBC) each composed of 64 modules in  $\phi$

- Coverage |η| < 1.0 (LB), 0.8 < |η| < 1.7 (EB).

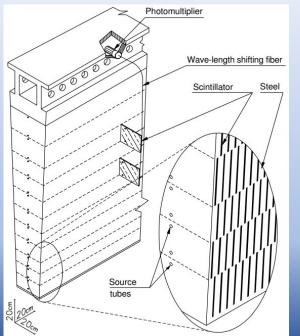

- Sampling calorimeter: steel absorbers and plastic scintillators (the "tiles") coupled to wavelength shifting (WLS) fibers.

- About 5000 pseudo-projective cells.

- Each cell readout by 2 PMTs (~10k readout channels in total).

- Energy resolution for hadrons:

$$\frac{\sigma}{E} = \frac{50\%}{\sqrt{E}} \oplus 3\%$$

• Dynamic range from ~10 MeV to ~2 TeV per calorimeter cell

# **SATLAS** TileCal Upgrade for HL-LHC: motivations **SATEAS**

- High Luminosity (HL) LHC, starting around 2029, will achieve an instantaneous luminosity 5-7 higher than the LHC nominal value and total integrated luminosity of ~4000 fb<sup>-1</sup> at the end (2029-2040)

- $\rightarrow$  high radiation environment

- $\rightarrow$  high pile-up contribution, from 60 in Run3  $\rightarrow$  up to 200 collisions per bunch crossing

- Lifetime of TileCal extended  $\rightarrow$  Readout electronics is ageing due to operation time and to radiation

- Current readout architecture is not compatible with the new fully digital TDAQ system of ATLAS and with the timing requirements for trigger and data flow.

- $\rightarrow$  Technical challenges coming from the HL-LHC are huge and complicated

### TileCal upgrade strategy:

- Replace the full readout system to:

- $\rightarrow$  handle the increase in the data rate

- $\rightarrow$  enhance radiation tolerance of the on-detector electronics

- $\rightarrow$  be compatible with the fully digital ATLAS Trigger/DAQ system

- Improve reliability through redundancy  $\rightarrow$  reduces impact of component failures

- The scintillating tiles and WLS fibers are built into the detector  $\rightarrow$  will not be modified.

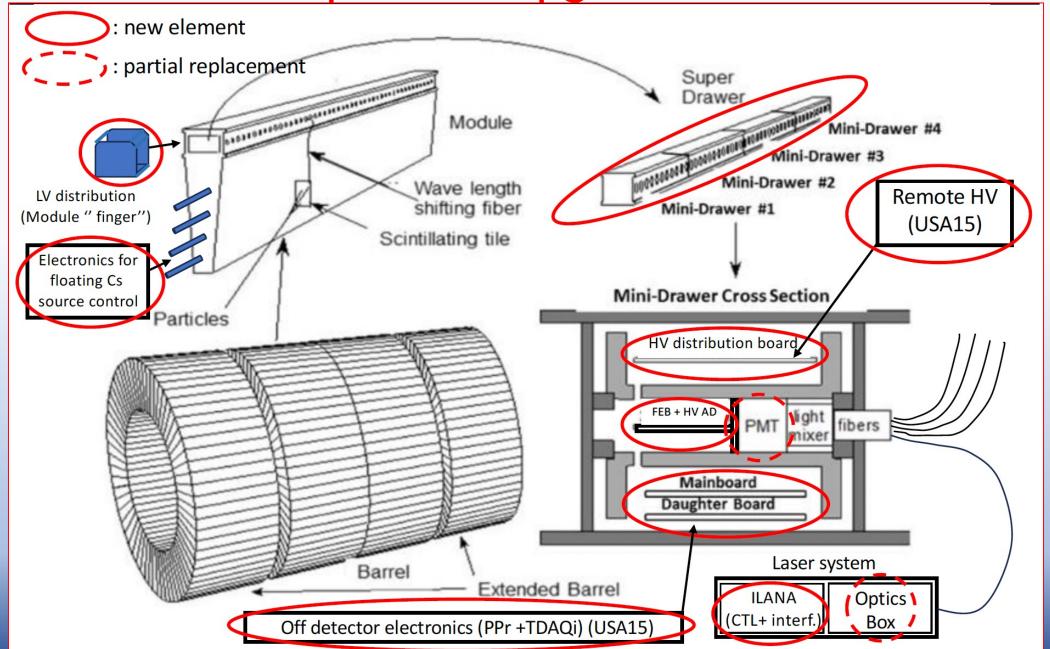

## **SATLAS** TileCal Upgrade for HL-LHC: overview

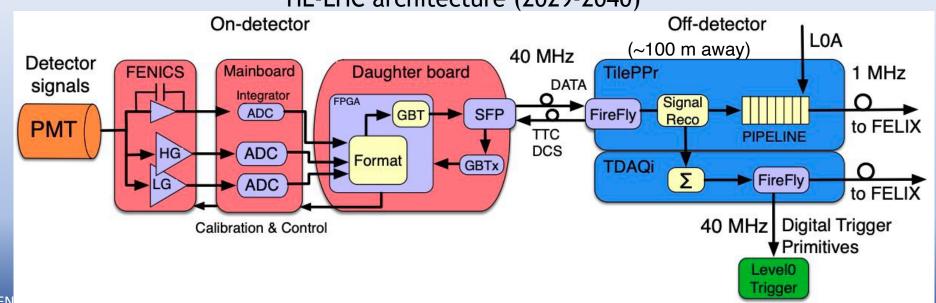

- Complete replacement of on-detector and off-detector electronics.

- Increased detector read-out bandwidth: 40 Tbps for the entire TileCal.

- Compatibility with new digital ATLAS trigger system up to 40 (1) MHz read-out (accept) rate.

- New mechanical structure for the on-detector electronics  $\rightarrow$  easier access for maintenance.

- New high voltage active dividers for all PMTs and replacement of 10% of most exposed PMTs.

- Improved High Voltage (HV) and Low Voltage (LV) distribution systems

- New control electronics for the Cs source system.

- New control/readout electronics for the laser system and upgraded optical line.

HL-LHC architecture (2029-2040)

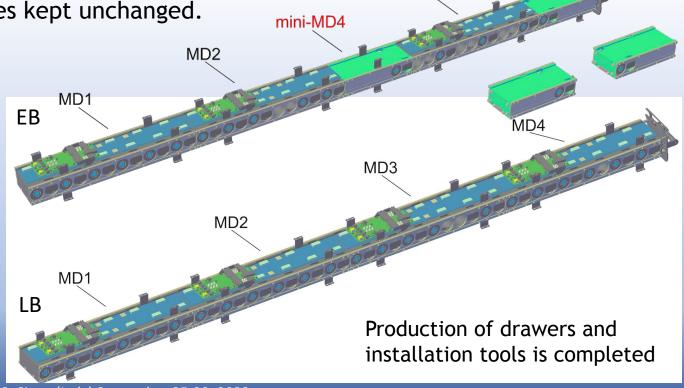

### The mechanics

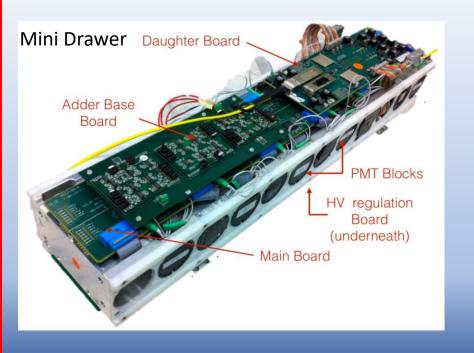

- Currently Tile on-detector electronics is housed in long Super-Drawers: difficult to extract to access electronics.

- The upgrade mechanics has substructures (Mini-Drawers) to facilitate access during maintenance.

- Different configuration for Long and Extended Barrel modules:

- 4 Mini-Drawers (MD) for Long Barrel modules  $\rightarrow$  45 PMTs

- 3 MD + 2 micro-drawers for Extended Barrel modules  $\rightarrow$  32 PMTs

- Each mini-drawer is divided into two independent sections for redundant cell readout, accommodating 12 PMT blocks for 6 TileCal cells.

- Independent electronics and readout for each half of MD.

- Remaining mechanics of the individual modules kept unchanged.

mini-MD5

MD3

## The PMT Block (I)

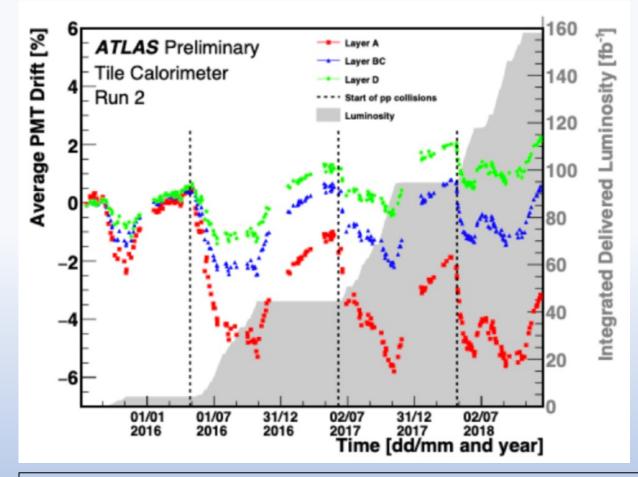

- 1024 PMTs out of 9852 will be replaced due to ageing effects (those reading the most exposed cells: expected response loss > 25%)

- Characterization of new Hamamatsu PMT model R11187 used for replacement (same geometry as legacy model, better response stability) was done in Pisa (for more details see also the POSTER: "Long term aging studies of the new PMTs for the HL-LHC ATLAS hadron calorimeter upgrade")

- Dedicated test-benches are operational at Bratislava, Pisa and CERN to test and qualify new PMTs.

- Tests of first production batch (20 PMTs) performed in the 3 sites in Summer 2023

Passive HV dividers will be replaced with active dividers to provide response linearity at high anode currents (up to 100 µA) (production and testing completed).

Pisa setup used for long term PMT testing OPTICS BOX PMT box temperature senso 24 PMTs (PMT0-23) integratin clear fibre bundle beam splitter reen DC LF lines temperature CTL lines sensor Signal lines Average PMT relative response **ATLAS** Preliminary Hamamatsu PMT A R7877 **Tile Calorimeter** O R11187 1.05 0.95 0.85 0.8 100 200 300 400 500

Sandra Leone, INFN Pisa

Integrated anode charge [C] 6

### The PMT Block (II)

### <u>On detector electronics</u> $\rightarrow$ <u>new Front End board: the FENICS</u>

(Front End board for the New Infrastructure with Calibration and signal Shaping)

- Provides PMT pulse shaping with 2 gain amplifications (LG:x0.4, HG:x16), 0.2 pC to 1000 pC dynamic range.

- High precision integration of slow signals for <sup>137</sup>Cs calibration and for luminosity measurements.

- Built-in Charge Injection system for ADC calibration.

- Analog signals are sent to the next step of the readout chain: the Main Board.

- Production and burn-in tests are in progress.

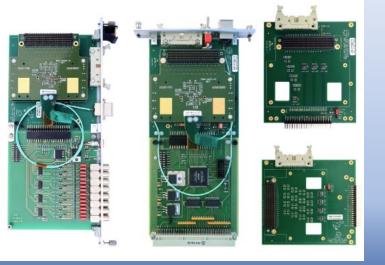

Production FENICS test-bench @ Clermont Ferrand

FENICS card

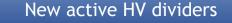

# **SATLAS** On detector electronics: the Main Board **SATERS**

#### 69 cm long board, FPGAs used only for configuration

One Main Board installed in each MD receives and digitises the analog signals from 12 FENICS

- 12 bit dual ADCs at 40 Msample/s for 2 gain signals.

- 16 bit ADC at 50 ksample/s for integrated signal readout.

Provides digital control and configuration of FENICS + high-speed transmission to the DaughterBoard

• Divided in two halves for redundancy  $\rightarrow$  independent read-out and LV power distribution to all on-detector electronics.

Production is close to completion (845 boards out of 896).

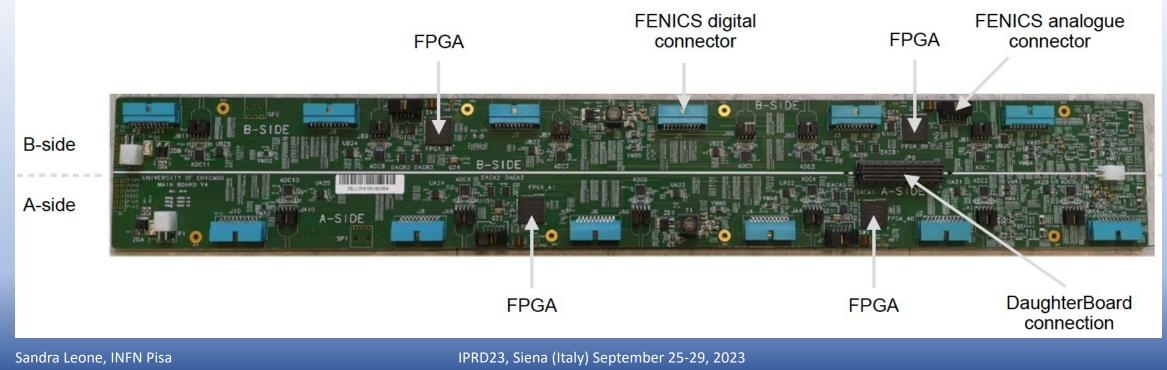

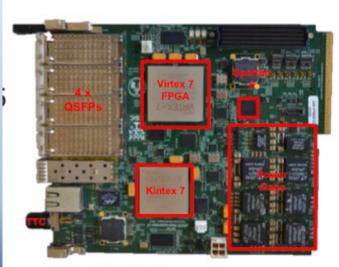

### **SATLAS** On detector electronics: the DaughterBoard **SATEAS**

High-speed interface with the off-detector electronics:

- Collects PMT digitized data from the MainBoard.

- Interfaces to off-detector electronics through optical links  $\rightarrow$  4 uplinks @ 9.6 Gbps

- Clock and commands recovery and distribution.

- Uses 2 GBTx chips for LHC clock recovery and distribution

- 2 Kintex Ultrascale(+) FPGAs for communication and data processing

- 2 QSFP high-speed optical modules

- Each side provides control and readout services for 6 PMTs (12 in total)

- A massive campaign of SEE, TID and NIEL radiation tests was performed for most of the active components and KU FPGAs

- Design to be finalized in 2023.

#### •Redundancy Line

•Power circuitry •Chained Power-up and Fast triggered power-cycle sequence •Current monitoring

•Cesium interfaces (5V)

•xADC interface

•GBTx I2C/configuration •ProASIC JTAG •Kintex Ultrascale JTAG

·400 pin FMC connector to MB

•Kintex Ultrascale FPGAs

•128-Mbit PROM chips

·48-bit ID chips

•CERN radiation tolerant GBTxs

•ProASIC FPGAs

•4x SFPs+ •2x Downlink RX @4.8Gbps •4x Uplink TX @9.6 Gbps

### **Off-detector electronics**

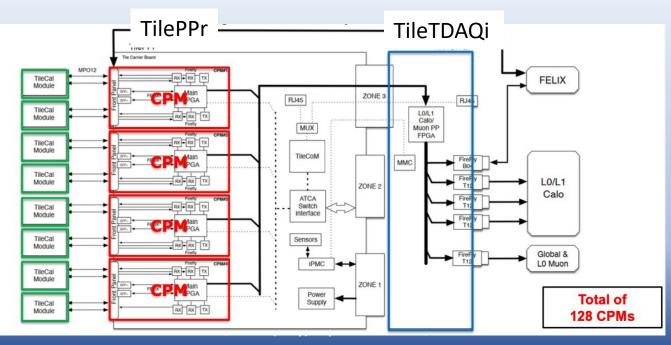

The back-end electronics is formed by Tile PreProcessor (PPr) and TDAQi systems.

- Real time data processing, handling and reconstruction from on-detector electronics

- Storage of up to 10  $\mu s$  of consecutive data samples in pipeline memories

- Provides clocks and configuration for the TileCal modules

- Interface with the ATLAS trigger and read-out systems (FELIX)

Each PPr formed by 1 ATCA carrier + 4 Compact Processing Modules (CPM)  $\rightarrow$  32 PPr in total

• Each CPM receives data from 2 modules (8 minidrawer)  $\rightarrow$  128 CPMs in total

32 Tile TDAQi in total: Interfaces with L0Calo, L0Muon, Global, and FELIX system

Sandra Leone, INFN Pisa

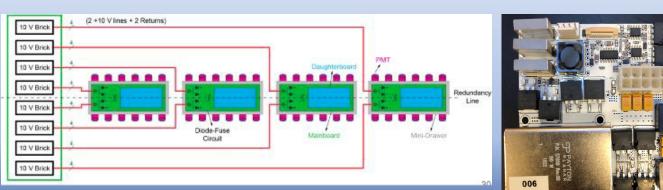

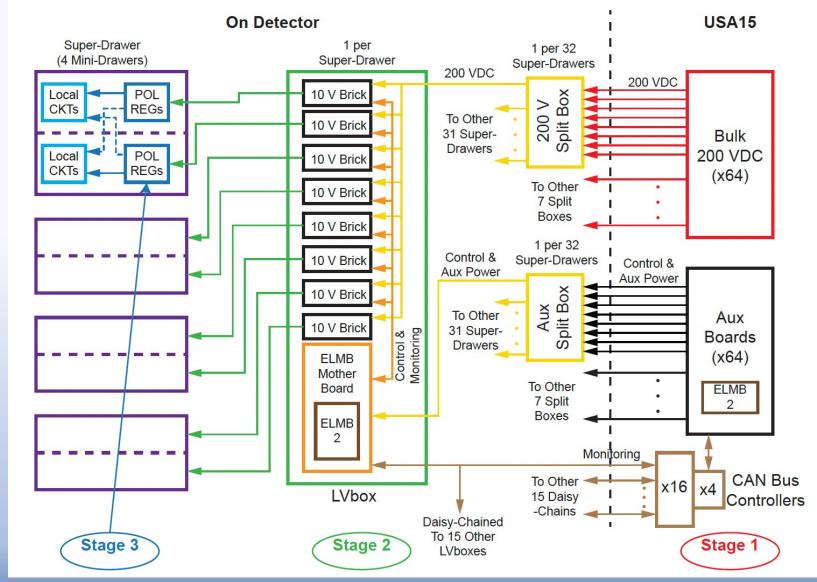

### Low/High Voltage Distribution

#### Low Voltage:

The high radiation environment on-detector requires Rad-Hard DC-DC converters.

- There are strong constraints in terms of radiation tolerance, noise, power efficiency and reliability.

- 200 V DC is transformed to 10 V DC to power the Point of Load regulators on the on-detector electronics boards.

- Lower number of connections (single DC level (+10V) and regulators for the voltages needed).

- Redundant power distribution  $\rightarrow$  two bricks connected to each MD, one for the up and one for the down half.

Low voltage power distribution scheme. Sandra Leone, INFN Pisa

Low voltage brick

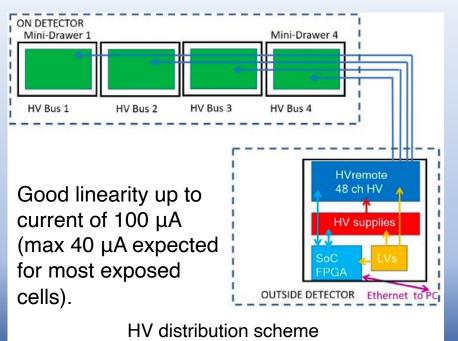

#### High Voltage: new concept

HV power supplies (48-channel boards) and regulators are installed in the ATLAS service cavern (USA15)

- 100 m long HV cables for each PMT.

- HV bus board set high voltage to individual PMTs

- Easy maintenance, no radiation hardness issues

- Prototypes were produced and validated during the test-beam at CERN SPS since 2018.

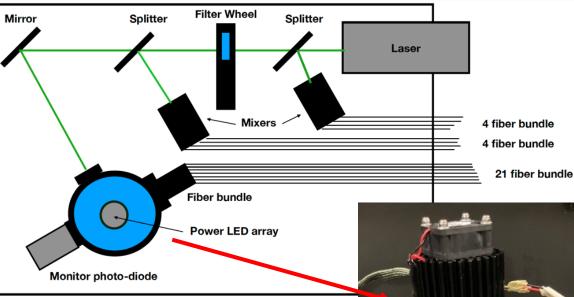

### **Calibration systems**

#### Laser Calibration system

- New TDAQ interface and control electronics board is under test at CERN.

- We will also replace the pulsed laser and add a continuous light source (LED array) to mimic the actual regime during collisions.

- The optical line is being redesigned: an integrating sphere used to mix pulsed and DC light.

#### **Cesium calibration system**

- The on and off-detector electronics will be replaced.

- The new electronics is designed around the CERN EMCI-EMP systems.

- Design of all boards is ready, all prototypes were produced and are under test.

- NIEL and SEU tests were performed, TID tests in progress.

Preliminary scheme of new optical line

Power LED array positioned on top of Integrating sphere

#### New Cs electronics prototype

Sandra Leone, INFN Pisa

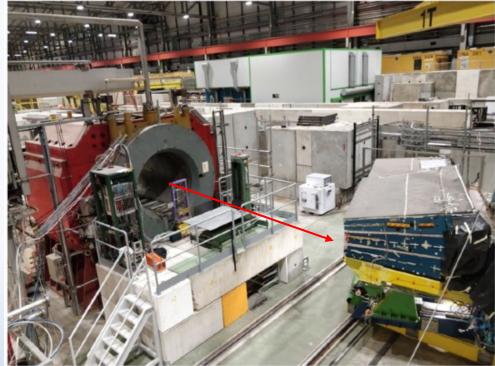

### Test-beam at the SPS

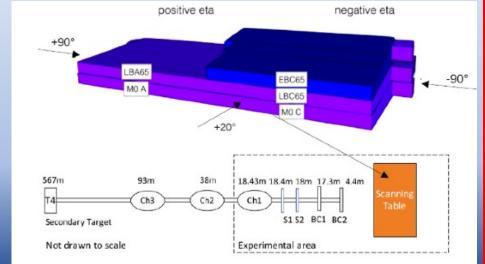

- Many test-beam campaigns were performed in the SPS-H8 beam line between 2015 and 2023 to validate the hardware and carry out physics studies

- $\rightarrow$  3 modules from the calorimeter (two Long-Barrel and one Extended-Barrel)

- Different designs of the front-end electronics have been tested over the years

- The setup is partially equipped with new electronics

- We used electron, muon and hadron beams of various energies and the detector positioned in different orientation

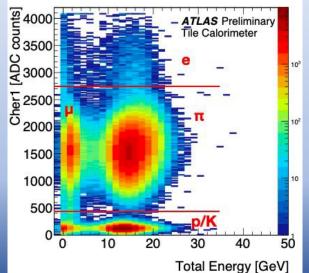

- Cherenkov detectors, part of the beam instrumentation, allow for particle ID

Cherenkov 1 signal vs. energy measured in the calorimeter for 18 GeV particle beams

TileCal setup in the SPS-H8 beam-line.

Sandra Leone, INFN Pisa

### Some test beam results

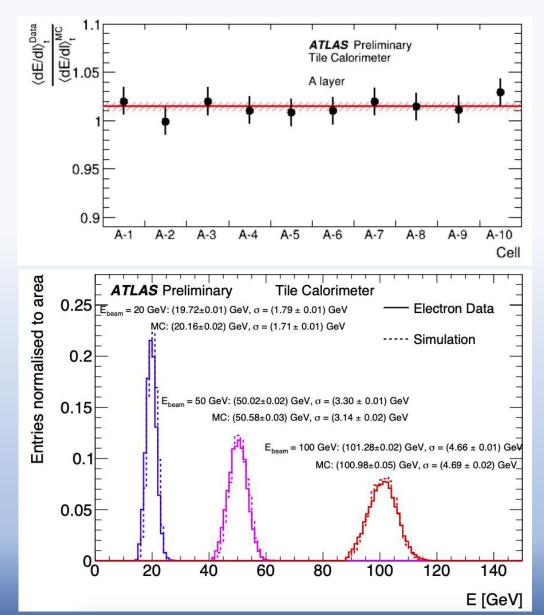

#### Muons:

- On top, results from 165 GeV/c Muons that cross the entire TileCal modules with an angle of 90°, with new electronics (May 2018 campaign).

- The deposited energy is a function of the muon path length in each cell → checking the equalization of the cell response.

- Layer uniformity within 1%, very good agreement of data and simulations.

#### **Electrons:**

- Below, electrons of different energies are used to determine the EM scale by calculating the average chargeto-energy conversion factor, (pC/GeV).

- We could verify the response linearity and the energy resolution as function of the electron energy

### Some test beam results

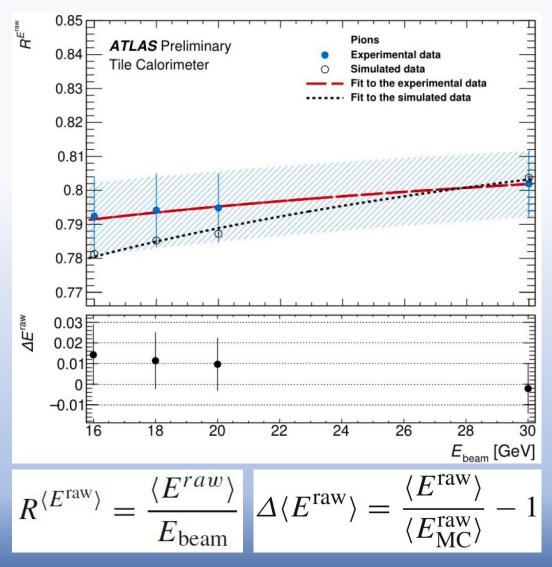

#### Hadrons:

- Response to isolated hadrons is important to validate and improve the modeling for jet and tau measurements in ATLAS.

- The beam composition is a mix with a majority of  $\pi$ , K and protons with fractions not known a priori.

- Kaon content is small in the beam  $\rightarrow$  dominated by statistical errors

- Protons have high statistics  $\rightarrow$  low systematic and statistical uncertainties

- For pions, electron contamination plays an important role.

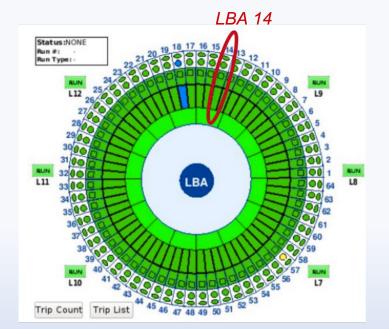

### Phase-II demonstrator in ATLAS

- In Summer 2019, we installed a special module equipped with upgrade mechanics/electronics ("*Demonstrator*") in one of the TileCal long barrel modules of the ATLAS detector.

- It is backward compatible with the current DAQ system: dual readout → Legacy and Phase II.

- It has proven a very useful exercise to learn about the new electronics and timely identify problems.

- Embedded into legacy calibration systems (pedestal, laser, charge injection system (CIS)).

- $\rightarrow$  Stable, good CIS and laser signals.

- It was decided to keep it in for Run-3.

- Good performance with low noise levels wrt the legacy modules.

- Currently, the Demonstrator module provides physics data from proton-proton collisions with the rest of the TileCal modules.

- Aiming to install a second special module in the extended barrel.

TilePPr Demonstrator

### Summary

• The High-Luminosity LHC era will bring new challenges:

$\rightarrow$  a harsher radiation environment, higher pile-up, higher luminosity and readout rates

- In order for TileCal to continue to play a crucial role for ATLAS physics program an upgrade is required:

- $\rightarrow$  replace all on- and off-detector electronics and 10% of the PMTs in LS3 (2026-2028)

- $\rightarrow$  new mechanical structure (more reliable and easier to service) and electronics (more radiation hard)

$\rightarrow$  new digital readout and trigger path, ready for 1 MHz first level trigger rate.

- Regular test-beam campaigns are helping to validate designs and integrate different components of the upgraded detector

- The Tile Demonstrator in ATLAS is fully integrated in the current ATLAS DAQ and DCS systems, and it is taking Run 3 data.

### The overall project is on track and advancing well

# Backup

### TileCal components upgraded for HL-LHC

EXPERIMENT

### **Off-detector electronics**

- Each PPr comprises 1 Carrier + 4 CPM and processes data from 8 modules (2 modules per CPM)

- $\rightarrow$  Processing, data handling from "on detector" electronics and pipeline of data.

- $\rightarrow$  Distribution of the LHC clock towards the on-detector electronics.

- $\rightarrow$  Interface with the ATLAS read-out system FELIX.

- $\rightarrow$  Communication with the Timing, Trigger and Control system for the LHC.

- The TDAQi is connected to the rear side of the Carrier.

- Receives the cell energies from 4 CPMs synchronously

- $\rightarrow$  Calculation of the trigger objects (trigger towers or cluster in  $(\eta, \Phi)).$

- $\rightarrow$  Building and synchronous transmission of trigger objects to the different electron/photon, jet, muon trigger sub-systems and Global trigger.

- $\rightarrow$  It sends monitoring data to the FELIX system.

Compact Processing Module (CPM) IPRD23, Siena (Italy) September 25-29, 2023

PPr carrier boards

Trigger DAQ interface (TDAQi)

### Three-stages LV system

The block diagram of the TileCal low-voltage distribution system for the HL-LHC upgrade. The "10 V bricks" stand for 200 V DC to 10 V DC converters. The stage 3 is implemented directly on the front-end electronics boards

### PMT aging studies

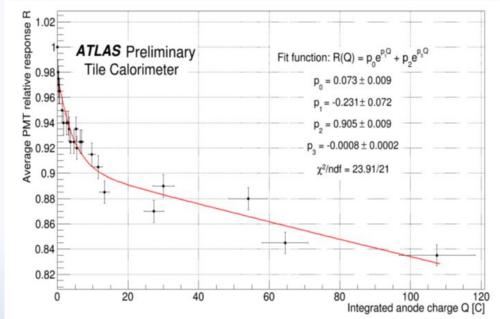

Double exponential fit of the data representing the average response variation as a function of the integrated charge. Different cells (integrating different charges) are used in the plot.

Cell layer A : innermost layer, most irradiated cells, larger PMT anode current, larger response loss Cell layer BC : intermediate layer Cell layer D : outermost layer, less irradiated cells, smaller PMT anode current, no relevant response loss