# Characterization of the radiation tolerant ToASt ASIC for the readout of the PANDA MVD strip detector

### FRANCESCA LENTA ON BEHALF OF THE PANDA-MVD GROUP

francesca.lenta@polito.it francesca.lenta@to.infn.it

**Politecnico** di Torino

## SEPTEMBER 26th 2023

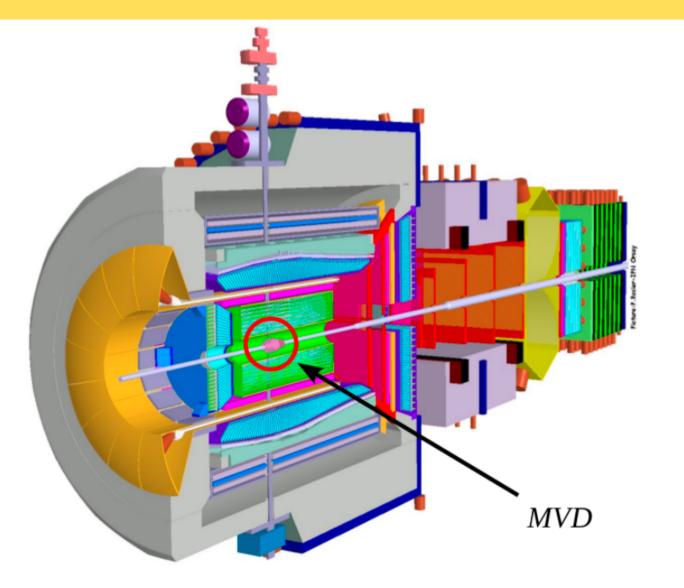

## The PANDA experiment

**Pixel barrels**

Strip barrels

- disks

- Located at the FAIR facility in Darmstadt

- *antiproton-proton* and *antiproton-nuclei* annihilation reactions

- Fixed target (a target pipe intersects the beam pipe) and triggerless experiment

#### Francesca Lenta

#### 26/09/2023

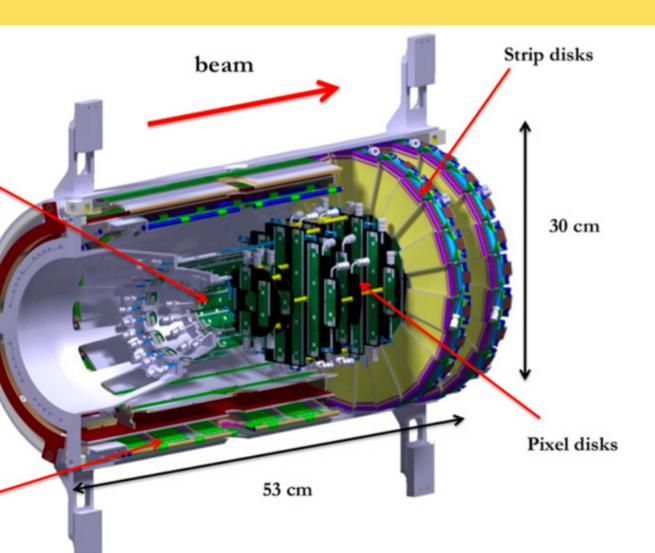

• Barrel region : 2 layers of Silicon Pixel Detectors (SPDs) + 2 of Silicon Strip Detectors (SSDs) • Forward region : 4 SPDs disks, 2 SPDs + SSDs

• Double side SSDs

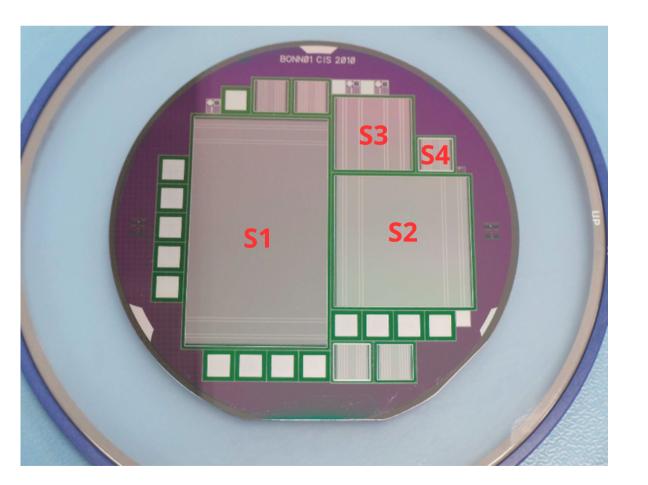

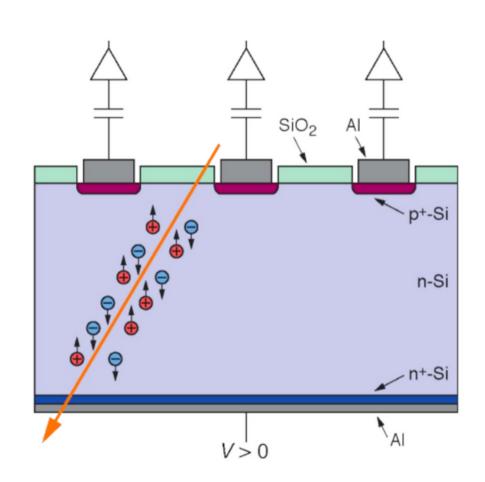

# Silicon Strip Detector

DEVELOPED BY

UNIVERSITY OF GIESSEN

JUSTUS-LIEBIG-

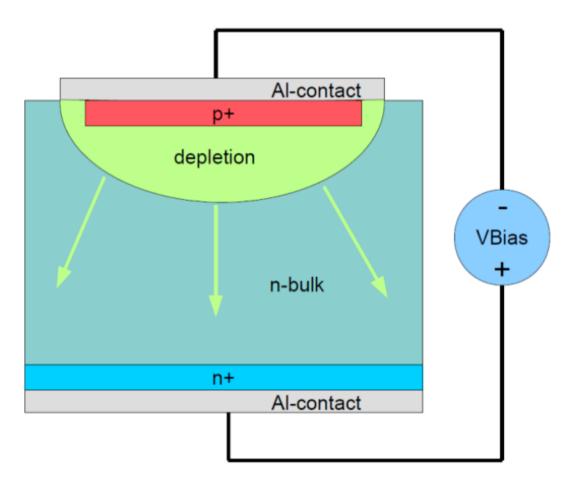

- PN-junction

- Depletion voltage  $\approx$  100 V

- Breakdown voltage > 200 V

26/09/2023

Francesca Lenta

- DOUBLE SIDE SILICON STRIP DETECTOR:

- Doped silicon semiconductor

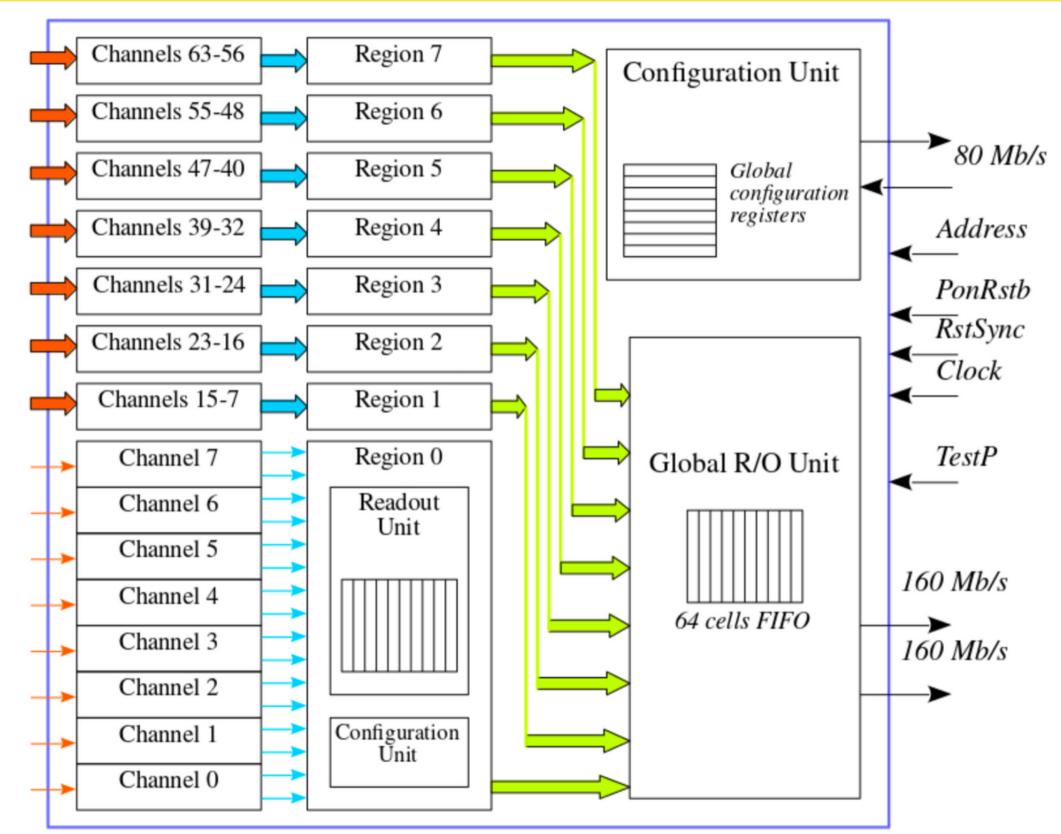

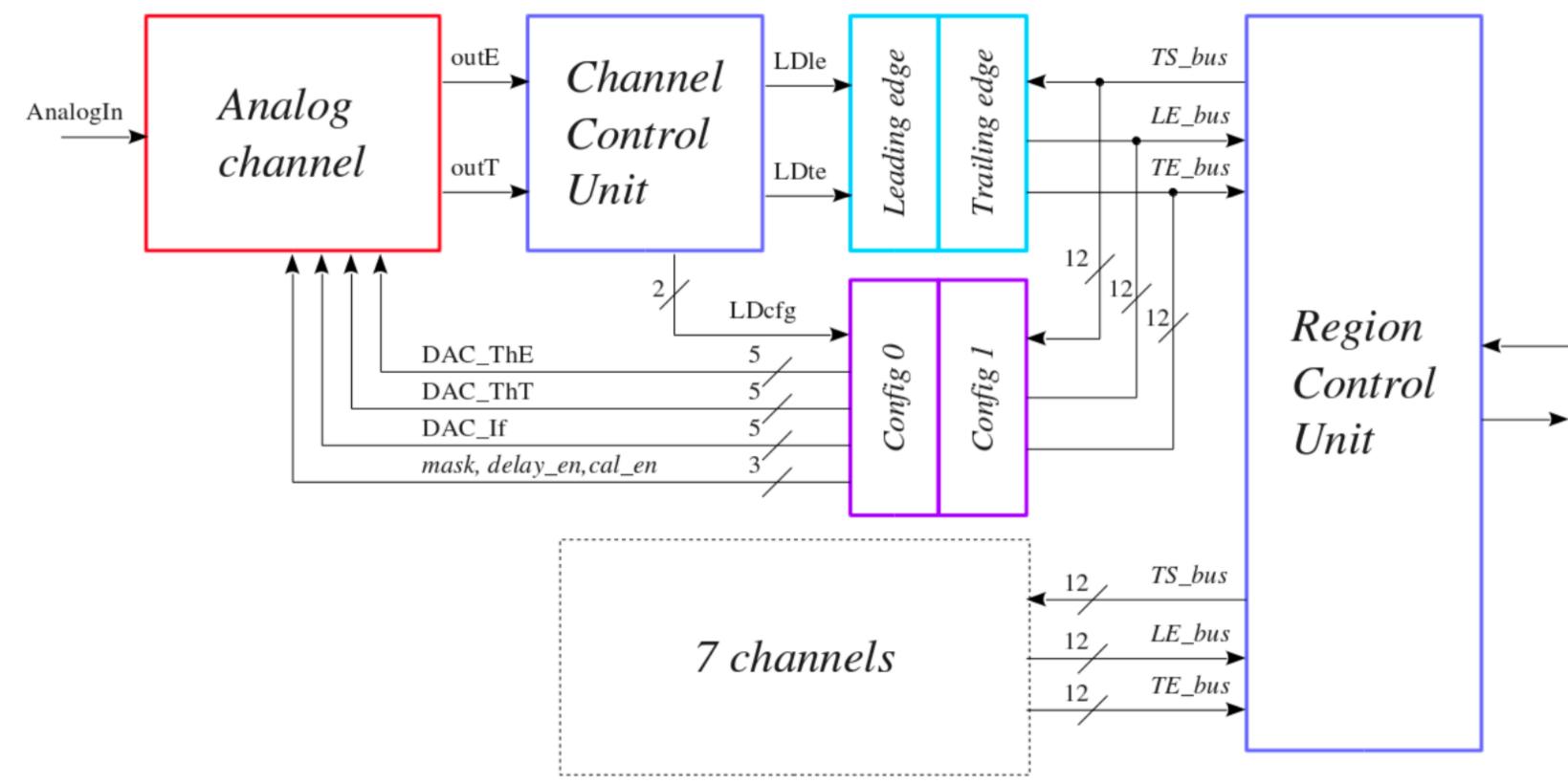

# ToASt specifics and architecture

- Each particle crossing the detector has to be associated with its space, energy and its Time of Arrival (ToA)

- 64 readout channels

- Each channel provides the ToA and the charge measurement

- 160MHz clock

- 8 regions with local FIFO

- Two 160 Mb/s serial lines

- Configuration serial link running at half the master clock frequency (80 Mb/s)

- Fully digital interface in order to avoid the transmission of noise sensitive analog signals

- Triplicated logic to protect against single event upsets

- Commercial 110 nm CMOS technology

#### Francesca Lenta

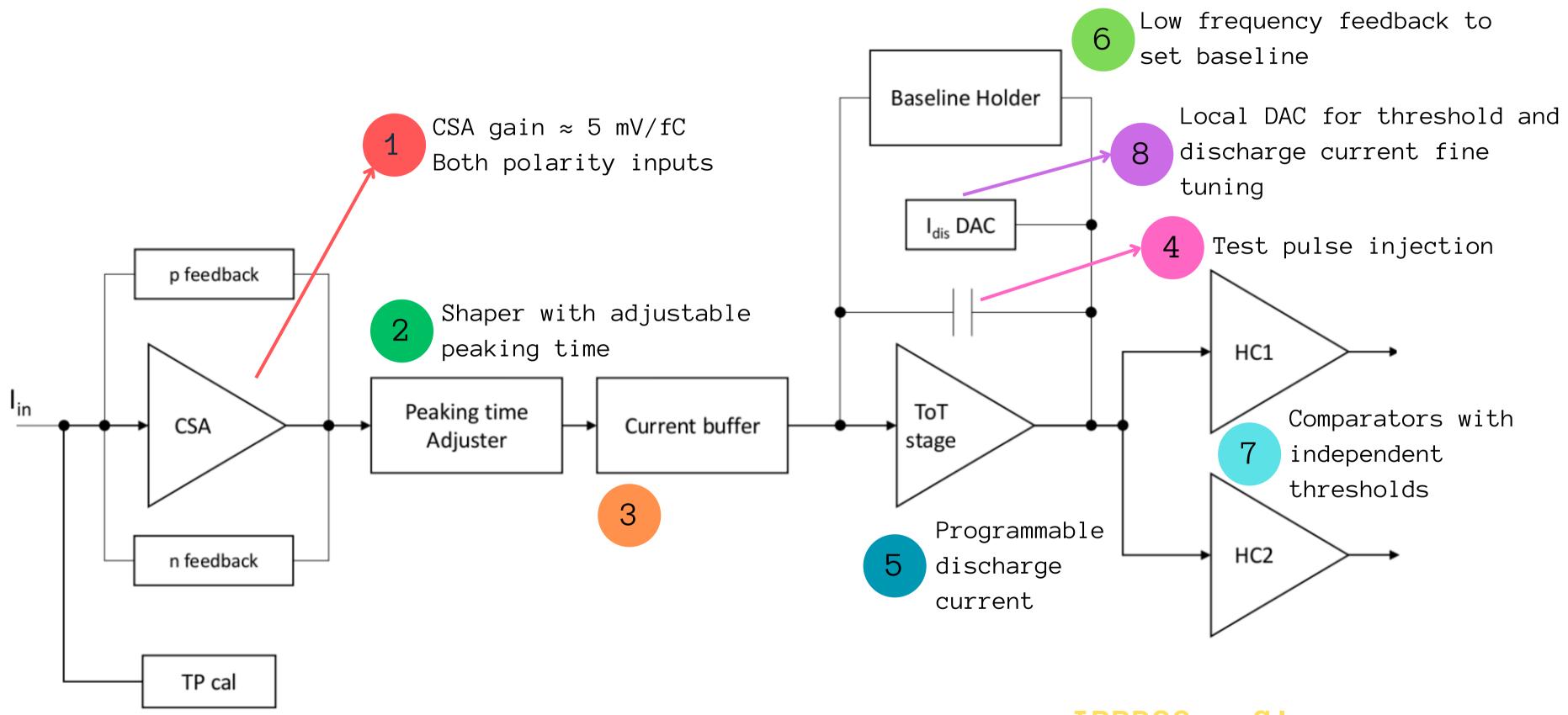

## ToASt analog channel

Francesca Lenta

26/09/2023

## ToASt time measurement

Francesca Lenta

```

26/09/2023

```

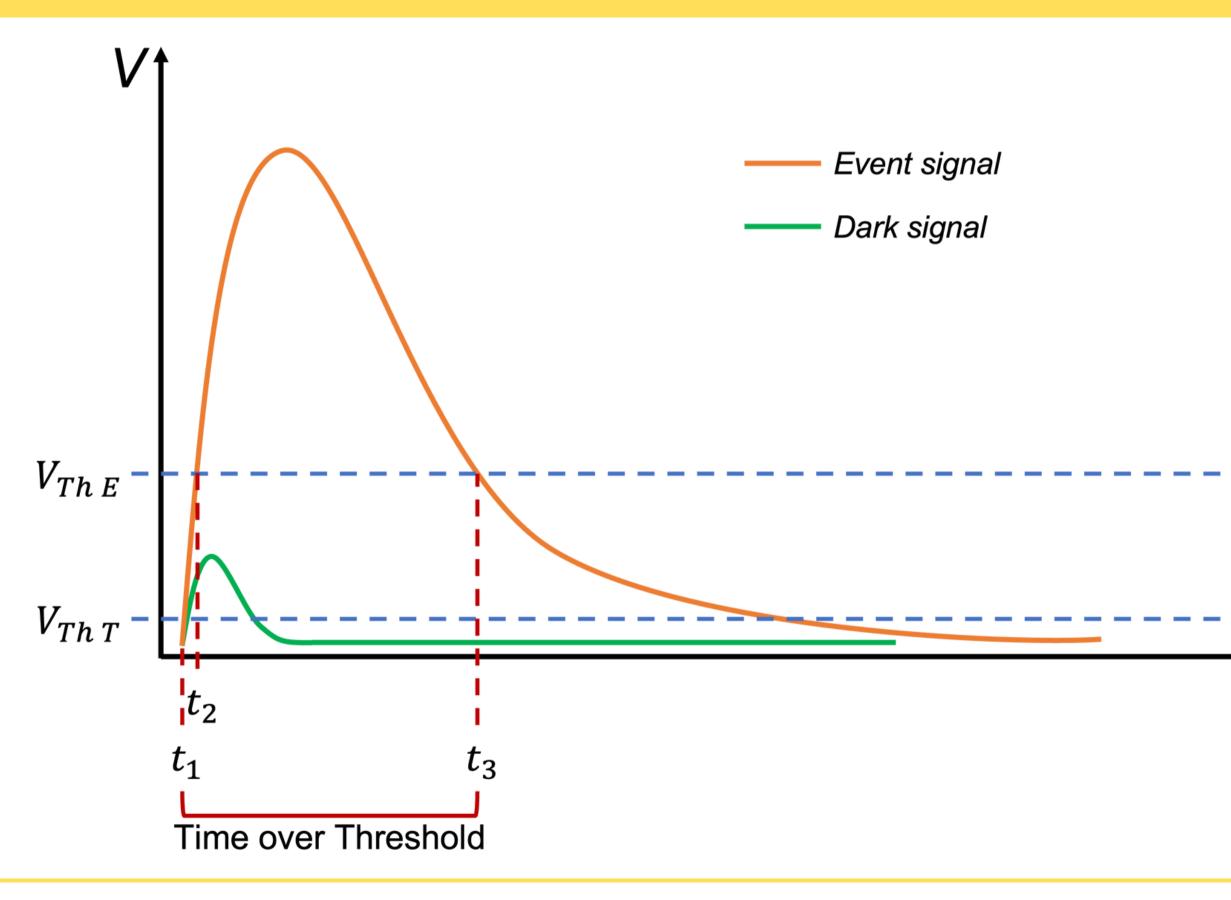

Two threshold:

- store the time stamp on the low threshold  $(Vth_T)$

- validate it with the high threshold  $(Vth_E)$

ToT = t3 - t1

Possibility to disable the double threshold

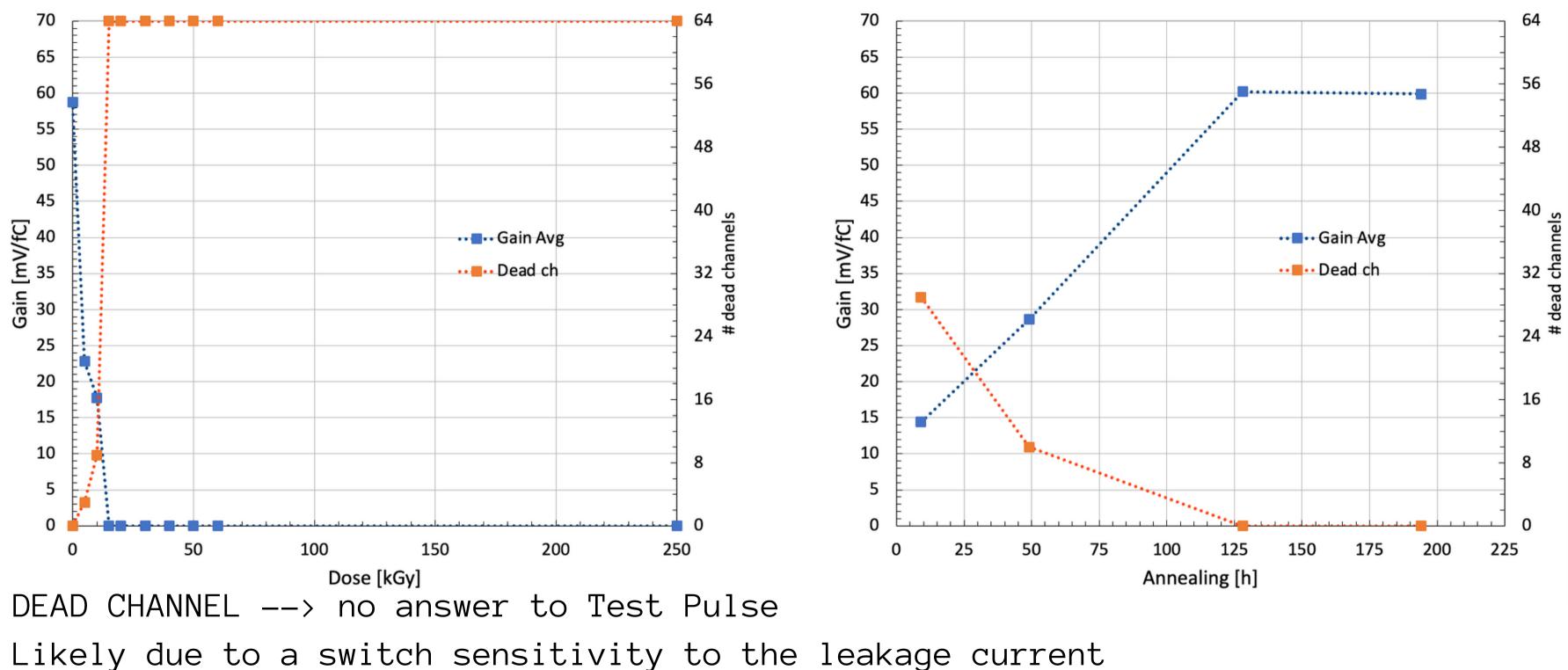

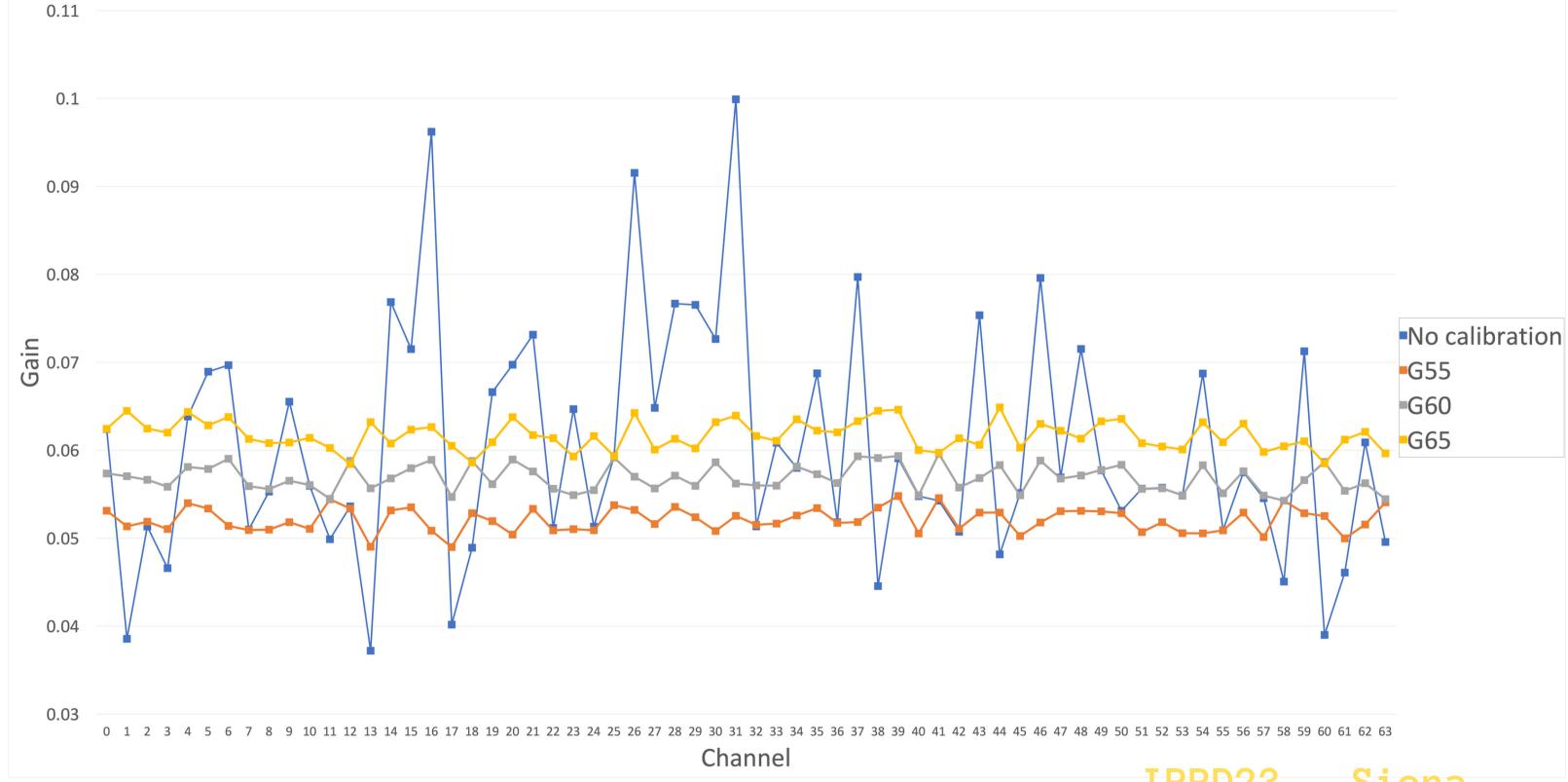

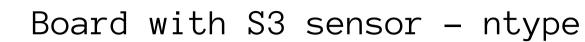

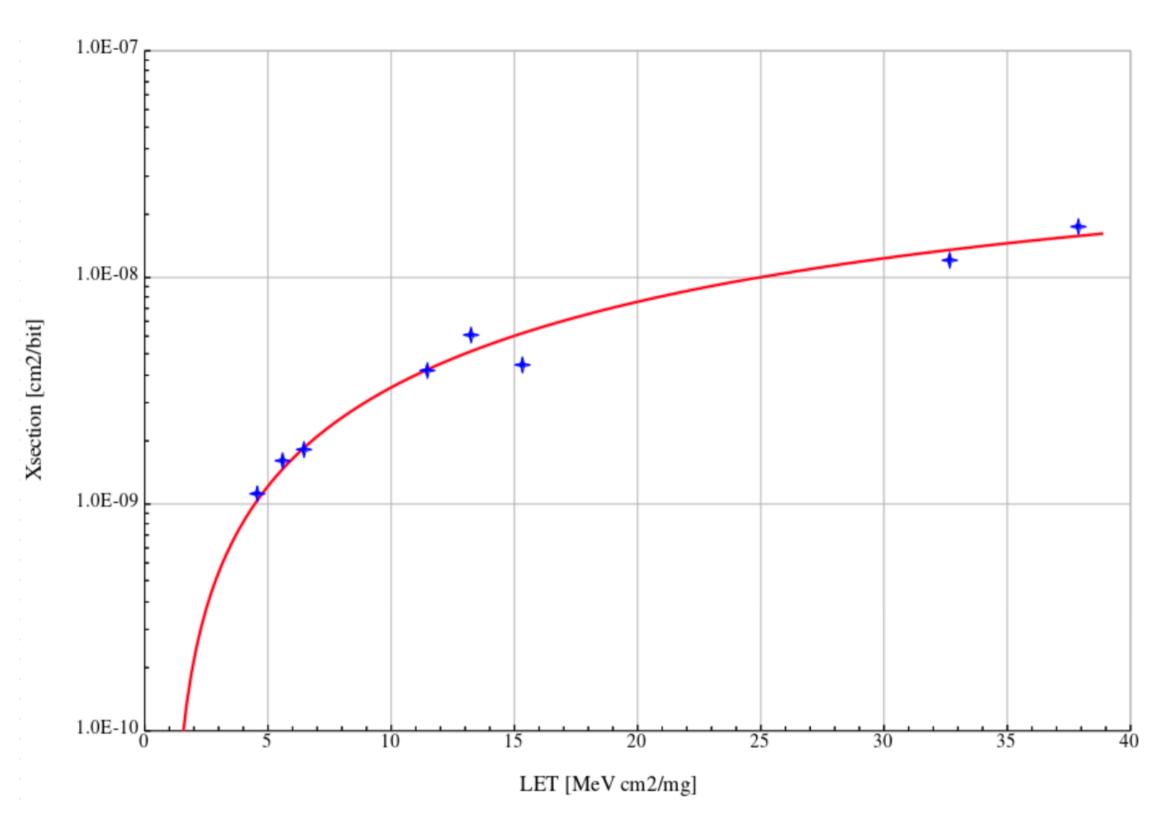

## Calibration

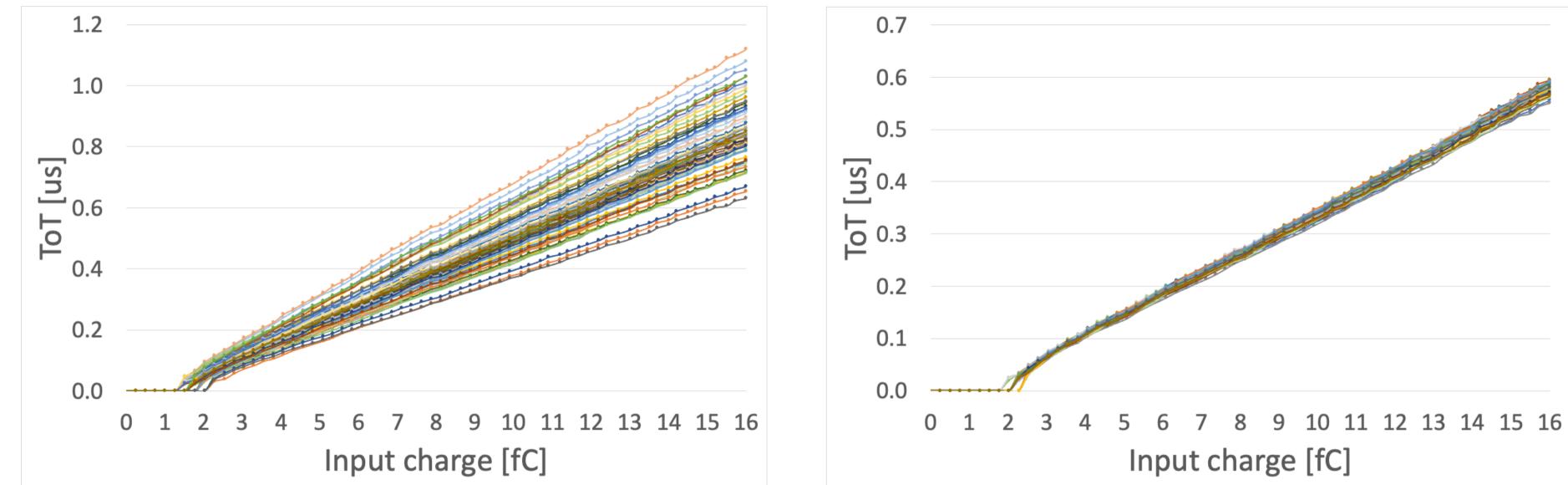

#### BEFORE CALIBRATION

- All 64 channels respond correctly to the

Gain spond for the

Test Pulse

ToT of:

- $\bullet$  ToT measured Gain 50 60 ns/fC

#### Francesca Lenta

26/09/2023

### AFTER CALIBRATION

Gain spread reduced from 11.7% to 1.5%ToT offset spread reduced from 15.6% to 3.5%

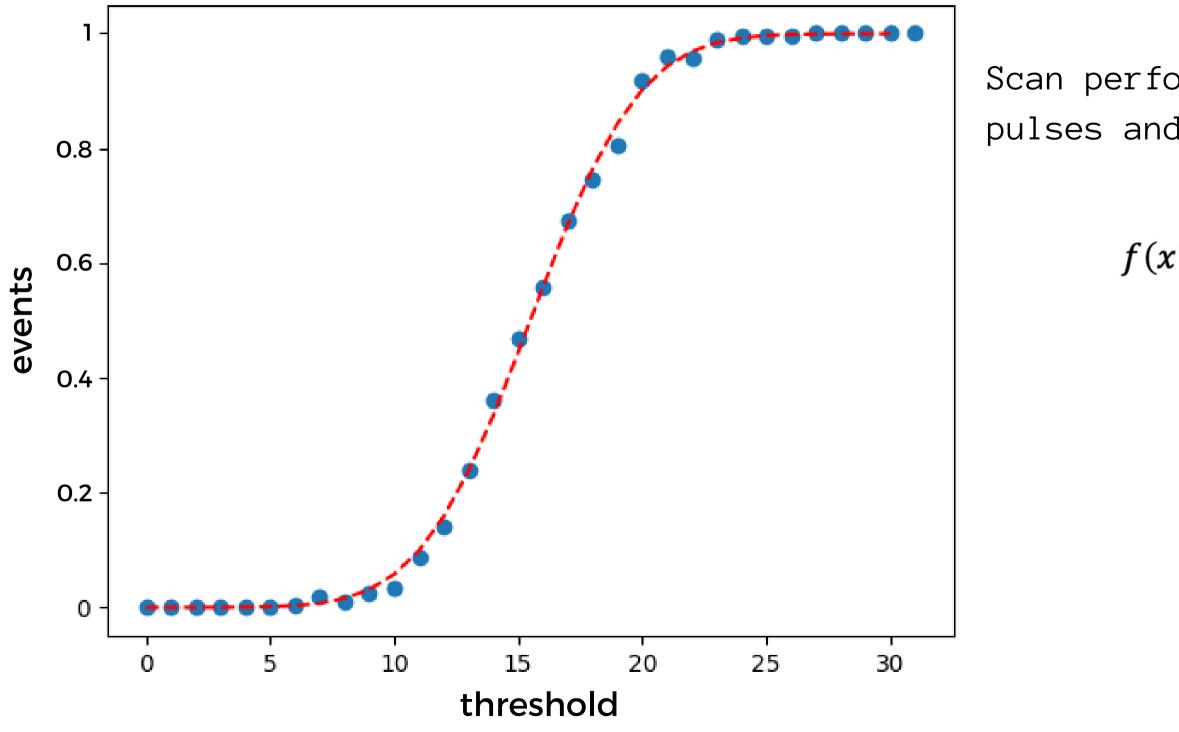

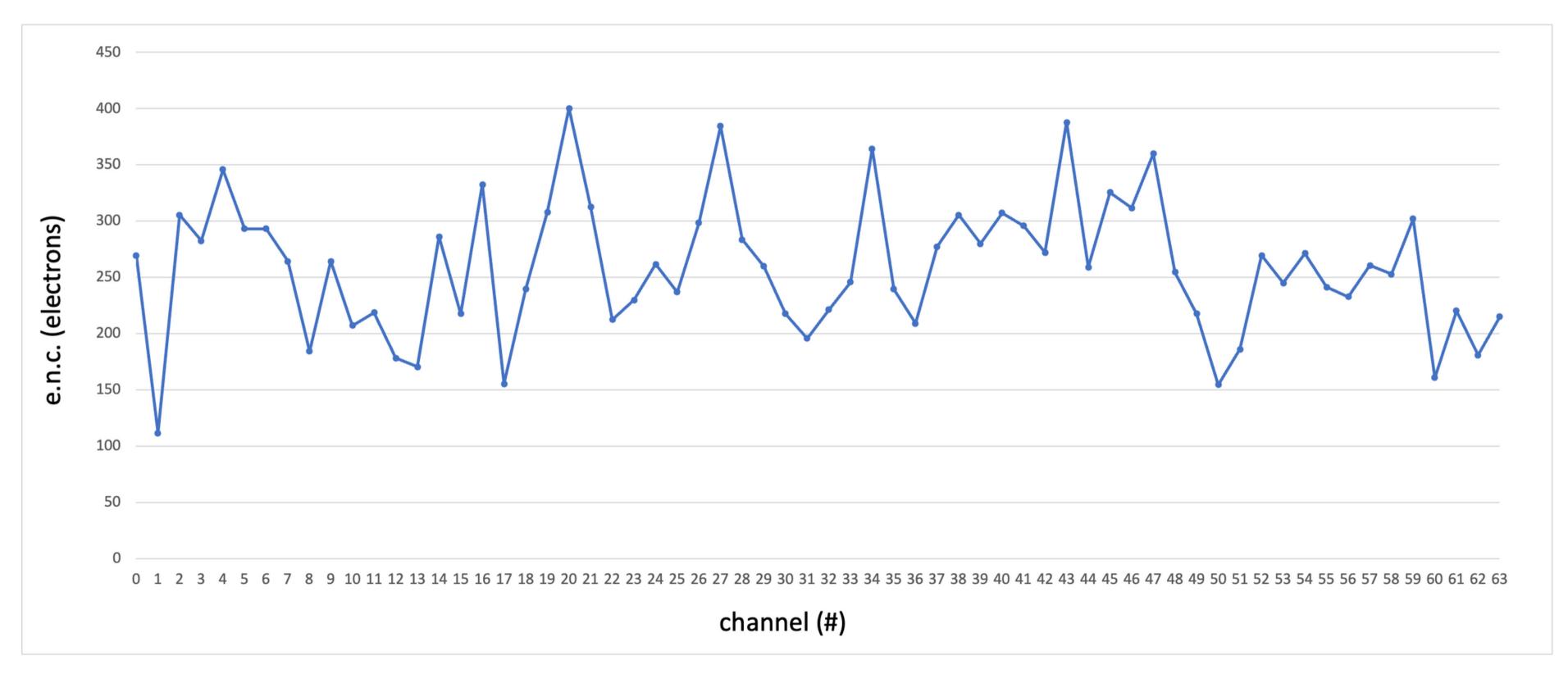

## Noise measurement

Francesca Lenta

Scan performed with a fixed number of pulses and changing the threshold

$$x') = \frac{N}{2} \left( 1 + \frac{2}{\sigma\sqrt{\pi}} \int_0^{x'} \exp(-s^2) \, dx \right)$$

$$s = \frac{x - \mu}{\sigma}$$

<sup>26/09/2023</sup>

## Noise measurement

Francesca Lenta

26/09/2023

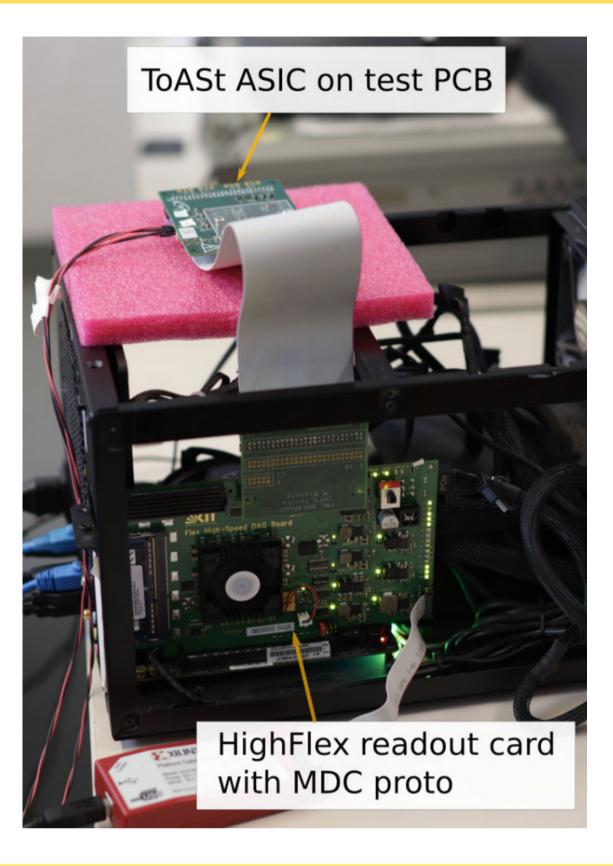

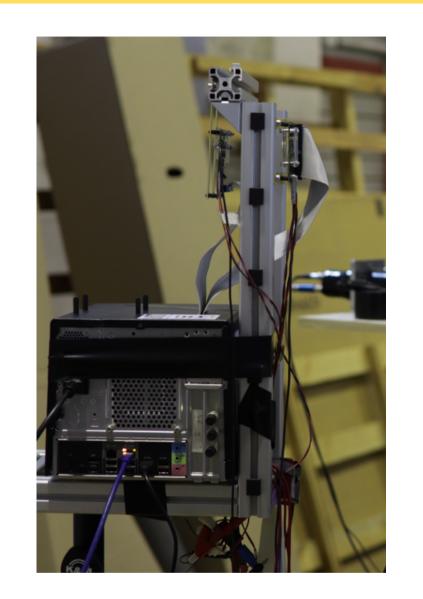

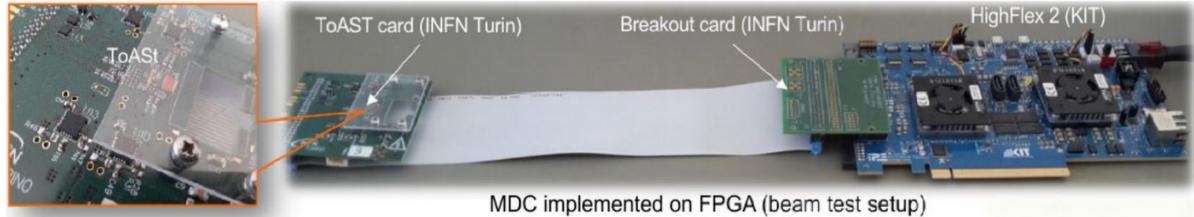

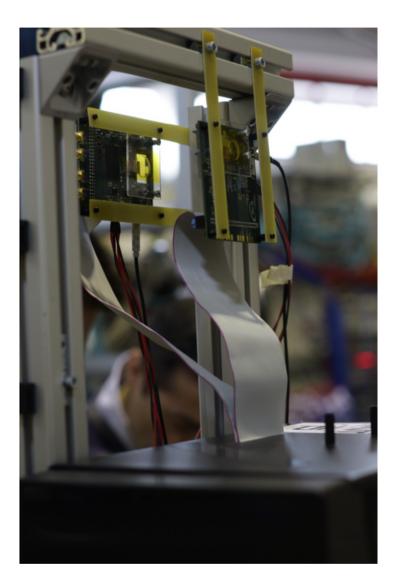

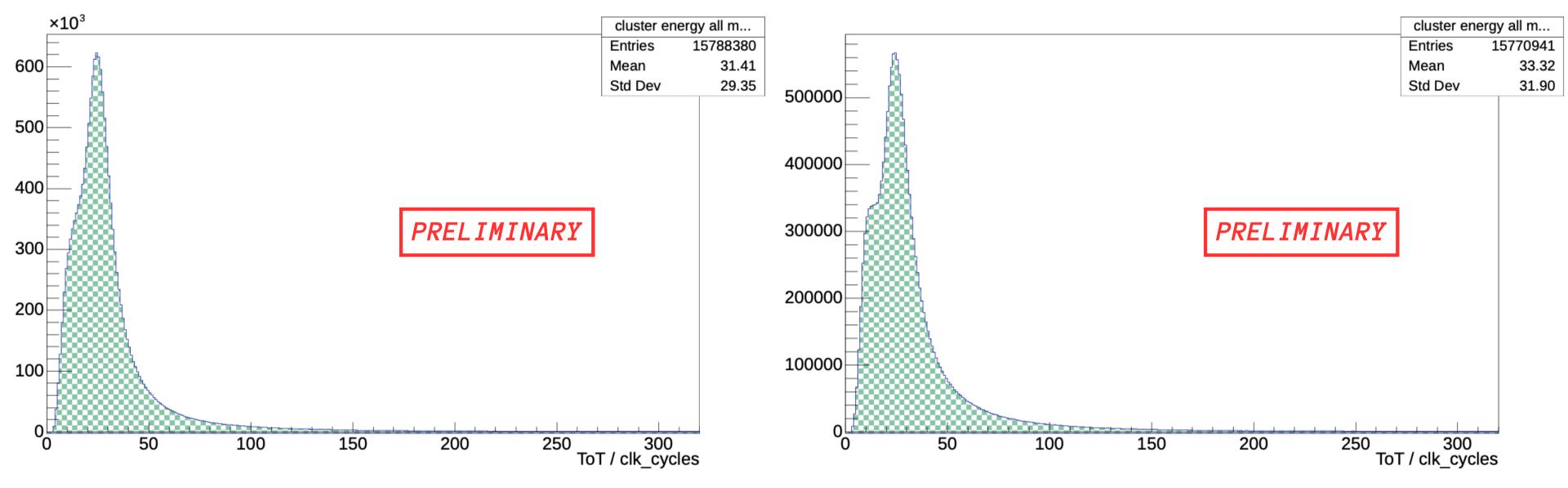

## Preliminary beam test measurement

#### 26/09/2023

#### Francesca Lenta

## Preliminary beam test measurement

## Under analysis

26/09/2023

Francesca Lenta

### ToASt 1

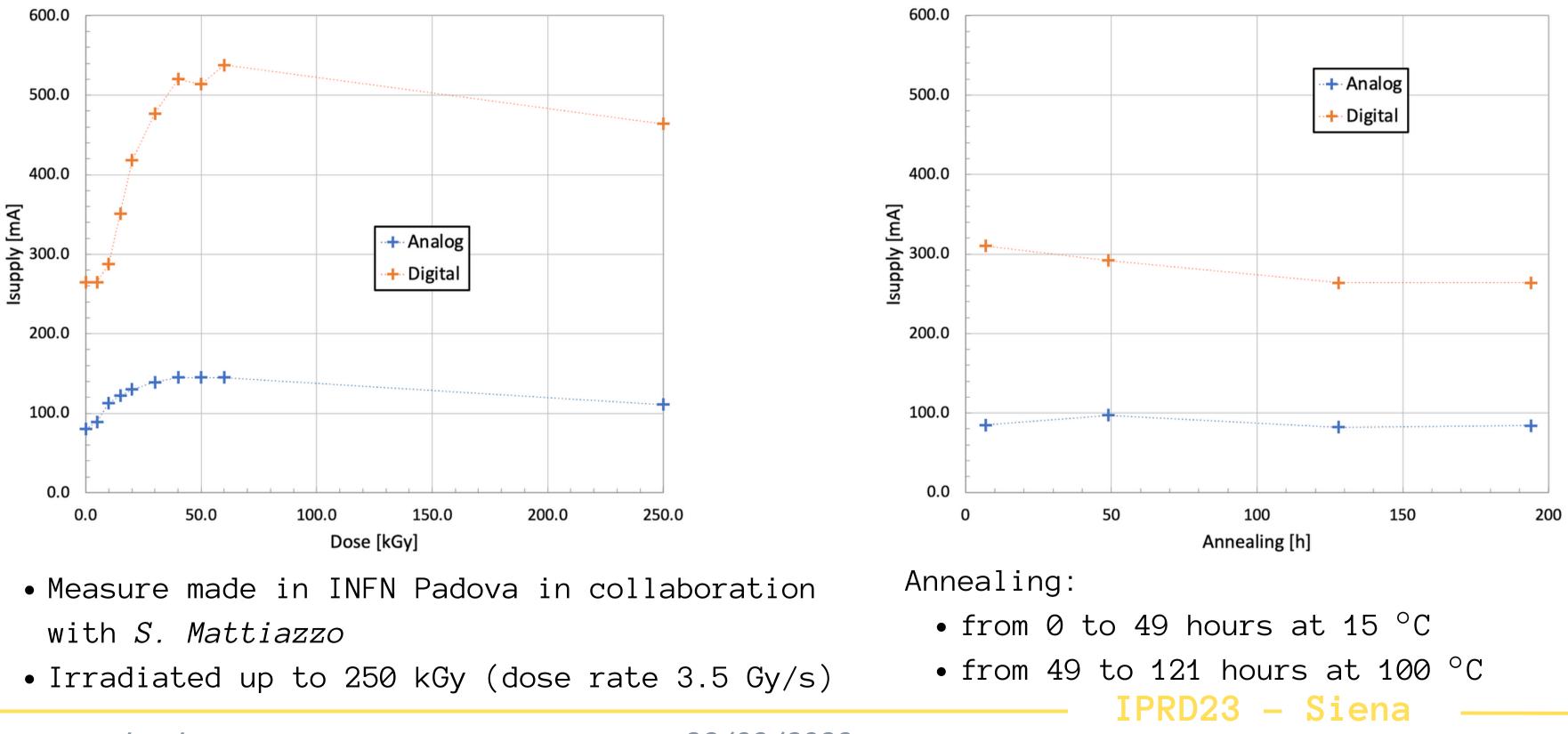

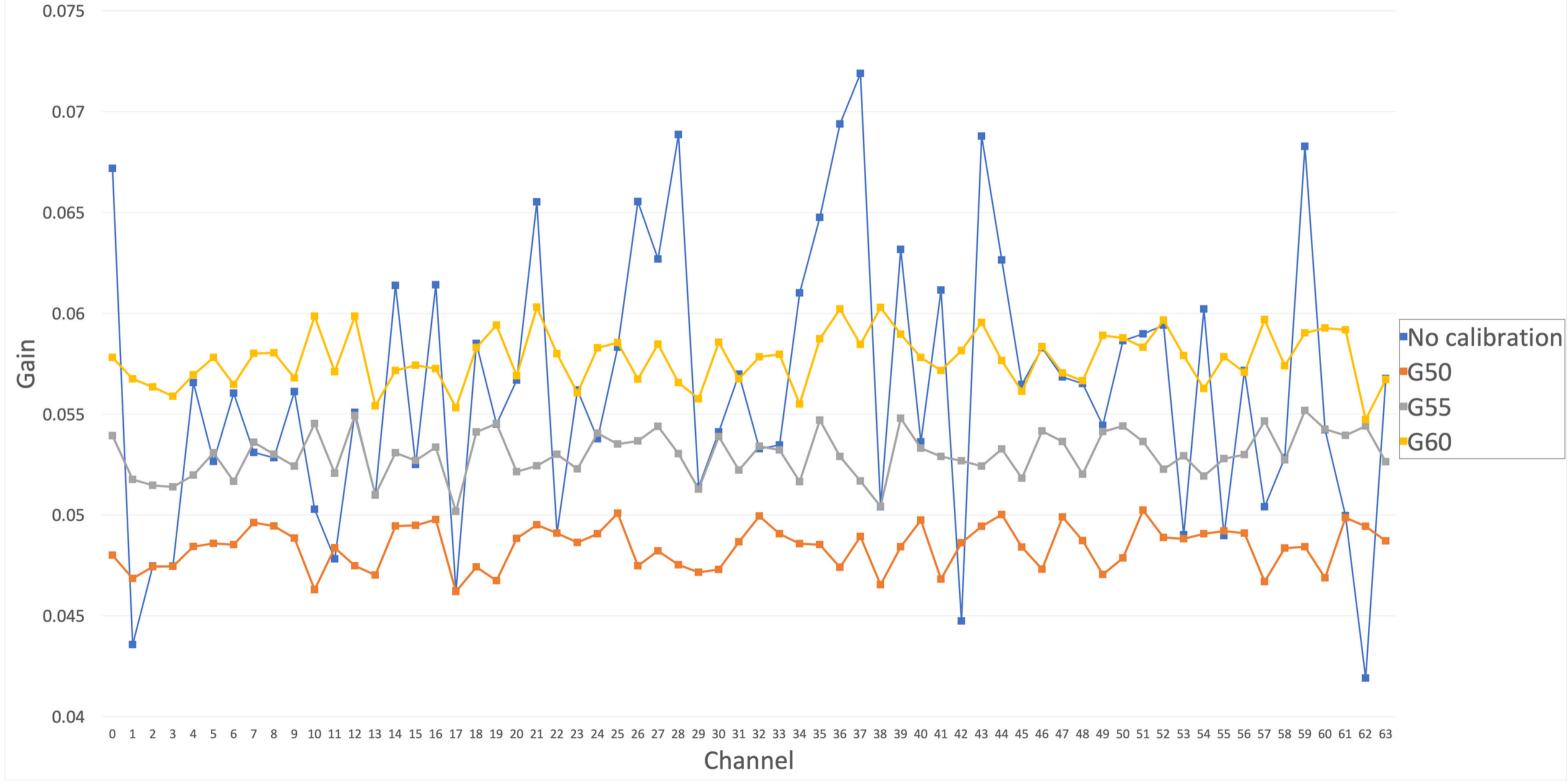

# Total Ionizing Dose tests

SUPPLY CURRENT

Francesca Lenta

26/09/2023

## Total Ionizing Dose tests

GAIN

Francesca Lenta

26/09/2023

IPRD23 - Siena

# CONCLUSION

ToASt:

- A 64 channels ASIC

- Designed for the readout of the silicon strip detectors of the PANDA MicroVertex Detector

Test:

- Performances of Gain and Noise are as expected

- Tested with detector under preliminary beam test --> results under analysis

- Test for Total Ionizing Dose is not fully satisfying --> improvement required

Future works:

- Beam test data analysis

- Next version of ToASt

# THANKS FOR THE ATTENTION

26/09/2023

Francesca Lenta

## BACKUP SLIDES

Francesca Lenta

26/09/2023

Calibration procedure:

- For each channel, measure the transfer curve for each channel ToT Ibias DAC value

- Select a reference gain

- For each channel, select the DAC value providing the gain closest to the reference

- For each channel, measure the offset of the ToT

- Select a reference offset

- For each channel, select the DAC value providing the offset closest to the reference

## Measurement - gain calibration

Board without sensor - ptype

Francesca Lenta

26/09/2023

## Measurement - gain calibration

Board without sensor - ntype

Francesca Lenta

```

26/09/2023

```

## Measurement - gain calibration

Francesca Lenta

26/09/2023

# SSDs readout requirements

| Specification       | Min               | Max        | Unit            |

|---------------------|-------------------|------------|-----------------|

| Channels per chip   | 64                |            |                 |

| ToA (pk-pk)         |                   | 6.25       | ns              |

| ToA (r.m.s.)        |                   | 1.8        | ns              |

| Charge resolution   | 8                 |            | bits            |

| Input charge        | 1                 | 40         | fC              |

| Input capacitance   | 2                 | 17         | pF              |

| Max rate per strip  |                   | 40         | kHz             |

| Noise               |                   | 1500       | e <sup>-</sup>  |

| Preamp peaking time | 50                | $\geq 100$ | ns              |

| Reference clock     |                   | 160        | MHz             |

| Power consumption   |                   | 256        | mW              |

| Radiation tolerance |                   | 20         | kGy             |

| Chip dimensions     | 4.5 × 3.5         |            | mm <sup>2</sup> |

| Pads position       | On two sides only |            |                 |

|                     |                   |            | – IPF           |

Francesca Lenta

26/09/2023

18

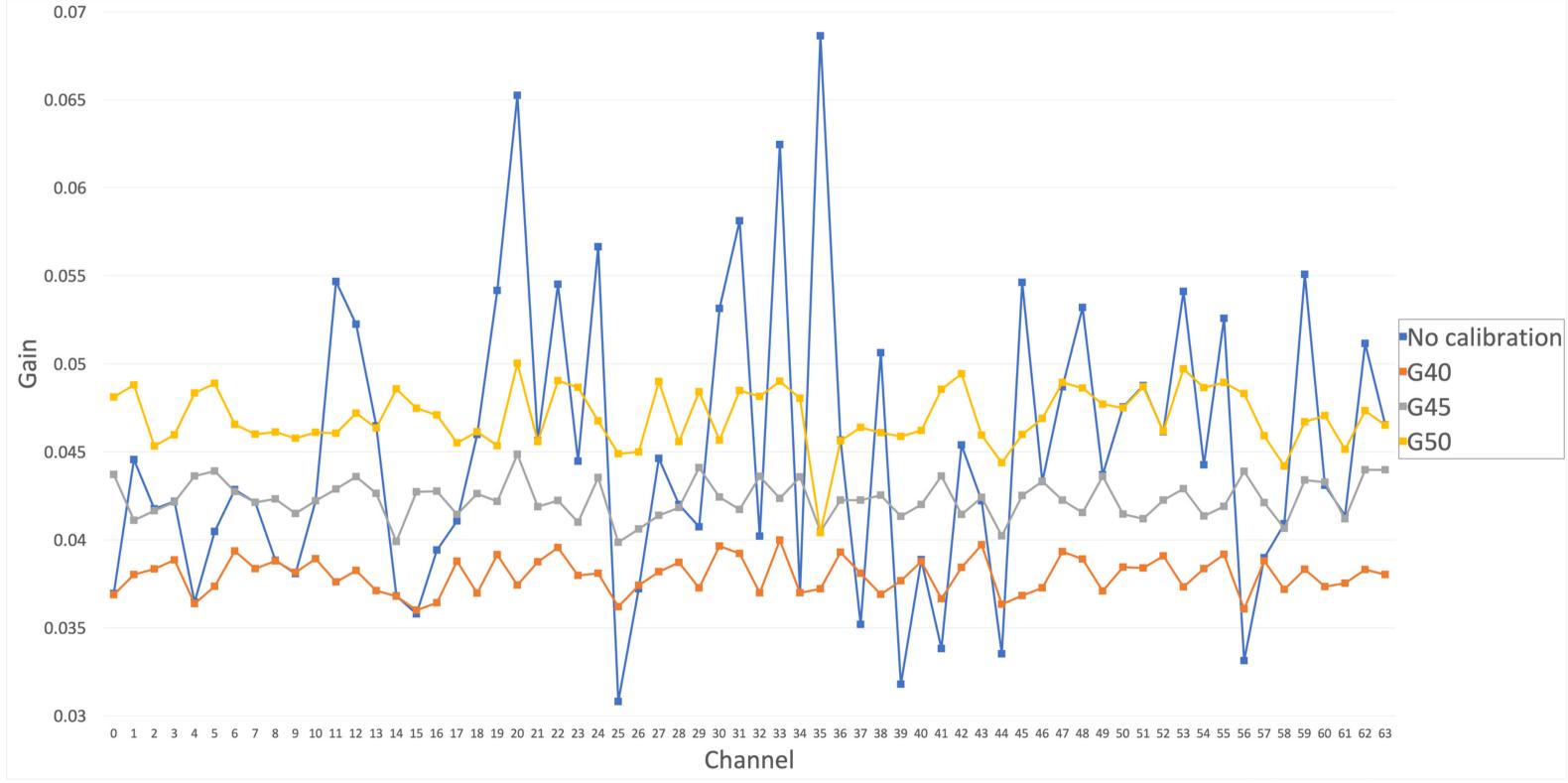

# Single Event Upset

- Test at INFN LNL SIRAD facility

- Ion fluence  $5 \cdot 10^{7}$  per ion

- Estimated cross section for 200 MeV protons :  $3 \times 10^{(-15)}$  cm<sup>2</sup>

- Hadron flux 5×10^6

hadrons/(cm^2×s) → 9.3×10^(-2)

errors/(h chip)

- Only 1→0 errors observed triplication error found in the Verilog code

IPRD23 - Siena

## ToASt channel schematic

Francesca Lenta

26/09/2023