ECFA PED study on future e+e- EW/Higgs/Top/Flavour factories ECFA WG3: Topical workshop on tracking and vertexing

# Conceptual designs and R&D challenges for vertex detectors and silicon trackers

"how the detectors in the concepts would fit within the constraints and deliver the needed performance, and what are the R&D challenges towards making the concept a reality"

⇒ Not a technology R&D overview

## A matter of priority?

I want the ideal detector, just make it!

Give me space and materials for my cables and mechanical supports. Can I add some concrete to make it stiffer?

Physicists doing physics studies

Integration experts

I can design a wonderful chip with smart pixels that can make coffee. Do you really need that resolution?

build a beam pipe with Lead. Beam background is an unvoidable collateral damage

We decided to

Chip designers

Machine detector interface experts

#### Tracking/vertexing detectors in future e<sup>+</sup>e<sup>-</sup> colliders

| Collider              | ILC       |          | CLIC     | FCCee       |                  |                                   | СЕРС          |                  |

|-----------------------|-----------|----------|----------|-------------|------------------|-----------------------------------|---------------|------------------|

| Bunch separation (ns) | 330/550   |          | 0.5      | 20/990/3000 |                  |                                   | 25/680        |                  |

| Power Pulsing         | yes       |          | yes      | no          |                  |                                   | no            |                  |

| beamstrahlung         | high      |          | high     | low         |                  |                                   | low           |                  |

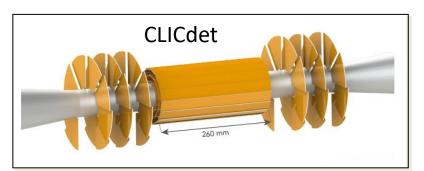

| Detector concept      | SiD       | ILC      | CLICdet  | CLD         | IDEA             | Lar                               | Baseline      | IDEA             |

| B Field (T)           | 5         | 3.5      | 4        | 2           | 2                | 2                                 | 3             | 2                |

| Vertex                | Si-Pixel  | Si-Pixel | Si-Pixel | Si-Pixel    | Si-Pixel         | Si-Pixel                          | Si-Pixel      | Si-Pixel         |

| Vertex Rmin (mm)      | 16        | 16       | 31       | 12          | 12               | 12                                | 16            | 16               |

| Tracker               | Si-strips | TPC      | Si-Pixel | Si-Pixel    | DC/Si-<br>strips | DC/Si-<br>strips or Si-<br>Pixels | TPC or Strips | DC/Si-<br>strips |

| Tracker Rmax<br>(m)   | 1.25      | 1.8      | 1.5      | 2.2         | 2.0              | 2.0                               | 1.8           | 2.1              |

| Disks layers          | 4 + 4     | 2 + 5    | 6 + 7    | 3 + 7       | 3<br>(150 mrad)  |                                   | 2+6           |                  |

(From D. Dannheim)

Large similarities between the concepts but also significant differences

rasbourg

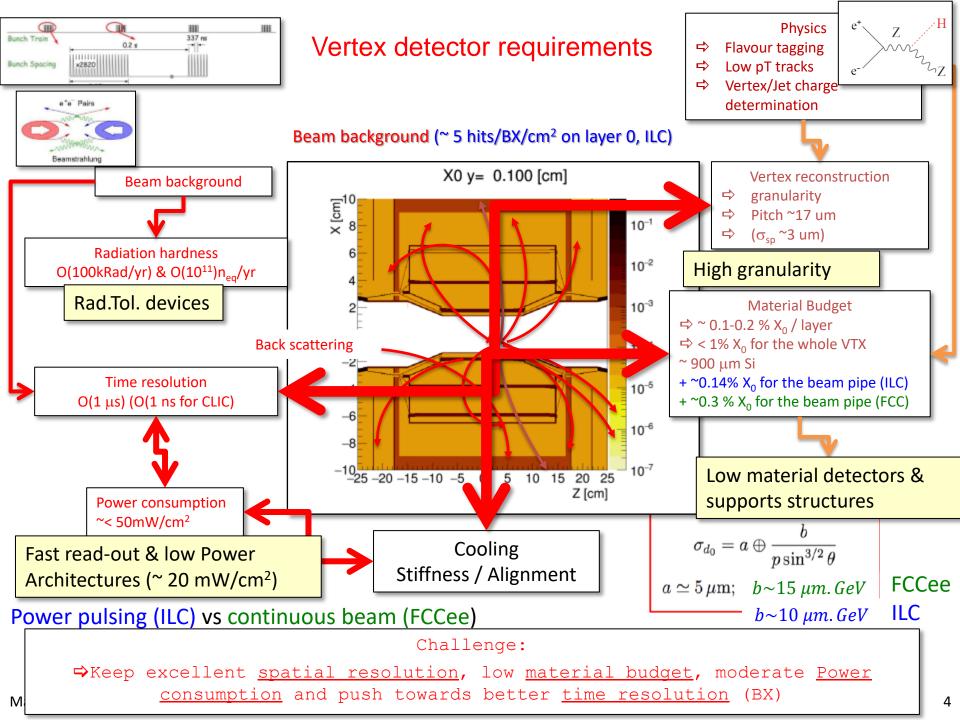

#### Tracker requirements

- Material budget vs intrinsic resolution

- ✓ Typically  $\sigma_{sp}$  ~5-10 µm/layer; material ~1-2%  $X_0$ /layer; Power ~< 100 mW/cm<sup>2</sup>

- ✓ Low momentum vs high momentum

Often, the "canonical" requirement is expressed as

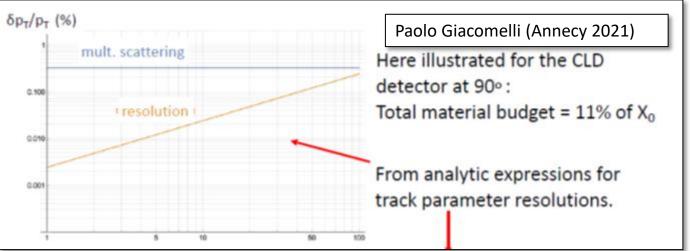

$$\sigma_{p_T}/p_T^2 \simeq 2 \times 10^{-5} \, \text{GeV}^{-1}$$

Drasal, Riegler, https://doi.org/10.1016/j.nima.2018.08.078

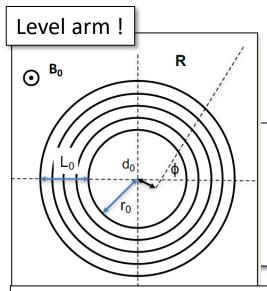

$$\frac{\Delta p_T}{p_T}|_{m.s.} \; \approx \; \frac{0.0136 \, {\rm GeV/c}}{0.3\beta \, B_0 L_0} \, \sqrt{\frac{d_{tot}}{X_0 \, \sin \theta}} \qquad \quad \frac{\Delta p_T}{p_T}|_{res.} \; \approx \quad \frac{12 \, \sigma_{r\phi} \, p_T}{0.3 \, B_0 L_0^2} \sqrt{\frac{5}{N+5}}$$

$d_{tot}/X_0 = (N+1)d/X_0$  d = layer thickness, N = # layers

m.s. term dominates for pT ~< 100 GeV/c

#### Vertex/tracking detector comments

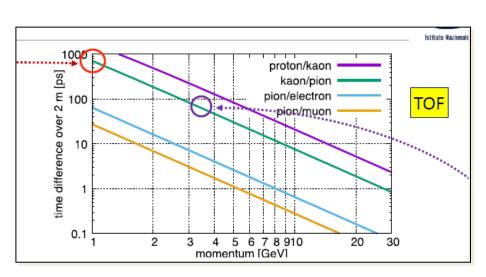

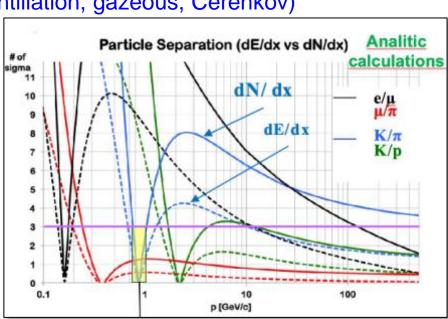

- Particle ID has to be included in the tracker concept

- √ dEdx and/or dNdx and/or fast timing

- Inner and outer radius are key factors

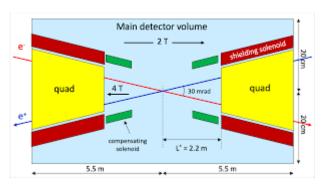

- Forward acceptance (e.g. asymmetry measurements)

- ✓ Limited by MDI constraints, beam pipe, luminosity measurements, etc.

- 30 mrad acceptance (FCCee)

- B-field

- ✓ Limited to 2 T in circular machine (@ Z-pole)

- Beam structure

- ✓ Power pulsing only for linears

- Background

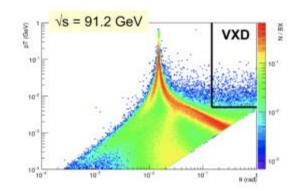

- ✓ Beamstrahlung (incoherent e+e- pairs)

- Occupancy driver for linears

- Less severe for circular (⇒Rmin reduction ~10mm))

- ✓ Synchrotron radiation (mainly circulars)

- Possible shielding (increase beampipe material budget)

- Geometry

- ✓ Probably 5-6 layers VTX (R < 60 mm)

</p>

- Robustness (standalone tracking)

- low momentum tracking

- Track seeding @ different radii

- e.g. FIPs, highly ionizining particles, LLPs, etc.

- √ « long barrel » (sticking the first measurement point to the beam pipe)

- Minimize « Rmin » w.r.t. to « short barrel+disk » approach.

- Trigger-less

## Silicon detectors

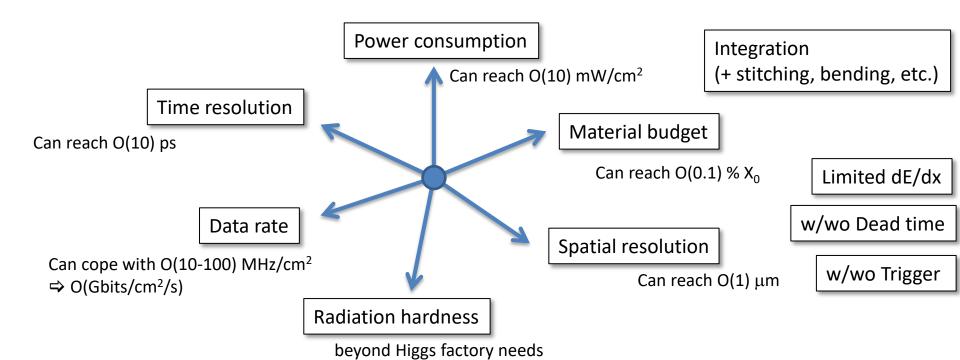

#### Silicon tracking detector figure of merit

- Ultimate performances look like the ideal tracking or vertexing detector.

However

- ✓ Very precise ⇒ not that fast

- ✓ Very fast ⇒ large pitch and/or large Power

- Need a hierarchy or specialized layers

- ✓ Governed by physics requirements and experimental conditions

- ✓ Fast timing and small granularity/low material budget are very antagonist.

- ✓ R&D needed to improve the parameter space

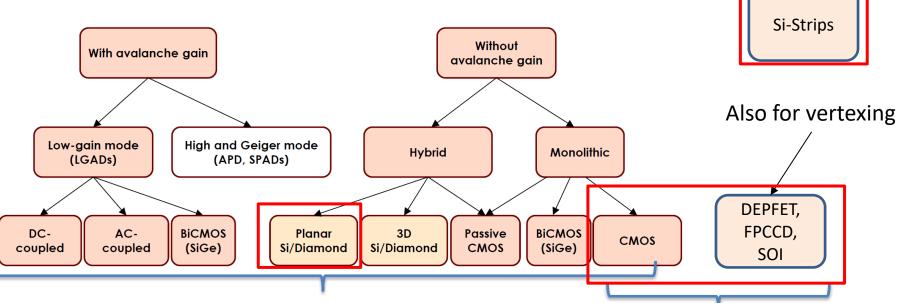

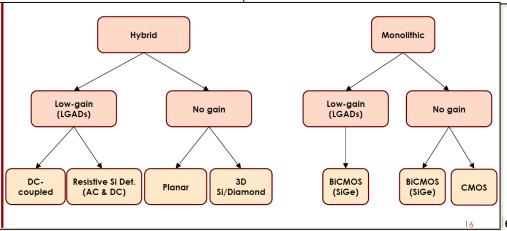

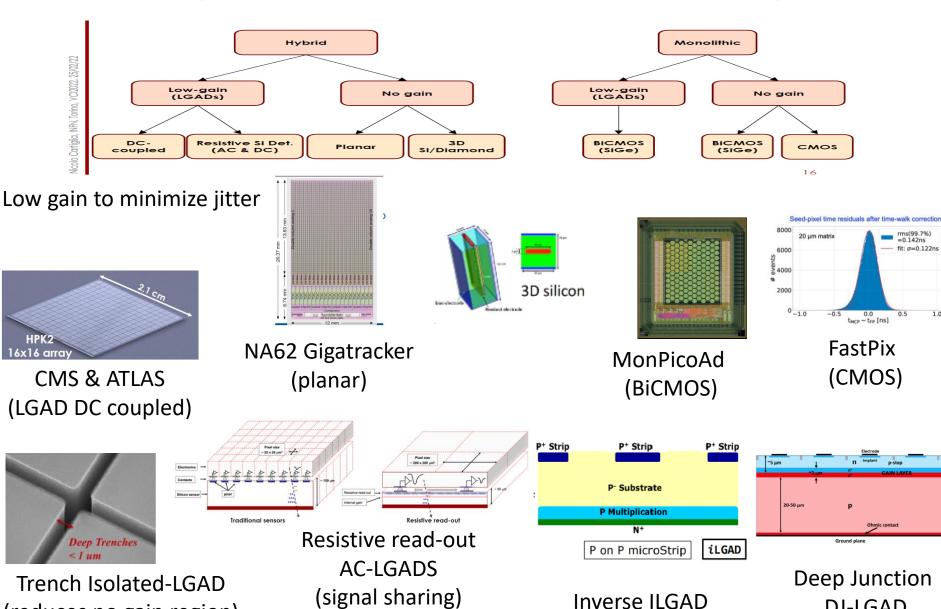

#### Silicon detectors landscape

#### A very active area. e.g. see

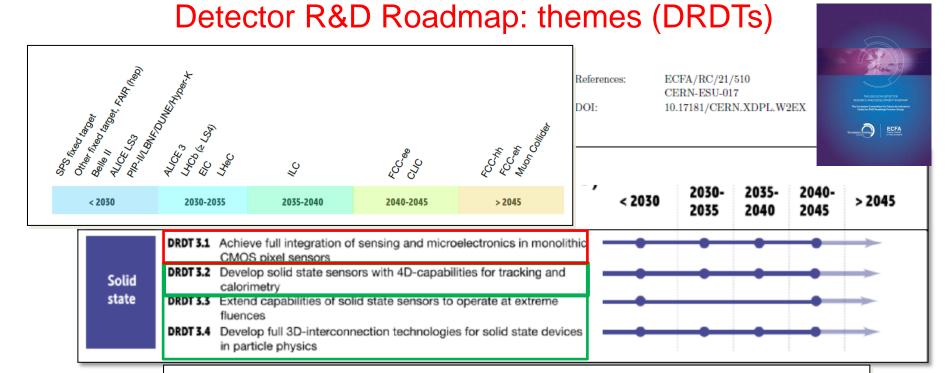

- ✓ 2021: ECFA Detector R&D Roadmap Symposium of Task Force 3 Solid State Detectors

- √ 2022: VCI 16th Vienna conference

- ✓ 2022: 15th Pisa Meeting on Advanced Detectors

- ✓ 2022: AIDAInnova Kick-off meeting

- ✓ 2022: Vertex2022

- ✓ 2022: PIXEL2022

- ✓ ALICE ITS-3 CERN Detector seminar (M. Mager)

- ✓ 2023: Implementation of TF3 Solid State Detectors

#### TF3 Symposium: Solid State Detectors

ECFA Detector R&D Roadmap

D. Bortoletto, N. Cartiglia, D. Contardo, I. Gregor, G. Kramberger, G. Pellegrini, H. Pernegger.

ECFA

European Committee for Future Accelerators

Solid state detectors for future (4D) trackers

Fast timing, radiation hardness

Granularity, low power, low material budget

Also for tracking

#### Plenty of R&Ds to follow carefully...

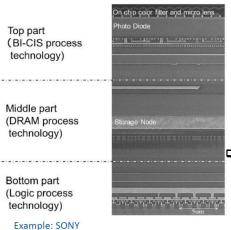

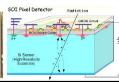

#### Wafer stacking in CMOS (quoted by W. Snoeys)

Several wafers stacked with different technologies to make a full sensor

⇒ Starts to be available in imaging tech.

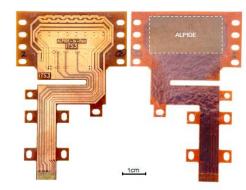

MAPS Foil: Embedded MAPS inside polymide flexible printed circuits

⇒ Provides electrical connection, protection, bending, 0.1%X<sub>0</sub>

arXiv:2205.12669v1 [physics.ins-det] 2022

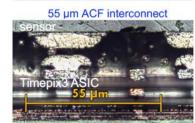

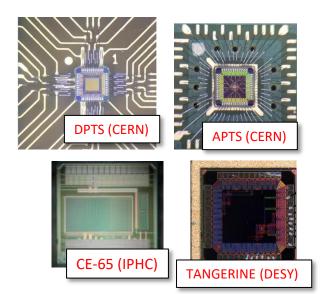

#### Huge panel of R&D and projects in CMOS

✓ Different technologies (TJ180 nm, TPSCo 65nm, LF 110 nm, etc.)

Many others: LF150, LF110, SOI, XFAB, SiGe BiCMOS, with and without gain layer, TJ180 ...

Anisotropic

Conductive

Film

Hybrid R&D

bonding

25 um bump

IVIAY 30th 2023

A.Besson, Université de Strasbol

#### An example of R&D: TPSCo 65 nm CMOS technology

- 65 nm feature size technology

- ✓ Main driver: CERN EP R&D WP 1.2 & ALICE ITS-3 upgrades

- Privileged relation between CERN with the foundry

- Added values

- ✓ Larger wafers (⇒ 30 cm)

- ✓ More functionalities inside the pixel

- ✓ Keeps pixel dimensions small ⇒ spatial res.

- ✓ Potentially faster read-out

- ✓ Lower Power consumption

- ✓ Synergy with Higgs factories requirements

- First submission: MLR1 (2020)

- ✓ Validated the technology for HEP

- 2<sup>nd</sup> Submission ER1 (2022-23)

- ✓ Dedicated to ITS3 (MOSS/MOST; stitching)

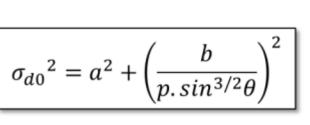

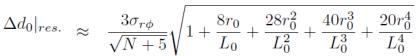

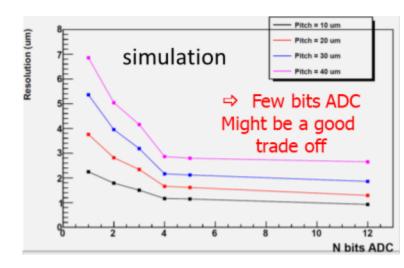

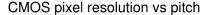

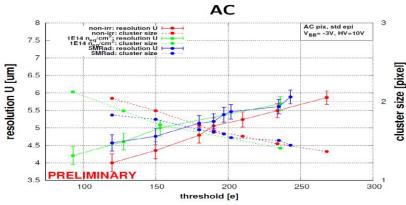

# Challenge 1: the spatial resolution

## Spatial resolution in Higgs factories

- Typical targets:

- $\checkmark~\sigma_{\text{sp}}\text{~~}3~\mu\text{m}$  for the vertex layers

- $\checkmark$   $\sigma_{sp}$ ~5-10 µm for the outer tracker layers

- Resolution in each layer depends on

- ✓ Pitch

- In conflict with the functionnalities inside the pixel

- Favored by small feature size technology

- ✓ Charge deposition

- Sensitive layer thickness

- ✓ Charge sharing (SNR vs resolution)

- Depletion:

- Staggered pixels

- ✓ Charge encoding

- Binary output / ADC / Tot / etc.

$$\Delta d_0|_{m.s.} \approx \frac{0.0136 \,\text{GeV/c}}{\beta p_T} r_0 \sqrt{\frac{d}{X_0 \sin \theta}} \sqrt{1 + \frac{1}{2} \left(\frac{r_0}{L_0}\right) + \frac{N}{4} \left(\frac{r_0}{L_0}\right)^2}$$

(assuming binary output, ~20  $\mu$ m epi.thickness & large depletion in 180nm tech.)

Level arm!

## Elongated clusters: low pT tagging

# Challenge 2: time resolution

## Timing & 4-D tracking

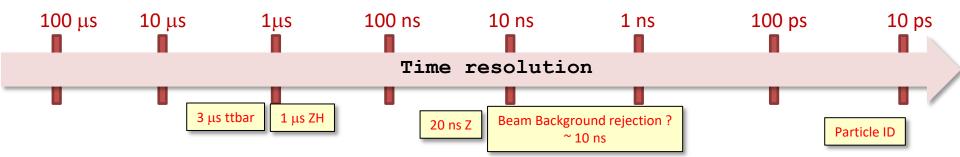

#### Time resolution ∆t

- ✓ Bunch separation (3 μs / 1 μs / 20 ns @ FCCee)

- ✓ Background rejection ? (1-10 ns range)

- √ Particle ID (10-100 ps)

#### Usual drawbacks to go faster

- ✓ Power consumption

- ✓ Active Cooling & geometrical acceptance due to services

- ✓ In pixel circuitry ⇒ larger pixels (or multipixels)

- ✓ Fill factor, dead time

- ✓ PID Restricted to low momentum particles (~< few GeV/c)

</p>

#### Still

- ✓ Forward region not covered by a central gazeous detector.

- ✓ Added value for intermediate radii (e.g. LLPs ?)

## Power vs fast timing vs pixel size

Brief considerations about electronics: power

|  | Name       | Sensor             | node     | Pixel size                | Temporal precision [ps] | Power [W/cm²]                   |

|--|------------|--------------------|----------|---------------------------|-------------------------|---------------------------------|

|  | ETROC      | LGAD               | 65       | 1.3 x 1.3 mm <sup>2</sup> | ~ 40                    | 0.3                             |

|  | ALTIROC    | LGAD               | 130      | 1.3 x 1.3 mm <sup>2</sup> | ~ 40                    | 0.4                             |

|  | TDCpic     | PiN                | 130      | 300 x 300 μm²             | ~ 120                   | 0.45 (matrix) +<br>2 (periphery |

|  | TIMEPIX4   | PIN, 3D            | 65       | 55 x 55 μm²               | ~ 200                   | 8.0                             |

|  | TimeSpot1  | 3D                 | 28       | 55 x 55 μm²               | ~ 30 ps                 | 5-10                            |

|  | FASTPIX    | monolithic         | 180      | 20 x 20 μm²               | ~ 130                   | 40                              |

|  | miniCACTUS | monolithic         | 150      | 0.5 x 1 mm <sup>2</sup>   | ~ 90                    | 0.15 - 0.3                      |

|  | MonPicoAD  | monolithic         | 130 SiGe | 25 x 25 μm²               | ~ 36                    | 40                              |

|  | Monolith   | LGAD<br>monolithic | 130 SiGe | 25 x 25 μm²               | ~ 25                    | 40                              |

Nicolo Cartiglia, INFN, Torino, VCI2022, 25/02/22

Price to pay: additionnal cooling system (additionnal material)

e Strasbourg

#### Fast timing

- Extremely active domain

- ✓ Interest to push beyond 10 ps resolution

- PID not discussed here (covered by TF4)

- √ dE/dX; dN<sub>cl</sub>/dx and timing for PID

- ✓ Fast timing not proper to silicon (also scintillation, gazeous, Cerenkov)

- Specialized layers

- ✓ Doesn't compromise the other requirements (material budget and granularity)

- Probably not in the most inner layers

- ✓ Dedicated studies needed for design optimization

#### Timing Landscape in semi-conductor technologies

See e.g. ECFA-TF4 Time of flight technologies (R. Forty)

(reduces no gain region)

**DJ-LGAD**

# Challenge 3: material budget

#### Material budget: starting from the layers

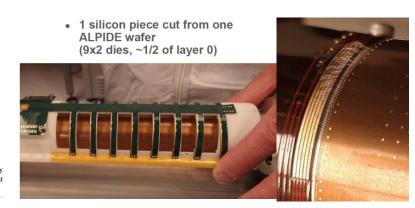

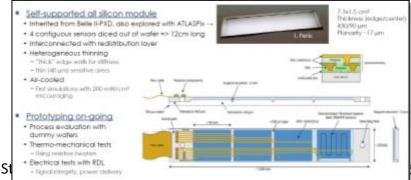

Pseudo stitching+ bent sensors(superALPIDE)

1 silicon piece cut from one ALPIDE wafer (9x2 dies, ~1/2 of layer 0)

Double sided layers

PLUME

(Bristol, DESY, IPHC)

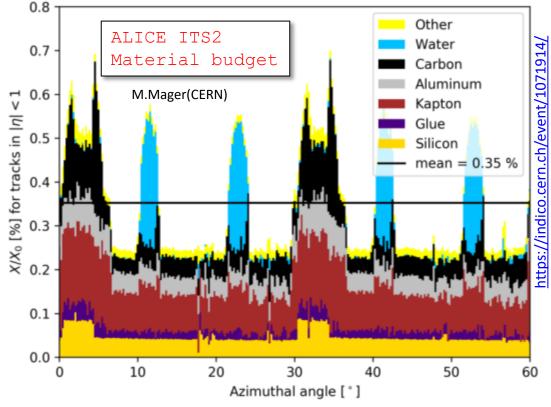

Double sided ladders with minimized material budget 0.35%  $X_0$  reached  $\Rightarrow$  ~0.3  $X_0$  doable (with air flow cooling)

Layers 2+1

+ bent sensors

ALICE-ITS3

Self supported silicon (Belle-2 upgrade)

I. Peric

Inputs for engineering studies

spatial resolution

7.1x1.5 cm2

430/90 µm Planarity ~17 µm

Thickness (edge/center)

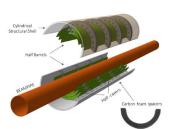

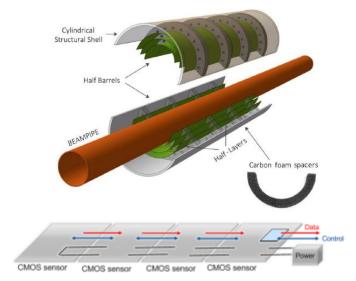

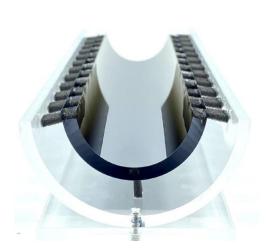

## ALICE ITS3: Bent sensors & stitching

- ALICE-ITS3/CERN drives the R&D on Stitching + bent sensors:

- ✓ Sensor part ~15% of total material budget

- ✓ Sensors thinned down to 50 μm

- Minimizing overlapping regions,

minimizing minimal radius around the beam pipe

- Challenges and caveats (for e+e- colliders)

- ✓ Mechanics? Bonding? Air cooling only?

- ✓ Design: Minimizing peripheral circuits (Fill factor ~90%)

- ✓ Bent sensor performances ? Yield

- $\Rightarrow$  design rules constraints the minimal pitch (~22 µm)

- ✓ ITS-3 do not have disk (chip periphery adds Z position constraint)

- ✓ Approach validated in a limited radius range (R> 18mm)

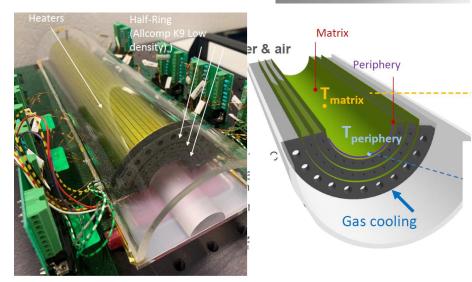

## **ALICE ITS3 tests**

0.033 W/m·K

#### Layers 2+1

#### Carbon fiber foam spacer

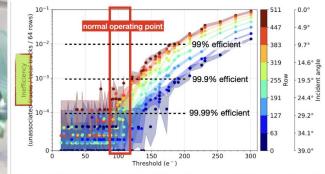

Fig. 10: Inefficiency as a function of threshold for different rows and incident angles with partially logarithmic scale  $(10^{-1} \text{ to } 10^{-5})$  to show fully efficient rows. Each data point corresponds to at least 8k tracks.

Bent sensors in test beam

Integation and cooling studies

Inteconnexion tests (superALPIDE)

On going experiments pave the road for Higgs factory detectors (many other examples)

# Challenge 4: Time scale

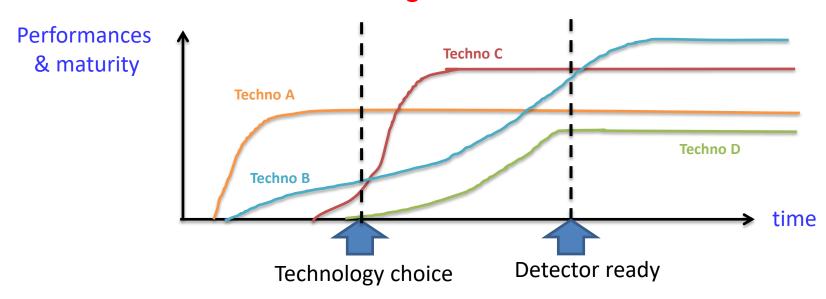

#### Challenge: the time scale

- Vertex detectors are small and relatively fast to build

- √ ~ 4-5 years projects

- Complete Silicon trackers need more time

- Avoid the Never Ending R&D syndrom

- Do not be too conservative

- Right balance to find between

- ✓ Exploring technologies

- √ Focusing on the most promising ones

- Mid-term applications provides invaluable milestones

- ✓ CBM, ALICE ITS-3, Belle-2 upgrade, LHCb, EIC, etc.

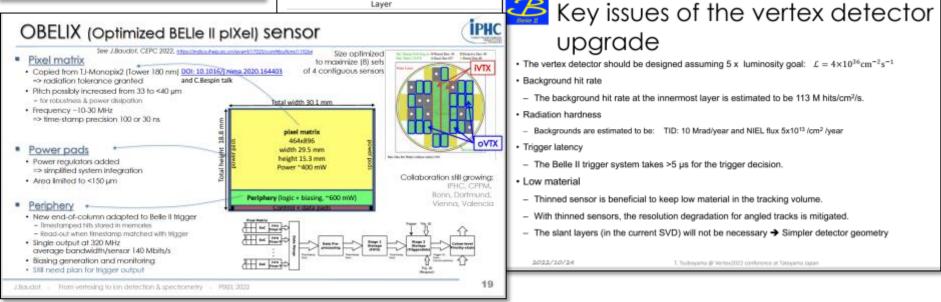

- ✓ e.g. OBELIX for Belle-2 inherited from TJ-Monopix-2

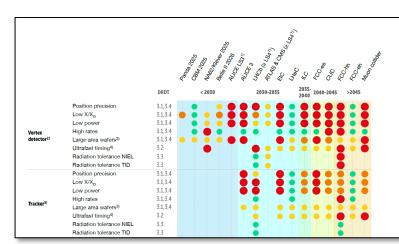

Must happen or main physics goals cannot be met 🔵 Important to meet several physics goals 🔵 Desirable to enhance physics reach 🔵 R&D needs being met

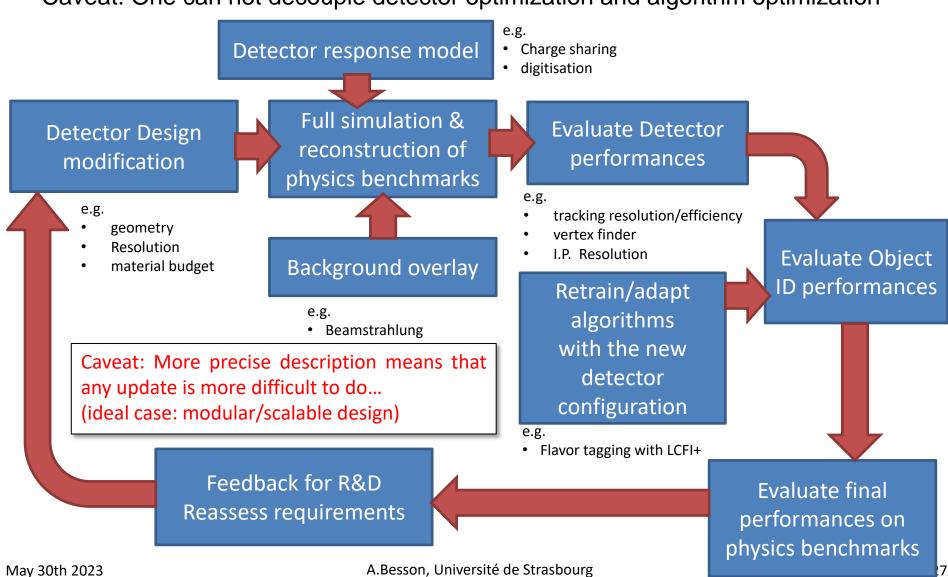

# Challenge 5: Detector optimization and simulations

### Challenge: optimization of the detector

- Example: Shall we target 18 or 22 μm pitch?

- Caveat: One can not decouple detector optimization and algorithm optimization

#### Optimization of the detector: pragmatic approach

- One does not need to target the best performances from the beginning

- Added value of mockups / demonstrators / engineering designs

- ✓ Relatively cheap but realistic enough

- ✓ Study conflicting requirements (material, cooling, services, mechanics, etc.)

- ✓ Check issues difficult to anticipate (e.g. available space for services, etc.)

- ✓ Reinforce the cooperation between different expertises (e.g. chip design/mechanics/DAQ)

- ✓ Integrated test beams possible

- ⇒ DRDs should be the place to do it!

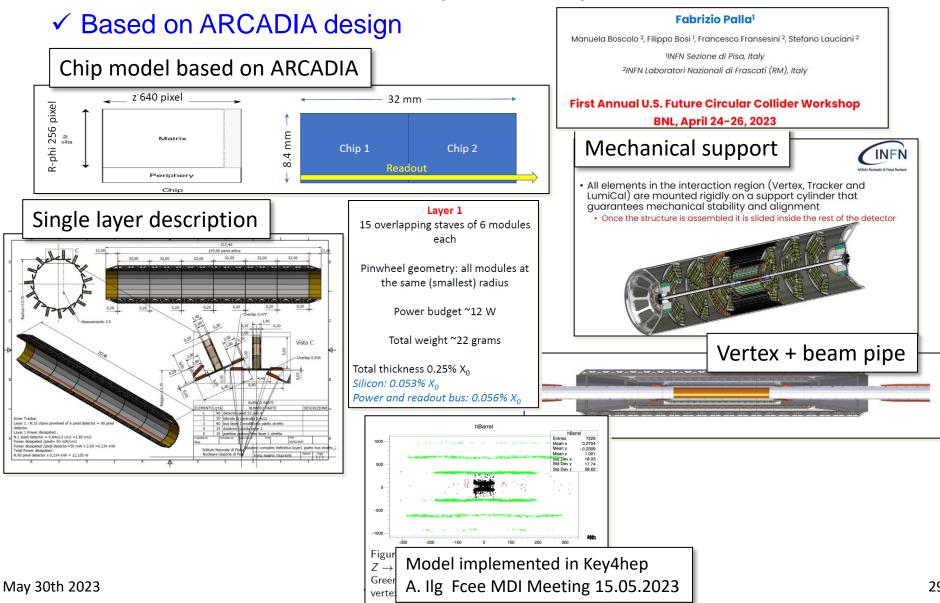

#### A pragmatic approach: mechanical/simulation studies for the IDEA vertex detector

Starts from a detector concept and chip modules

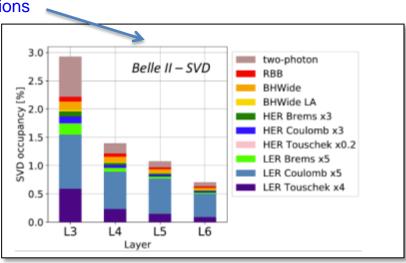

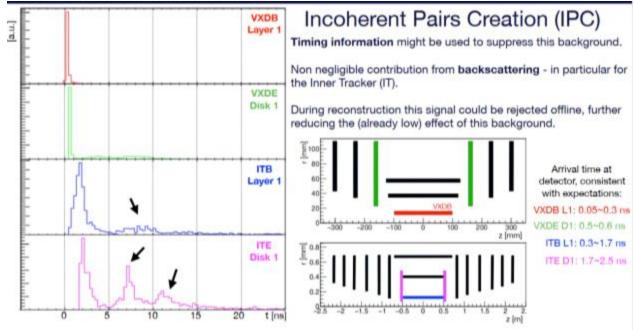

# Challenge 6: understanding beam related background

#### Challenge: understand beam related backgrounds

- Sources:

- ✓ Incoherent pairs (« beamstrahlung »)

- ✓ Synchrotron

- ✓ Beam loss (circular machines)

- Radiative bhabha

- ✓ Beam gas, etc.

- Usually one considers that occupancy ~< 10<sup>-2</sup>-10<sup>-3</sup> is safe for tracking/vertexing purposes

- Experience from ILC studies over 20 years

- ✓ Any modification in the Interaction region (beam scheme, beam pipe design, B field) might bring surprises

- ✓ One should not consider that a 10<sup>-4</sup> occupancy estimation means that there is no issue.

- The robustness is questionnable

- Large possible variations in some acceptance corners (asymmetries in φ or z)

- Safety factor absolutely mandatory

- 2 independant simulation tools would be welcome (GuineaPig, Fluka, etc.)

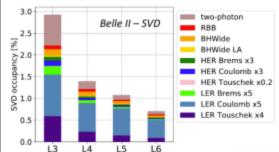

- Experience from Belle-2

- ✓ Discrepancies observed between simulations and first collisions

- Direct beam background vs backscattered background

- ✓ Generally the backscattered ones are more sensitive to any MDI change.

- What about timing information to reject background?

- ✓ Need ~ 5 ns to reject backscattered particles

- ✓ Is it worth paying the price in terms of additionnal power?

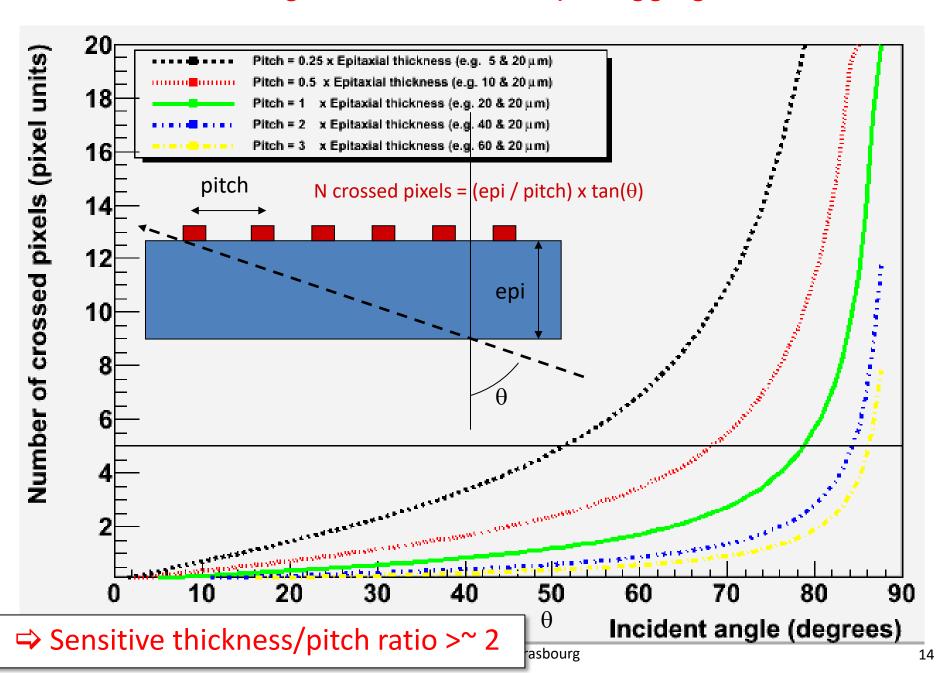

- What about cluster shape to reject background?

- ✓ Need very good sensitive thickness/pitch ratio (> 2).

- ✓ Charge information helps.

- ✓ (you actually reject very low pT particles)

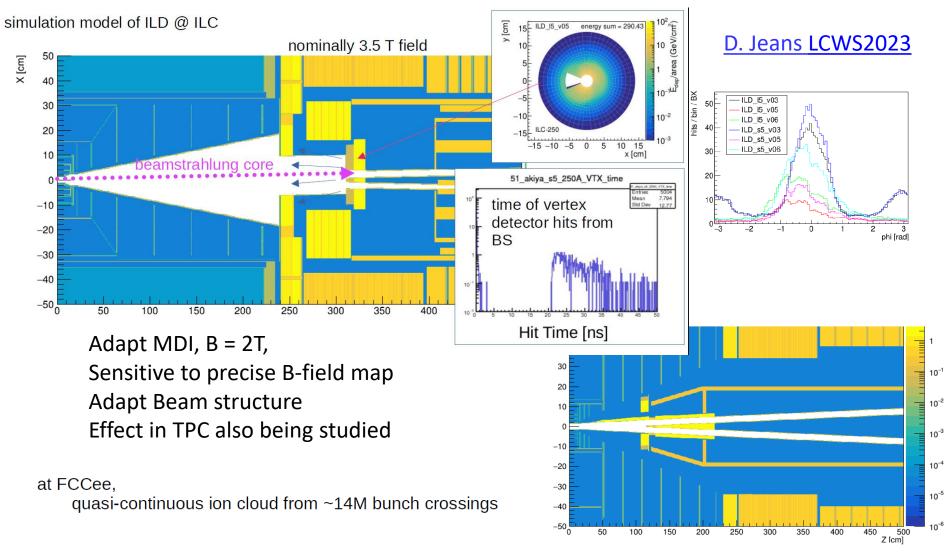

## Example of background study: ILD, from linear to circular

- at FCCee, MDI extends to ~1m from IP

- → 6 times more beamstrahlung background hits in TPC

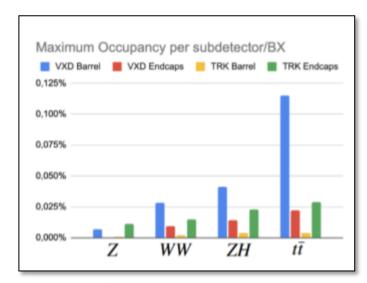

## Example of study in CLD

|                    | Z       | ww      | ZH       | Тор     |

|--------------------|---------|---------|----------|---------|

| Bunch spacing [ns] | 30      | 345     | 1225     | 7598    |

| Max VXD occ. 1us   | 2.33e-3 | 0.81e-3 | 0.047e-3 | 0.18e-3 |

| Max VXD occ.10us   | 23.3e-3 | 8.12e-3 | 3.34e-3  | 1.51e-3 |

| Max TRK occ. 1us   | 3.66e-3 | 0.43e-3 | 0.12e-3  | 0.13e-3 |

| Max TRK occ.10us   | 36.6e-3 | 4.35e-3 | 1.88e-3  | 0.38e-6 |

US FCC workshop 25/04/2023 Ciarma

BX rate might be an issue at the Z-pole

Timing resolution range to reject background ~ 1 ns

May 30th 2023 A.Besson, Université de Strasbourg 33

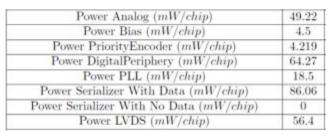

# Challenge 7: The Power

#### Power challenges

- Power is in conflict with all other parameters

- Baseline:

- ✓ Air flow cooling only to minimize material budget

- ✓ Up to ~ 20 mW/cm²

- what is the limit? ~50 mW/cm² or even more?

- Driving parameters:

- ✓ # channels, Time resolution / data flux

- ✓ Surface (VXD ~ 3500 cm²; tracker O(10 m²)

- ✓ Power Pulsing (ILC/CLIC) ⇒ Constraints more relaxed w.r.t. FCCee

- The « Power paradox »

- ✓ Small radius ⇒ Higher hit density and Power/cm² but small fraction of total power

- ✓ Higher radius ⇒ less hit density but higher total power/layer

- Power sharing

- ✓ Analog part: O(25-50%) ⇒ density of pixels, charge collection speed

- ✓ Digital part: O(25-50%) ⇒ data flux, freq.

- ✓ Output→DAQ: maximum flux. (25%)

- Architecture optimization is important

- ✓ Priority encoder (limited by flux)

- ✓ Asynchronous might be adapted (tot, etc.)

- ✓ Etc.

- Technology feature size

- ✓ e.g. 180nm to 65 nm: ~50% Power reduction

- Air extraction:

- ✓ In conflict with disks and forward acceptance

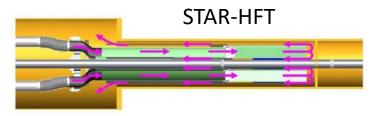

- (≠ALICE ITS2/3, Belle-2, STAR-HFT)

MIMOSIS like architecture, 180 nm

# Challenge 8: Chip design

# Design challenges: From new ideas to real chips

- How to really make it?

- ✓ R&D prototypes ≠ final production chip installed in real experiment

- ✓ Submission cost issue for R&D

- Trade-off between new (expensive) technologies and older (cheaper) technologies

- The complexity is growing

- ✓ New read-out architecture, etc.

- ✓ Work flow inspired from successfull chips installed in experiments (e.g. ALPIDE for ALICE-ITS2)

- push to concentrate on few technologies

- ✓ Verification tools are absolutely crucial

- « Digital on top »

- Global support on tools DRD3/ DRD7 connexion!

- Connexion with foundries absolutely crucial

- ✓ Contracts, confidentiality, etc.

- ✓ Long term plans to maintain interest from fourndries (HEP is a small player)

- ✓ Access to technology options to optimize it for HEP applications

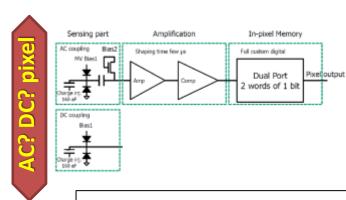

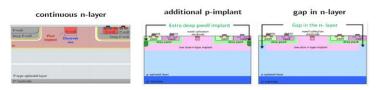

### Example: MIMOSIS (CBM-MVD) & Decision on options for sensing elements

#### **Process modification: Standard? P-stop? N-Gap?**

$$\sigma = 4 - 5 \,\mu\text{m}$$

> 3 x 10<sup>13</sup>n<sub>eq</sub>/cm<sup>2</sup>

Spatial resolution Rad. hardness

$\sigma = 5 - 7 \,\mu\text{m}$ > 30 x 10<sup>13</sup>n<sub>eq</sub>/cm<sup>2</sup>

Process options inherited from ALPIDE

- Better spatial res. at given rad. tolerance?

- Higher S/N => Robustness to external noise?

- Nuclear fragment ID by dE/dx?

- DC pixel limited rad. hardness.

- AC Pixel more biasing lines.

W. Snoeys et al., NIM-A Vol.871 (2017) 90–96. Munker, Vertex 2018, Status of silicon detector R&D at CLIC

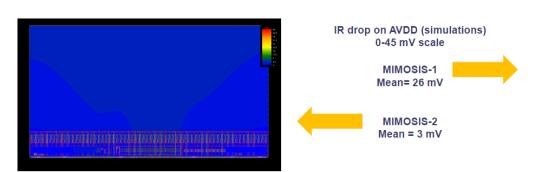

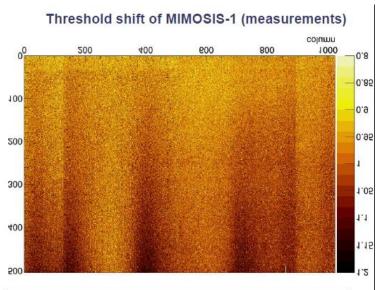

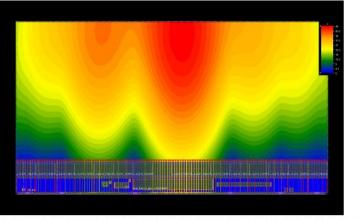

# Mimosis-1 Verification tools example

- Large and complex designs need

- ✓ A hierarchy in the work flow to keep submission on schedule

- ✓ Verification tools that can be run in a reasonnable time

- ✓ Knowledge of these tools is crucial

- Example Power-grid problem observed in MIMOSIS-1

- ✓ Threshold shifts

- ✓ Problem fixed quickly

#### F. Morel DRD7 kick-off meeting

# **Summary**

- Apologies for not covering

- ✓ Many technologies and on going R&D

- (FPCCD, SOI, DEPFET, BiCMOS (SiGe), etc.

- ✓ Cooling R&D (MCC, etc.)

- ✓ Read-out

- ✓ Operation and monitoring (Built-in Self Test (BIST) approach ?)

- ✓ Alignment

- The physics requirements impose a hierarchy between the conflicting parameters

- ✓ Granularity and material budget first!

- ✓ CMOS/MAPS Pixel sensors offer the best compromise for the inner vertexing/tracking layers.

- ✓ Specialized timing layers

- Integration R&D is a final performances driver!

- ✓ Fill the gap between nice ideas and real detectors

- e.g. Stitching & bent sensors developed in ALICE-ITS3 context

- Strategy

- ✓ The right balance has to be found inside DRDs between defining priorities and allowing new ideas to emerge

- ✓ Given the complex parameter space of R&D and detector design, a pragmatic approach should be privileged

- Increasing complexity step by step, demonstrators, mock-ups, experience from mid-term experiments, etc.

# backup

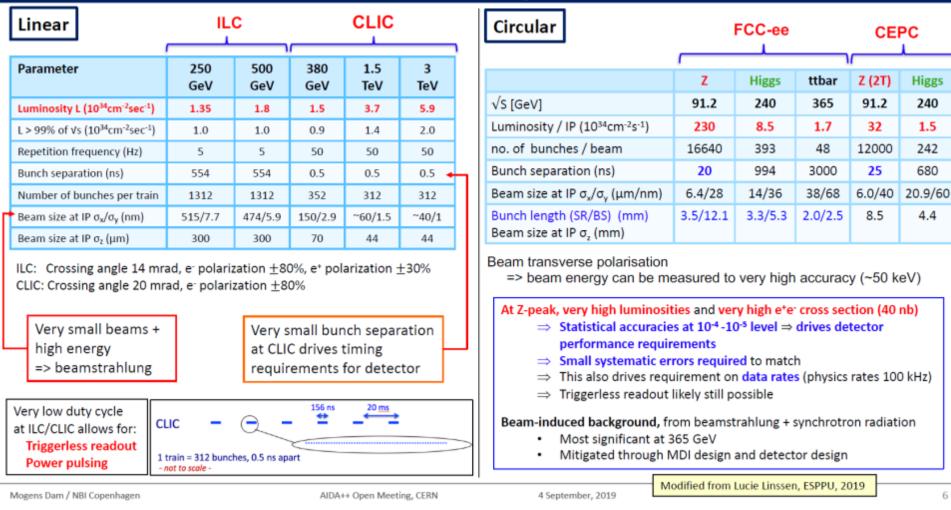

## e<sup>+</sup>e<sup>-</sup> collider beam parameters

(slide from Mogens Dam/Lucie Linssen)

train duration = 727 (baseline) or 961 (Lupgrade) µs

Bunch spacing = 554 (baseline) or 366 (Lupgrade) ns

200 or 100 ms (5 or 10 Hz)

# Collider parameters

# FCC-ee collider parameters

| parameter                                                             | z          | ww         | H (ZH)    | ttbar     |

|-----------------------------------------------------------------------|------------|------------|-----------|-----------|

| beam energy [GeV]                                                     | 45         | 80         | 120       | 182.5     |

| beam current [mA]                                                     | 1390       | 147        | 29        | 5.4       |

| no. bunches/beam                                                      | 16640      | 2000       | 393       | 48        |

| bunch intensity [10 <sup>11</sup> ]                                   | 1.7        | 1.5        | 1.5       | 2.3       |

| SR energy loss / turn [GeV]                                           | 0.036      | 0.34       | 1.72      | 9.21      |

| total RF voltage [GV]                                                 | 0.1        | 0.44       | 2.0       | 10.9      |

| long. damping time [turns]                                            | 1281       | 235        | 70        | 20        |

| norizontal beta* [m]                                                  | 0.15       | 0.2        | 0.3       | 1         |

| vertical beta* [mm]                                                   | 0.8        | 1          | 1         | 1.6       |

| horiz. geometric emittance [nm]                                       | 0.27       | 0.28       | 0.63      | 1.46      |

| vert. geom. emittance [pm]                                            | 1.0        | 1.7        | 1.3       | 2.9       |

| bunch length with SR / BS [mm]                                        | 3.5 / 12.1 | 3.0 / 6.0  | 3.3 / 5.3 | 2.0 / 2.5 |

| uminosity per IP [10 <sup>34</sup> cm <sup>-2</sup> s <sup>-1</sup> ] | 230        | 28         | 8.5       | 1.55      |

| beam lifetime rad Bhabha / BS [min]                                   | 68 / >200  | 49 / >1000 | 38 / 18   | 40 / 18   |

30/11/2021

Detector concepts for FCC-ee - Paolo Giacomelli

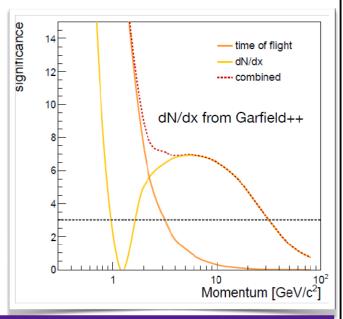

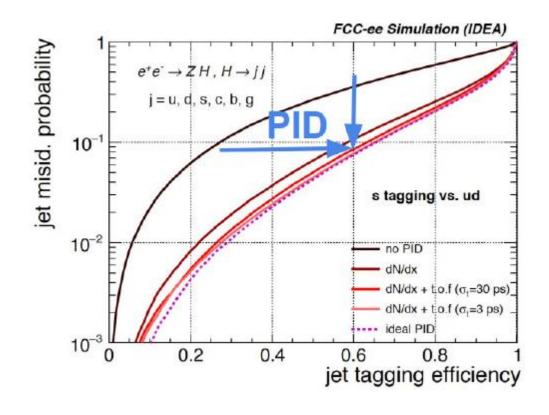

## PARTICLE IDENTIFICATION CAPABILITIES (PID)

Essential for flavour physics / spectroscopy

PID needed in a large momentum range!

- \* Suppress backgrounds e.g.  $B_s \rightarrow D_s K$ , p(K) extends up to 30 Gev

- Time-dependent CP asymmetries: need to tag the flavour (B or Bbar) of the meson at production.

- Use charge of 'opposite-side'

Kaon (b → c → s): p(K) very soft

Typically exploit ionisation energy loss and time-of-flight. Space constraints for a RICH, but ideas / work ongoing.

- Very useful for tau physics

- e.g. determination of B(  $\tau \to v \, \pi$  ), B(  $\tau \to nu$  K) hence  $V_{us}$  independent of lattice predictions

- · Input to jet flavour tagging (strange tagging)

30 ps assumed resolution for timing detector

- ➤ Expect > 3σ K/π separation from Cluster Counting in Drift Chamber up to ~30 GeV

- ➤ ToF at <100 ps resolution covers the region around 1 GeV

14

# DRDT 3.1 - Achieve full integration of sensing and microelectronics in monolithic CMOS pixel sensors.

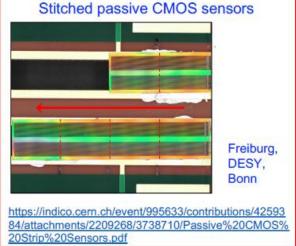

Developments of Monolithic Active Pixel Sensors (MAPS) should achieve very high spatial resolution and very low mass aiming to also perform in high fluence environments. To achieve low mass in vertex and tracking detectors, thin and large area sensors will be crucial. For tracking and calorimetry applications MAPS arrays of very large areas, but reduced granularity are required for which cost and power aspects are critical R&D drivers. Passive CMOS designs are to be explored, as a complement to standard sensors

DRDT 3.2 - Develop solid state sensors with 4D-capabilities for tracking and

Understanding of the ultimate limit of precision timing in sensors, with and without internal multiplication, requires extensive research together with the developments to increase radiation tolerance and achieve 100%-fill factors. New semiconductor and technology processes with faster signal development and low noise readout properties should also be investigated.

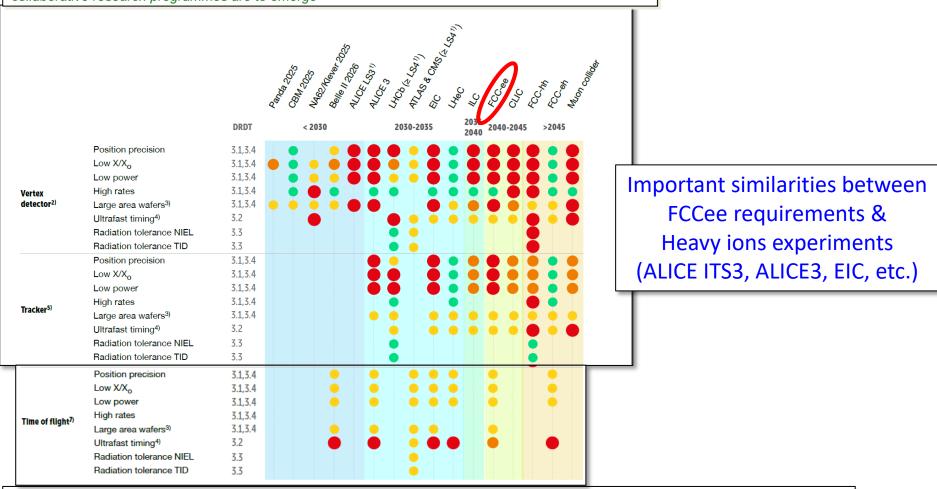

# **Synergies**

ECFA recognizes the need for the experimental and theoretical communities involved in physics studies, experiment designs and detector technologies at future Higgs factories to gather. **ECFA supports a series of workshops** with the aim to **share challenges and expertise**, **to explore synergies in their efforts** and to respond coherently to this priority in the European Strategy for Particle Physics (ESPP).

K. Jakobs, FCC Physics Workshop, Feb 2022

Goal: bring the entire e<sup>+</sup>e<sup>-</sup> Higgs factory effort together, foster cooperation across various projects; collaborative research programmes are to emerge

Must happen or main physics goals cannot be met 🛑 Important to meet several physics goals 🕒 Desirable to enhance physics reach 🔵 R&D needs being met

# s-tagging

Introduction

The MightyPix and friends

## MightyPix R&D: requirements

Programme dedicated to developing a HV-CMOS sensor that meets the following requirements for the Mighty Tracker:

| Pixel Size                                           | $< 100 \times 300 \mu \mathrm{m}$        |  |  |  |

|------------------------------------------------------|------------------------------------------|--|--|--|

| Timing resolution                                    | pprox 3 ns within 25 ns window           |  |  |  |

| In-time efficiency                                   | >99% within 25 ns window                 |  |  |  |

| Radiation tolerance                                  | $6 \times 10^{14} \; \rm n_{eq} cm^{-2}$ |  |  |  |

| Noise limit                                          | 5 Hz/pixel                               |  |  |  |

| Power consumption $< 150\mathrm{mW}\mathrm{cm}^{-2}$ |                                          |  |  |  |

| 32-bit data word.                                    |                                          |  |  |  |

| Compatible with LHCb Readout system                  |                                          |  |  |  |

From [1].

N.B. Studies are ongoing, and these requirements may evolve.

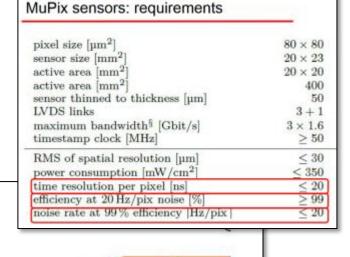

## Mupix: Monolithic sensors for the Mu3e experiment

Φ

Luigi Vigani University of Heidelberg Vertex 2022 25/10/2022

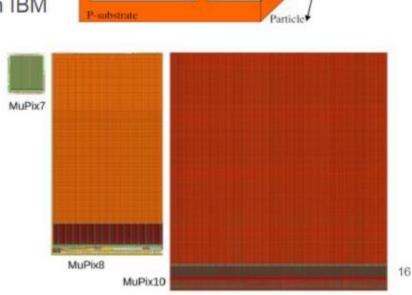

#### MuPix sensors

- Monolithic HV-CMOS

- Can be thinned while maintaining high performance

- 180 nm H18 technology derived from IBM

- AMS until 2018

- TSI afterwards

- Long R&D campaign

- Mupix7 first fully monolithic

- Mupix8 first large area

- Mupix9 implemented slow control

- Mupix10 with final size

- Used for prototyping

- Mupix11 final chip

- Characterization ongoing

E field

N-well

https://indico.cern.ch/event/1140707/contributions/5036352/attachments/2533480/4359729/tsuboyama-Belle2-vertex-upgrade-S3.pdf

https://indico.cern.ch/event/1140707/contributions/4988213/attachments/2533474/4359608/Vertex2022 khkang v3.pdf

https://indico.cern.ch/event/829863/contributions/5062886/attachments/2568342/4428391/baudot-pixel2022.pdf

### Example of trade off: MIMOSIS

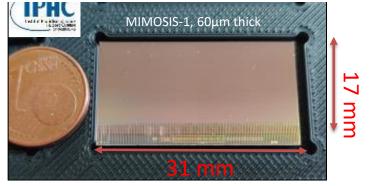

#### MIMOSIS-1 chip for CBM-MVD @ FAIR

| Parameter             | Value                        |  |  |  |

|-----------------------|------------------------------|--|--|--|

| Technology            | TowerJazz 180 nm             |  |  |  |

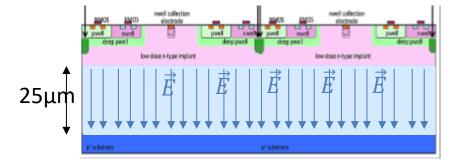

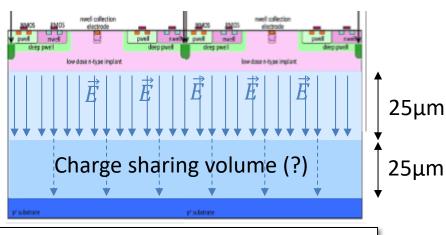

| Epi layer             | ~ 25 µm                      |  |  |  |

| Epi layer resistivity | $> 1k\Omega cm$              |  |  |  |

| Sensor thickness      | 60 µm                        |  |  |  |

| Pixel size            | 26.88 μm × 30.24 μm          |  |  |  |

| Matrix size           | 1024 × 504 (516096 pix)      |  |  |  |

| Matrix area           | $\approx 4.2  \mathrm{cm}^2$ |  |  |  |

| Matrix readout time   | 5 μs (event driven)          |  |  |  |

| Power consumption     | $40-70  \text{mW/cm}^2$      |  |  |  |

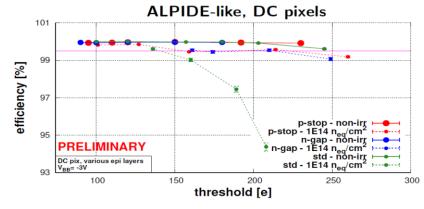

#### ✓ Based on ALPIDE architecture

- Multiple data concentration steps

- Elastic output buffer

- 8 x 320 Mbps links (switchable)

- Triple redundant electronics

- ✓ Pixel variants: DC/AC (top bias up to >20V)

- Different epitaxial variants tested

Pic from: Munker, Vertex 2018, Status of silicon detector R&D at CLIC Carlos, TREDI 2019, Results of the Malta CMOS pixel detector prototype for the ATLAS Pixel ITK

#### Intense test beam campaign(2021-22)

- ✓ Mimosis-2 submission these weeks

- Thicker epi layer tests

- Test prototype for 1 μs readout time

# Current large CMOS Monolithic Active Pixel Sensors

| Sensor                                                          | MIMOSA26/28                | ALPIDE          | MIMOSIS-1  | TJ-MONOPIX2    | MALTA-2        | LF-MONOPIX2 | ARCADIA MD2 | ATLASPix-3 | MuPix10    |

|-----------------------------------------------------------------|----------------------------|-----------------|------------|----------------|----------------|-------------|-------------|------------|------------|

| Date                                                            | 2008/10                    | 2015-17         | 2021       | 2021           | 2021           | 2021        | 2021        | 2019       | 2020       |

| Labo/Collab                                                     | IPHC                       | CERN+           | IPHC       | CERN-Bonn+     | CERN+          | Bonn-CERN+  | INFN        | KIT+       | KIT+       |

| Techno                                                          | AMS-350 nm                 | TJ-180 nm       | TJ-180 nm  | TJ-180 nm      | TJ-180 nm      | LF-150 nm   | LF-110 nm   | TSI 180 nm | TSI 180 nm |

| Pixel pitch (µm²)                                               | <b>18.4x18.4</b> 20.7x20.7 | 29x27           | 30x27      | 33x33          | 36.4x36.4      | 150x50      | 25x25       | 150x50     | 80X81      |

| #Columns x #Rows                                                | 1152x576<br>960/928        | 1024x512        | 1024x504   | 512x512        | 256x512        | 56x340      | 512x512     | 132x372    | 256x250    |

| Sensitive area (mm²)                                            | 21.2x10.6<br>19.7x19.2     | 27.5x15.0       | 31.0x13.6  | 16.9x16.9      | 10x20          | 8.4x17      | 12.8x12.8   | 19.8x18.6  | 20.5x20.0  |

| Time Stamp (ns)                                                 | 112/ x10 <sup>3</sup>      | 5000            | 5000       | 25             | 25             | 25          | ?           | 25         | 20         |

| Trigger latency (μs)                                            | Continuous r.o.            | Contin./Trig. 2 | Continuous | Global shutter | Global shutter | Continuous  | ?           | 25         | -          |

| Output charge (bits)                                            | 1                          | 1               | 1          | 7              |                | 6           | ?           | 7          | 5          |

| Bandwidth (Mbits/s)                                             | 180                        | 1200            | 3200       | 320            | 1300           |             | 2000        | 1300       | 3800       |

| Power (mW/cm²)                                                  | 300/150                    | 18-35           | ~50        | O(200)         | >70            |             | O(20) ?     | 150        | <350       |

| Hit rate (Mhz/cm²)                                              | O(0.1)                     | <10             | 15-70      | >100           | >100           | >100        | >100        | >100       | ?          |

| TID kGy                                                         | 2                          | 27              | 100        | 1000           | 1000           |             | ?           | 1000       | -          |

| Fluence (x 10 <sup>13</sup> n <sub>eq</sub> .cm <sup>-2</sup> ) | 0.1                        | 1.7             | 10         | 300            | 300            | 100         | ?           | 100        | 100        |

J. Baudot. - MAPS activities at IPHC-Strasbourg - KEK, 2022/11/29

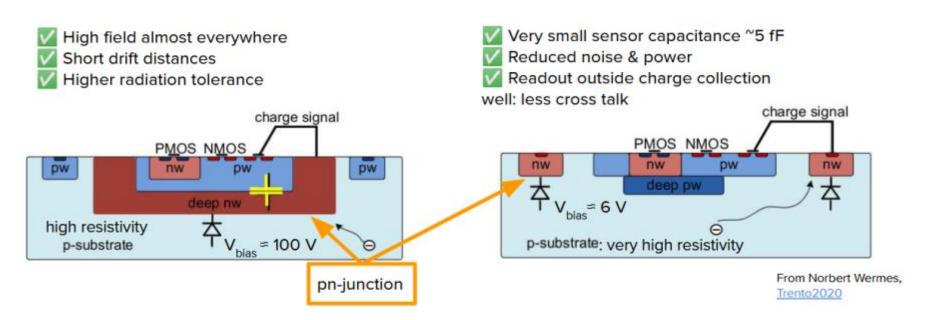

# Depleted MAPS: small and large collection electrodes

- Stronger electric field results in less trapping and higher radiation tolerance

- Larger electric field comes at a cost: more capacitance, power and more noise

From E. Vilella, Vertex2018

# **Mechanics**

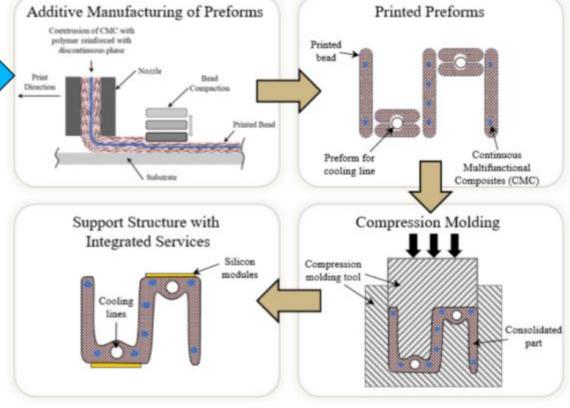

# Going into the future of mechanics

#### Identified by DOE BRN effort & CPAD

Scaling of low-mass detector system towards irreducible support structures with integrated services. Includes: integrated services, power management, cooling, data flow, and multiplexing.

→ Collaboration with material sciences, companies for novel materials, and latest techniques.

- → Example: Cutting-edge composite manufacturing techniques, in-house

- → Reduce mass & boost thermal performance

54

## Hybrid strip detectors

#### Hybrid strip detectors:

- baseline for ILC trackers (also suitable for CLIC outer layers)

- Well-established technology (e.g. HL-LHC)

- low material + power (sparse readout)

- large and fast signals (dE/dx)

- high spatial resolution (charge interpolation) in R/phi direction

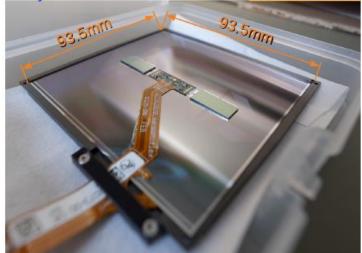

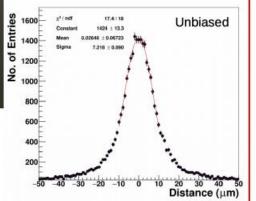

- Allows for testing of advanced sensor concepts (e.g. stitched passive CMOS strip sensors)

- Challenges: not for high occupancy regions; complex interconnect

Lycoris module

Routing Layer (to bump pad)

PolySi-R

Passivation SiO<sub>2</sub>

Coupling Layer InterLayer

Strip Implant Layer

- Lycoris development DESY / SLAC:

- 320 µm thick SiD strip sensors, 25 µm pitch

- KPiX r/o ASIC

- Chip bump-bonded on-sensor → high fill factor

- 7 µm single-point resolution achieved in test beam

- Test-case: beam telescope for PCMAG@DESY

https://indico.cern.ch/event/995633/contributions/4259345/attachments/2210031/3740113/LCWS 2021.pdf

October 6, 2022

Tracking and Vertexing for Higgs Factories

1/