HL-LHC Magnet Circuit Instrumentation Day 2023

# Power Interlock Controller Loops, System Tests and Commissioning

Alain Antoine (TE-MPE-MI)

20 June 2023

### OUTLINE

- INTRODUCTION TO PIC

- HL-LHC SPECIFICATIONS for PIC

- SECOND GENERATION OF PIC

- IST AND COMMISSIONING

- CONCLUSIONS

# Introduction

20.06.2023

HL-LHC Magnet Circuit Instrumentation Day 2023

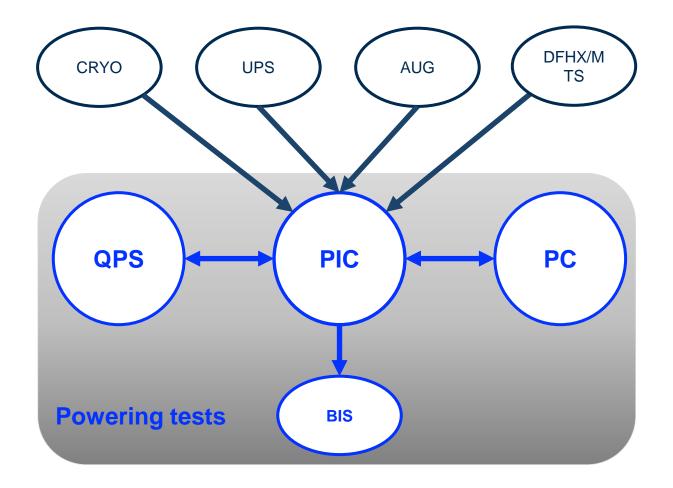

### **PIC is designed to:**

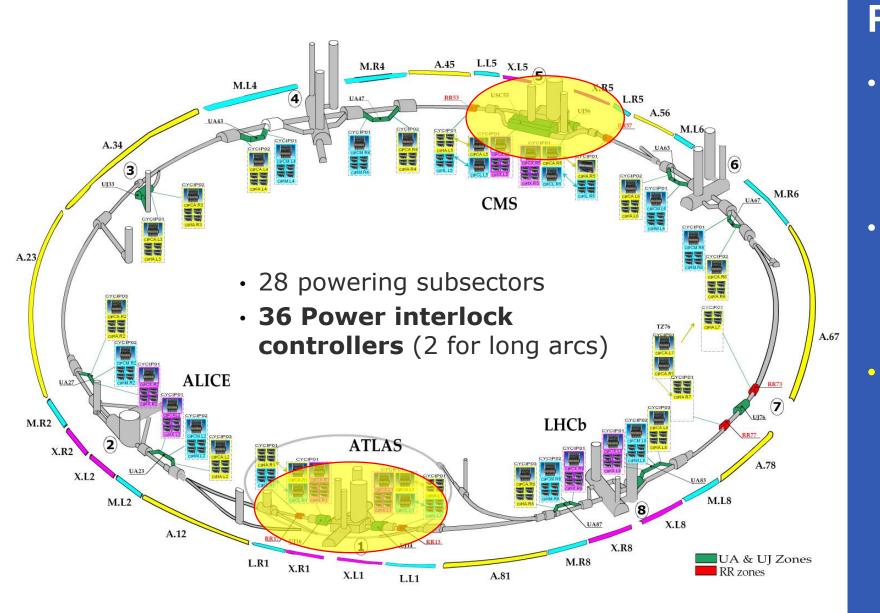

- Ensure the correct powering conditions for the superconducting magnet circuits of the LHC.

- Request a beam dump via the Beam Interlock System in case of failure of a connected circuits.

- A total of 12 out of 36 PICs are located at point 1 and 5.

# **HL-LHC Specifications for PIC**

20.06.2023

HL-LHC Magnet Circuit Instrumentation Day 2023

## **HL-LHC Specifications for PIC**

### • Relocation of the 12 PICs of the sectors 1 and 5:

- from UL14, UL16 to UR15,

- from USC55, UL557 to UR55.

- Moving the electronics from the RRs to the URs to cope with the predicted increase in radiation levels induced by future HL-LHC beams.

- New configuration of the PICs of the inner triplet regions and matching sections in point 1 & 5.

- New interface at point 1 and 5 for HL-LHC circuits: DFHX/M thermal switches for the inner triplet and matching sections

- <u>Note:</u> PIC is ready for the 11T magnet integration

|               | Circuits for HiLumi                      | Magnet Type     | Circuit Name                                                            | Number of<br>circuits per IP<br>side | Total number<br>of circuits | l_nominal<br>(7 TeV) [kA] | l_ultimate<br>[kA] | L per circuit<br>at nominal<br>current [mH] | R per circuit<br>[mΩ] | Comments or References           |  |  |

|---------------|------------------------------------------|-----------------|-------------------------------------------------------------------------|--------------------------------------|-----------------------------|---------------------------|--------------------|---------------------------------------------|-----------------------|----------------------------------|--|--|

|               | Triplet Q1, Q2a, Q2b, Q3                 | MQXFA / MQFXB   | RQX                                                                     | 1                                    | 4 (IR1/5)                   | 16,23                     | 17,5               | 255,4                                       | 0,15                  | CERN-ACC-2017-0101; EDMS 1375861 |  |  |

| Inner Triplet | Trim Q1                                  | -               | RTQX1                                                                   | 1                                    | 4 (IR1/5)                   | 2                         | 2                  | 69                                          | 1,35                  |                                  |  |  |

|               | Trim Q1a                                 | -               | RTQXA1                                                                  | - 1                                  | 4 (IR1/5)                   | 0,035                     | 0,035              | 34,5                                        | 226,16                |                                  |  |  |

|               | Trim Q3                                  | -               | RTQX3                                                                   | - 1                                  | 4 (IR1/5)                   | 2                         | 2                  | 69                                          | 1,2                   |                                  |  |  |

|               | Orbit correctors Q1/2 - Horizontal/Inner | MCBXFB          | RCBXH[1,2]                                                              | 2                                    | 8 (IR1/5)                   | 1,74                      | 1,864              | 58,4                                        | 2,37                  |                                  |  |  |

|               | Orbit correctors Q1/2 - Vertical/Outer   | MCBXFB          | RCBXV[1,2]                                                              | 2                                    | 8 (IR1/5)                   | 1,43                      | 1,532              | 124,8                                       | 2,42                  |                                  |  |  |

|               | Orbit correctors Q3 - Horizontal/Inner   | MCBXFA          | RCBXH3                                                                  | - 1                                  | 4 (IR1/5)                   | 1,593                     | 1,709              | 107.1                                       | 1,99                  |                                  |  |  |

| erT           | Orbit correctors Q3 - Vertical/Outer     | MCBXFA          | RCBXV3                                                                  | - 1                                  | 4 (IR1/5)                   | 1,34                      | 1,441              | 232,3                                       | 1,98                  |                                  |  |  |

| ŭ             | Superferric, order 2                     | MQSXF           | RQSX3                                                                   | - 1                                  | 4 (IR1/5)                   | 0,174                     | 0,197              | 1530                                        | 14,31                 |                                  |  |  |

| -             | Superferric, order 3, normal and skew    | MCSXF / MCSSXF  | RCS[S]X3                                                                | 2                                    | 8 (IR1/5)                   | 0,099                     | 0,112              | 213                                         | 54                    |                                  |  |  |

|               | Superferric, order 4, normal and skew    | MCOXF / MCOSXF  | RCO[S]X3                                                                | 2                                    | 8 (IR1/5)                   | 0,102                     | 0,115              | 220                                         | 54                    |                                  |  |  |

|               | Superferric, order 5, normal and skew    | MCDXF / MCDSXF  | RCD[S]X3                                                                | 2                                    | 8 (IR1/5)                   | 0,092                     | 0,106              | 120                                         | 54                    |                                  |  |  |

|               | Superferric, order 6                     | MCTXF           | RCTX3                                                                   | 1                                    | 4 (IR1/5)                   | 0,085                     | 0,097              | 805                                         | 54                    |                                  |  |  |

|               | Superferric, order 6, skew               | MCTSXF          | RCTSX3                                                                  | 1                                    | 4 (IR1/5)                   | 0,084                     | 0,094              | 177                                         | 54                    |                                  |  |  |

| D1            | Separation dipole D1                     | MBXF            | RD1                                                                     | 1                                    | 4 (IR1/5)                   | 12,11                     | 13,231             | 24,84                                       | 0,31                  |                                  |  |  |

| 2             | Recombination dipole D2                  | MBRD            | RD2                                                                     | 1                                    | 4 (IR1/5)                   | 12,33                     | 13,343             | 27,46                                       | 0,13                  |                                  |  |  |

| D2            | Orbit correctors D2                      | MCBRD           | RCBRD[V,H]4                                                             | 4                                    | 16 (IR1/5)                  | 0,394                     | 0,422              | 920                                         | 1,36                  |                                  |  |  |

| 8             | Individually powered quad Q4 (4.5K)      | MQY             | Same Circuit Paramters                                                  |                                      |                             |                           |                    |                                             |                       |                                  |  |  |

| ď             | Orbit correctors Q4 (4.5K)               | MCBY            | Q4 Magnets                                                              |                                      |                             |                           |                    |                                             |                       |                                  |  |  |

| 5             | Individually powered quad Q5 (4.5K)      | MQML            |                                                                         |                                      | ECR EDMS no. 2083813        |                           |                    |                                             |                       |                                  |  |  |

| Q5            | Orbit correctors Q5 (4.5K)               | MCBC            | Samo Circuit Paramter                                                   | for O5 Of and                        | ECK EDM510. 2083813         |                           |                    |                                             |                       |                                  |  |  |

| QG            | Individually powered quad Q6 (4.5K)      | MQML            | Same Circuit Paramters for Q5, Q6 and Correctors in IR1/5 as in the LHC |                                      |                             |                           |                    |                                             |                       |                                  |  |  |

| σ             | Orbit correctors Q6 (4.5K)               | MCBC            |                                                                         |                                      |                             |                           |                    |                                             |                       |                                  |  |  |

| Q10           | Individually powered quad Q10 (1.9K)     | MQML            | RQ10                                                                    | 2                                    | 8 (IR1/5)                   | 5,39                      | 5,83               | 21                                          | 0,4                   |                                  |  |  |

|               | Orbit correctors Q10 (1.9K)              | MCB             | RCB[V,H]10                                                              | 2                                    | 8 (IR1/5)                   | 0,055                     | 0,06               | 6020                                        | 45,8                  | ECR EDMS no. 2796793             |  |  |

|               | Lattice Sextupole (1.9K)                 | MS              | RS[D,F][1,2]                                                            | 2                                    | 8 (IR1/5)                   | 0,55                      | 0,6                | 432                                         | 7,5                   |                                  |  |  |

| Q5            | Individually powered quad Q5 (4.5K)      | MQY             | RQ5                                                                     | 2                                    | 4 (IR6)                     | 3,61                      | 3,9                | 74                                          | 0,4                   |                                  |  |  |

|               | Orbit correctors Q5 (4.5K)               | MCBY            | RCBY[V,H]5                                                              | 2                                    | 4 (IR6)                     | 0,088                     | 0,1                | 5270                                        | 34,4                  |                                  |  |  |

|               | 11T dipole, MBH                          | 11T dipole, MBH | RB.A67-RB.A78                                                           | -                                    | 2 (IR7)                     | 11,85                     | 12,798             | 15734                                       | 1                     |                                  |  |  |

|               | Trim circuit                             | -               | RTBH9                                                                   | -                                    | 2 (IR7)                     | 0.25                      | 0.25               | 127 1                                       | 30.96                 |                                  |  |  |

# **Second Generation of PIC (PICv2)**

20.06.2023

HL-LHC Magnet Circuit Instrumentation Day 2023

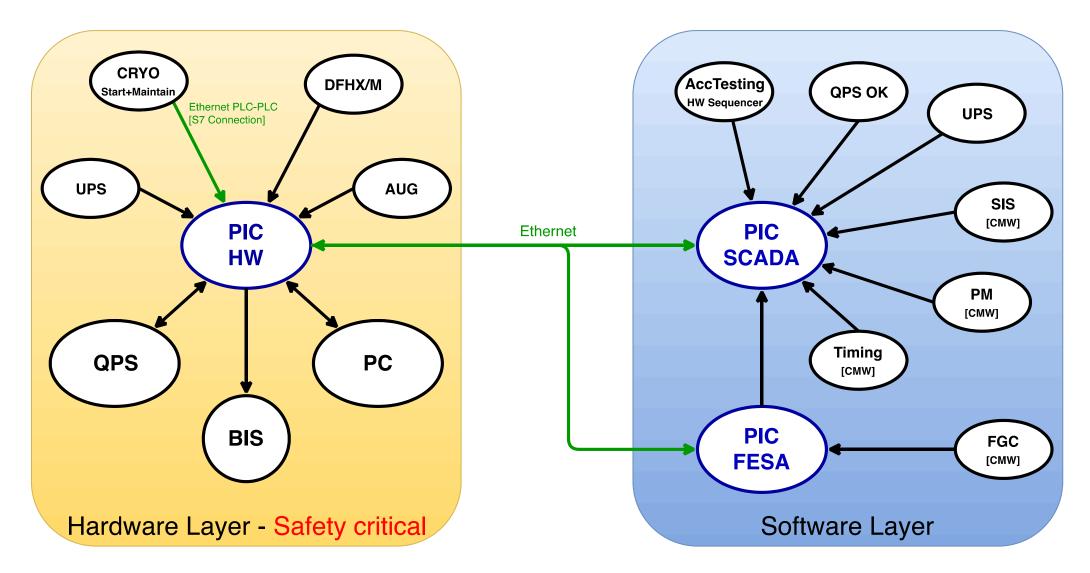

### **Interface overview**

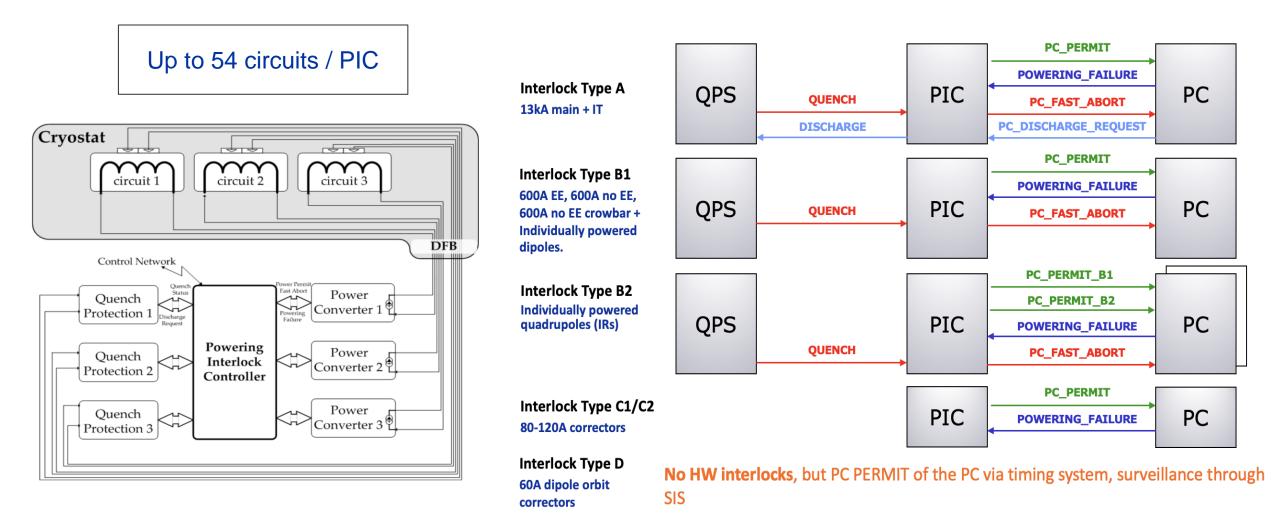

## **Circuit Interlock Types**

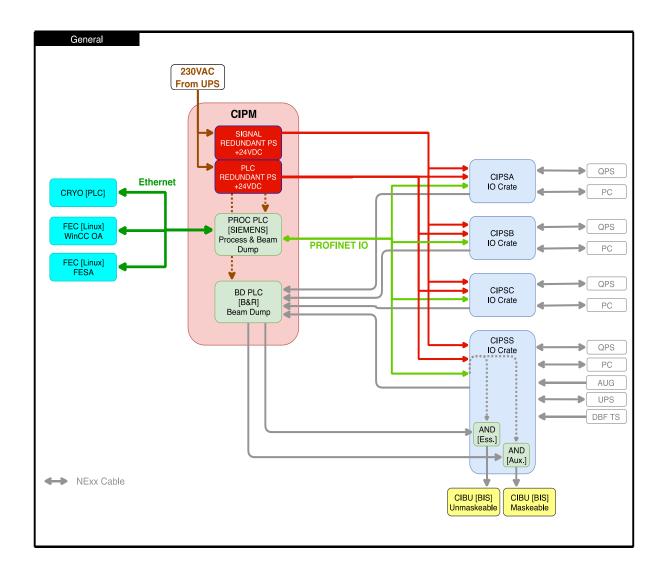

# **Second Generation of PIC**

### • Why?

- Extend the lifespan of the PIC systems beyond HL-LHC by addressing the obsolescence of critical components in the system design.

- Assure compatibility with HL-LHC protection requirements.

### Design

- A purely industrial solution prototype based on PLC is available (HW) and will be installed at IT-STRING.

- Redesign of the PLC, WinCC software by BE-ICS using UNICOS is in progress and should be available by end of June.

|                                  |             |     |          |                        |          |                                              | AR.      |                                   |        |                                         | -        | 10:17:55 AM 19-Jun-2023              |

|----------------------------------|-------------|-----|----------|------------------------|----------|----------------------------------------------|----------|-----------------------------------|--------|-----------------------------------------|----------|--------------------------------------|

| Cuit Bad<br>BXH1<br>POWER PERMIT |             | uit | <b>\</b> | UACV1_UEI<br>cut       | EZ_M05_2 | 52 BATTERIE EI<br>RCBXV2<br>READY<br>CIRCUIT | ECTRIQUE | CITCUIT                           | SE II  | I 1/183 T<br>RCBXV3<br>READY<br>CIRCUIT | 4 Unack. | Circuit<br>RQSX3<br>READY<br>CIRCUIT |

| TUIT READY                       | RQX         |     | RC       | CREADY                 |          | Circuit<br>RCSSX3<br>READY                   |          | Circuit<br>RCOX3<br>READY         |        | Circuit<br>RCOSX3<br>READY<br>CIRCUIT   |          | Crcuit<br>RCDX3<br>READY<br>CIRCUIT  |

| rcuit<br>DSX3<br>READY           | Circ<br>RCT |     | O RC     | rcuit<br>TSX3<br>READY |          | Circuit                                      | 0        | Circuit<br>B2_B1_4<br>0<br>CRCUIT | 0<br>0 | Circuit<br>B2_B1_5<br>0<br>CIRCUIT      | 6<br>0   | Circuit<br>B2_B1_6<br>0<br>CIRCUIT   |

### Reliability studies Outcome

- Redundant reading of the loops.

- Beam dump request redundancy ensured by an extra CPU.

- Study ongoing

- Possibility of reducing the number of CPUs per LHC sector to 2, to avoid the exchange of hardware signals between the PICs.

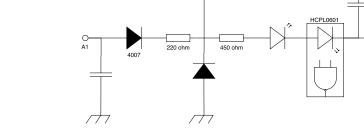

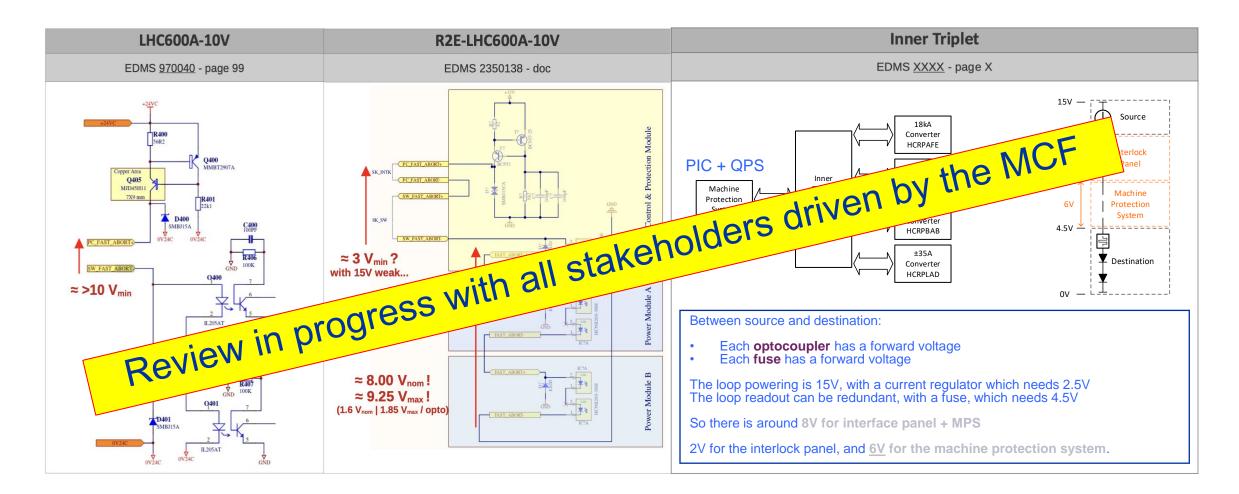

### **Current loops**

- The new design of the PICv2 highlighted the potential risk of degradation of the integrity of the Quench loop induced by the voltage drops produced by all the systems.

- LHC specifications (EDMS 1001985) for current loops:

- 10 mA < I < 20 mA and 15 V < V < 24 V

- Maximum allowed voltage drop of each system is 2.5 V.

#### PICv2 Prototype

- Preliminary studies to select the components have focused on the reaction time (<75us for CLIQ integration) :

- Opto-coupler to write on the loops: Finder 24 VDC.

- Opto-coupler to read on the loops: Weidmüller MOS 12-28 VDC.

- 2x 4.2 VDC optocoupler voltage drop is caused by internal protection against reverse current, over voltage and short circuit.

- CLIQ is out of the picture: reaction time restrained to 10 ms -> wider opto-coupler choice.

- HW validated in MPE testbed 272 and in the PIC testbed:

- Power Permit loop with FGC

- Powering Failure loop with FGC

- Quench loop with FGC and CLIQ (No EE)

4.4 Kohm

Finder

Weidmüller

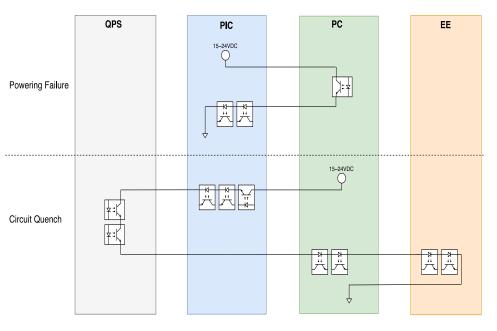

### **Quench Loop: different cases...**

#### Courtesy of Y. Thurel and B. Todd

# **IST & HWC**

20.06.2023

### **Reference Documents**

- General Procedure for the Commissioning of the Electrical Circuits of a sector (Eng. Spec.)

- EDMS 477145: <u>LHC-D-HCP-0001</u>

- Individual System Tests of the Powering Interlock Controller

- EDMS 531823: LHC-CI-TP-0001

- MPS Aspects of the Power Interlock System Commissioning

- EDMS 896390: <u>LHC-OP-MPS-0005</u>

- Interlock Tests of Powering Subsector Prior & After Connection of the Power Cables to DFB Leads

- EDMS 519704: <u>LHC-D-HCP-0002</u>

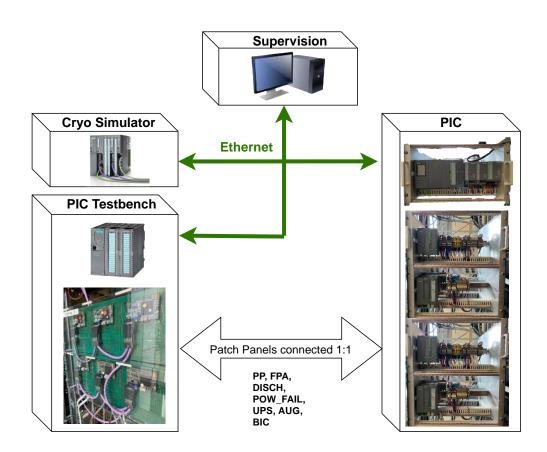

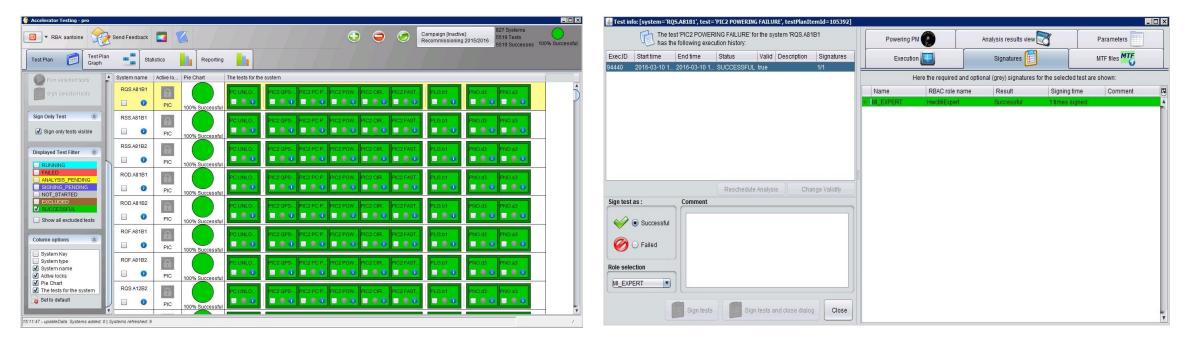

### **Individual System Tests**

- To validate the correct functioning of the PIC, including the supervision application in stand-alone mode.

- 2 steps:

- Prior to the installation of a PIC in the LHC:

- A **dedicated test system** is used to interface any existing PIC hardware configuration and to simulate all protection signals.

- An automated procedure verifies the correct response of the powering interlock controller for all possible failure scenarios simulated with the test system (validation of PLC HW + SW).

- In-situ (proposal to be tested at IT-STRING):

- The PIC is entirely cabled but all systems are disconnected and replaced by dedicated "bouchon".

# **Hardware Commissioning**

- 12 out of 36 PIC are to be tested for HL-LHC.

- Tests entirely carried out manually (with the concerned teams).

- CRYO

- Tests and validation from the CCC.

- UPS

- Validation in collaboration with EN/EL team which acts on the UPS in the tunnel.

- AUG

- Analysis of all events in the PIC history buffer.

- DFHX/M Thermal switches.

- Interface and configuration.

- Automated tests via AccTesting.

- Powering tests.

Test Procedure in EDMS 519704.

The aim is the commissioning of hardwired protection signals, transmitted via current loops in between the involved systems (PC\_PERMIT, POW\_FAIL, QUENCH, DISCHARGE\_REQ, BIS).

Test management with AccTesting (MPE-CB).

# **Powering Tests (2)**

| Test                      | Interlock Type  | Circuit Type           | PIC Signature    |  |  |

|---------------------------|-----------------|------------------------|------------------|--|--|

| PC_PERMIT                 | A, B1, B2, C    | All                    | Not required     |  |  |

| POWER FAILURE             | A(1)            | RB                     | PIC Expert       |  |  |

|                           | A(2), B1, B2, C | Others                 | Automatic (eDSL) |  |  |

| CIRCUIT QUENCH<br>VIA QPS | A, B1           | RB, RQD, RQF, RQX, IPD | PIC Expert       |  |  |

|                           | B1, B2          | 600A EE/noEE           | Automatic (eDSL) |  |  |

| FAST ABORT                | A, B1           | RB, RQD, RQF, RQX, IPD | PIC Expert       |  |  |

| VIA PIC                   | B1, B2          | 600A EE/noEE           | Automatic (eDSL) |  |  |

| DISCHARGE REQ<br>VIA PIC  | A               | RB, RQD, RQF           | PIC Expert       |  |  |

| PIC TO BIC                | All             | All                    | PIC Expert       |  |  |

### HL-LHC: 88 PIC tests / IP Side (+31 PIC to BIC tests).

- The PICv2 prototype is a full industrial solution that has been successfully tested in the MPE testbed and the Hardware is ready for IT-STRING.

- PLC configuration for LHC still to be defined.

- Review of the current loops specifications and voltage drop study with all stakeholder ongoing.

- The Second generation of PIC Software is currently under development by BE-ICS.

- PICv2 still to be integrated in AccTesting (ongoing).

- Very good understanding of the IST and HWC.

home.cern

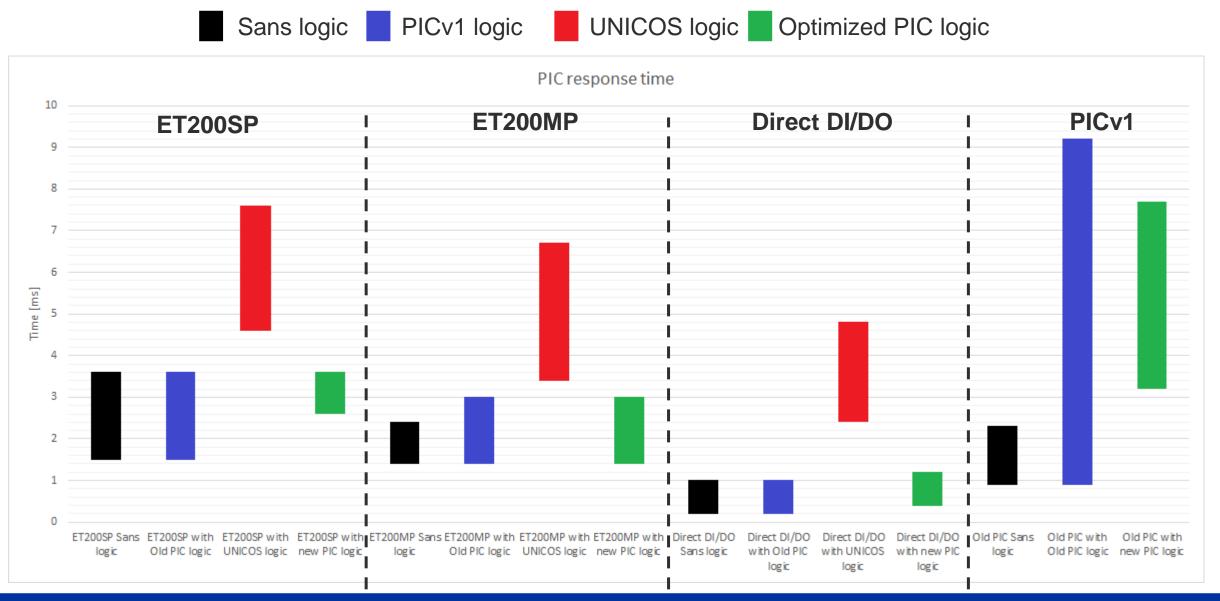

### **Second Generation of PIC**

### **PICv2 Industrial Solution – Response Time Results**

### **PIC Software: Towards a Second Generation**

### Original PLC software

- Tailor-made, written in STL language.

- Based on UNICOS TSPP protocol to communicate with WinCC OA (SCADA).

- Not compatible with the current Siemens S7-1500 series PLC (UNICOS communication protocol).

- A second generation of software is mandatory, keeping each system software generic throughout all instances.

### **Two possible solutions**

# PIC v2 – UNICOS software Prototype

Fully UNICOS integrated PIC v2 software, is currently being developed by BE-ICS as a solution for IT STRING.

- Study ongoing:

- Merging several PICs in a powering Subsector maintaining a reaction time < 10 ms (PLC cycle time + Interface).

- AccTesting integration.

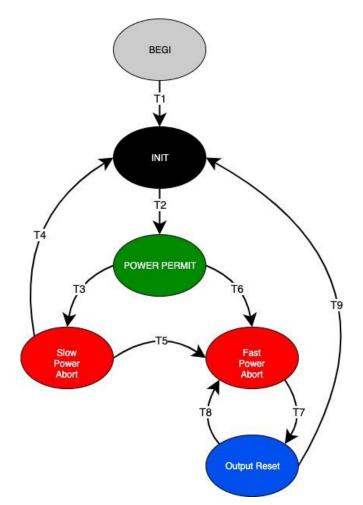

### **Interlocking Strategy**

| Foilure Tupe     | PIC Action       |  |  |  |  |  |

|------------------|------------------|--|--|--|--|--|

| Failure Type     | PIC ACTION       |  |  |  |  |  |

| Powering Failure | Slow Power Abort |  |  |  |  |  |

| Quench           | Fast Power Abort |  |  |  |  |  |

| Discharge        | Fast Power Abort |  |  |  |  |  |

| Cryo             | Slow Power Abort |  |  |  |  |  |

| UPS              | Slow Power Abort |  |  |  |  |  |

| AUG              | Slow Power Abort |  |  |  |  |  |

| GPM              | Fast Power Abort |  |  |  |  |  |

| Operator         | Slow Power Abort |  |  |  |  |  |

|                  | Fast Power Abort |  |  |  |  |  |

- The Global Protection

Mechanism (GPM) is designed

to trigger a preventive discharge

of magnet circuits in the vicinity

of a main magnet that

quenched, in order to reduce the

likelihood of secondary

quenches due to heat

propagation.

- Each circuit is configured to activate or not the global protection mechanism (GPM).