# **Technology Transfer** on high rate µ-RWELL

### Matteo Giovannetti [LNF-INFN]

on behalf of LNF-INFN (leading group) Bologna-Ferrara INFN teams R. De Oliveira – CERN-EP-DT-MPT Workshop R. Pinamonti, M. Pinamonti – ELTOS S.p.A.

RD51 collaboration meeting, CERN, June 21<sup>th</sup> 2023

## The µ-RWELL detector (reminder)

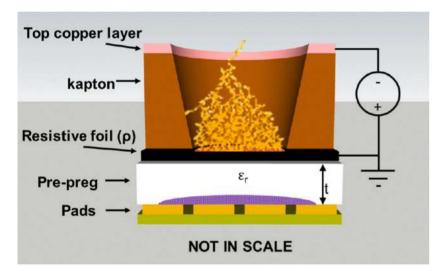

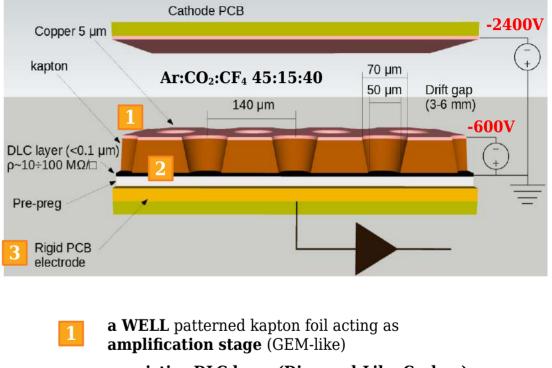

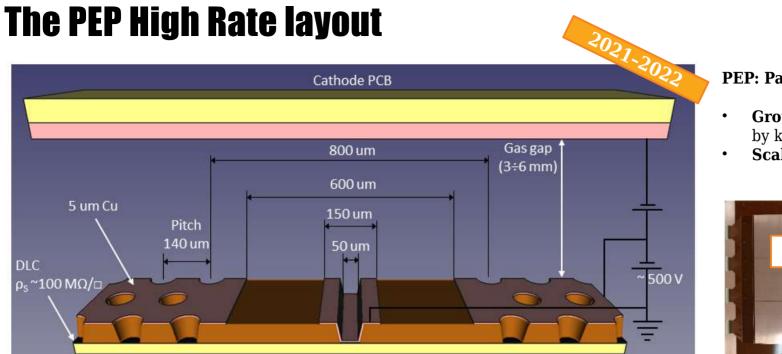

The  $\mu$ -RWELL is a Micro Pattern Gaseous Detector (MPGD) composed of only two elements: the  $\mu$ -RWELL\_PCB and the cathode. **The core is the \mu-RWELL\_PCB**, realized by coupling three different elements:

Applying a suitable voltage between the **top Culayer and the DLC** the WELL acts as a **multiplication channel for the ionization** produced in the conversion/drift gas gap.

a **resistive DLC layer (Diamond-Like-Carbon)** for discharge suppression with surface resistivity  $\sim 50 \div 100 \text{ M}\Omega/\Box$

a standard readout PCB

### **Task objectives**

### **DELIVERABLE - m30**

• **D7.3:** µ-RWELL prototypes co-produced by industry under the guidance and supervision of the research team. A complete report will be provided (Task 7.3)

### MILESTONE - m36

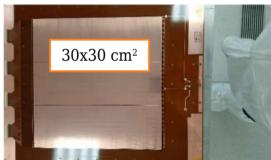

• MS27: build a 0.3×0.3 m<sup>2</sup> prototype and the readout plane, with the new structure

## **Operative Meetings**

#### $\mathbf{21^{st}}$ Sept. $\mathbf{2021}$ - joint INFN-ELTOS-CERN meeting

• standardizing manufacturing procedures of  $\mu$ -RWELL layout

#### $1^{\mbox{\scriptsize st-}}3^{\mbox{\scriptsize rd}}$ Dec. 2021 - CERN-INFN meeting

- status of the R&D on the High Rate layout

- 2D layout based on the readout of a segmented amplification stage

#### $7^{th}\text{--}10^{th}$ Dec. 2021 – $1^{st}$ test batch in ELTOS

- DLC patterning

- PCB planarizing tests

#### $7^{th}\text{-}8^{th}$ Mar. 2022 - 2<sup>nd</sup> test batch in ELTOS

\_\_\_\_\_

- PCB planarizing tests

- Kapton DLCed foil coupling with PCB-readout

**28<sup>th</sup>-31<sup>th</sup> Mar. 2022** 1<sup>st</sup> AIDAinnova Annual meeting

## **Operative Meetings**

21st Sept. 2021 - joint INFN-ELTOS-CERN meeting

• standardizing manufacturing procedures of  $\mu\text{-RWELL}$  layout

$1^{\mathrm{st}}\text{-}3^{\mathrm{rd}}$  Dec. 2021 - CERN-INFN meeting

- status of the R&D on the High Rate layout

- 2D layout based on the readout of a segmented amplification stage

### $7^{th}$ -10<sup>th</sup> Dec. 2021 – 1<sup>st</sup> test batch in ELTOS

- DLC patterning

- PCB planarizing tests

#### 7<sup>th</sup>-8<sup>th</sup> Mar. 2022 - 2<sup>nd</sup> test batch in ELTOS

- PCB planarizing tests

- Kapton DLCed foil coupling with PCB-readout

### $\mathbf{31^{st}}$ Oct. $\mathbf{2022}$ - joint INFN-CERN meeting

- Discussion with Rui about the results obtained

- Planning 2023 production

### $\mathbf{5}^{th}$ Dec. $\mathbf{2022}$ - joint INFN-ELTOS meeting

• Planning 2023 production

#### 20th-22th Mar. 2023 - 1st production batch in ELTOS

- DLC patterning

- PCB palnarizing (prepreg thickness scan)

24<sup>th</sup>-27<sup>th</sup> Apr. 2023 2<sup>nd</sup> AIDAinnova Annual meeting

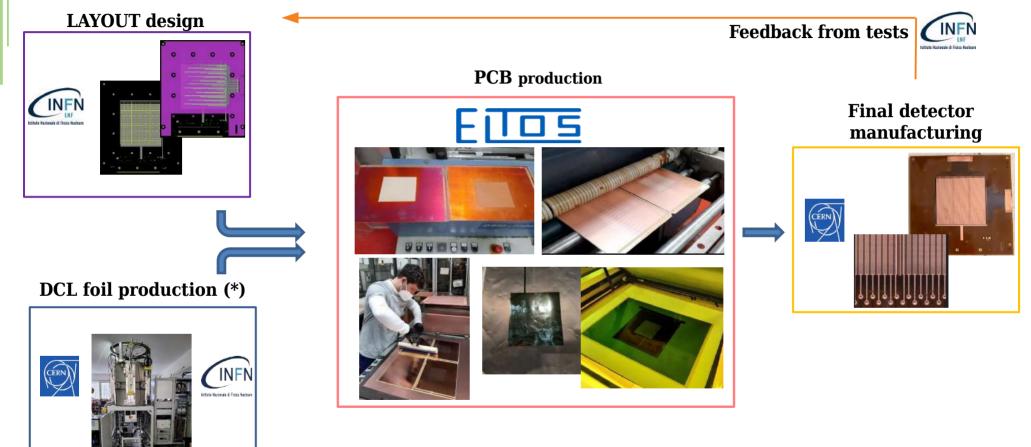

# WP7.3.2: Technology Transfer (flow chart)

\*DLC Magnetron Sputtering machine co-funded by INFN- CSN1

# WP7.3.2: Technology Transfer 2022

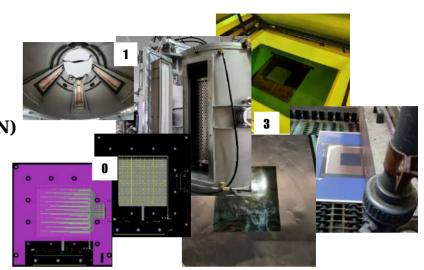

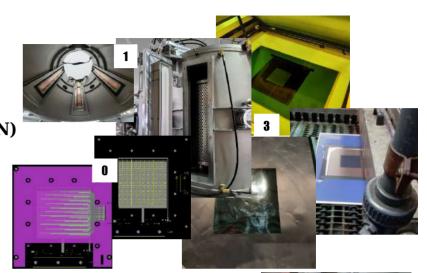

Step 0 - Detector PCB design @ LNF

- Step 1 CERN INFN DLC sputtering machine @ CERN (+INFN)

- delivery foreseen by the end of Oct. 2022

- INFN crew tbd & trained

- Step 2- Producing readout PCB by **ELTOS**

- pad/strip readout

- Step 3 DLC patterning by CERN

- photo-resist  $\rightarrow$  patterning with BRUSHING-machine

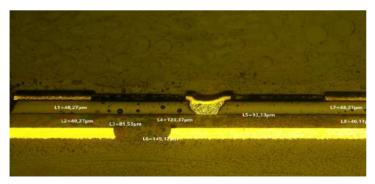

- Step 4 DLC foil gluing on PCB by  $\ensuremath{\textbf{CERN}}$

- double 106-prepreg  $\rightarrow 2x50\mu m$  thick

- \* PCB planarizing w/ screen printed epoxy  $\rightarrow$  single 106-prepreg

- Step 5 Top copper patterning by **CERN** (in future by **ELTOS)**

- Holes image and HV connections by Cu etching

- Step 6 Amplification stage patterning by  $\ensuremath{\textbf{CERN}}$

- PI etching  $\rightarrow$  plating  $\rightarrow$  ampl-holes

- Step 7 Electrical cleaning and detector closing @  $\ensuremath{\textbf{CERN}}$

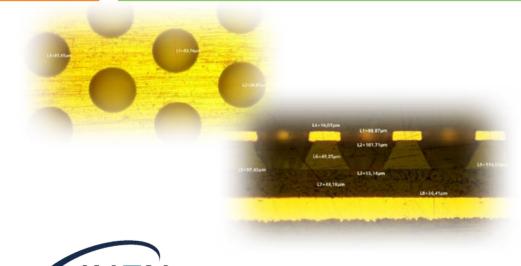

# WP7.3.2: µ-RWELL layouts co-built by ELTOS & CERN (Oct.'22)

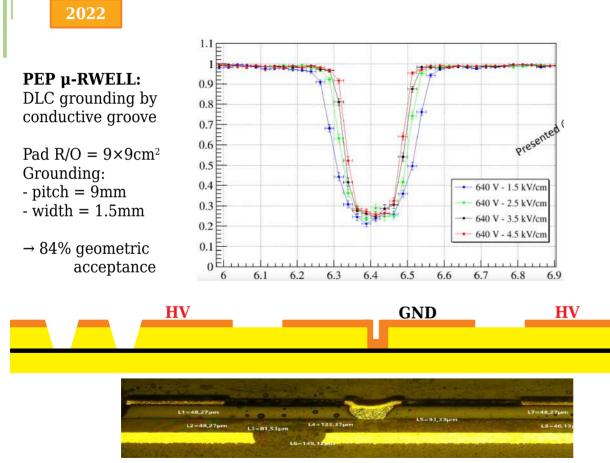

# WP7.3.2: (June '23) PEP optimization

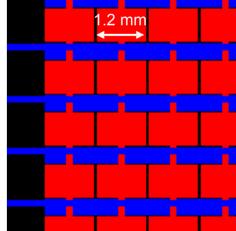

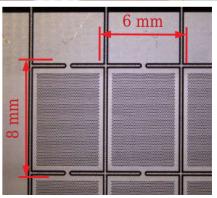

**PEP-dot µ-RWELL:** DLC grounding by conductive dot connected to the readout Dot rim = 1.6mm | Pad R/O =  $9 \times 9$ cm<sup>2</sup>  $\rightarrow 97\%$  geometric acceptance

2023

RD51 collaboration meeting - M. Giovannetti

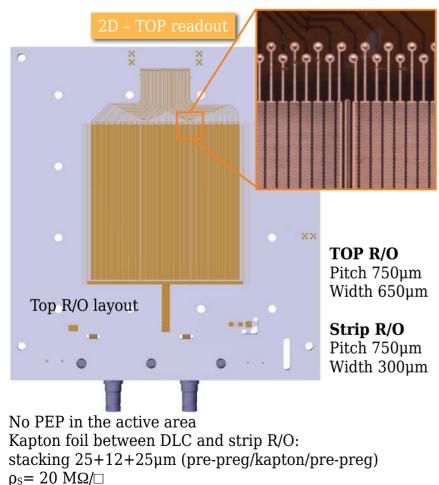

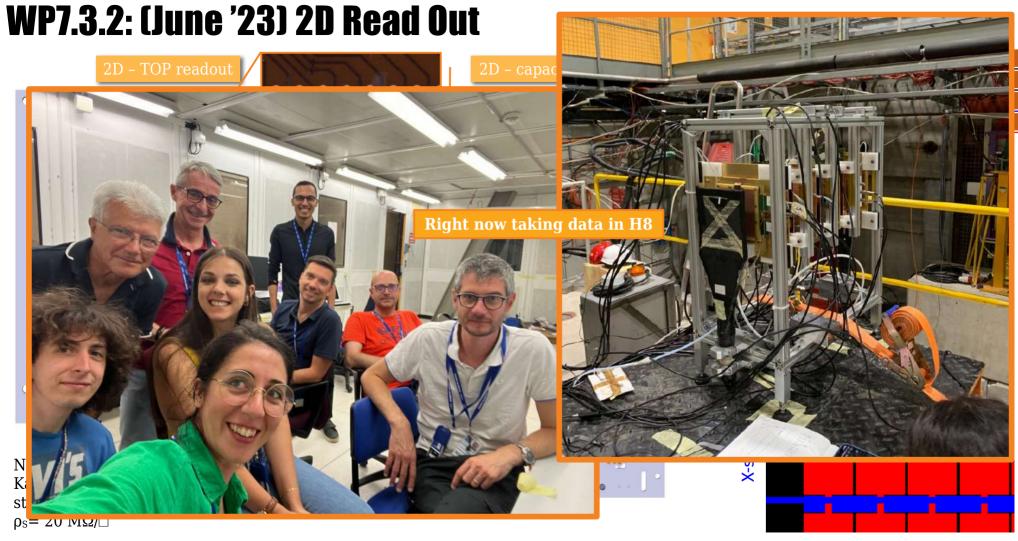

### **WP7.3.2: (June '23) 2D Read Out**

#### Trasversal view

1 X-strips

21/6/2023

21/6/2023

**RD51 collaboration meeting - M. Giovannetti**

# WP7.3.2: Technology Transfer 2022

Step 0 - Detector PCB design @ LNF

- Step 1 CERN INFN DLC sputtering machine @ CERN (+INFN)

- delivery foreseen by the end of Oct. 2022

- INFN crew tbd & trained

- Step 2- Producing readout PCB by **ELTOS**

- pad/strip readout

- Step 3 DLC patterning by CERN

- photo-resist  $\rightarrow$  patterning with BRUSHING-machine

- Step 4 DLC foil gluing on PCB by  $\ensuremath{\textbf{CERN}}$

- double 106-prepreg  $\rightarrow 2x50\mu m$  thick

- PCB planarizing w/ screen printed epoxy  $\rightarrow$  single 106-prepreg

- Step 5 Top copper patterning by **CERN** (in future by **ELTOS)**

- Holes image and HV connections by Cu etching

- Step 6 Amplification stage patterning by  $\ensuremath{\textbf{CERN}}$

- PI etching  $\rightarrow$  plating  $\rightarrow$  ampl-holes

- Step 7 Electrical cleaning and detector closing @  $\ensuremath{\textbf{CERN}}$

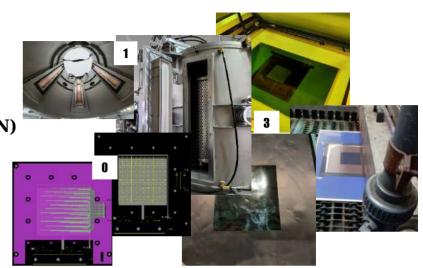

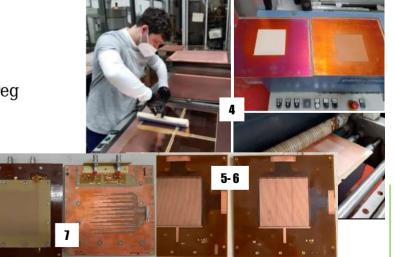

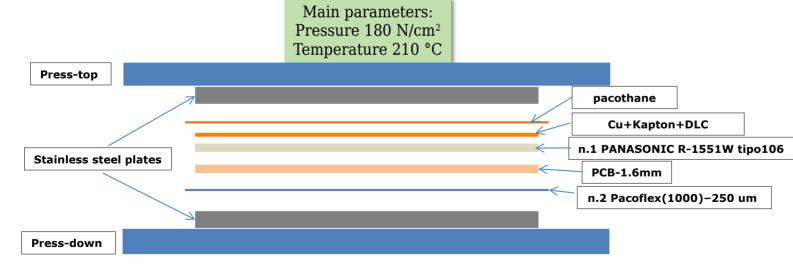

# WP7.3.2: Technology Transfer 2023

Step 0 - Detector PCB design @ LNF

109

- Step 1 CERN\_INFN DLC sputtering machine @ CERN (+INFN)

- <u>delivered</u> at the end of Oct. 2022

- **INFN** crew tbd & trained

- Step 2- Producing readout PCB by **ELTOS**

- pad/strip readout

- Step 3 DLC patterning by  $\ensuremath{\textbf{ELTOS}}$

- photo-resist  $\rightarrow$  patterning with BRUSHING-machine

- Step 4 DLC foil gluing on PCB by  $\ensuremath{\textbf{ELTOS}}$

- double 106-prepreg  $\rightarrow 2x50\mu m$  thick

- \* PCB planarizing w/ screen printed epoxy  $\rightarrow$  single 106-prepreg

- Step 5 Top copper patterning by  $\ensuremath{\textbf{CERN}}$  (in future by  $\ensuremath{\textbf{ELTOS}}\xspace$

- Holes image and HV connections by Cu etching

- Step 6 Amplification stage patterning by CERN

- PI etching  $\rightarrow$  plating  $\rightarrow$  ampl-holes

- Step 7 Electrical cleaning and detector closing @ CERN

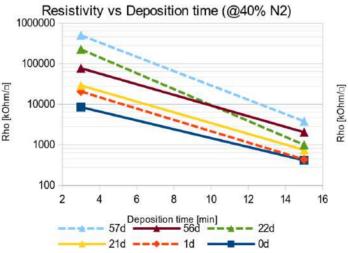

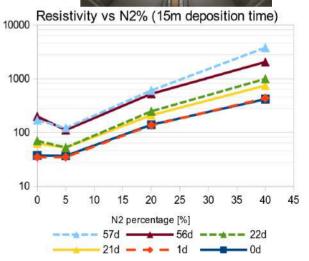

## WP7.3.2: update on the CERN-INFN DLC machine

$\mathbf{31^{st}~Oct.~2022}$  – Delivered  $\mathbf{31^{st}~Oct.~-4^{th}~Nov.~2022}$  – Commissioning & test training  $\mathbf{21^{st}~-23^{rd}~Nov.~2022}$  – First DLC sputtering test

- Ar + N<sub>2</sub> doping (increase sp<sup>3</sup> bonds  $\rightarrow$  resistivity)

- $19^{\rm th}$   $28^{\rm th}$  Jun. 2023 Second DLC sputtering test

- Ar +  $C_2H_2$  doping (study H presence in the plasma)

Some technical features:

- Flexible substrates up to 1.7m×0.6m

- **Rigid** substrates up to 0.2m×0.6m

**Five cooled target holders**, arranged as two pairs face to face and one on the front, equipped with five shutters.

The machine shall be able to **sputter or co-sputter different materials,** in order to create a coating layer by layer or an adjustable gradient in the coating.

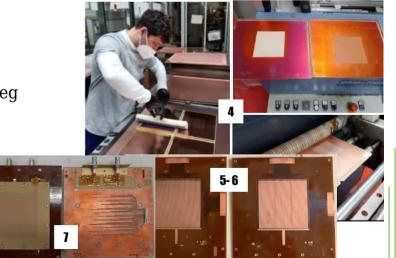

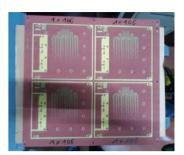

# WP7.3.2: Mar.'23 ELTOS production – DLC patterning

Step 2:

1) **PCB** production

#### <u>Step 3:</u>

- 2) Photoresist **lamination** for DLC protection

- 3) Photoresist **development**

- 4) **DLC patterning** with brushing machine (@CERN different approach: JET-SCRUBBING)

| DLC    |  |

|--------|--|

| Kapton |  |

| Cu     |  |

# WP7.3.2: Mar.'23 ELTOS production – DLC-foil gluing

### Step 4: Cu-Kapton-DLC gluing on PCB

**Goal:** 16 PEP-dot detectors (9×9mm<sup>2</sup> pad R/O), with **different pre-preg thickness:** systematic study of signal **pulse width as a function of coupling capacitance** between DLC and R/O pad.

Waiting for shipment to CERN and detector finalization (Step 5-7)

| Pre-preg | Δx [µm] |

|----------|---------|

| 106      | 50      |

| 1080     | 75      |

| x2 106   | 100     |

| x2 1080  | 150     |

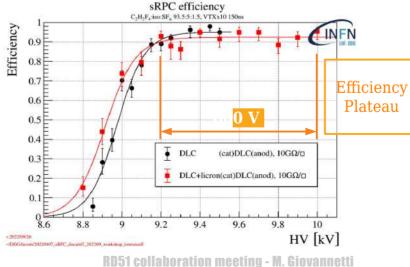

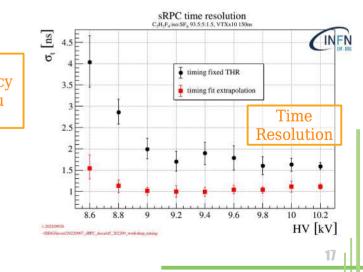

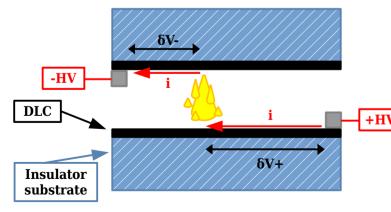

# sRPC – an MPGD-tech based RPC

#### DLC-based RPC:

- From bulk resistivity to surface resistivity: easy tunable resistivity w.r.t. bakelite or glass

- μ-RWELL inspired

High Rate schemes

- Flexible substrate

A promising novel technology, from MPGD material and technology experience.

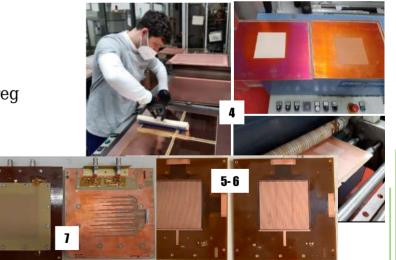

### WP7.3.2 – Summary

The activity of WP7.3.2 task proceeds on two parallel paths:

- 1) The **industrialization** of a part of the construction steps of the μ-RWELLs at the **ELTOS** company (Arezzo IT), in close **collaboration** with the **CERN-EP-DT-MPT** Workshop:

- Advances in the TT; **more contruction steps** performed by ELTOS

- Detector finalization (Kapton Etching, ...) performed at CERN

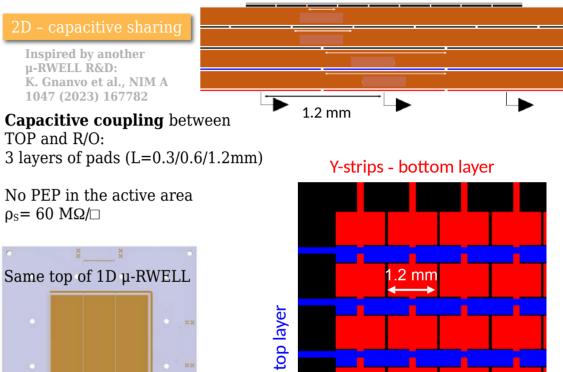

- 2) The R&D with CERN on the various  $\mu$ -RWELL layouts is focusing on different items:

- Design/optimization of the PEP layout  $\rightarrow$  **PEP-dot** (97% geom. acceptance)

- Design of two **2D strip R/O** (capacitive sharing and top strip patterned)

- Prototype gain characterization with X-ray @LNF-INFN

- Beam Test in **June'23 in H8-SpS** for all the new prototypes.

### WP7.3.2 – Summary

The activity of WP7.3.2 task proceeds on two parallel paths:

- 1) The **industrialization** of a part of the construction steps of the μ-RWELLs at the **ELTOS** company (Arezzo IT), in close **collaboration** with the **CERN-EP-DT-MPT** Workshop:

- Advances in the TT; **more contruction steps** performed by ELTOS

- Detector finalization (Kapton Etching, ...) performed at CERN

- 2) The R&D with CERN on the various  $\mu$ -RWELL layouts is focusing on different items:

- Design/optimization of the PEP layout  $\rightarrow$  **PEP-dot** (97% geom. acceptance)

- Design of two **2D strip R/O** (capacitive sharing and top strip patterned)

- Prototype gain characterization with X-ray @LNF-INFN

- Beam Test in **June'23 in H8-SpS** for all the new prototypes.

**Spare**

21/6/2023

RD51 collaboration meeting - M. Giovannetti

20

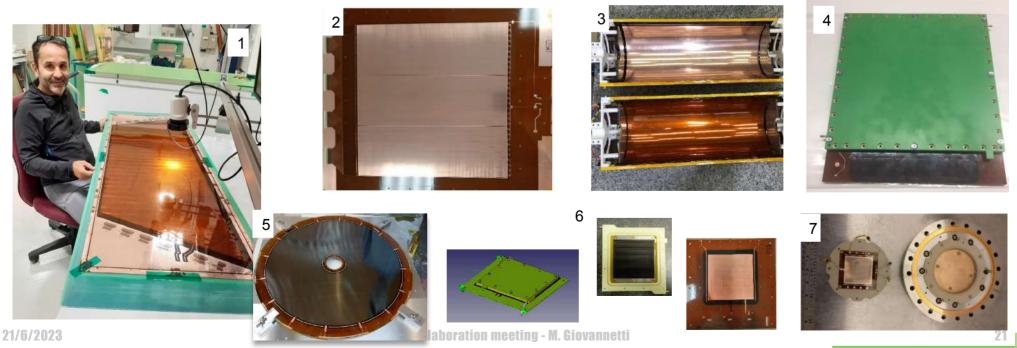

## **µ-RWELL technology spread**

The  $\mu\text{-}Resistive$  WELL is proposed in

- 1. CLAS12 @ JLAB: the upgrade of the muon spectrometer

- 2. X17 @ n\_TOF EAR2: for the amplification stage of a TPC dedicated to the detection of the X17 boson

- 3. TACTIC @ YORK Univ.: radial TPC for detection of nuclear reactions with astrophysical significnace

- 4. Muon collider: hadron calorimeter

- 5. CMD3: uRWELL Disk for the upgrade of the tracking system

- 6. URANIA-V: a project funded by INFN-CSN5 for neutron detection,

- 7. UKRI: neutron detection with pressurized <sup>3</sup>He-based gas mixtures

#### **PEP: Patterning - Etching - Plating**

- **Grounding from top** by kapton etching and plating

- Scalable to large size

Unitary cell. **black** - the exposed kapton is visible.

RD51 collaboration meeting - M. Giovannetti

22

**RD51** collaboration meeting - M. Giovannetti

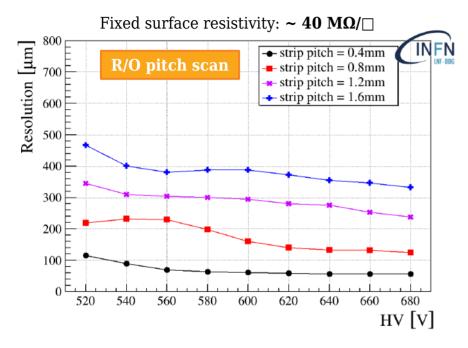

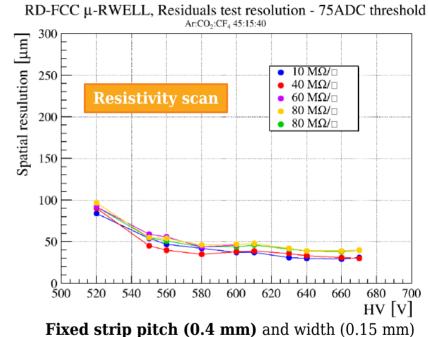

## **µ-RWELL: DLC charge spread**

Need to reduce # FEE channels = Increase the R/O pitch

As expected: reduction of the space resolution.

#### No effects in this resistivity range.

$\rightarrow$  DLC resistivity uniformity is not a crucial parameter Near future: charge dispersion through different R/O architecture  $\rightarrow$  capacitive sharing R/O

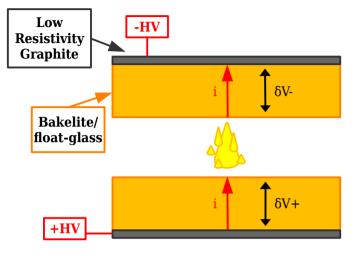

# **Bulk RPC vs Surface RPC**

### **Classical RPCs**

- Bulk resistivity electrodes (bakelite, float-glass, ...)

- Recovery time proportional to **volume resistivity, electrode thickness**

- $\circ \quad \tau = \rho_V \epsilon_0 (\epsilon_r + 2d/g)$

- Low volume resistivity and thin electrodes, together with the reduction of the gas gain (⊕high gain low noise pre-amp) is the standard recipe to increase the detector rate capability.

### **sRPCs - surface RPC**

- Surface resistivity electrodes manufactured with sputtering techniques of Diamond-like-carbon (DLC) on flexible supports

- High density current evacuation schemes, similar to those used for resistive MPGD (μ-RWELL and MicroMegas), can be implemented to improve the rate capability of the detector

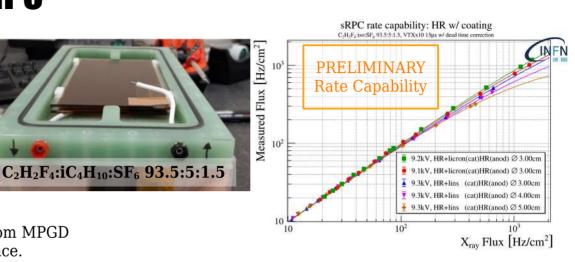

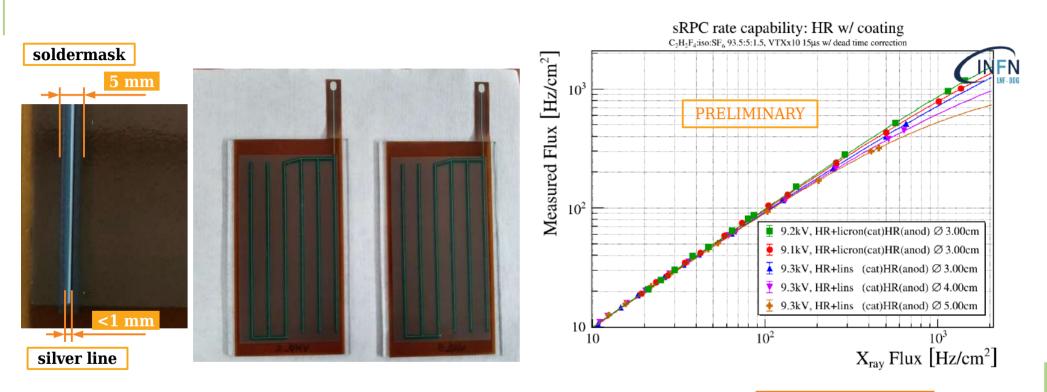

# High Rate layout – preliminary results

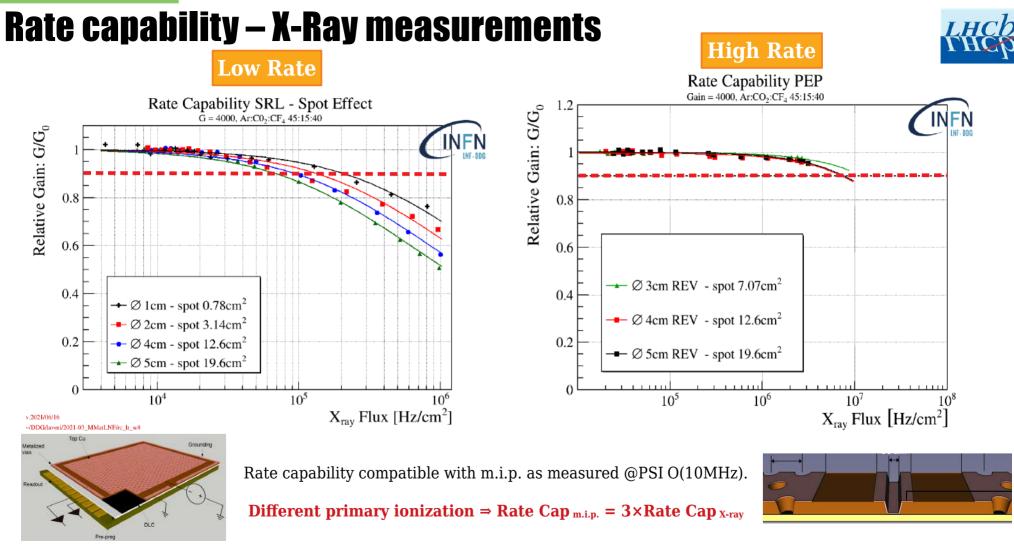

A **preliminary** measurement of the **rate capability** (defined as the radiation flux corresponding to an efficiency drop of 20%) of the high-rate layout has been **performed** by irradiating the detector **with a 5.9 keV X-ray gun** with a spot size comparable with the pitch of the conductive grid realized on the DLC ( $\rho_{DLC} \approx 1.6 \text{ G}\Omega/\Box$ ).

Rate capability of ~1 kHz/cm<sup>2</sup> with X-ray