# Neubauer Group Overview

### Dewen Zhong (UIUC)

NSF Site Visit July 11-12 2023 https://indico.cern.ch/event/1282754

### Mark Neubauer

#### Markus Atkinson (Postdoc)

GNN-based EF tracking

UNIVERSITY OF

Analog AI, ML Boosted WW tagging, HH/SH searches in bbWW decay channel

ILLINOIS NESA

#### Casey Smith (ECE, Engineer)

GNN-based EF tracking on FPGA, VHDL design

#### Avik Roy (Postdoc)

Explainable AI, FAIR, Anomaly-aware ML for trigger, Vector-like quark searches

#### Santosh Parajuli\* (Postdoc)

GNN-based EF tracking

#### Jared Burleson\* (PhD student)

GNN-based EF tracking, Vector Boson Scattering, Boson Polarization-aware ML

#### Ben Galewsky (NCSA Software Engineer)

Caching, Columnar Data

Delivery (ServiceX)

#### Jiangcong Zeng (PhD student)

Vector Boson Scattering in semileptonic decay channel

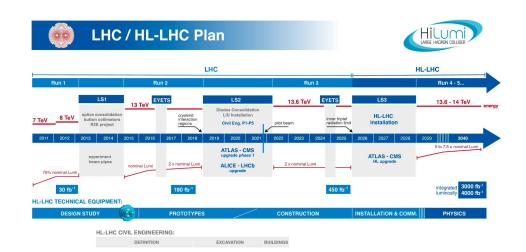

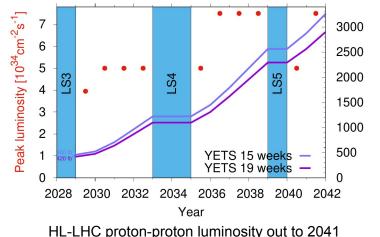

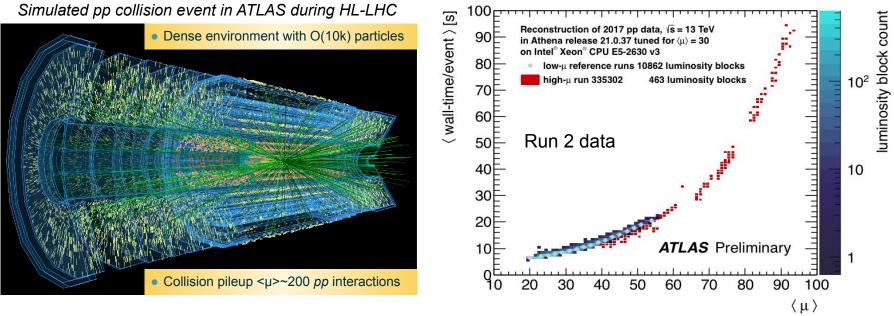

## **HL-LHC Computing challenge**

Efficient computational strategies are paramount for devices in resource-limited settings, particularly within high-energy physics experiments.

During the HL-LHC era, 10x more data per second than Run 1 & 2.

# Tracking challenge

Event reconstruction is a computationally-challenging problem for the (HL)-LHC  $\rightarrow$  Critical element for high-quality physics

• Particle tracking takes ~40% of the reconstruction time

# **GNNs for Tracking**

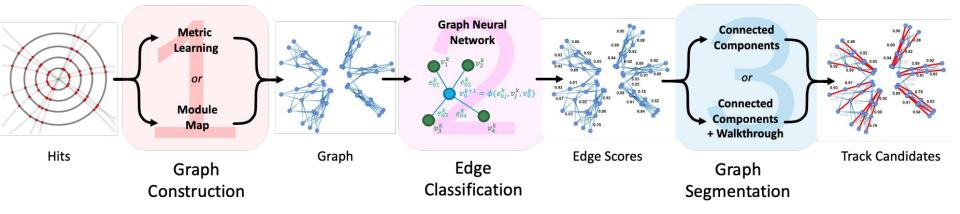

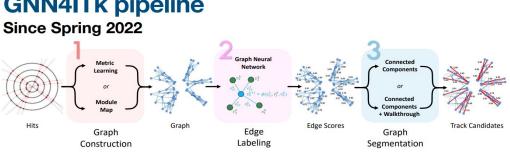

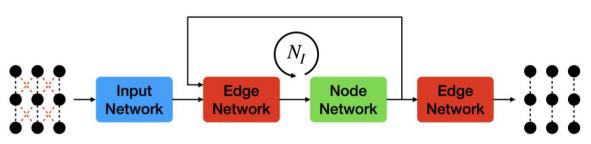

- Graph Neural Networks (GNNs) are a class of geometric deep learning methods for modeling data dependencies via message passing over graphs

- Detector measurements are represented as nodes. Nodes are associated with each other by learned edges that represent charged particle trajectories

# **Event Filter GNN Tracking Efforts**

#### **FPGA Strengths over GPUs:**

- low-latency inference

- reduced power consumption

### Effort to convert python code for firmware implementation:

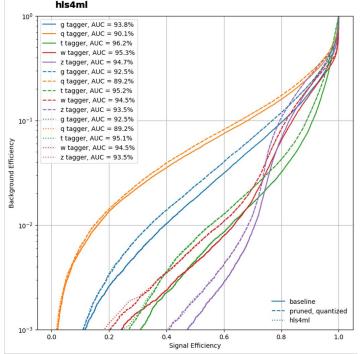

- Use HLS4ML or FINN (for metric learning and GNN) using ITk data, already explored on TrackML (<u>Elabd</u> et. al (2022))

- Write VHDL code "from scratch" (for module map and final track building)

See: Ju et al. (2021) and CTD (2022) for more info

#### **Ongoing and Future Efforts:**

- Concerns of limited resources encourages new FPGA studies

- Subgraph construction in regions of detector for module map

- Quantization Aware Training used for metric learning MLP

- Pruning studies on metric learning significant reduction in model size at maintained efficiency (see <u>CHEP (2023)</u> )

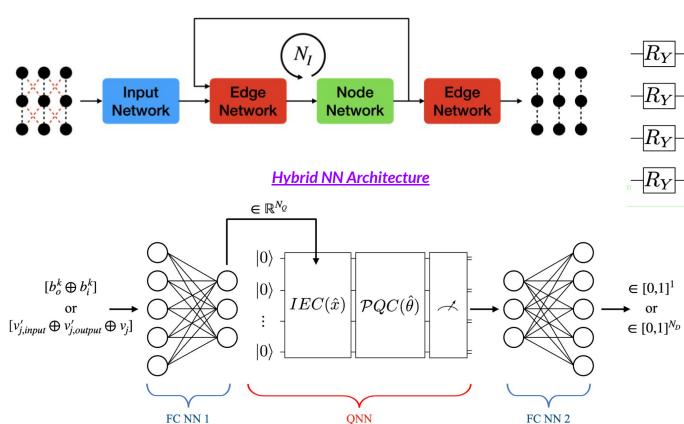

## **Hybrid Approach to GNN tracking**

With support from the Illinois Quantum Applications Program, we are working to build on our GNN tracking with classical GNNs and the prior work by others on Quantum GNNs (QGNNs, e.g. <u>C. Tüysüz, et al</u>) to develop a *Hybrid Neural Network* (combining classical & quantum networks) approach

#### **QGNN Architecture**

25.13

### Hybrid Neural Network approach to Tracking

**QGNN** Architecture

Previous study limited to QC simulations (and up to 16 qubits), mainly due to thousands of circuit executions required by the model

Also no noise included in the simulations

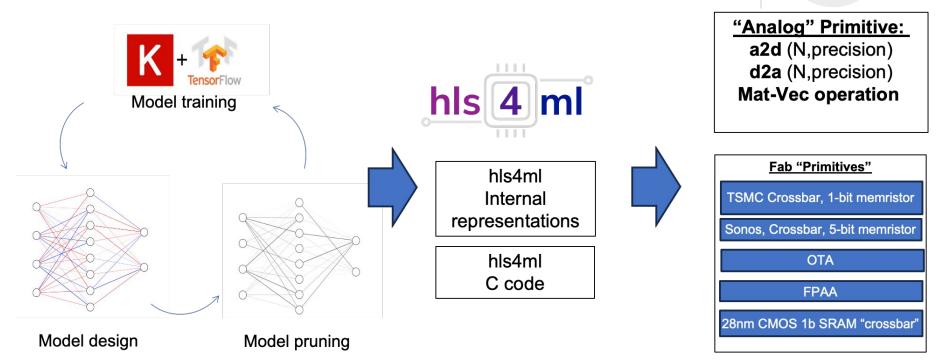

**hIs4mI** is a firmware implementations of machine learning algorithms using high level synthesis language (HLS) in FPGAs with ultra low latency.

- Simplify the hardware implementation process.

- Support for popular machine learning libraries.

- Compatibility with diverse hardware platforms such as FPGAs and ASICs.

- Deploy models in real-time and embedded applications.

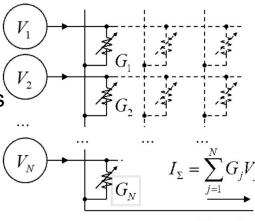

### Analog Al

Application of analog computing techniques to perform artificial intelligence (AI) tasks.

- Analog computing operates on continuous physical quantities, such as voltages or currents.

- Inherent parallelism and efficiency of analog computations

- More energy-efficient, Lower latency to accelerate AI algorithms

Working on new tools for Analog AI in hls4ml

- **People Involved**: Neubauer, Zhong (UIUC) with collaborators from UIC, FNAL and the <u>Discovery</u> <u>Partners Institute</u>

- In early stage: starting with a simple MLP primitive implemented on a crossbar array

- Synergies with memristors and CMOS devices also being explored

### **Mixed Analog/Digital Pathway**

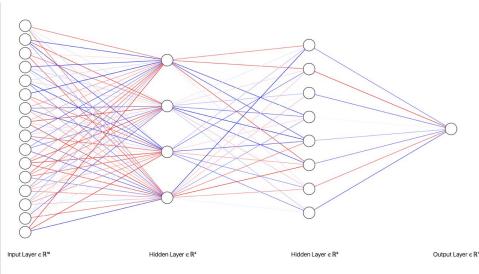

### **Machine Learning architectures**

Custom ANN model

- 16 inputs, with full connecting 4 and 8 nodes Hidden layers and output is 1

- Quantization weight and activation function of NN model • and setup output node to 4 bits

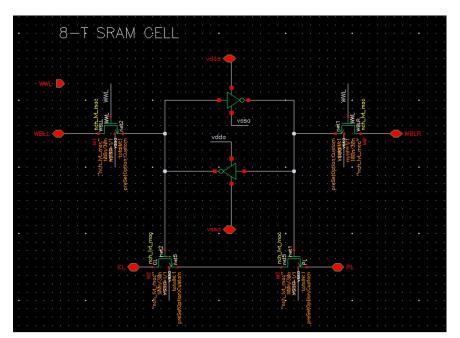

### 8-T SRAM-Unit Cell

#### Based off design

- Mf-net: Compute-in-memory sram for multi-bit precision inference using memory-immersed data conversion and multiplication-free operators

- MC-CIM: Compute-in-Memory With Monte-Carlo Dropouts for Bayesian Edge Intelligence

### **First Layer Analog Representation**

Basic Matrix for fc1 layer:

- 16 4-bits input (16 columns)

- 4 4-bits output

- 4 1-bit bias (1 bias column)

All production lines charged are accumulated and summed horizontally bit by bits.

Each bit needs to be binary weight.

|                                                                                                                                     | Dense<br>fc1 | input: (16,)  |                            | ): ap_fixed<1,1>               | ]                     |

|-------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------|----------------------------|--------------------------------|-----------------------|

|                                                                                                                                     |              | output: (4,)  | bias (4,):<br>output (4,): | ap_fixed<1,1><br>ap_fixed<4,4> |                       |

| _                                                                                                                                   | 1.<br>       |               | ↓<br>↓                     |                                |                       |

| 16:4÷bit input (16<br>4:4-bit output<br>4:-1+bit bios (1:c<br>Nb:of SRAM<br>(16+1)x4x4:= 272                                        |              | ). the 4-bite | s tnput will be            | submitted and p                | rocessed sequentially |

|                                                                                                                                     |              |               |                            |                                |                       |

| - 3월:- 3월:- 3월:- 3월:- 3<br>- 3월:- 3월:- 3월:- 3월:- 3 |              |               |                            |                                |                       |

### **Expectation of analog ML and Goal**

- Using hls4ml to generate analog AI models and implement analog models to ML-based jet Tagger.

- Provide similar performances as digital hls4ml ML models.

Further work

- Complete the full analog representation for entire ANN model structure.

- Tuning and Optimize the analog AI model performance for High Energy Physic models and beyond.