# Thin planar pixel detectors for highest radiation levels

L. Andricek, M. Beimförde, E. Fretwurst, C. Gössling, G. Kramberger, G. Lindstroem, A. Macchiolo, M. Moll, H.-G. Moser, R. Nisius, R.H. Richter

R.H. Richter Semiconductor Laboratory MPI for Physics, Munich

» Proposal of a RD50 project

Institutes: CERN, Univ. Dortmund, Univ. Hamburg,

- J. Stefan Inst. Ljubljana, MPI Munich

- » Embedded within an ATLAS-Proposal for 3D integration

- » Study of charge collection before and after radiation on pixelated readout nodes with different geometries and different sensor thicknesses – Check out the limits of planar detectors

- » Status and plans

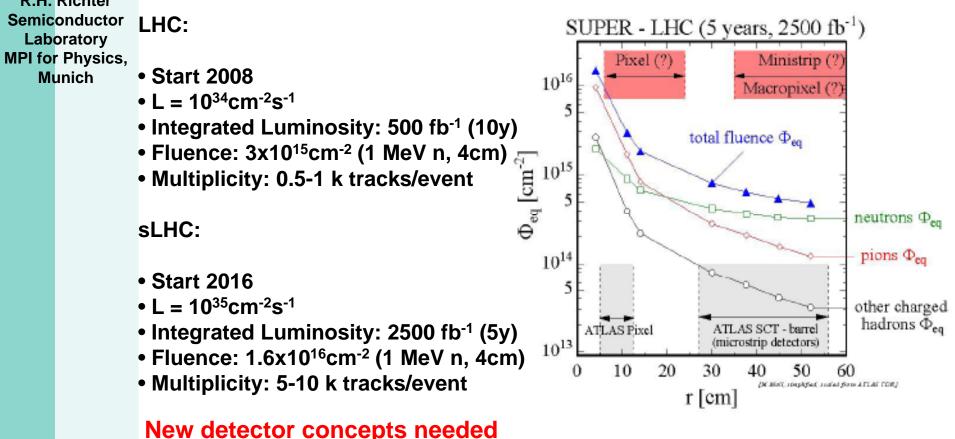

### **The Challenge**

#### Expected conditions at LHC and sLHC

#### 10th RD50 Workshop Vilnius 4-6th June 07

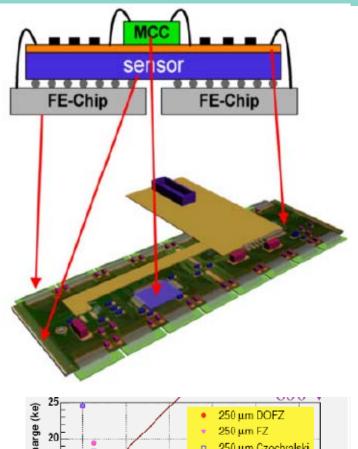

### **The ATLAS Pixel Detector**

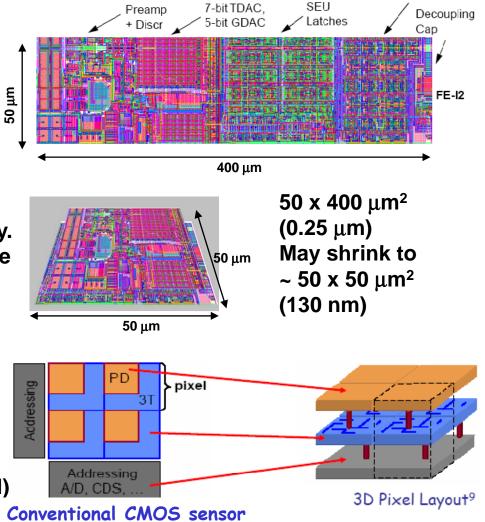

**Present Layout:**

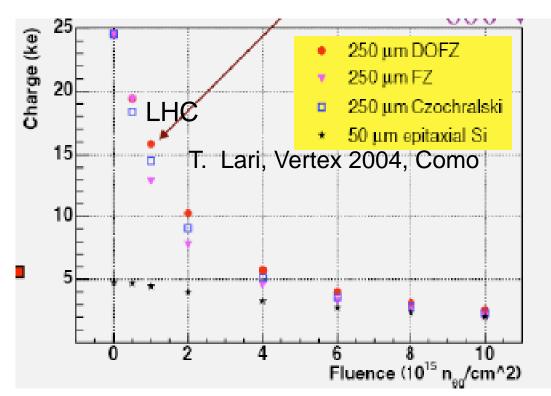

-250  $\mu$ m n-in-n pixel sensor -50 x 400  $\mu$ m<sup>2</sup> pixels -0.25  $\mu$ m rad hard ASIC -raf hard till 10<sup>15</sup> n/cm<sup>2</sup>

-Live fraction ~71% -Cantilever for readout -Sensor width 2x chip size: 16 mm -Large material overhead

At SLHC:

-V<sub>dep</sub> ~ 4200V -Charge collection: ~15% (at 10<sup>16</sup> n/cm<sup>2</sup>) -High occupancy

Main cost driver: Bump bonding !

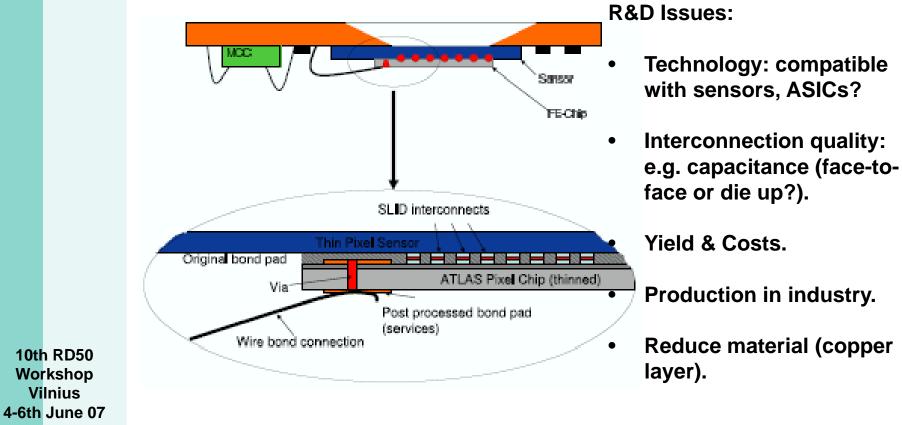

**R&D** for a novel pixel detector for SLHC

3D interconnection (sensor – electronics; electronics – electronics):

**R.H.** Richter Semiconductor Laboratory **MPI for Physics**, Munich

Alternative to bump bonding (fine pitch, potentially low cost?). New possibilities for ASIC architecture (multilayer, size reduction). Optimization of rad. hardness, speed, power. Impact on module design (ultra thin ASICs, top contact, 4-side abuttable).

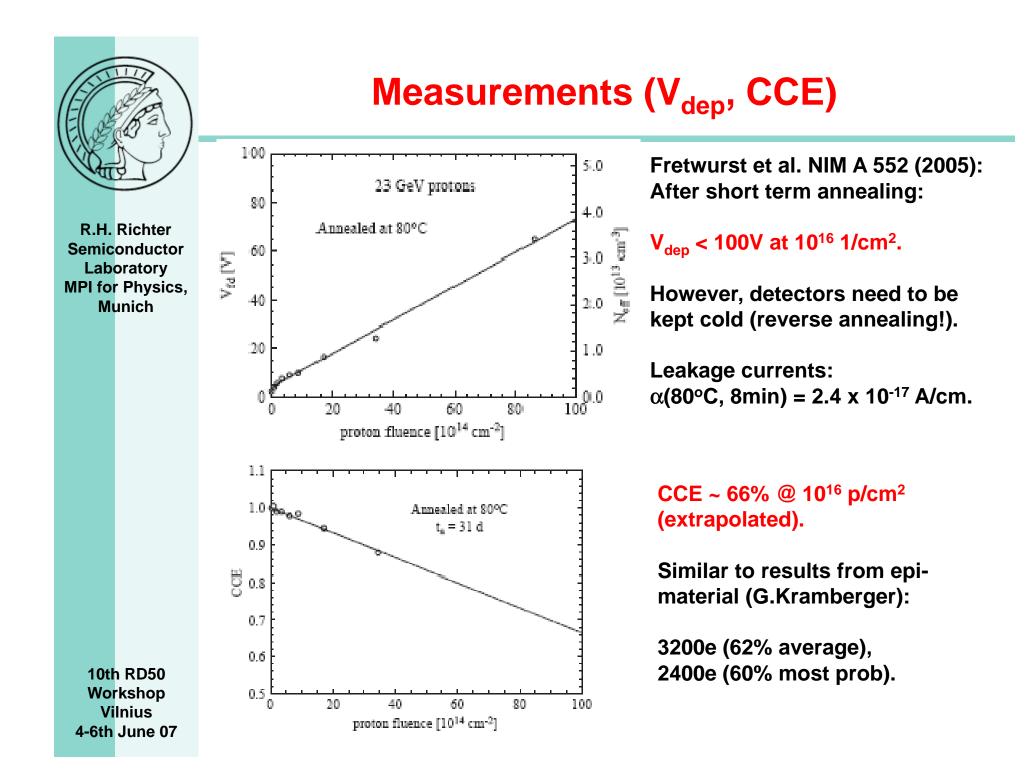

Can be operated at 10<sup>16</sup> n/cm<sup>2</sup> (V<sub>dep</sub>, I<sub>leak</sub>, CCE)?

10th RD50 Workshop Vilnius 4-6th June 07

Can lead to an advanced module design: rad hard with low material budget

### **3D Interconnection**

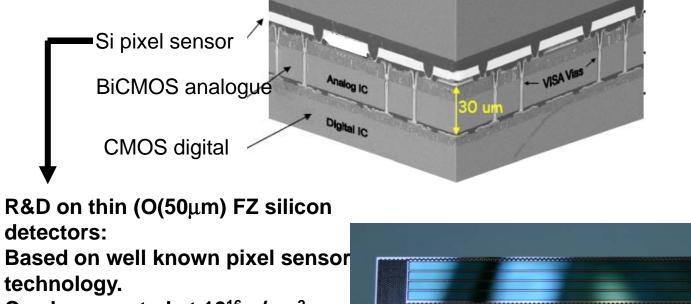

Two or more layers (="tiers") of thinned semiconductor devices interconnected to form a "monolithic" circuit.

**R.H.** Richter Semiconductor Laboratory **MPI for Physics**, Munich

Vilnius

Different layers can be made in different technology (BiCMOS, deep sub-µ CMOS, SiGe,....).

#### 3D is driven by industry:

- Reduces R,L and C.

- Improves speed.

- Reduces interconnect power, x-talk.

- Reduces chip size.

- Each layer can be optimized individually

#### For HEP: sensor layer: fully depleted Si Example: 2-Tier CMOS Sensor, **1024 x 1024 pixel**, pitch 8 μm by MIT-Lincoln Lab

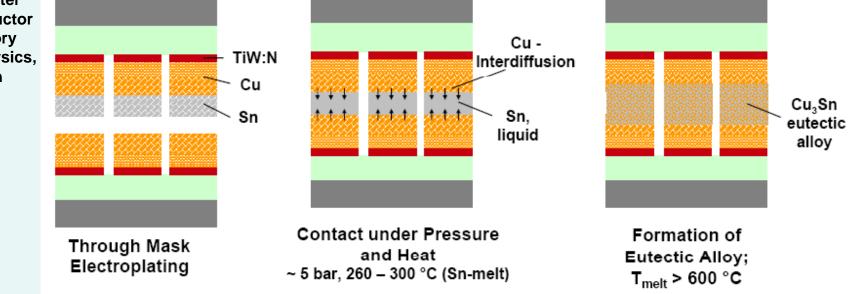

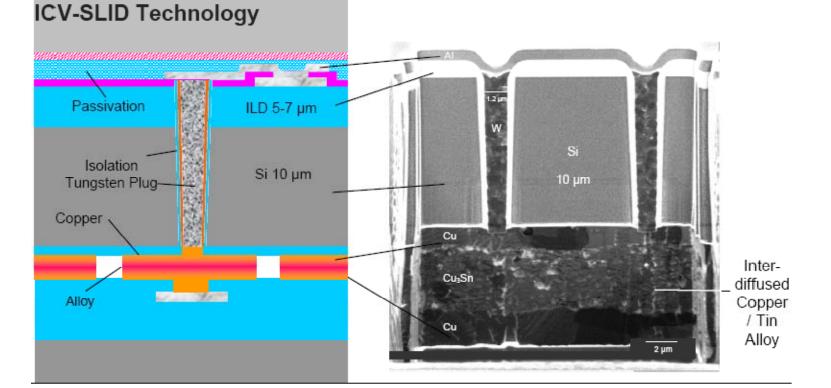

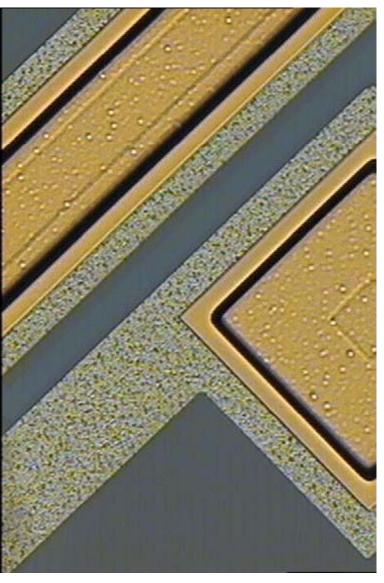

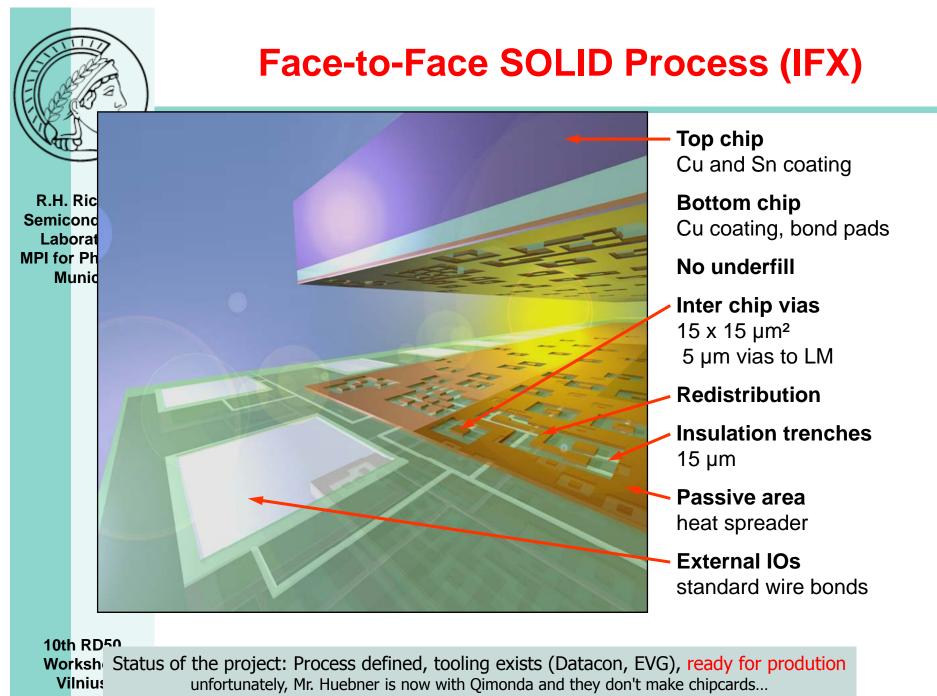

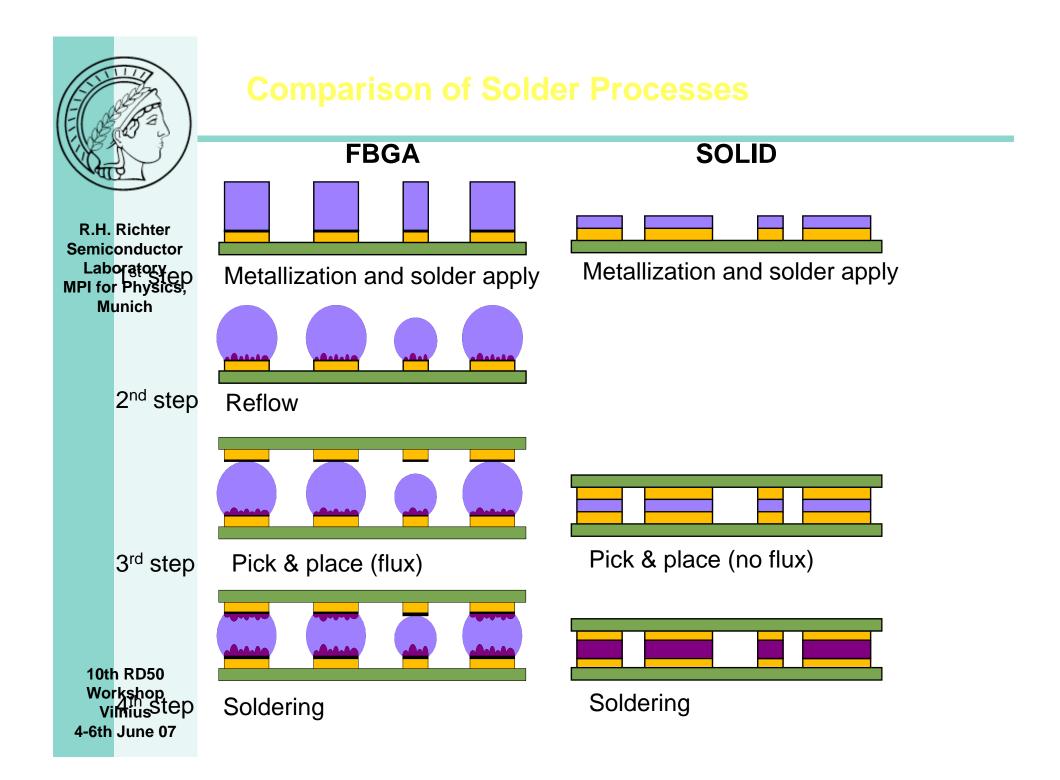

### **IZM SLID Process**

#### Metallization SLID (Solid Liquid Interdiffusion)

R.H. Richter Semiconductor Laboratory MPI for Physics, Munich

Alternative to bump bonding (less process steps "low cost" (IZM)).

Small pitch possible (<< 20 μm, depending on pick & place precision).</li>

Stacking possible (next bonding process does not affect previous bond).

Wafer to wafer and chip to wafer possible.

Fraunhofer

Institut

Zuverlässigkeit und

Mikrointegration

10th RD50

Workshop

Vilnius

4-6th June 07

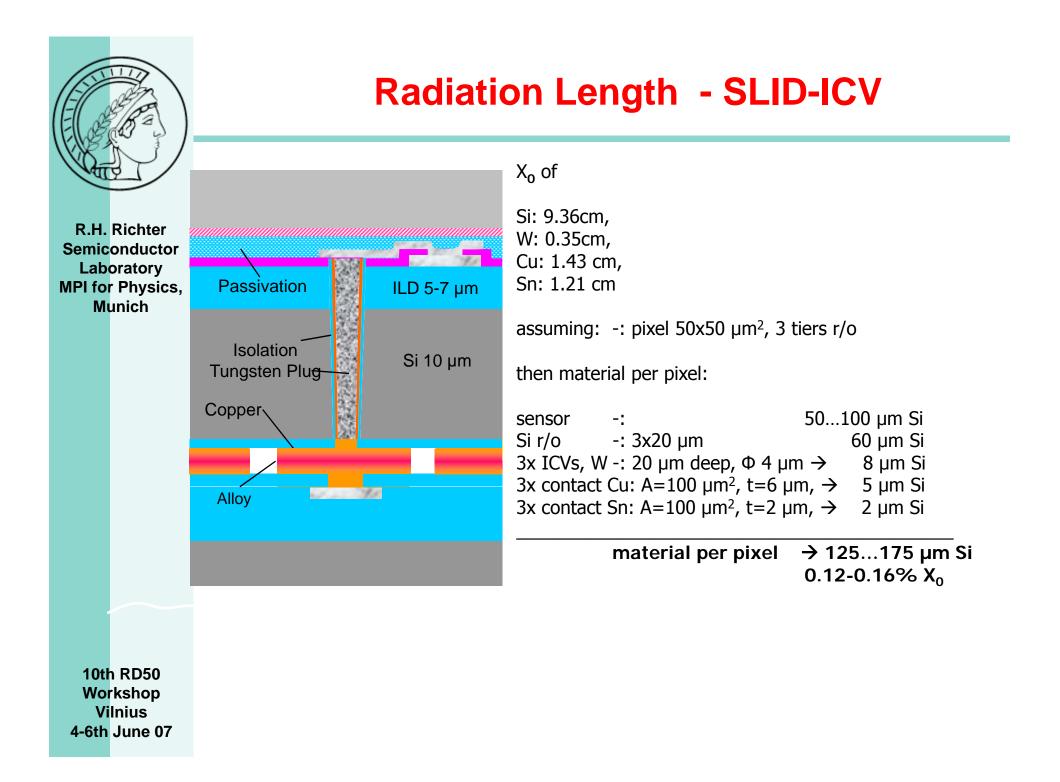

### **Through Silicon Vias**

#### **ICV** = Inter Chip Vias

Hole etching and chip thinning

Via formation with W-plugs.

Face to face or die up connections.

2.5 Ohm/per via (including SLID).

No significant impact on chip performance (MOS transistors).

### **Advantages of 3D**

**Multilayer electronics:**

Split analogue and digital part Use different, individually optimized technologies:

-> gain in performance, power,

speed, rad-hardness, complexity.

-> smaller area (reduce pixel size or more functionality).

4-side abuttable devices:

- -> no dead space.

- -> simpler module layout.

- -> larger modules.

(reduce complexity and material)

Conventional CMOS sensor (optical, similar: MAPS)

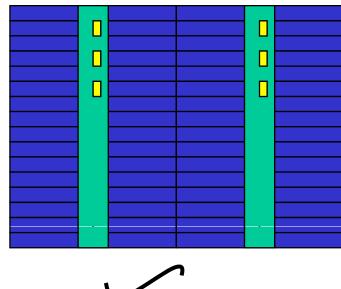

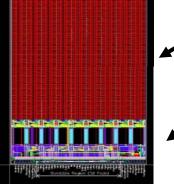

### Advantages even for single layer

Periphery, column logic, services

Periphery, column logic, services

Image: Service service

**Conventional Layout**

**3D Layout**

Make use of smaller feature size (gain space)

-> move periphery in between pixels (can keep double column logic)

- -> backside contacts with vias possible

- -> no cantilever needed, 4-side abuttable

10th RD50 Workshop Vilnius 4-6th June 07

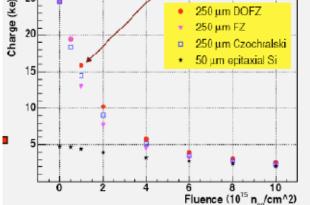

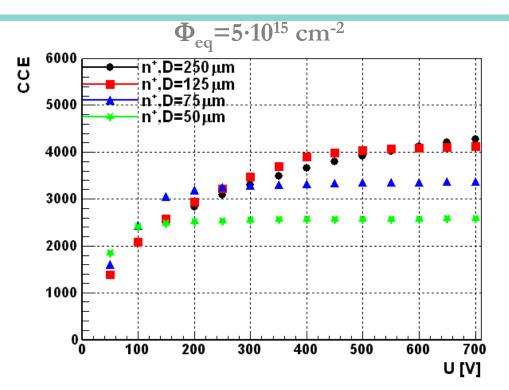

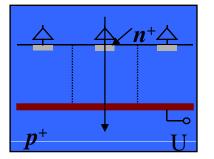

### **Motivation for Thin Detectors**

After 10<sup>16</sup> n/cm<sup>2</sup>:

V<sub>dep</sub> > 4000V (250 μm) -> operate partially depleted. Large leakage currents.

Charge loss due to trapping (mean free path ~ 25  $\mu$ m). I<sub>e</sub> > I<sub>h</sub> (need n-in-n or n-in-p) to collect electrons.

No advantage of thick detectors ->thin detectors: low V<sub>dep</sub>, I<sub>leak</sub> (and X<sub>0</sub>) However: small signal size is a challenge for the readout electronics

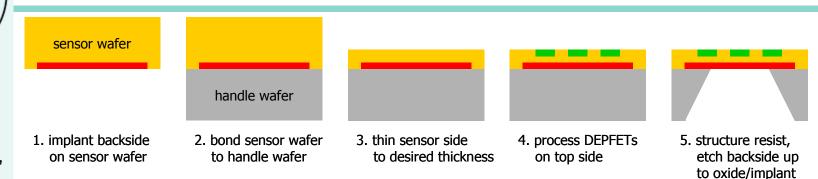

Sensor wafer: high resistivity d=150mm FZ wafer.

Bonded on low resistivity "handle" wafer".(almost) any thickness possible

Thin (50  $\mu$ m) silicon successfully produced at MPI.

- MOS structures - diodes

-No deterioration of detector properties, keep I<sub>leak</sub> <100pA/cm<sup>2</sup>

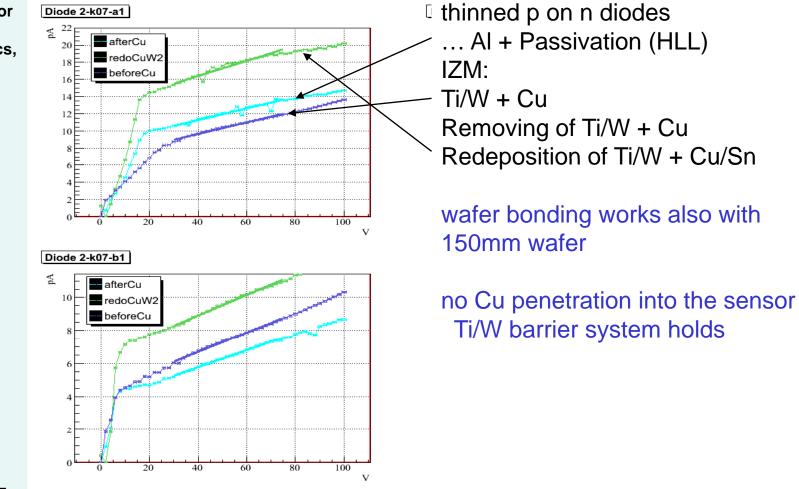

### **Pre tests and Plans**

Diode test wafers processed at HLL -Preparation for SLID process IZM -Diffusion barriers & Cu layers

ok

#### **RD50**

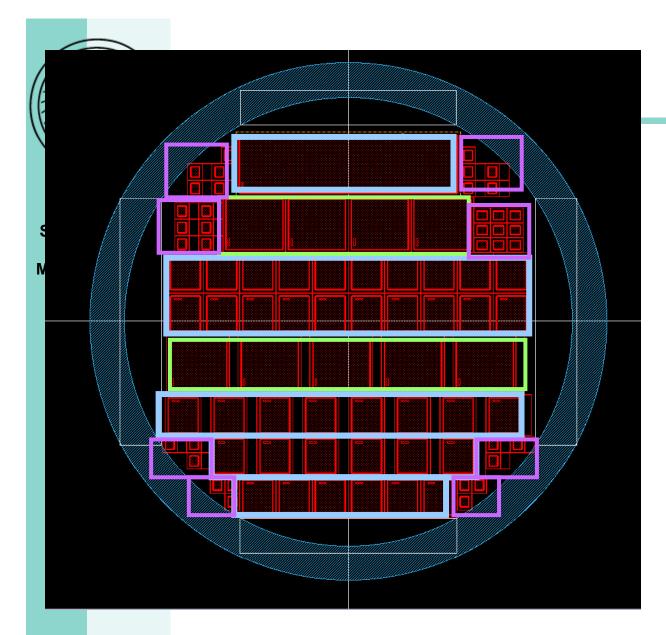

Production of thin pixel detectors ATLAS footprint, single chip size: start, summer 2007 -includes test structures for irradiations (diodes, strips, small pixel arrays)

Connection of wafer & ATLAS pixel chip using SLID: 2008

Full demonstrator (thinning, SLID, ICV): 2009

### Pre tests on 50µm thin 10mm<sup>2</sup> diodes

### before and after Cu/Sn deposition and after rework

R.H. Richter Semiconductor Laboratory MPI for Physics, Munich

### **Modular approach**

3D integration with SLID can be combined with any sensor concept

- N on P

- N on P (epi) Fz or MCz

- 3D sensor

**Prototyping at HLL:**

N on N technology, moderated pspray, no polyresistors if 6" p-doped material is available, some wafers P on N

3 thicknesses: 50µm, 100µm, 150µm

### **Test program**

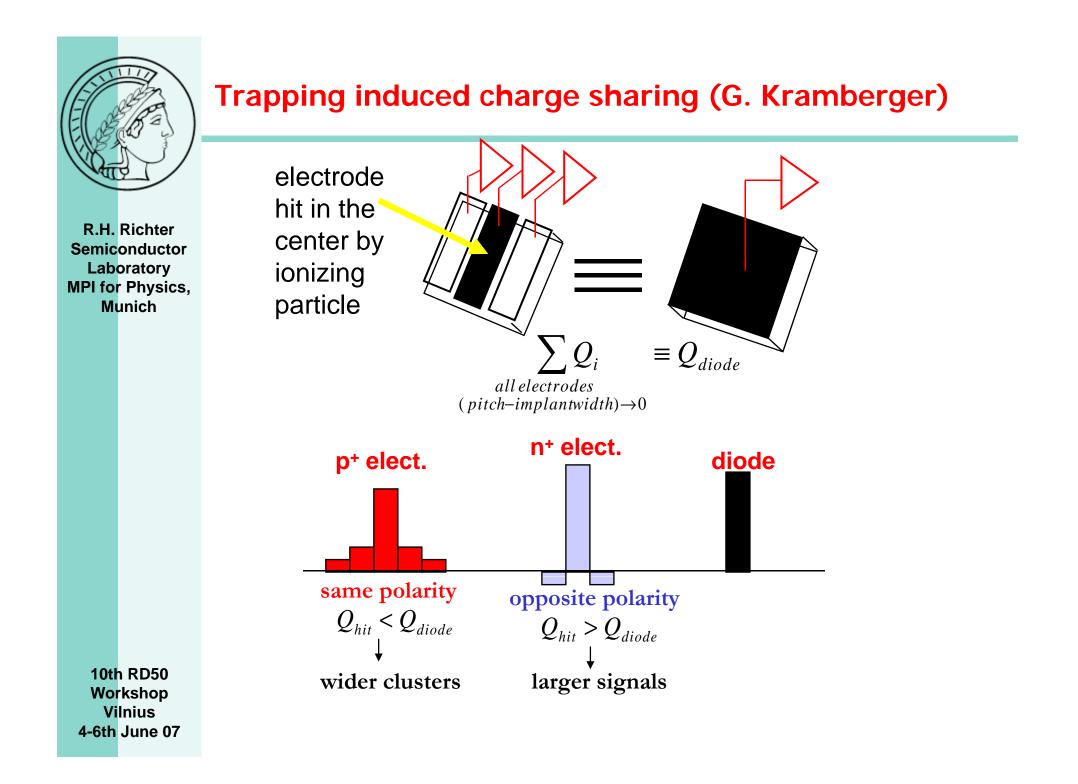

Charge collection and sharing vs readout node geometry, bias voltage, irradiation

R.H. Richter VS rea Semiconductor Laboratory MPI for Physics, Munich 4 readout chips

- ATLAS-pixel chip: 400x50µm<sup>2</sup>, binary (ToT), SLID, rad hard, available Test structures: pixel (ATLAS geometry)

- SCT128, pitch adaptor, analogue, wire bonded after irradiation, available (Ljubljana)

Test structures: mainly short strips (different geometries)

- Interon-Chip (Einar Nygard, Oslo), 10x10pixel, 200x50µm<sup>2</sup>, analogue, SLID, rad hard, to be designed

- Medipix: 55x55µm<sup>2</sup>, analogue, SLID, not rad hard, slow

#### QV plots (Simulations) – different detector thicknesses G. Kramberger (Schloss Ringberg 2007)

Similar Q-V characteristics up to full depletion!

Thinner sensors are beneficial at lower voltages

the more voltage you can apply the more

beneficial are thicker detectors

10th RD50 Workshop Vilnius 4-6th June 07 pixels to be read-out by the FE ATLAS Chip and test diodes

pixels to be read-out by the MEDIPIX2 Chip and short strips

pixels to be read-out by the Interon Chip

For each type of read-out chip two different geometries of the pixels cells are foreseen to allow for:

- a) standard wire bonding on the pads for the services of the chip

- b) access to the pad through a via etched from the backside

### Schedule

- » Begin of pre processing July 07 (definition of chips active areas for backside implantation)

- » Waferbonding: July-August

- » Final design: Aug. 07

- » Production start: Sept. 07

- » First samples: begin of 2008

### Summary

#### Thin detectors

- ≻Keep V<sub>dep</sub> low.

- ≻Keep I<sub>leak</sub> low (power).

>Reduce  $X_0$  (if this is not an issue: backside etching not necessary, simpler fabrication)

- ➢ Results on radiation hardness and CCE encouraging.

- >Large scale industrial production possible.

- > Thickness can be adapted to radius (fluence) -> parameter!

**R&D** topics:

- >Make real pixel detectors.

- >Irradiations, measurement of CCE.

- Optimize thickness

- >Charge sharing.

- >Optimize production process

10th RD50 Workshop Vilnius 4-6th June 07

#### New collaborators are welcome !

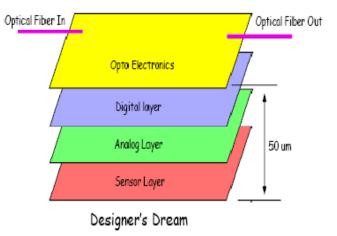

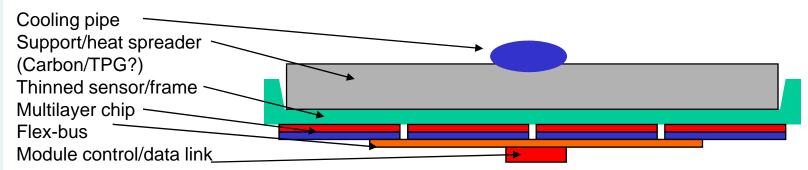

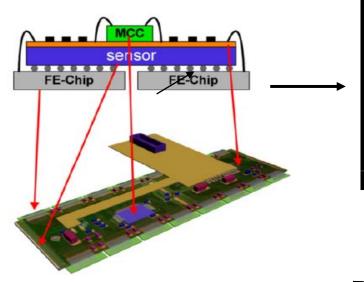

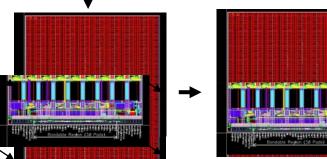

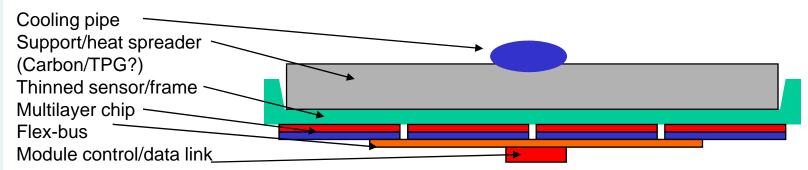

### **Conceptual Module Design**

#### "Designer's dream"

Two layer chip ("analogue" and "digital" layer)

Connected to thin detector using SLID small pixel size small pitch

Low material budget:

4-side abuttable ASICs large live fraction (-> 100%) larger modules less services and material overhead

10th RD50 Workshop Vilnius 4-6th June 07

further advantages if used with edgeless sensors

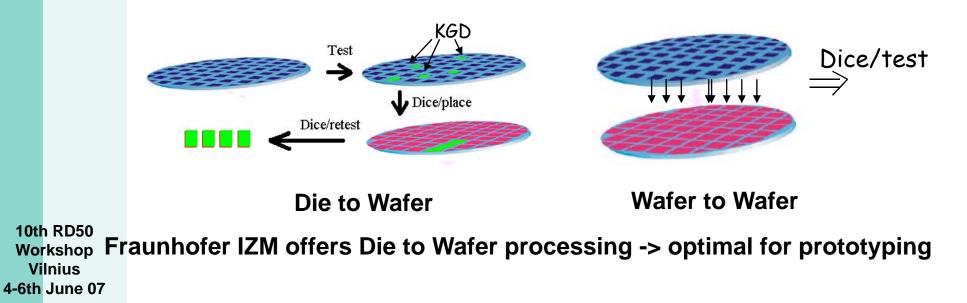

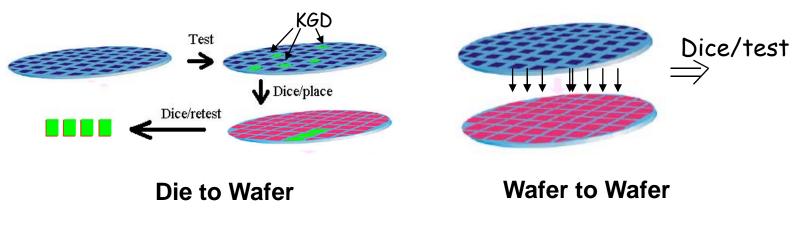

### **Two Different 3D Approaches**

#### Wafer to Wafer bonding

- Must have same size wafers

- Less material handling but lower overall yield

#### Die to Wafer bonding

- Permits use of different size wafers

- Lends itself to using KGD (Known Good Die) for higher yields

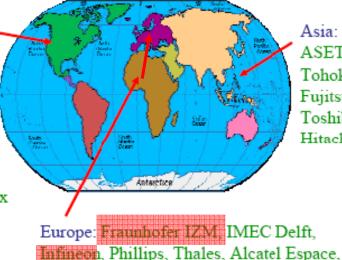

### World Wide Interest in 3D

USA Albany Nanocenter U. Of Kansas, U of Arkansas Lincoln Labs, AT&T MIT,RPI, RTI, TI IBM, Intel, Irvine Sensors Micron, Sandia Labs Tessera, Tezzaron, Vertical Circuits, Ziptronix

Asia: ASET, NEC, University of Tokyo, Tohoku University, CREST, Fujitsu, ZyCube, Sanyo, Toshiba, Denso, Mitsubishi, Sharp, Hitachi, Matsushita, Samsung

R. Yarema (Fermilab)

3D is discussed in the ITRS (International Technology Roadmap for Semiconductors) as an approach to improve circuit performance and permit continuation of Moore's Law.

NMRC, CEA-LETI, EPFL, TU Berlin

R&D driven by industry. Different approaches (solder, SOI, epoxy).

Fraunhofer Institut Zuverlässigkeit und Mikrointegration

10th RD50 Workshop Vilnius 4-6th June 07

MPI will work with Fraunhofer IZM, Munich.

Munich

### **IBM Press Release**

### the third-dimension

and the second of the

Breakthrough demonstrates viability of 3-D chip stacking technique for manufacturing

**ARMONK, N.Y., April 12, 2007** -- IBM today announced a breakthrough chip-stacking technology in a manufacturing environment that paves the way for three-dimensional chips that will extend Moore's Law beyond its expected limits. The technology - called "through-silicon vias" -- allows different chip components to be packaged much closer together for faster, smaller, and lower-power systems.

The IBM breakthrough enables the move from horizontal 2-D chip layouts to 3-D chip stacking, which takes chips and memory devices that traditionally sit side by side on a silicon wafer and stacks them together on top of one another. The result is a compact sandwich of components that dramatically reduces the size of the overall chip package and boosts the speed at which data flows among the functions on the chip.

"This breakthrough is a result of more than a decade of pioneering research at IBM," said Lisa Su, vice president, Semiconductor Research and Development Center, IBM. "This allows us to move

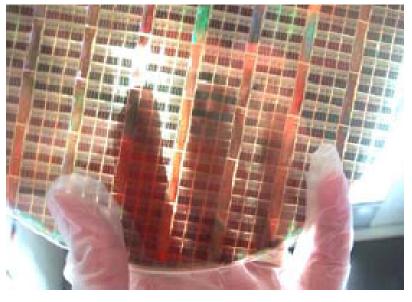

High-res image

**IBM extends Moore's Law to the thirddimension:** An IBM scientist holds a thinned wafer of silicon computer circuits, which is ready for bonding to another circuit wafer, where IBM's

### **Two Different 3D Approaches**

#### Wafer to Wafer bonding

- Must have same size wafers

- Less material handling but lower overall yield

#### Die to Wafer bonding

- Permits use of different size wafers

- Lends itself to using KGD (Known Good Die) for higher yields

10th RD50 Workshop Vilnius 4-6th June 07

IZM offers Die to Wafer processing -> optimal for prototyping

### IZM chip to wafer concept

3D System Integration

#### Handling Concept for Wafer-Level Chip-Scale Processing (1)

- · Placement of Chips on Handling Substrate

- Grid of Aligment Marks according to the Positions on the Target Wafer

- Processing of Chips on Wafer Scale

(e.g. cleaning prior to bond, thinning, backside metalization etc.)

- Transfer to Target Wafer

- Adjusted Stack Formation (Wafer-Flip)

- Removal of Handling Substrate

- Further Processing of new Stack (if necessary)

Dr. A. Klumpp

Fraunhofer Institut Zuverlässigkeit und Mikrointegration

IZN

FEE 2006, Perugia, Italy

### **Advantages for Module Design**

(facing sensor) Periphery Pipeline and control Bond pads (cantilever)

**Pixel area**

Control on top of pixel area. External contact from top. Contact pixels through vias: -> 4-side buttable.

-> No "cantilever" needed.

Larger module with minimal dead space.

10th RD50 Workshop Vilnius 4-6th June 07

Less support structures & services. Substantial material savings.

### **Conceptual Module Design**

#### "Designer's dream"

Two layer chip ("analogue" and "digital" layer)

Connected to thin detector using SLID small pixel size small pitch

Low material budget:

4-side abuttable ASICs large live fraction (-> 100%) larger modules less services and material overhead

10th RD50 Workshop Vilnius 4-6th June 07

further advantages if used with edgeless sensors

### **Proposed R&D Program**

- a) Test interconnection process with diode test structures

- b) Build demonstrator using ATLAS pixel chip and pixel sensors made by MPI

### **Summary**

3D interconnection offers a solution for highly integrated, complex, high performance pixel detectors

-Could be used with many sensor types (planar, 3D, DEPFET,.....) -Can combine different ASIC technologies

-Backside-connection of 4-side abuttable chips

-Thinning of ASICs is basic ingredient -> low mass!

-R&D driven by industry -> potentially cost effective solutions

-Several HEP groups started to look into 3D (Fermilab, MPI)

-MPI started a R&D program for the ATLAS sLHC upgrade:

•3D interconnection using IZM SLID and ICV processes

Thin FZ sensors ("standard" pixel sensors optimized for SLHC).

•3D Interconnection is an option for other sensor types (e.g. 3D detectors).

Inviting collaborators (especially ASIC experts)

10th RD50 Workshop Vilnius 4-6th June 07

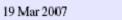

### ATLAS sLHC Upgrade R&D

#### B-layer: Highest radiation damage, look for new technology

- 3D-Silicon (Sherwood Parker, Cinzia Davia, et al):

- Test-beam results available; R&D proposal under review (currently being improved)

- Thin-silicon combined with 3D-interconnect technologies (Richard Nisius/MPI-Munich et al):

- Vias through si layers + replace bump bonding with solid-liquid diffusion

- Low bias V; low C + low signal --> still good S/N

- Gossip (Harry van de Graaf/NIKHEF et al)

- Gas detector on slimmed silicon pixel chip

- PO will set up a group to exploit common items, keep together, look at risk etc.

Nigel Hessey

4-6th June 07

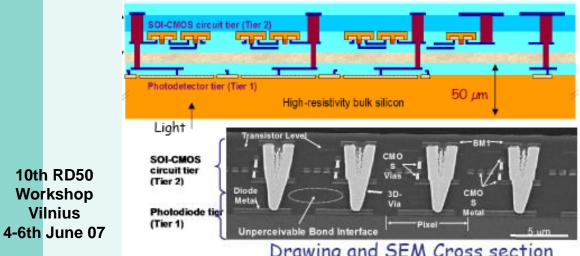

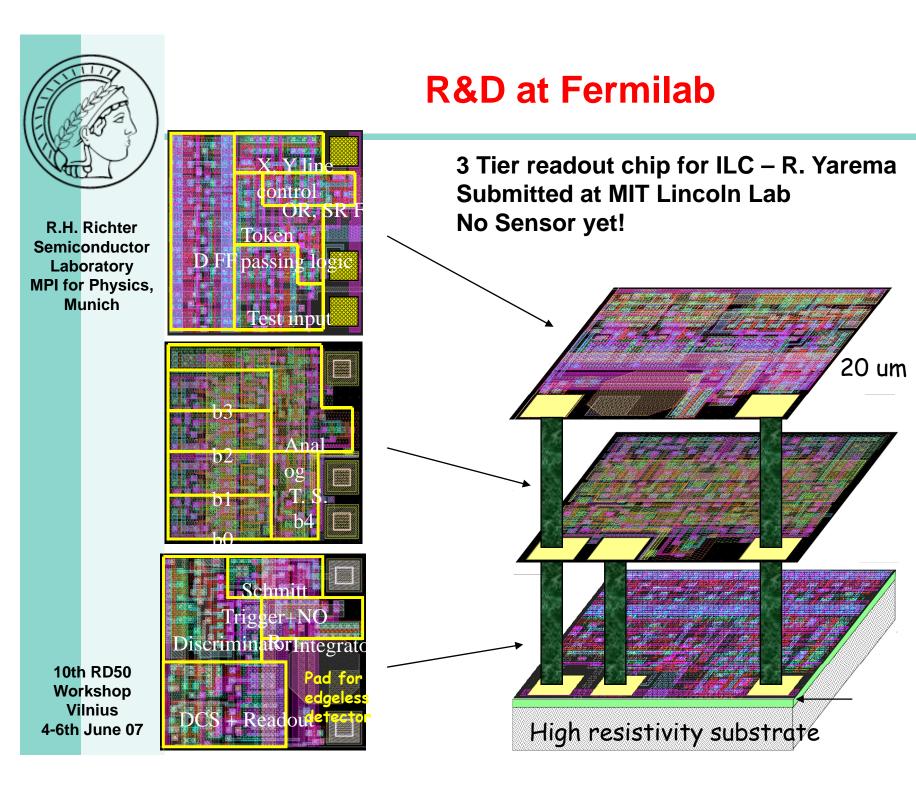

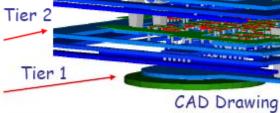

### **R&D** at MIT Lincoln Lab

7μm

## 3D Megapixel CMOS Image Sensor

- 1024 × 1024, 8 μm pixels

- 2 tiers

- Wafer to wafer stacking (150 mm to 150 mm)

- 100% diode fill factor

- Tier 1 p<sup>+</sup>n diodes in >3000 ohm-cm, n-type sub, 50 μm thick

- Tier 2 0.35 um SOI CMOS,

7 μm thick

- 2 μm square vias, dry etch, Ti/TiN liner with W plugs

- Oxide-oxide bonding

- 1 million 3D vias

- Pixel operability >99.999%

- 4 side abuttable array

SOI-CMOS circuit tier (Tier 2) Photodetector tier (Tier 1) 50 µm High-resistivity bulk silicon Light ansistor Lev SOI-CMOS circuit tier (Tier 2) Diode CMO Meta Photodiode tie Motal (Tier 1) Unperceivable Bond Interface

#### Drawing and SEM Cross section

#### 10th RD50 Workshop Vilnius 4-6th June 07

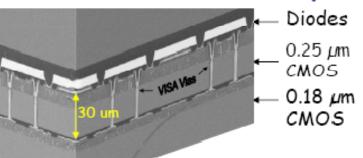

### **R&D** at MIT Lincoln Lab

### 3D Laser Radar Imager

3D Via

7 µm

**Completed Pixel Cross-Sectional SEM**

Tier-2: 3.3V SOI CMOS Lave

SEM Cross section

Tier-1: 26V Back Illuminated APD Layer

Design of the last

Tier-3: 1.5V SOLCMOS Lay

10 um

• 64 x 64 array, 30 µm pixels

3 tiers

- 0.18µm SOI

- 0.35 µm SOI

- High resistivity substrate diodes

- Oxide to oxide wafer bonding <sup>7 μm</sup>

- 1.5 µm vias, dry etch

- Six 3D vias per pixel

ILC VTX Workshop at Ringberg

Tier 3

R.H. Richter Semiconductor

Laboratory

**MPI for Physics**,

Munich

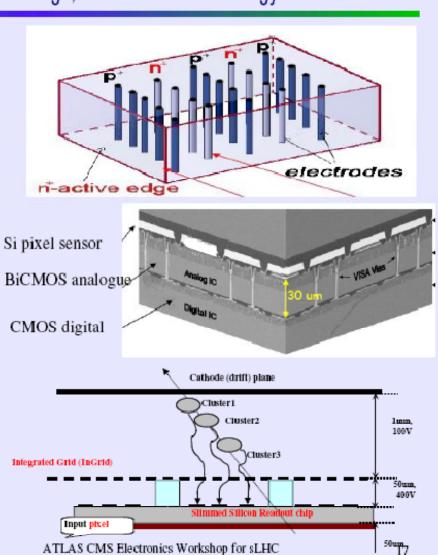

### **R&D** at MIT Lincoln Lab

# **3D Infrared Focal Plane Array**

Hacatte

alog IC

Digital IC

- 256 x 256 array with 30 μm pixels

- 3 Tiers

- HgCdTe (sensor)

- 0.25 µm CMOS (analog)

- 0.18 μm CMOS (digital)

- Die to wafer stacking

- Polymer adhesive bonding

- Bosch process vias (4 μm) with insulated side walls

- 99.98% good pixels

- High diode fill factor

Array cross section

slog Residue

Output

Logic

NBR

Riippie Counter

44---4

N BI Parallel

Digital Data Out

Analog Digital

CTIA

3 Tier circuit diagram

Infrared image

10th RD50 Workshop Vilnius 4-6th June 07

Detector