From Software to Hardware: An easy guide to accelerate algorithms for the HL-LHC upgrades of CMS Level-1 Trigger System

erc

**Funded by**

the European Union

The 42<sup>nd</sup> International Conference on High Energy Physics (ICHEP2024) - Prague, July 2024

Pelayo Leguina López – University of Oviedo, on behalf of the CMS Collaboration

## MOTIVATION

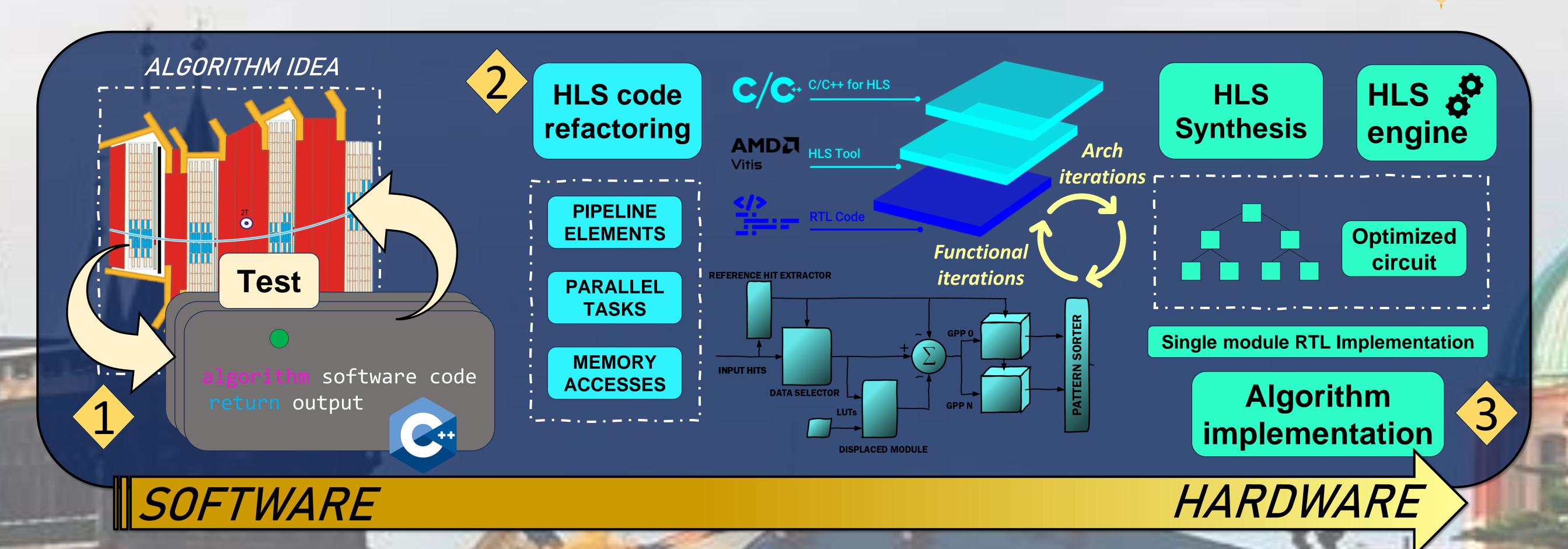

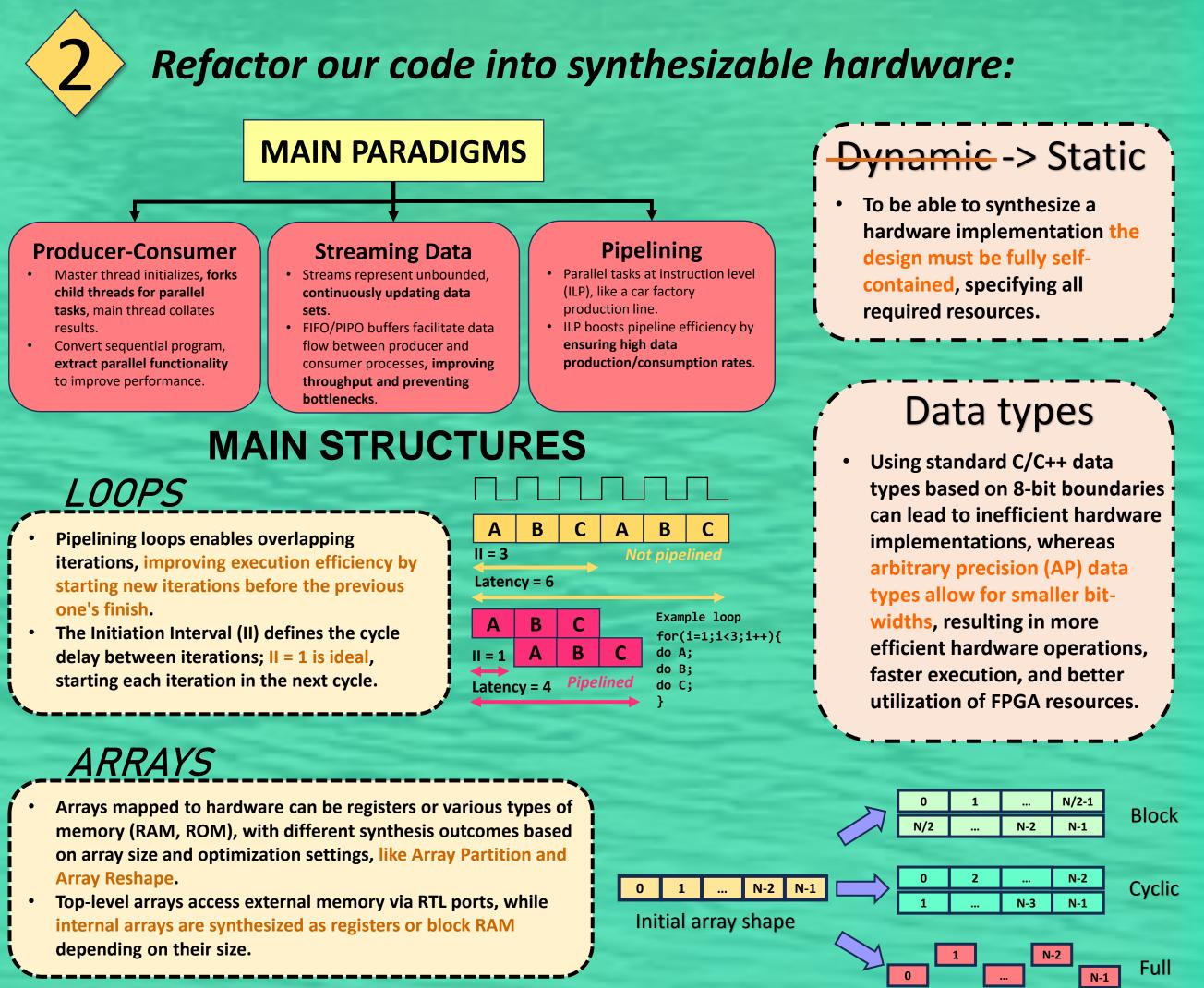

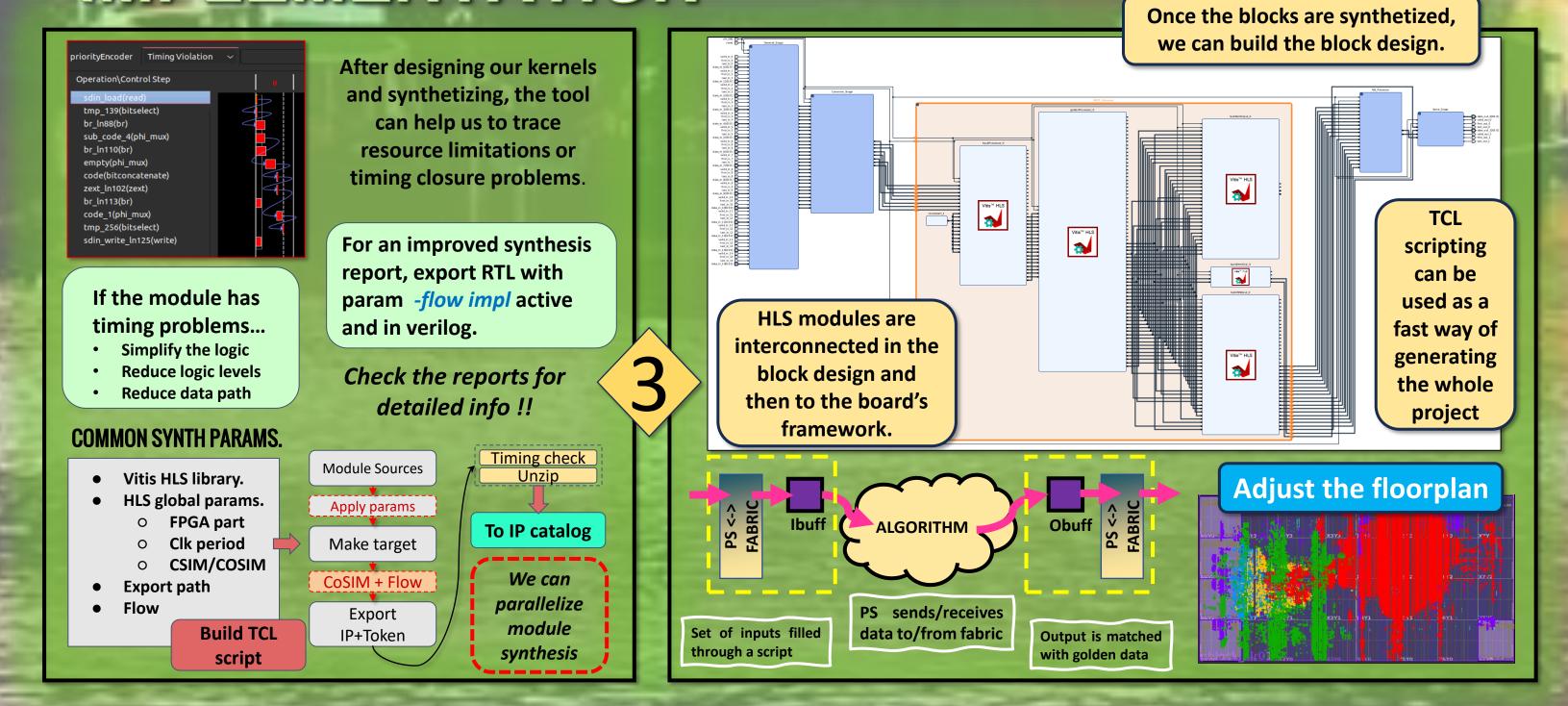

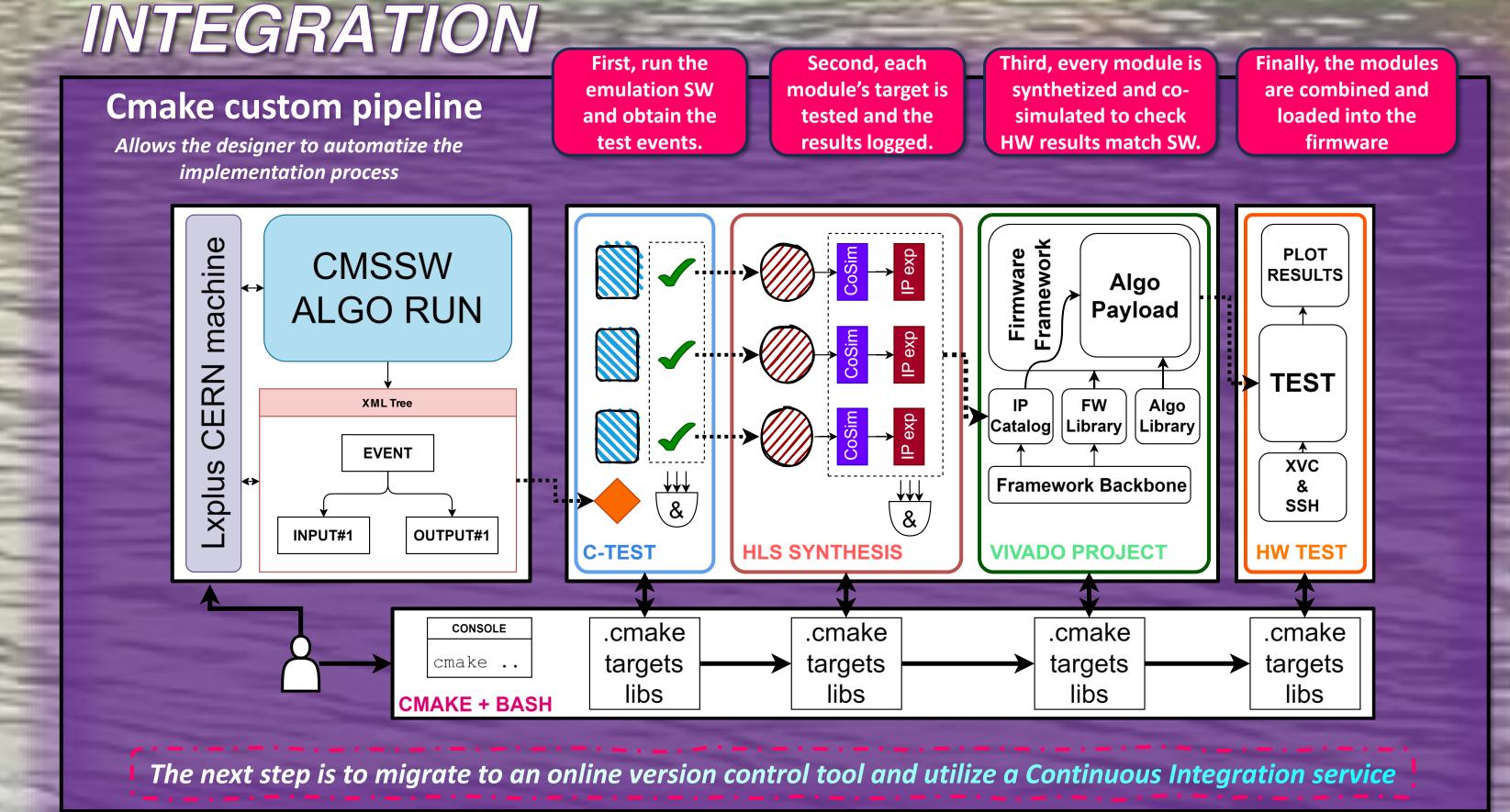

Writing our algorithms in High Level Synthesis (HLS) language enables a faster developing iteration time for FPGA design.

- Users can apply directives to the C code to create the Register Transfer Level (RTL) specific to a desired implementation.

- C simulation can be used to validate the design and allows faster iterations than a traditional RTL-based simulation.

- Increased level of abstraction accelerates development.

- Verification time is reduced.

- New possibilities for triggering on new physics signatures.

## FIRST STEPS

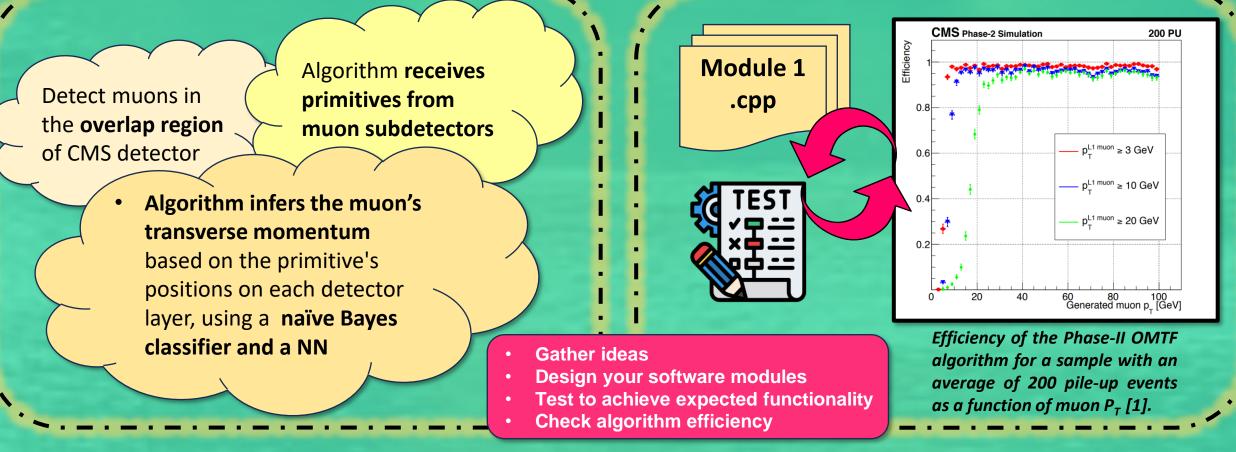

We will use the case study of a track-finding algorithm for muon reconstruction with the CMS experiment to show some of the optimizations with HLS [1].

Design our algorithm and implement it in C++ in a modular approach:

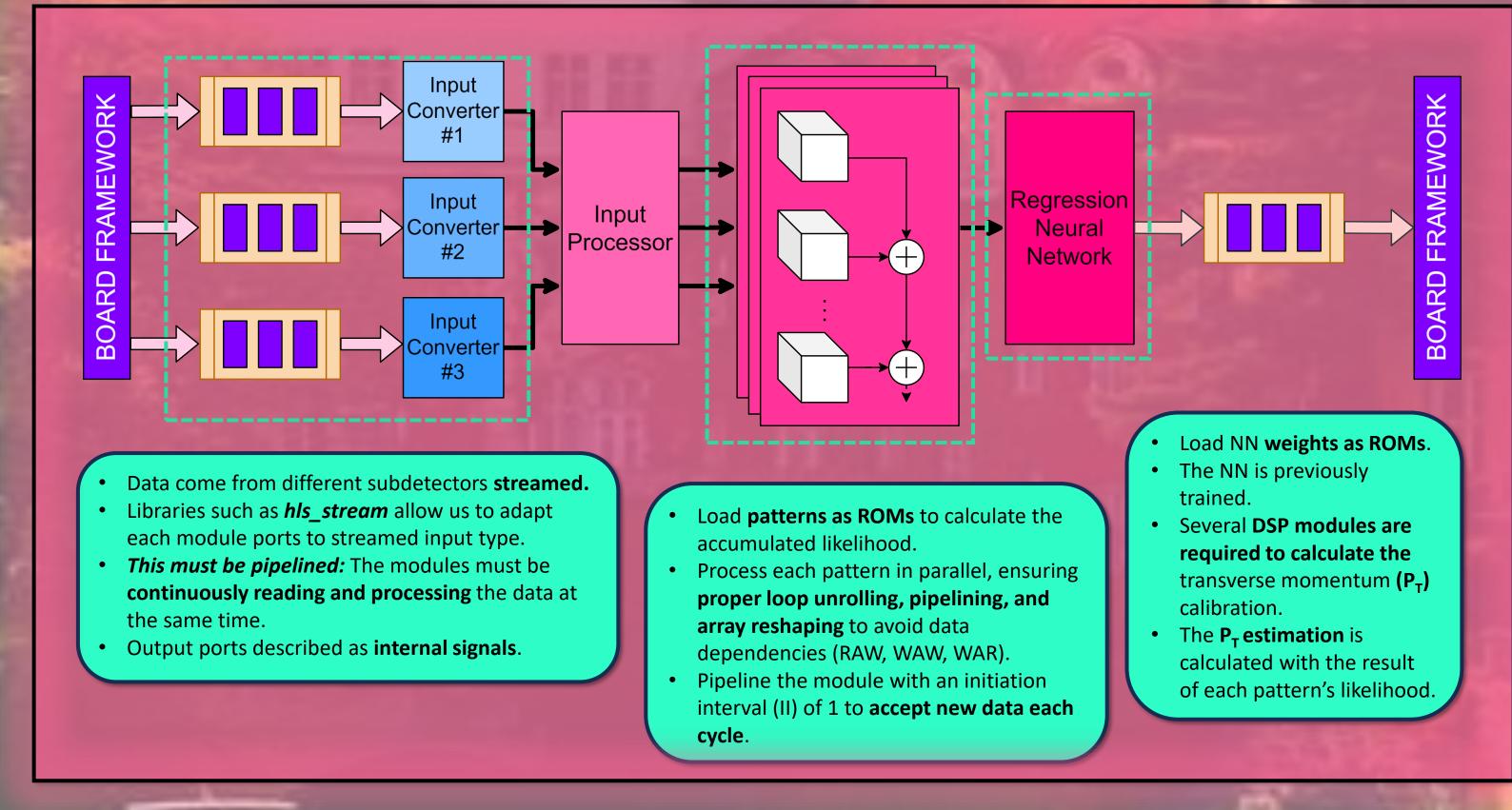

## BLOCK DIAGRAM

[1] The Phase-2 Upgrade of the CMS Level-1 Trigger, Tech. Rep. CMS-TDR-021, CERN, Geneva (2020) https://cds.cern.ch/record/2714892