# Study of Surface Radiation Damage in Silicon Sensors

Eckhart Fretwurst<sup>1</sup>, Robert Klanner<sup>1</sup>, Ioana Pintilie<sup>2</sup>, Joern Schwandt<sup>1</sup>, Jiaguo Zhang<sup>1</sup>

<sup>1</sup>Institute for Experimental Physics, University of Hamburg, Germany <sup>2</sup>National Institute of Materials Physics, Bucharest-Magurele, Romania

# Outline

- Introduction

- Measurement techniques (TDRC, C/G-V)

- Determination of the concentration of defects

- Results:

- 1) dose dependence of defects

- 2) orientation dependence: <1 1 1> vs. <1 0 0>

- 3) annealing kinetics of defects

- Influence on electric performance of segmented sensors

- Summary

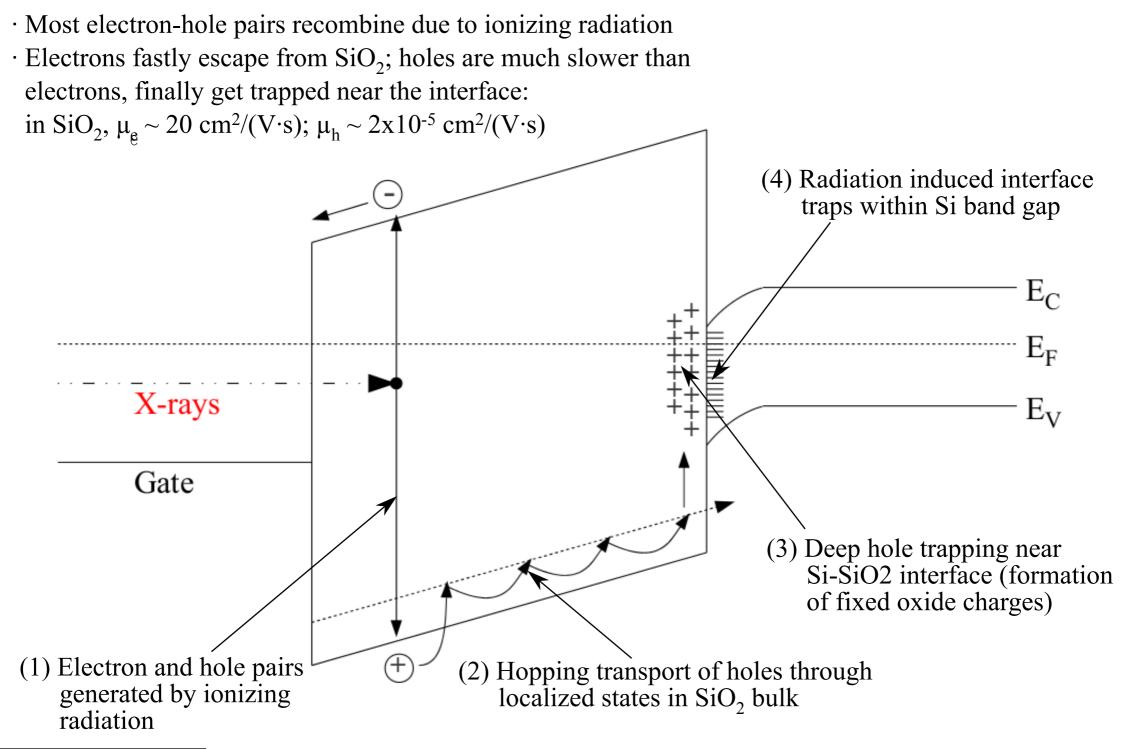

## Introduction to surface radiation damage

#### • Formation of defects close to the Si-SiO<sub>2</sub> interface:

<sup>\*</sup> from T.P. Ma and Paul V. Dressendorfer, "Ionizing Radiation Effects in MOS Devices and Circuits", WILEY 1989.

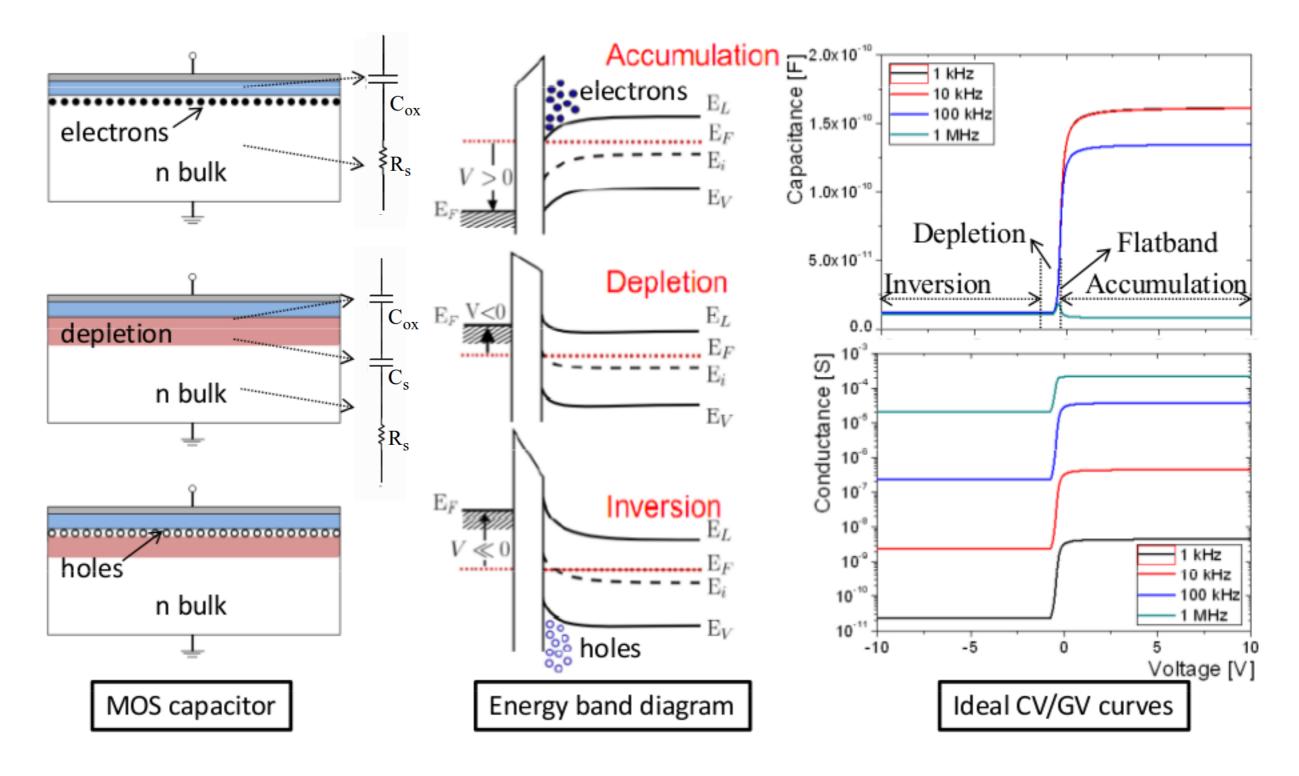

## Introduction to the principles of MOS capacitor

• Ideal C/G-V curves (no bulk, interface traps or fixed oxide charges):

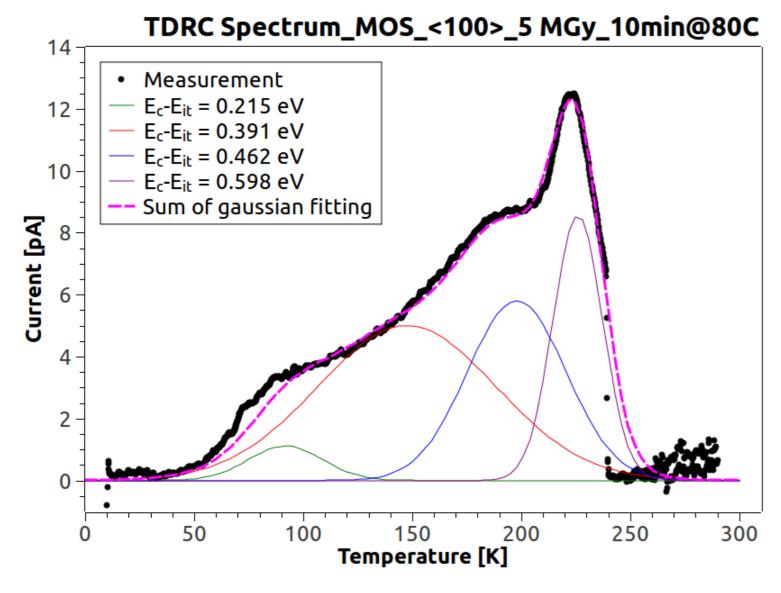

## Measurement techniques: TDRC

#### • TDRC (Thermally Dielectric Relaxation Current technique): (TSC technique for bulk damage)

Procedures:

- Bias the MOS capacitor into strong accumulation → fill interface traps with electrons;

- (2) Cool down the device to 10 K  $\rightarrow$  freeze traps;

- (3) Reverse\* the bias and heating up the device till 290 K  $\rightarrow$  trapped charges at Si-SiO<sub>2</sub> interface get released.

- Reverse bias should not put MOS capacitor into strong inversion (avoid border trap injection)

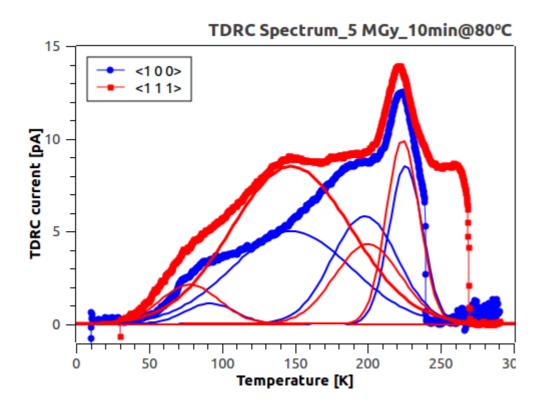

TDRC current  $[pA] \rightarrow Dit [cm^{-2}eV^{-1}]$ · 3 dominant traps and 1 subordinate trap were used to describe the measured TDRC spectrum

· Temperature  $[K] \rightarrow \text{Ec-Eit} [eV]$

integration of Dit

Nit

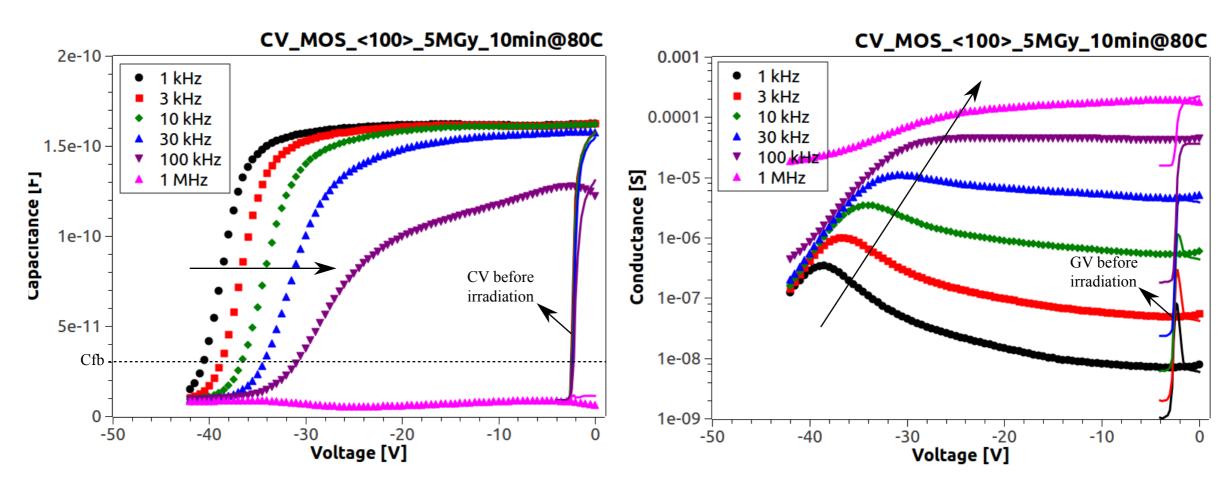

## Measurement techniques: C/G-V

· C/G-V (Capacitance-Voltage & Conductance-Voltage):

- · Shift of flatband voltage  $\leftarrow$  fixed oxide charges + interface traps

- · Frequency shift of C/G-V curves  $\leftarrow$  interface traps

- · Increase of conductance in depletion  $\leftarrow$  interface traps

- Flatband capacitance C<sub>tb</sub> after irradiation shows strong frequency dependence! It is difficult to determine fixed oxide charge density directly from the shift of flatband voltage.

## **Determination of the concentration of defects**

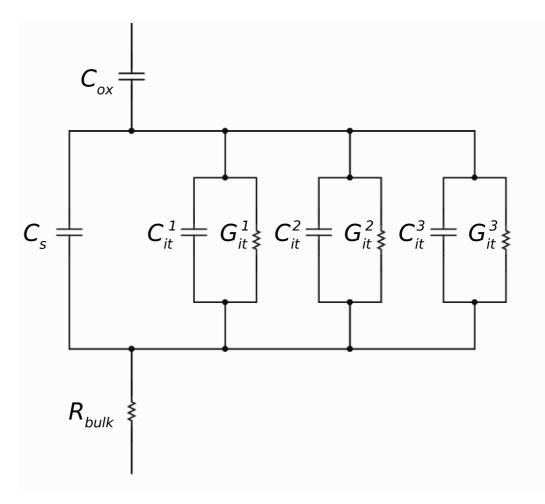

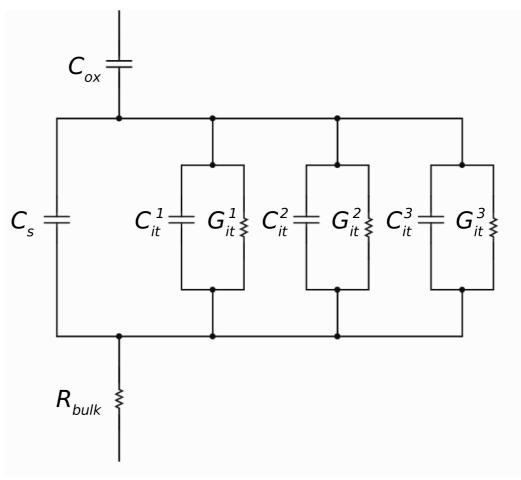

#### Simplified trap-included model for MOS capacitors:

- $\cdot C_{ox}$ : oxide capacitance, ~  $A_{gate}/d_{ox}$ .

- ·  $C_s (V_s)$ : space-charge capacitance, is doping dependent. higher  $N_d \rightarrow$  higher  $C_s$

- ·  $R_{bulk}$ : series resistance from bulk doping, ~  $1/N_d$ .

- Relation between  $V_g$  and band bending  $V_s$ :  $V_g(V_s) = V_s + \varphi_{ms} \left[ -\frac{q_0 N_{ox} A}{C_{ox}} - \frac{Q_{si}(V_s)}{C_{ox}} - \frac{Q_{it}(V_s)}{C_{ox}} \right]$

From the model, it can be concluded that:

- 1) interface traps contribute to  $C_{it}$  and  $G_{it}$  (change slope & cause frequency shift of measured C/G-V curves), and shift the curves.

- 2) fixed oxide charges only shift the entire C/G-V curves to lower voltage.

## **Determination of the concentration of defects**

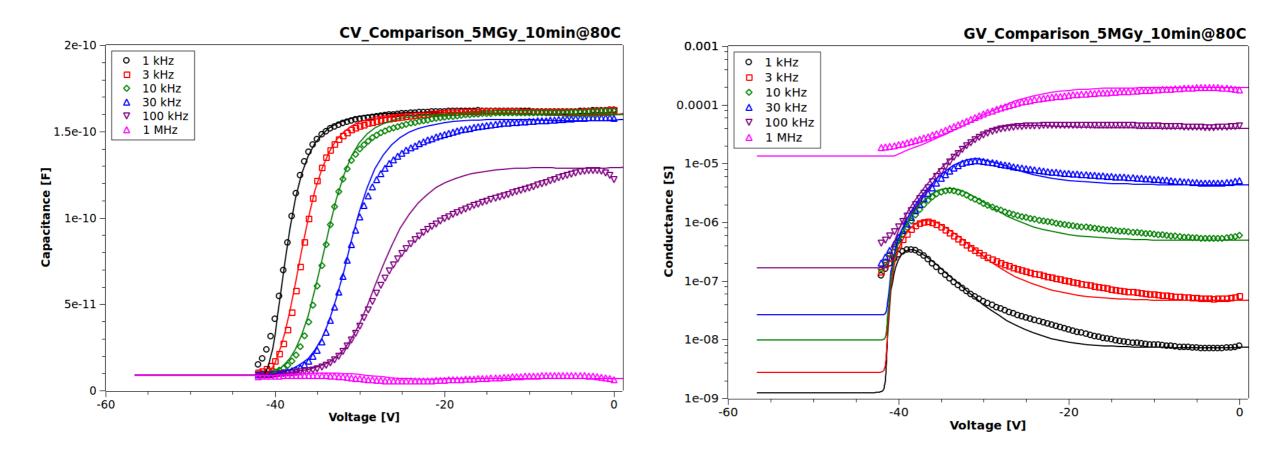

#### • Model calculation to reproduce measured C/G-V curves:

- $\cdot$  TDRC spectrum as an input for D<sub>it</sub> in the program, all interface traps were assumed to be acceptor like.

- Capture cross sections for the interface traps were evaluated by measuring TDRC spectrum with different heating rates:

- $\sigma$  (E<sub>c</sub>-E<sub>it</sub>=0.391eV)=1.2×10<sup>-15</sup> cm<sup>2</sup>,  $\sigma$  (E<sub>c</sub>-E<sub>it</sub>=0.598 eV) =6×10<sup>-16</sup> cm<sup>2</sup>,  $\sigma$  (E<sub>c</sub>-E<sub>it</sub>=0.462 eV) =2.5×10<sup>-17</sup> cm<sup>2</sup> · C/G-V curves were calculated and compared to measurements

· Fixed charge density was determined when model calculation reproduce measurement curves!

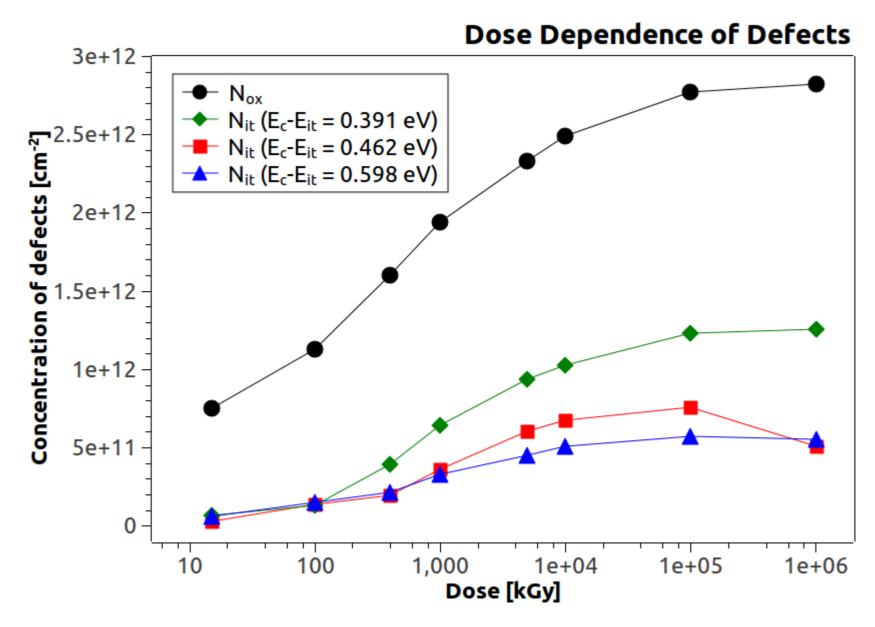

#### **Results: dose dependence of defects**

• Dose dependence of a MOS capacitor with <100> orientation:

- · Measurements were done after 10min@80C annealing to stablize properties of sensors.

- $\cdot$  N<sub>ox</sub> and N<sub>it</sub> saturate at a dose value in between 10 MGy and 100 MGy.

- · Saturation value of N<sub>ox</sub> is  $2.8 \times 10^{12}$  cm<sup>-2</sup>.

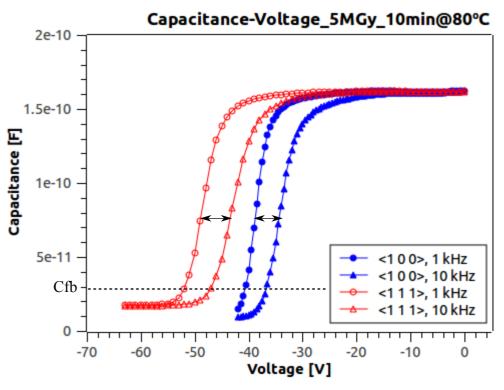

#### **Results: orientation dependence**

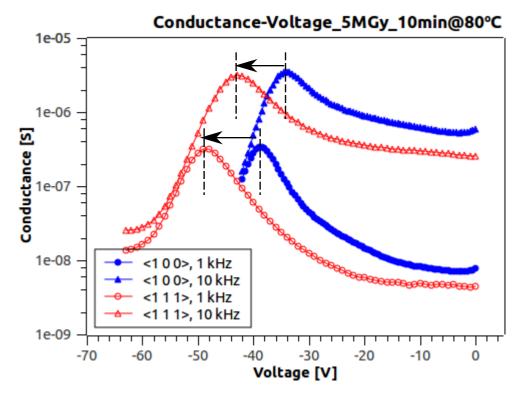

#### • <1 0 0> vs. <1 1 1>: results for 5 MGy after 10min@80 °C annealing.

- From TDRC spectrum, density of interface traps close to conductance band from <1 1 1> is larger than that from <1 0 0>:  $N_{it}^{<111>} > N_{it}^{<100>}$ .

- The capacitor with orientation <1 1 1> shows larger frequency shift  $\rightarrow$  confirms the increase of shallow traps.

- Shift of C/G-V curves → indication of increase of fixed oxide charges? (Yes if traps are acceptor-like, BUT the types of interface traps can not be determined from C/G-V and TDRC measurements)

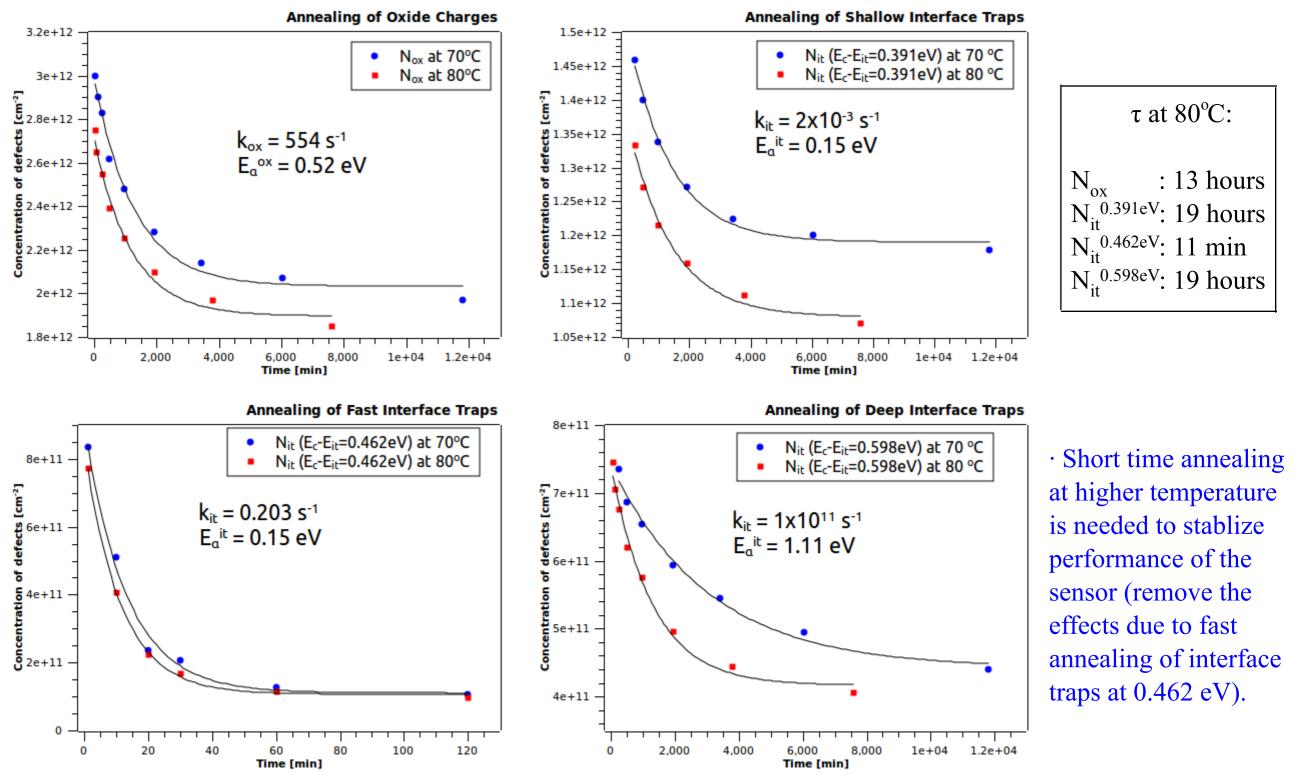

### **Results: annealing kinetics of defects**

#### • Annealing study for a MOS capacitor <1 1 1> after 5 MGy irradiation:

Jiaguo Zhang, Hamburg University

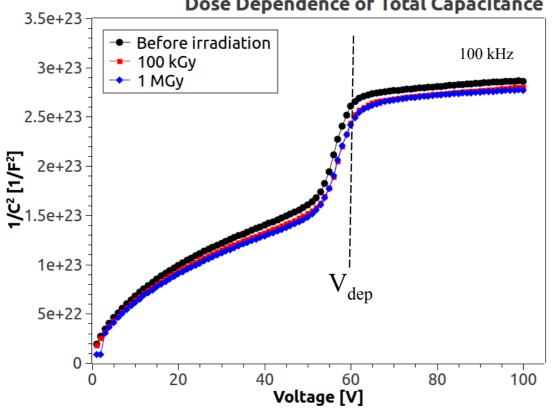

## Influence in electric performance of segmented sensors

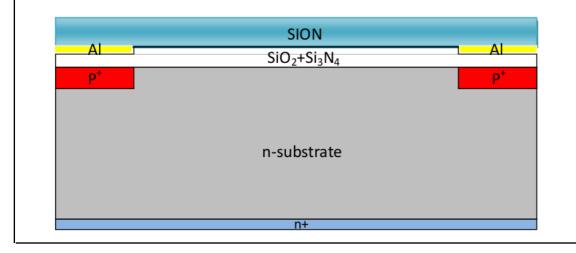

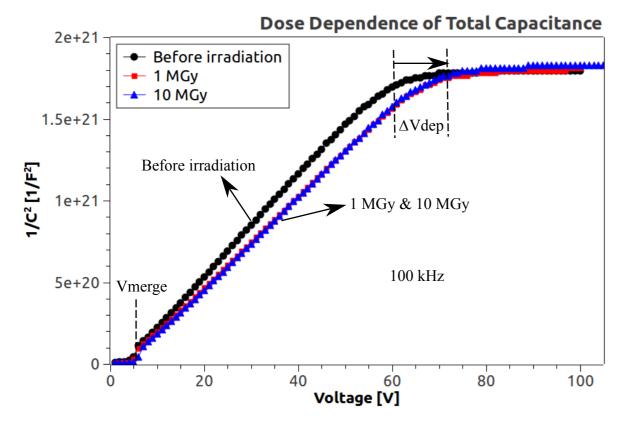

#### · CiS p-on-n microstrip sensors (Capacitance-Voltage behavior):

- · Sensor's thickness: 285  $\mu$ m · Orientation: <100>

- Pitch: 80  $\mu$ m · Gap: 62  $\mu$ m · G

- $\cdot$  At ~ 6 V, space charge region below each strip merges into together.

- Due to the presense of surface charges at the  $Si-SiO_2$ interface, full depletion voltage  $V_{dep}$  increases about 10 V after irradiaitons (not due to change of doping).

- From simulation, it was observed that increase of full depletion voltage  $\Delta V_{dep}$  saturates at a value of fixed oxide charge density ~  $3-5 \times 10^{11}$  cm<sup>-2</sup>.

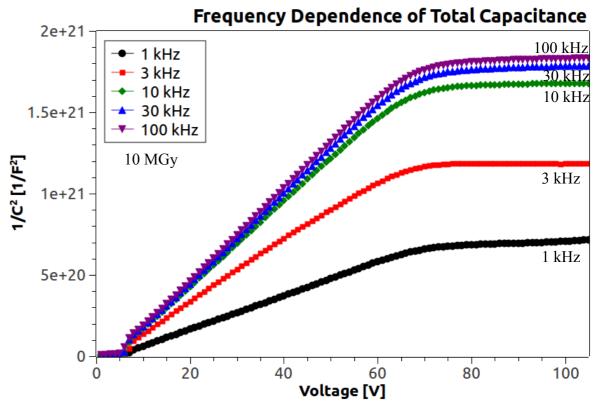

- Interface traps are responsible for the frequency dependence of total capacitance.

#### Jiaguo Zhang, Hamburg University

#### 18th RD50 Workshop, 23rd -25th May 2011, Liverpool

## **Influence in electric performance of segmented sensors**

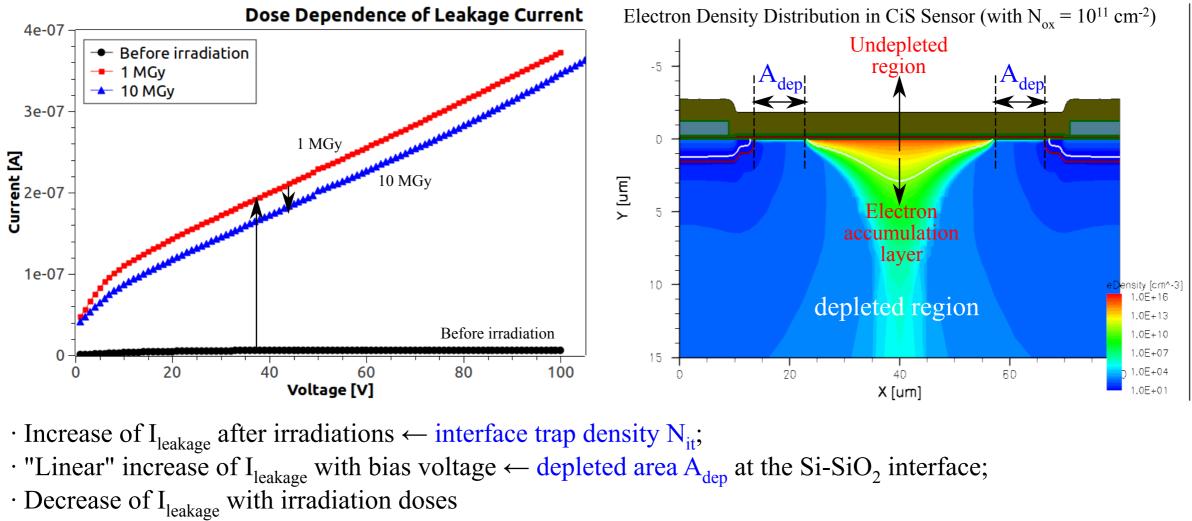

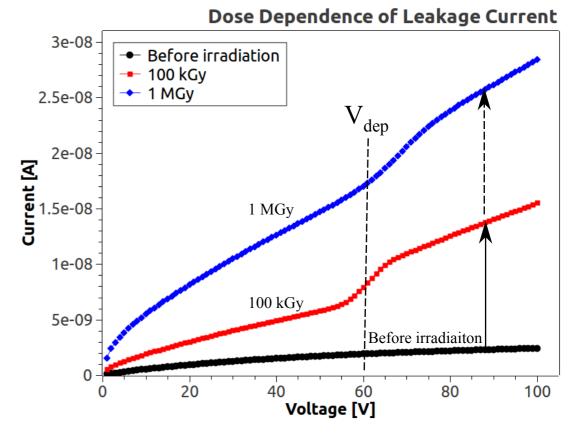

#### · CiS p-on-n microstrip sensors (Current-Votlage behavior):

- $\cdot I_{\text{leakage}} = I_{\text{bulk}} + I_{\text{surface}};$

- $\cdot I_{\text{bulk}}$  dependes on depleted volume of silicon sensor and life time of charge carriers in bulk;

- ·  $I_{surface}$  is proportional to interface trap density  $N_{it} \times$  depleted area  $A_{dep}$  at the Si-SiO<sub>2</sub> interface.

$\leftarrow$  increasing positive charges at the interface surpress the depleted area  $A_{dep}$ ;

<sup>\*</sup> A value of 8  $\mu$ A/cm2 from irradiated microstrip sensor compatible with previous measurements on gated diode.

## Summary

$\cdot$  N<sub>ox</sub> and N<sub>it</sub> were determined as function of dose: all defects density saturates at ~ 10-100 MGy.

- Annealing studies were performed at 70 °C and 80 °C; frequency factors and activiation energies of different defects were derived.

- Comparison between two irradiated MOS capacitors with different orientations was made. The densities of interface traps close to conductance band show significant difference.

- Irradiations for p<sup>+</sup>n microstrip sensors and n<sup>+</sup>n pixel sensors were done; electric properties were characterized for different doses and understood by the study from MOS.

# Thanks for your attention!

## Backup

## **Determination of the concentration of defects**

#### Simplified trap-included model for MOS capacitors:

- $\begin{array}{l} \cdot \ \mathbf{C}_{\mathrm{ox}} \colon \mathrm{oxide\ capacitance} \\ C_{ox} = \epsilon_{SiO_2} \epsilon_0 \frac{S}{t_{ox}} \\ \cdot \ \mathbf{C}_{\mathrm{s}} \colon \mathrm{space-charge\ capacitance} \\ c_{\mathrm{s}}(\mathrm{V}_{\mathrm{s}}) = \begin{cases} \frac{C_{FBS} \cdot \frac{V_s}{|V_s|} \cdot \left[\exp\left(\frac{q_0 V_s}{k_0 T}\right) 1\right]}{\sqrt{2\left[-\frac{q_0 V_s}{k_0 T} 1 + \exp\left(\frac{q_0 V_s}{k_0 T}\right)\right]}} & \frac{q_0 V_s}{k_0 T} > v_m \\ \frac{C_{FBS} \cdot \frac{v_m}{|v_m|} \cdot \left[\exp(v_m) 1\right]}{\sqrt{2\left[-v_m 1 + \exp(v_m)\right]}} & \frac{q_0 V_s}{k_0 T} \leq v_m \end{cases}$

- $\cdot C_{it}$ : interface trap capacitance

$$C_{it}^{p}(V_{s},f) = \frac{q_{0}^{2}S}{k_{0}T} \int_{E_{v}}^{E_{c}} D_{it}(E_{it}) \cdot \frac{\exp\left(\frac{-(E_{c}-E_{it})-q_{0}V_{s}-E_{F}}{k_{0}T}\right)}{\left[1+\exp\left(\frac{-(E_{c}-E_{it})-q_{0}V_{s}-E_{F}}{k_{0}T}\right)\right]^{2}}$$

$$\times \frac{dE_{it}}{1 + \frac{\omega^2}{C_0^2} \frac{1}{\left[\exp\left(\frac{q_0 V_s}{k_0 T}\right) + \exp\left(\frac{-(E_c - E_{it}) - E_F}{k_0 T}\right)\right]^2}}$$

$\cdot$  G<sub>it</sub>: interface trap conductance

$$G_{it}^{p}(V_{s},f) = \frac{\omega^{2}q_{0}^{2}S}{k_{0}T} \int_{E_{v}}^{E_{c}} D_{it}(E_{it}) \cdot \frac{\exp\left(\frac{-(E_{c}-E_{it})-q_{0}V_{s}-E_{F}}{k_{0}T}\right)}{\left[1+\exp\left(\frac{-(E_{c}-E_{it})-q_{0}V_{s}-E_{F}}{k_{0}T}\right)\right]^{2}}$$

$$\times \frac{\frac{1}{C_0} \cdot \frac{1}{\left[\exp\left(\frac{q_0 V_s}{k_0 T}\right) + \exp\left(\frac{-(E_c - E_{it}) - E_F}{k_0 T}\right)\right]}}{1 + \frac{\omega^2}{C_0^2} \frac{1}{\left[\exp\left(\frac{q_0 V_s}{k_0 T}\right) + \exp\left(\frac{-(E_c - E_{it}) - E_F}{k_0 T}\right)\right]^2}} \cdot dE_{it}$$

$\cdot R_{bulk}$ : series resistance from bulk doping

$$R_{bulk}\left(V_s\right) = \frac{1}{q_0\mu_n N_d} \cdot \frac{d_{si}}{S}$$

$\cdot$  Relation between  $V_g$  and band bending  $V_s$ :

$$V_g\left(V_s\right) = V_s + \varphi_{ms} - \frac{q_0 N_{ox} S}{C_{ox}} - \frac{Q_{si}\left(V_s\right)}{C_{ox}} - \frac{Q_{it}\left(V_s\right)}{C_{ox}}$$

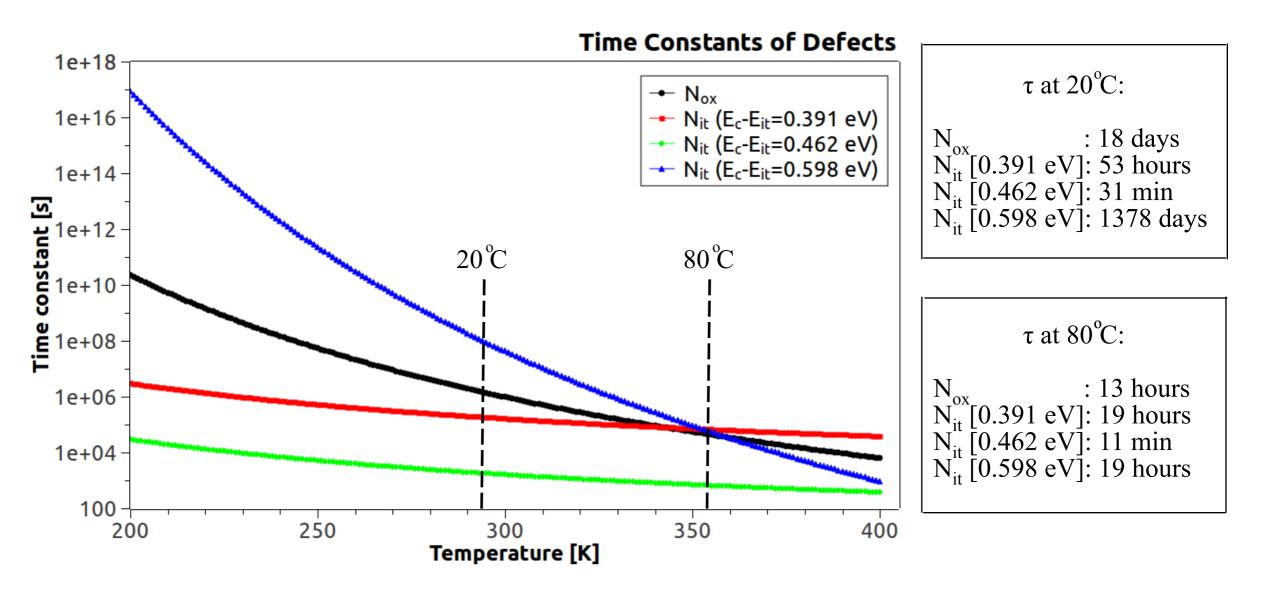

## **Results: annealing kinetics of defects**

• Annealing time constants for different defects:

- $\cdot$  The interface trap at 0.462 eV can be annealed out quickly at room temperature.

- $\cdot$  The interface traps at 0.391 eV and 0.598 eV, and fixed oxide charges are very stable at room temperature.

- $\cdot$  Short time annealing at higher temperature is needed to stablize sensors' performance (remove the effects due to fast annealing of the interface traps at 0.462 eV).

<sup>\*</sup> results with large uncertainties

## Influence in electric performance of segmented sensors

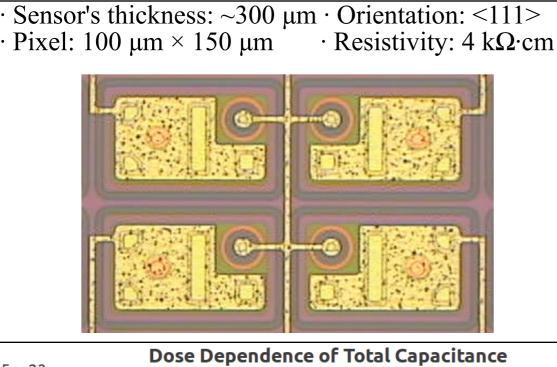

#### · CMS n-on-n test pixel sensors (Current/Capacitance-Votlage behavior):

- Jump of capacitance around  $V_{dep}$  is due to the isolation between pixel sensors on the same test field.

- $\cdot$  Due to the compensation of p-spray to surface charges, full depletion voltage  $V_{dep}$  did not increase with irradiaitons.

- $\cdot$  Similar behavior of leakage current was observed for  $n^+$  on n sensors:

- 1)  $V_{bias} < V_{dep}$ , p+ side traps contribute to  $I_{leakage}$ 2)  $V_{bias} > V_{dep}$ , both p+ and n+ side traps contribute

Jiaguo Zhang, Hamburg University