# Optimisation of Silicon Tracking Systems FCC Week 2024

### Armin Ilg

University of Zürich

11.06.2024

# FCC-ee detector concepts

CLD: CLIC-Like Detector [1, 2].

- ILC  $\rightarrow$  CLIC  $\rightarrow$  FCC-ee ( $\rightarrow$   $\mu$ Col)

- Si vertexing and tracking

- Highly-granular ECAL and HCAL, CALICE-like

- Solenoid coil outside calorimeter system

- IDEA: Innovative Detector for  $e^+e^-$ Accelerators [3, 4].

- Si vertexing

- Drift chamber (down to 1.6% X/X0, dN<sub>ion.</sub>/dx)

- Si wrapper with timing

- Dual-readout calorimeter with r preshower

- Solenoid coil inside calorimeter system

ALLEGRO: A Lepton coLLider Experiment with highly GRanular calorimetry Read-Out (M. Aleksa).

- Si vertexing and drift chamber

- Highly granular noble liquid ECAL, Pb/W+LAr or W+LKr

- ECAL and solenoid coil in same cryostat

- CALICE-like or TileCal-like HCAL

Armin Ilg (UZH)

Optimisation of Silicon Tracking Systems

FCC Week 2024

# FCC-ee detector concepts + variations (RICH, crystal ECAL, ...)

CLD: CLIC-Like Detector [1, 2].

- ILC  $\rightarrow$  CLIC  $\rightarrow$  FCC-ee ( $\rightarrow$   $\mu$ Col)

- Si vertexing and tracking

- Highly-granular ECAL and HCAL, CALICE-like

- Solenoid coil outside calorimeter system

- IDEA: Innovative Detector for  $e^+e^-$ Accelerators [3, 4].

- Si vertexing

- Drift chamber (down to 1.6% X/X0, dN<sub>ion.</sub>/dx)

- Si wrapper with timing

- Dual-readout calorimeter with r preshower

- Solenoid coil inside calorimeter system

ALLEGRO: A Lepton coLLider Experiment with highly GRanular calorimetry Read-Out (M. Aleksa).

- Si vertexing and drift chamber

- Highly granular noble liquid ECAL, Pb/W+LAr or W+LKr

- ECAL and solenoid coil in same cryostat

- CALICE-like or TileCal-like HCAL

Armin Ilg (UZH)

Optimisation of Silicon Tracking Systems

FCC Week 2024

University of

Zurich

# FCC-ee vertex detector layouts

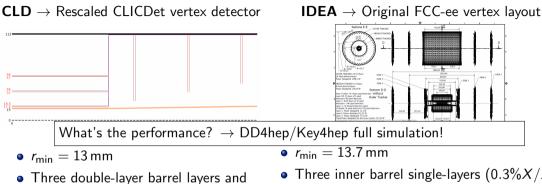

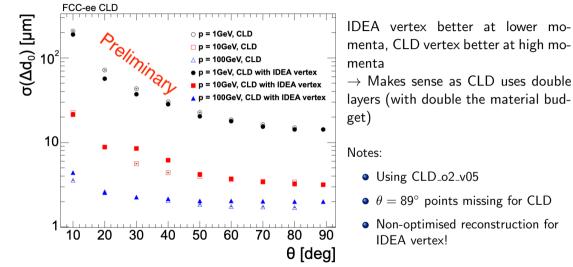

$\textbf{CLD} \rightarrow \text{Rescaled CLICDet vertex detector}$

- $r_{\rm min} = 13 \, \rm mm$

- Three double-layer barrel layers and disks, 0.6–0.7%X/X<sub>0</sub> per double layer

- No engineering studies since CLICDet developments

- So specific sensor chosen, assume  $3\,\mu m$  single-point resolution

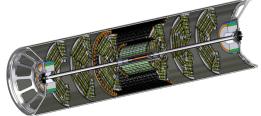

$\textbf{IDEA} \rightarrow \text{Original FCC-ee}$  vertex layout

- $r_{\min} = 13.7 \text{ mm}$

- Three inner barrel single-layers  $(0.3\% X/X_0)$ , two outer barrel layers and three disks

- Engineered design (F. Palla), integrated into MDI (INFN-LNF)

- Assume ARCADIA (inner barrel) and ALTASPix3 (outer barrel, disks) sensors

Armin Ilg (UZH)

# FCC-ee vertex detector layouts

- disks, 0.6–0.7% $X/X_0$  per double layer

- No engineering studies since CLICDet developments

- So specific sensor chosen, assume 3  $\mu m$  single-point resolution

- Three inner barrel single-layers  $(0.3\% X/X_0)$ , two outer barrel layers and three disks

- Engineered design (F. Palla), integrated into MDI (INFN-LNF)

- Assume ARCADIA (inner barrel) and ALTASPix3 (outer barrel, disks) sensors

Armin Ilg (UZH)

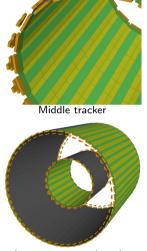

### Detector model in k4geo

- Linear collider reconstruction (iLCSoft/CLICPerformance)

- Can generate EDM4hep output using k4MarlinWrapper

- CLD\_o2\_v05: Small, AlBeMet beam pipe

- G. Sadowski, 7th FCC Physics Workshop

Armin Ilg (UZH)

Optimisation of Silicon Tracking Systems

University of

Zurich

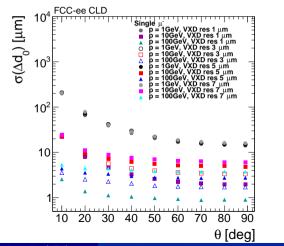

# CLD tracker and vertex performance updates G. Sadowski

### Using CLD reconstruction and k4DetPerformance for plotting! Impact of sensor spatial resolution ARC adapted

# ARC adapted CLD (CLD\_03\_v01 design)

- Reduced outer tracker radius and length

- 15–20% degradation in  $p_{\rm T}$  resolution

# IDEA vertex detector: ARCADIA and ATLASPix3

### **Depleted Monolithic Active Pixel Detectors**

- Inner Vertex (inspired to ARCADIA):

- Lfoundry 110 nm process

- 50 μm thick, 25 μm x 25 μm

- Module dimensions:  $8.4 \times 32 \ mm^2$

- Power density  $50 \ mW/cm^2$  (core  $30 \ mW/cm^2$ )

- Current at 100 MHz/cm<sup>2</sup>

- Outer Vertex and disks (inspired to ATLASPIX3)

- TSI 180 nm process

- 50 μm thick (50 μm x 150 μm)

- Module dimensions:  $42.2 \times 40.6 \ mm^2$

- Power density: assume  $100 \ mW/cm^2$

- Up to 1.28 Gb/s downlink

F. Palla, 2nd FCC US workshop at MIT

FCC Week 2024

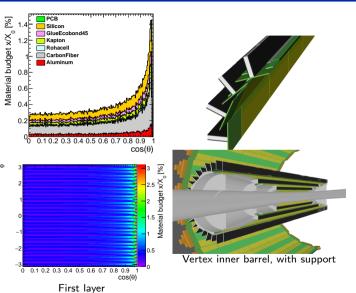

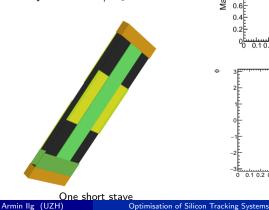

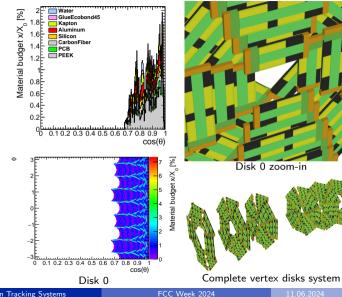

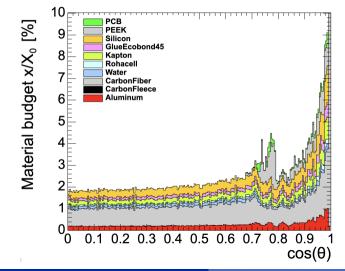

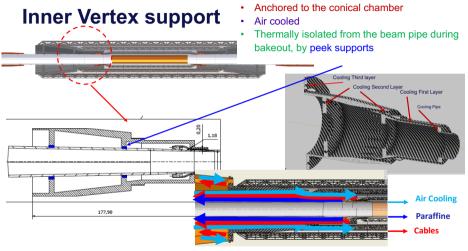

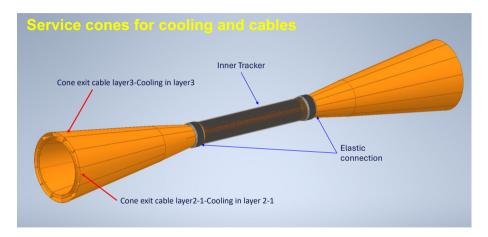

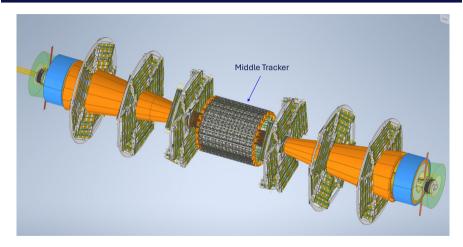

# Vertex inner barrel

- $r_{\min} = 13.7 \text{ mm}, 2 \text{ mm to}$ beam pipe (can we go closer?)

- Correct material stack, flexes, end-of-stave hybrid, insensitive sensor areas (2 mm)

- Proxy volume for stave holding structure

- Need to add service cones

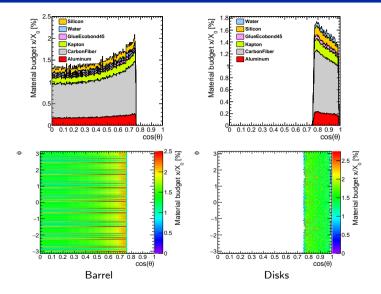

- Material budget in line with 0.3% per layer at cos(θ) = 0 (CDR assumption)

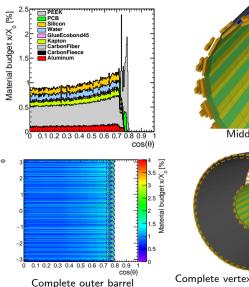

# Vertex outer barrel

- Correct material stack, correct description of ATLASPix3 insensitive peripheries

- Proxy volumes for truss structure and cooling pipes

- Proxy volume for end-of-stave holder (orange, material budget contribution optimised with F. Palla)

- $\rightarrow~$  Still significant contribution

Complete vertex outer barrel system

Optimisation of Silicon Tracking Systems

# Vertex disks

- Correct placement of all modules in *r* and *z*

- Missing vertex disk global support

- Very uneven  $x/X_0$  distribution

### Complete system

- Material budget comparable with CDR estimate

- Will make the updated version available soon

- Plan to include last missing volumes using DDCAD

- Look at all material budget evaluations as a lower limit, there's always gonna be more added! (e.g off-detector cabling)

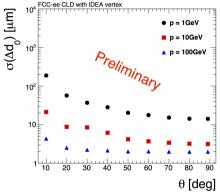

- $\bullet~$  No drift chamber tracking available yet  $\rightarrow~$  instead use CLD and iLCSoft reconstruction

•

## Complete system

Complete vertex system

- Material budget comparable with CDR estimate

- Will make the updated version available soon

- Plan to include last missing volumes using DDCAD

- Look at all material budget evaluations as a lower limit, there's always gonna be more added! (e.g off-detector cabling)

- $\bullet~$  No drift chamber tracking available yet  $\rightarrow~$  instead use CLD and iLCSoft reconstruction

- Frankenstein approach: Remove CLD vertex detector (and a couple of Inner Tracker layers and disks) and instead insert IDEA vertex, run CLD reconstruction and k4DetPerformance for plotting!

- Let's have a look!

### **Necessary changes**

- Removing first Inner Tracker barrel layer (*r* = 127 mm)

- Removing first and second Inner Tracker disks (*r* = 79.5 and 123.5 mm)

- Increase conformal tracking max. distance (CT\_MAX\_DIST)

- *MinClustersOnTrack* from 4 to 3 in conformal tracking in vertex barrel and disks

### Necessary changes

- Removing first Inner Tracker barrel layer (*r* = 127 mm)

- Removing first and second Inner Tracker disks (r = 79.5 and 123.5 mm)

- Increase conformal tracking max. distance (CT\_MAX\_DIST)

- *MinClustersOnTrack* from 4 to 3 in conformal tracking in vertex barrel and disks

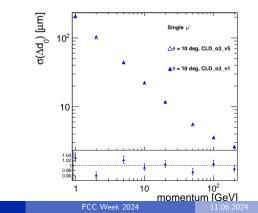

### Nota bene

- No silicon wrapper

- Assume spatial resolution of 3  $\mu$ m for vertex inner barrel (same as CLD), and 14  $\mu$ m × 43  $\mu$ m for outer barrel and disks (CLD: vertex endcap: 3  $\mu$ m, inner tracker endcap: 5  $\mu$ m or 7 × 90  $\mu$ m)

Optimisation of Silicon Tracking Systems

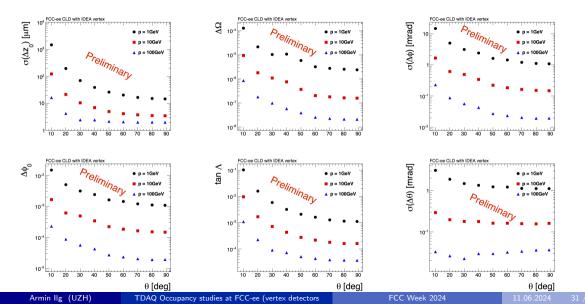

# Comparison between CLD and IDEA vertex

Other, preliminary, results in backup

Armin Ilg (UZH)

FCC Week 2024

### DMAPS in 65 nm TPSCo process

- More logic per cm<sup>2</sup>

- $\bullet$  Lower power consumption  $\rightarrow$  Air cooling

- Enables 12" wafers  $\rightarrow$  Wafer-scale bent sensors!

### DMAPS in 65 nm TPSCo process

- More logic per cm<sup>2</sup>

- Lower power consumption  $\rightarrow$  Air cooling

- Enables 12" wafers  $\rightarrow$  Wafer-scale bent sensors!

### DMAPS in 65 nm TPSCo process

• More logic per cm<sup>2</sup>

Azimuthal angle [

- Lower power consumption  $\rightarrow$  Air cooling

- Enables 12" wafers  $\rightarrow$  Wafer-scale bent sensors!

Othe

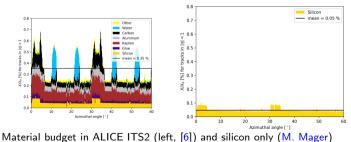

Material budget in ALICE ITS2 (left, [6]) and silicon only (M. Mager) See also F. Palla at 2nd FCC US workshop and G. Contin's talk.

0.7

v 0.6

0.4

F 0.3

-XX 0.2

0.1

0.0

0.7

0.1

0.0

20 Azimuthal angle [ \* Silicon

### DMAPS in 65 nm TPSCo process

• More logic per cm<sup>2</sup>

Azimuthal angle [

- Lower power consumption  $\rightarrow$  Air cooling

- Enables 12" wafers  $\rightarrow$  Wafer-scale bent sensors!

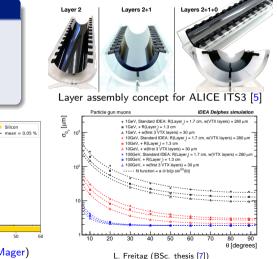

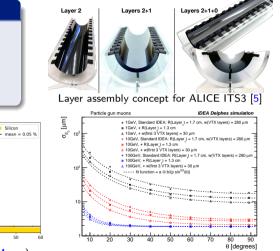

Azimuthal angle [ \* Material budget in ALICE ITS2 (left, [6]) and silicon only (M. Mager) L. Freitag (BSc. thesis [7]) See also F. Palla at 2nd FCC US workshop and G. Contin's talk. How adapt to FCC-ee?

20

Silicon

0.7

0.1

0.0

0.7

v 0.6

0.4

÷ 0.3

-XX 0.2

0.1

0.0

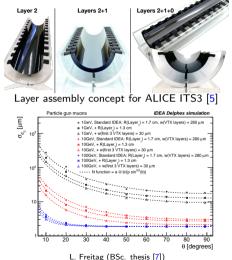

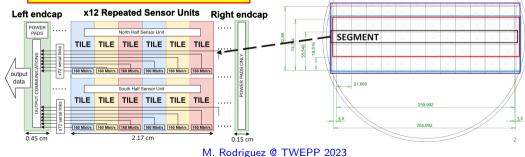

# ALICE ITS3 layout

- Wafer-scale Monolithic Active Pixel Sensors (MAPS)

- Cylindrical sensors of radii 18/24/30 mm

#### Architecture requirements (Stitching)

- Dies divided into 3,4 or 5 Segments

- 2 endcaps on the edges

- 12 Repeated Sensor Units (RSU)

- 12 tiles per RSU

#### Data transfer on-chip to the left edge (26.6 cm)

Armin Ilg (UZH)

Optimisation of Silicon Tracking Systems

# Differences between ALICE ITS3 and FCC-ee

University of Zurich<sup>™</sup>

- First layer at smaller radius, from 18 to 13.7 mm

- ightarrow Mechanically okay, electrically to be demonstrated

- ightarrow First layer to use just two segments

- ITS3 cables only to one side  $\rightarrow$  We want to measure forward-backward asymmetries extremely precisely

- $\rightarrow~$  Read and power from both sides where possible

- $\bullet\,$  Need forward coverage down to  $\theta\approx 140\,{\rm mrad}$

- ightarrow Multiple wafer-scale sensors in a row at larger radii

- $\rightarrow~$  Ensure flexes, cables, etc. are not in front of lumical

- Hermeticity?

- $\rightarrow$  Cannot overlap like with staves (wire bonds from sensor end to flex)

- $\rightarrow\,$  Evaluate impact of only  $\sim$  95% coverage per layer (RSU periphery, gap between sensors)

- $\rightarrow~$  Increase number of layers from 3 to 4 to ensure at least three hits

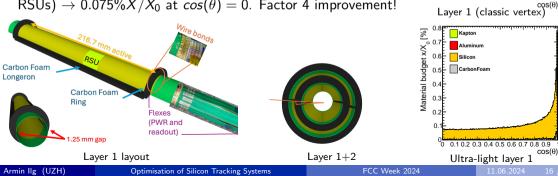

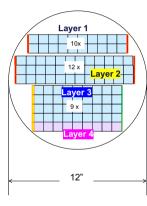

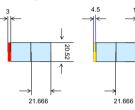

# Ultra-light vertex concept: Layer 1 and 2

- Layer 1: 10 RSUs long  $\rightarrow \theta \geq$  125 mrad

- Layer 2: 12 RSUs (max!)  $\rightarrow \theta \ge 155 \, {

m mrad}$

- Gap of 1.25 mm between half-barrels, layer 2 rotated in  $\phi$  to avoid overlap with layer 1

- Readout and power from both sides

- 50  $\mu$ m of Si + 16  $\mu$ m of Si-equivalent (metal layer connecting RSUs)  $\rightarrow 0.075\% X/X_0$  at  $cos(\theta) = 0$ . Factor 4 improvement!

GlueEcobond45

rhonEibo

0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8

X/X

Material budget

0 1

0

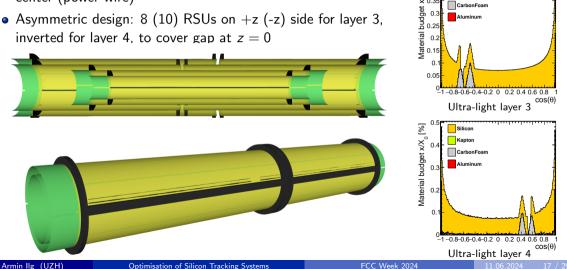

# Ultra-light vertex detector concept: Laver 3 and 4

- Two sensors per side, readout only on sides, power on sides and center (power wire)

- Asymmetric design: 8 (10) RSUs on +z (-z) side for layer 3, inverted for layer 4, to cover gap at z = 0

University of

Zurich

8 Ϋ́ο.35

Carbon Eoam

Aluminum

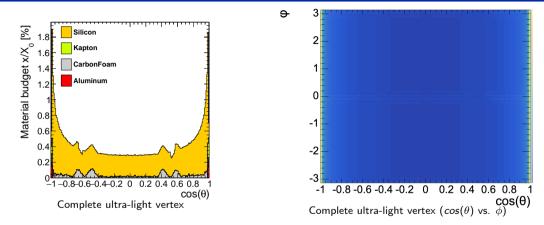

# Ultra-light vertex concept: Discussion

- Same material budget as one layer (!) of normal IDEA vertex, more uniformly in  $\phi$

- Compromise hermeticity (or radius of first hit) with reduced material budget

- Need to add new sensitive surface to DD4hep (cylinder segment) to estimate vertexing performance using CLD reconstruction

Armin Ilg (UZH)

Optimisation of Silicon Tracking Systems

# IDEA silicon wrapper: Reminder

A last hurrah of the tracking system before Coulomb scattering takes over

- Momentum resolution thanks to long lever arm

- Extend tracker coverage

- Precise and stable ruler for acceptance definition

### Possible technologies:

- DMAPS

- LGADs

- Microstrips

- ...

Needs to be added to DD4hep detector description as well!

### Slide following A. Andreazza FCC Week 2021

Barrel

FCC Week 2024

# IDEA silicon wrapper: What was assumed so far

- $\bullet$  Assume total of  $\approx 1\% X/X_0$  in barrel and disks

- Hermeticity

- Decided to increase disk  $r_{\rm out}$  from 2020 to 2040 mm

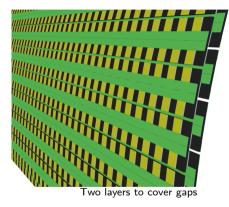

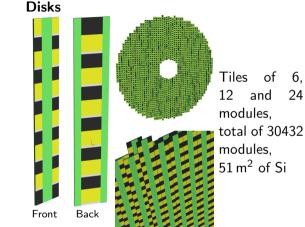

- Two barrel layers and two disks, to have at least one silicon hit, but most of the cases we have two silicon hits

- $\bullet\,$  Total area:  $\simeq 30\,m^2$  per barrel layer,  $\simeq 13\,m^2$  per disk  $\rightarrow\,$   $112\,m^2$  to cover

- Sensor thickness: 50  $\mu{\rm m},$  resolutions: pitch 0.05  $\times$  1  ${\rm mm}^2$  and 40 ps per hit, don't care about specific sensor technology

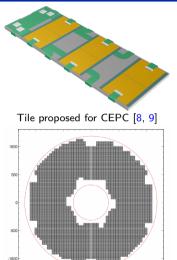

- Assume ATLASPix3-sized modules (42.2  $\times$  40.6  $mm^2)$  to construct tiles with 6, 12 or 24 modules each

- Disk design inspired by CMS endcap timing layer

CMS ETL layout [10]

# IDEA silicon wrapper: What is there

### Barrel

Layer of 151 staves with 129  $\cdot$  2 modules  $\rightarrow$  total of 77916 modules, 132 mm^2 of Si

Since Annecy: Made construction faster, and added a simplified version (30 s to load geometry)

Armin Ilg (UZH)

Optimisation of Silicon Tracking Systems

#### FCC Week 2024

- use only one disk/barrel layer, with overlapping modules to ensure hermeticity  $\rightarrow > 1$  hit

- $\rightarrow$  Require 30 ps time resolution

- Optimise disk z positioning and/or barrel length

- $\rightarrow$  No gap between disk and barrel (consider drift chamber services!)

**Barrel:** Fine resolution in  $\phi$  for momentum measurement

- Long longerons attached to support rings on DC, using a ferris wheel-like structure

- $\rightarrow$  Sensors facing IP, cables and cooling (pipes or micro-channel cooling plate) on top

**Disks:** Fine resolution in r for  $\theta$  measurement

- D-shaped half-rings  $\rightarrow$  Mounted as two separate components (disk cannot be one piece)

- Aim to mount onto sides of DC, but need to leave gap to guide DC cables out

- $\rightarrow$  Use a stilt structure attached to drift chamber, onto which rings are attached

### **IDEAs:**

- Aggregation of signal, opto-el. conversion and serial-powering on tile/along longeron

- Wireless data transmission from barrel centre and disk centre outwards?

Armin Ilg (UZH)

# IDEA silicon wrapper: What is to do

### CLD vertex and tracker

• Adaptions to accomodate ARC leave IP resolution unchanged, 15–20% worse  $p_T$  resolution, would be recovered by moving from 2 T to 3 T magnetic field

### **IDEA** vertex

- Reasonable  $d_0$  performance of IDEA vertex using CLD detector and reconstruction

- Additions such as cones for air cooling and services needed, but mostly outside of acceptance

### **IDEA** silicon wrapper

- Worked on simplified version of silicon wrapper, sufficient for first studies

- Working on adaptions to move to a single-layer design

### Ultra-light vertex detector concept

- Conceptual design, adapted from ALICE ITS3 to FCC-ee

- Compromise hermeticity (or radius of first hit) with reduced material budget

- Evaluate performance similarly to IDEA vertex

# TDAQ Occupancy studies at FCC-ee (vertex detectors) FCC Week 2024

### Armin Ilg

University of Zürich

11.06.2024

Can we run FCC-ee experiments without a trigger, to get rid of the associated uncertainties?

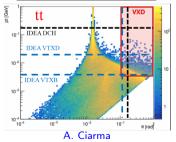

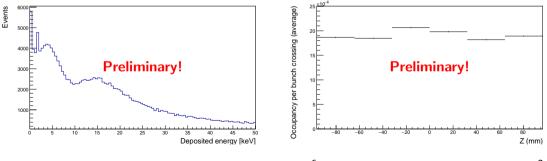

The problem is incoherent pair production in first vertex layer In 2019, in CLD vertex, a maximal occupancy of  $70\times10^{-6}$  per bunch crossing was found using GuineaPig simulation

- Assuming cluster size of 5, safety factor of 3

- $25 \times 25 \,\mu \mathrm{m}^2$  pixels

- $\rightarrow~$  Doesn't seem like a lot, but assuming bunch spacing of 20 ns at Z pole, results in 560 MHz/cm^2

- See also F. Bedeschi's talk in Annecy and A. Ciarma's talk on Thursday

Let's look at first vertex inner barrel layer of IDEA vertex detector!

Table 2: Number of pairs produced per bunch crossing (BX) at the four working points, and maximum occupancy measured in the barrel and endcaps of the vertex detector and tracker (respectively VXDE, VXDE, TRKB, TRKE).

|           |                 | Z    | WW   | ZH   | tī   |

|-----------|-----------------|------|------|------|------|

| 1         | Pairs/BX        | 1300 | 1800 | 2700 | 3300 |

| $10^{-6}$ | Omax(VXDB)      | 70   | 280  | 410  | 1150 |

| $10^{-6}$ | $O_{max}(VXDE)$ | 23   | 95   | 140  | 220  |

| $10^{-6}$ | Omax(TRKB)      | 9    | 20   | 38   | 40   |

| $10^{-6}$ | Omax(TRKE)      | 110  | 150  | 230  | 290  |

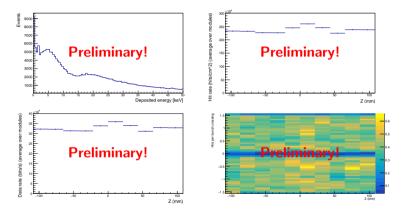

- GuineaPig files with incoherent pair production from 4000 bunch crossings at Z pole (thanks @A. Ciarma!)

- Using V23 lattice, with bunch population of  $1.7 imes 10^{11}$  (pre mid-term report)

- Paraffin-cooled AlBeMet beam pipe (not CAD beam pipe), first layer at r = 13.7 mm, 25  $\mu$ m pitch pixels, cluster size of 5, safety factor of 3

- Cut at  $E_{

m dep} \geq 1.8 \,

m keV$ , equivalent to 500 electrons

Lower occupancy than in previous study (70 imes 10 $^{-6}$ ), see hit rate of up to 170 MHz/cm<sup>2</sup>

Armin Ilg (UZH)

• Without trigger: Assume 32 bits transferred per pixel (10+8 needed for ARCADIA), could be reduced if on-chip center of gravity is reconstructed

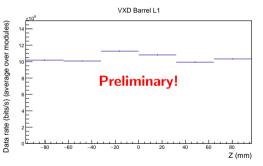

- Quite regular along z

- Recall safety factor of 3, cluster size of 5

- Will need to check impact of V24 lattice (with  $2.14 \times 10^{11}$  bunch intensity, see F. Zimmermann's slides)  $\rightarrow$  Details on lattice versions in backup

- $\rightarrow$  Need to continue these studies!

- $\rightarrow$  Triggerless readout for the moment seems neither impossible nor straightforward

- Quite regular occupancy in z and around φ (consider holes in coverage at φ = 0, π)

- Higher data rate per module mostly comes from larger area per module (~ factor 2)

- Hit rate of *O*(250 MHz/cm<sup>2</sup>)

University of

Zurich

# Conclusions

### Incoherent pair production background in IDEA vertex

- Decreased occupancies in vertex coming from lattice used

- Further studies needed

- $\rightarrow~$  Use mid-term report lattice

- $\rightarrow~$  What is the impact of an increased threshold on physics?

- $\rightarrow\,$  Can part of the background be cut away on-detector e.g. using cluster size? (need silicon digitisation with clustering algorithm in Key4hep)

### Detector optimisation: Smallest possible systematic uncertainties in detector

- Uncertainty coming from using a trigger

- Uncertainty coming from material budget

- Uncertainty coming from spatial resolution

- → Smaller pixels, larger cluster sizes, trigger-less readout and on-detector processing lead to more power consumption → More cooling → More material budget → Uncertainty!

- $\rightarrow~$  Need to consider all aspects simultaneously!

# Thanks!

### References I

- [1] N. Bacchetta, et al., CLD A Detector Concept for the FCC-ee, arXiv:1911.12230 [physics.ins-det].

- [2] D. Dannheim, et al., CERN Yellow Reports: Monographs, Vol 1 (2019): Detector Technologies for CLIC, tech. rep., 2019.

- [3] IDEA Collaboration, G. F. Tassielli, A proposal of a drift chamber for the IDEA experiment for a future e<sup>+</sup>e<sup>-</sup> collider, in Proceedings of 40th International Conference on High Energy physics — PoS(ICHEP2020).

Sissa Medialab, Feb., 2021.

- [4] FCC Collaboration, FCC-ee: The Lepton Collider, The European Physical Journal Special Topics 228 (2019) 261–623.

- M. Mager, On the "bendable" ALPIDE-inspired MAPS in 65 nm technology, 11, 2021. https://indico.ihep.ac.cn/event/14938/session/6/contribution/196. 2021 International Workshop on High Energy Circular Electron Positron Collider.

- [6] F. Reidt, Upgrading the Inner Tracking System and the Time Projection Chamber of ALICE, Nuclear Physics A 1005 (2021) 121793.

- [7] L. Freitag, Benefits of Minimizing the Vertex Detector Material Budget at the FCC-ee, 2023. http://cds.cern.ch/record/2851362. BSc thesis, presented 01 Feb 2023.

- T. Jones, CEPC Silicon /LHCb MT Tile, 2020. https://indico.ph.ed.ac.uk/event/65/contributions/814/Presentation at the First UK workshop on HV-CMOS technology for future e+e- colliders, University of Edinburgh.

- H. Zhu, A large tracking system with novel HV-CMOS sensors for the CEPC, 2021. https://indico.inp.nek.su/event/42/contributions/2186/attachments/1355/1777/CEPC\_Silicon\_Tracker\_AFAD.pdfPresentation at the Asian Forum for Accelerators and Detectors (AFAD), BINP.

- [10] M. Tornago, Detector optimization and physics performance of the CMS Phase-2 Endcap Timing Layer, 2023. https://cds.cern.ch/record/2848200. Presented 13 Feb 2023.

Armin Ilg (UZH)

TDAQ Occupancy studies at FCC-ee (vertex detectors

FCC Week 2024

1.06.2024 30 / 29

#### Further performance plots

| Study                  | Lattice | Bunch population [10 <sup>11</sup> ] | Bunch spacing [ns] |

|------------------------|---------|--------------------------------------|--------------------|

| CLD study              | VXX     | X.X                                  | 30                 |

| Det. concept last week | V22     | 2.4                                  | 19.2               |

| This work              | V23     | 1.7                                  | 19.2               |

| To do (mid-term)       | V24     | 2.14                                 | 25                 |

## IDEA vertex detector: Design

Vertex detector by INFN Pisa (more details in F. Palla's talk at 2nd FCC US Workshop), support tube by INFN-LNF, holding lumical, vertex and beam pipe (more on MDI in M. Boscolo's talk)

Vertex outer barrel and vertex disks using quad ATLASPix3 DMAPS with 150  $\times$  50  $\mu m^2$  pixels, water-cooled

Vertex inner barrel consisting of staves of dual ARCADIA DMAPS, with pixels of  $25 \times 25 \,\mu\text{m}^2$  ( $\sim 3 \,\mu\text{m}$  single point resolution), air-cooled

Only contribution in last two bins

○ FCC

F. Palla, 2nd FCC US Workshop

#### Data rates issues (see F. Bedeschi talk at 7th FCC Workshop)

- Largest data rates occur at the Z energy

- Expected data rates per BX/module [cluster size 5]

- From machine backgrounds (Incoherent pair creation safety factor of 3) ~ 19 hits/BX/module

- From collisions (200 kHz) ~ average ~<1 hit/BX/module</li>

- Inner layer ~400 MHz/cm<sup>2</sup> → ~25 Gb/s per module

- might be reduced if cluster size is only 2 as measured for many MAPS

- ALICE3 hit rate ~100 MHz/cm<sup>2</sup> (pixel size 10µm x 10µm)

- 2<sup>nd</sup> layer ~10x less data volume

- · Triggered readout: for 200 kHz the data bandwidth per module, rate is only 150 Mb/s

- Impact on physics?

- All these depend on pixel pitch, thickness, R/O architecture, bias voltage.

- For a review see M. Winter talk at March 11 meeting

#### F. Palla, 2nd FCC US Workshop

#### Same reticle for all layers

| Layer | Radius<br>(mm) |

|-------|----------------|

| 1     | 13.7           |

| 2     | 20.23          |

| 3     | 26.76          |

| 4     | 33.3           |

Layer 1&2

Layer 3&4

1.5

20.52

٨

|                                                                 | Power density<br>$[mW cm^{-2}]$ |                         |                         |

|-----------------------------------------------------------------|---------------------------------|-------------------------|-------------------------|

|                                                                 | Expected<br>25 °C               | Max<br>25 °C            | Max<br>45°C             |

| eft End Cap (LEC)                                               |                                 | 791                     |                         |

| Active area (RSU)                                               | 28                              | 44                      | 62                      |

| Pixel matrix<br>Biasing<br>Readout peripheries<br>Data backbone | 15<br>168<br>432<br>719         | 32<br>168<br>457<br>719 | 51<br>168<br>496<br>719 |

Power dissipation in ITS3 (not necessarily the same for FCC-ee)

- RSU~ 50 mW/cm<sup>2</sup> (depends on Temp.)

- LEC ~ 700 mW/cm<sup>2</sup>

024 38 / 29

#### Fabrizio Palla – Pisa & CERN – 2nd Annual U.S. FCC Workshop – MIT – 25 - 27 March 2024

Armin Ilg (UZH)

TDAQ Occupancy studies at FCC-ee (vertex detectors

FCC Week 2024

11.06.2024 39 / 2

## IDEA Silicon Wrapper material budget

- Flex and cooling pipes (same as in vertex outer barrel and disk), 50 μm silicon, 1.4 mm of carbon fibre

- Adjust material budget when engineered design becomes available

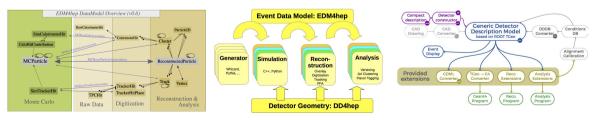

Key4hep is a huge ecosystem of software packages adopted by all future collider projects, complete workflow from generator to analysis

- Event data model: EDM4hep for exchange among framework components

- Podio as underlying tool, for different collision environments

- Including truth information

- Data processing framework: Gaudi

- Geometry description: DD4hep, ability to include CAD files

- Package manager: Spack: source /cvmfs/sw.hsf.org/Key4hep/setup.sh

Armin IIg (UZH) TDAQ Occupancy studies at FCC-ee (vertex detectors

FCC Week 2024

1.06.2024 41 / 2