# ITk pix Production QC training

2023/06/26~30

Karin Kuramochi

# Today's topics

- repicで行われる作業

- Assembly

- Metrology

- Electrical test

- ・ 1週間何を行ったか

- 測定結果

- 問題点

#### 6/26~30 ハヤシレピック館山工場に行ってきました

6/26~30にかけてハヤシレピック館山工場にて 量産作業のトレーニングとMetrology Machine GUIのデバッグなどを行った。

筑波大学(館山)

## repicで行われる作業

#### 現在行われている作業

- 1. Moduleアセンブリ

- 2. ASSEMBLED ITk Pix module Metrology

- 1. Visual Inspection(両面)

- 2. Size scan

- 3. WIREBOMDING module

- 1. Visual Inspection

- 2. Wire Bond Height scan

- 1. warm =  $20^{\circ}$ C

- 1. IV scan

- 2. SimpleScan

- 3. MHT(Minimum Health Test)

- 4. TUN(Tuning)

- 5. PFA(Pixel Failure Analysis)

- 6. disconnected bump scan

- 7. threshold scan w/o HV

- 8. x ray scan

- 2.  $cold = -15^{\circ}C$

- 5. Parylene

- 6. Mechanical Protection

- 7. Thermal Cycle(10 times)

- 8. Burn in

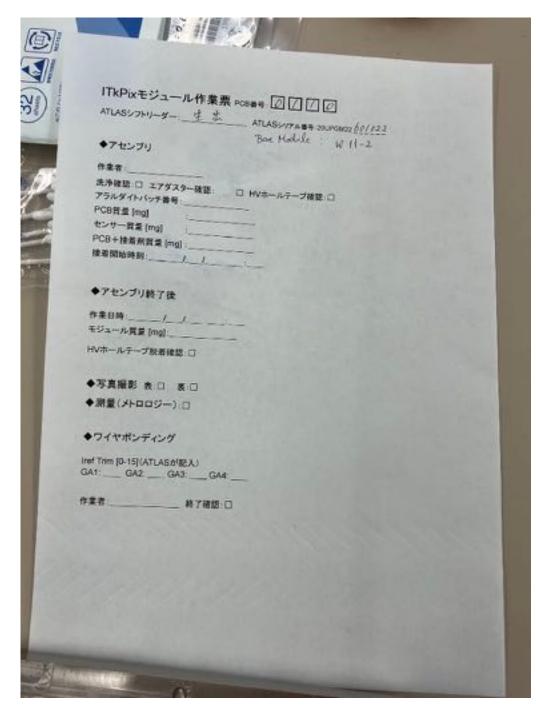

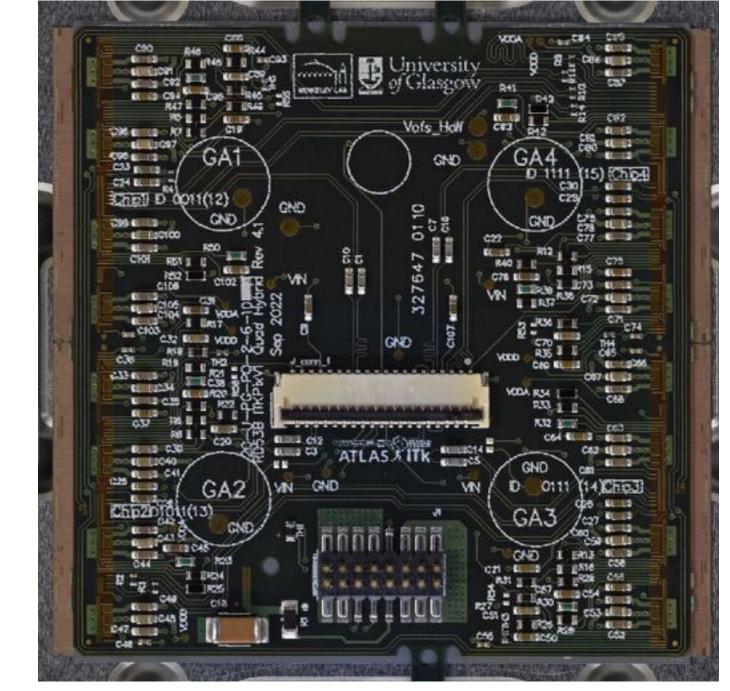

## Assembly

- ・作業を行うのは基本シフトリーダー(スタッフ)のみ

- ・ 記録は作業シート(紙)で行い、Repicの人に伝達する。

- Module SNとBare moduleのw#-#を記録

- Module SNと Flex SNの下6桁が同一

- 1台のアセンブリには12時間程度かかるためAssembled module のQCは翌日

Repic用module作業シート

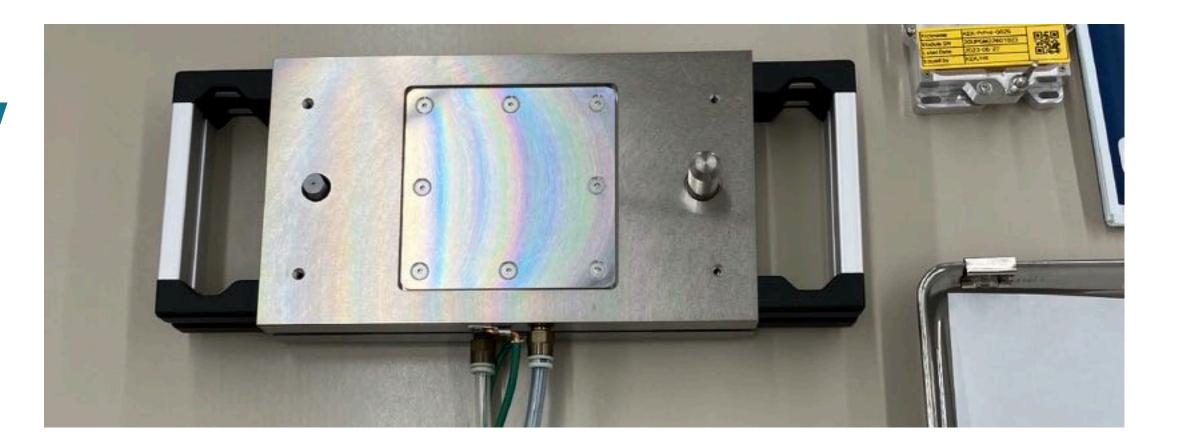

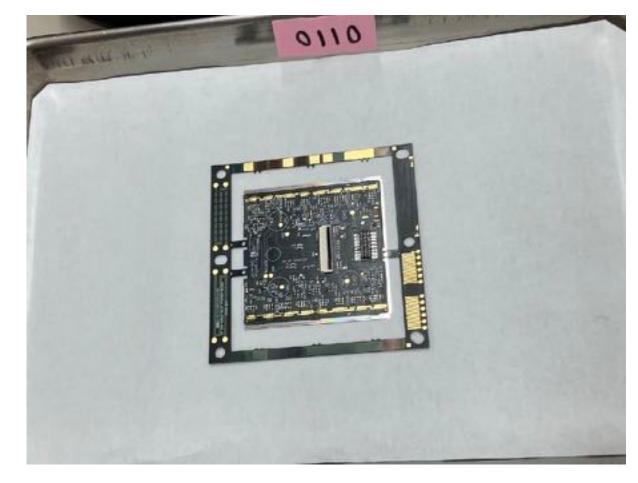

Assembled module

#### Assembled module Metrology

#### 測定項目

- photo scan

- photo scan(LED ON)

- Size scan

- Back side photo scan

### Wirebonded module Metrology

#### 測定項目

- photo scan

- photo scan(LED ON)

- Wire Bond Height scan

# Metrology GUI

・Visual InspectionとMetrologyを行うGUIが実装されている (made by 河野さん)

・ Metrology 測定後はGUIにdataを読み込ませてmoduleの状態をcheckする

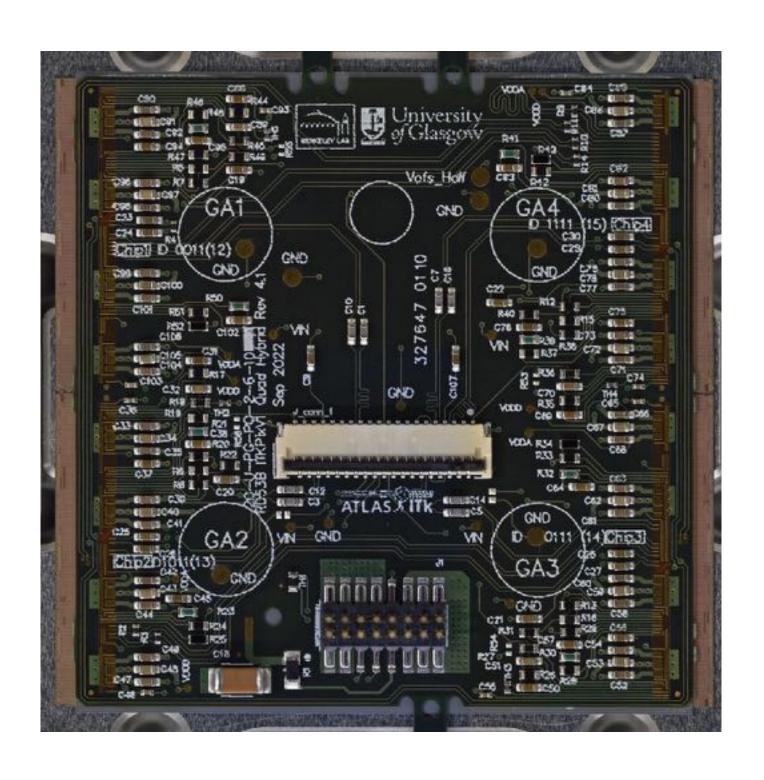

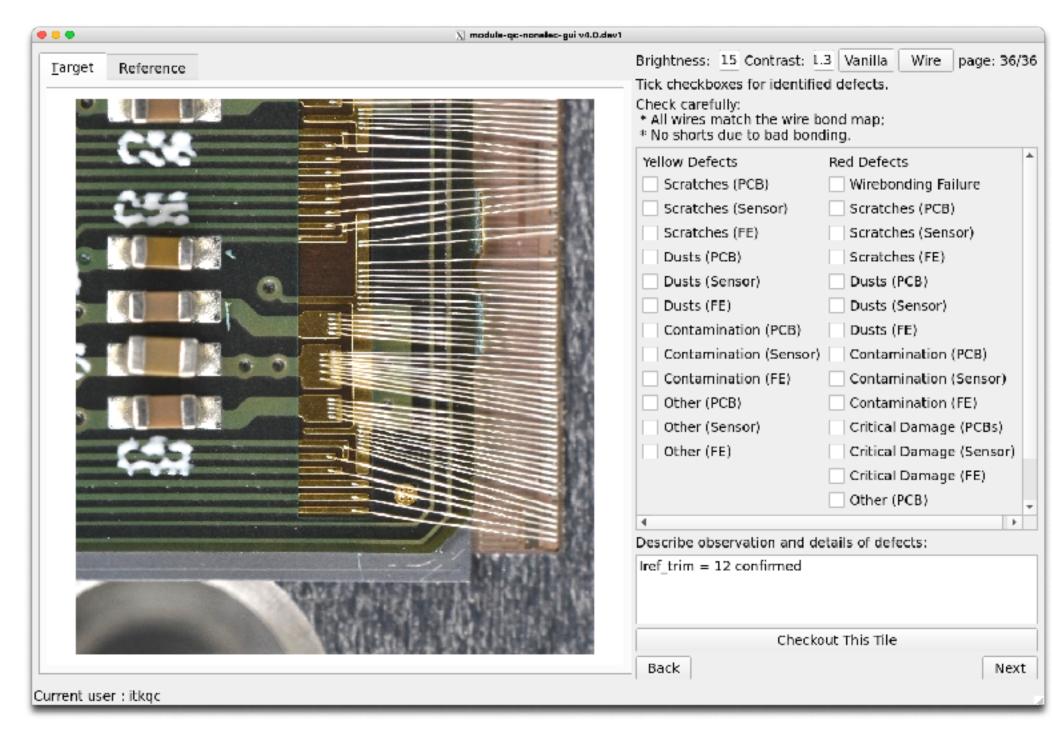

Visual Inspection GUI

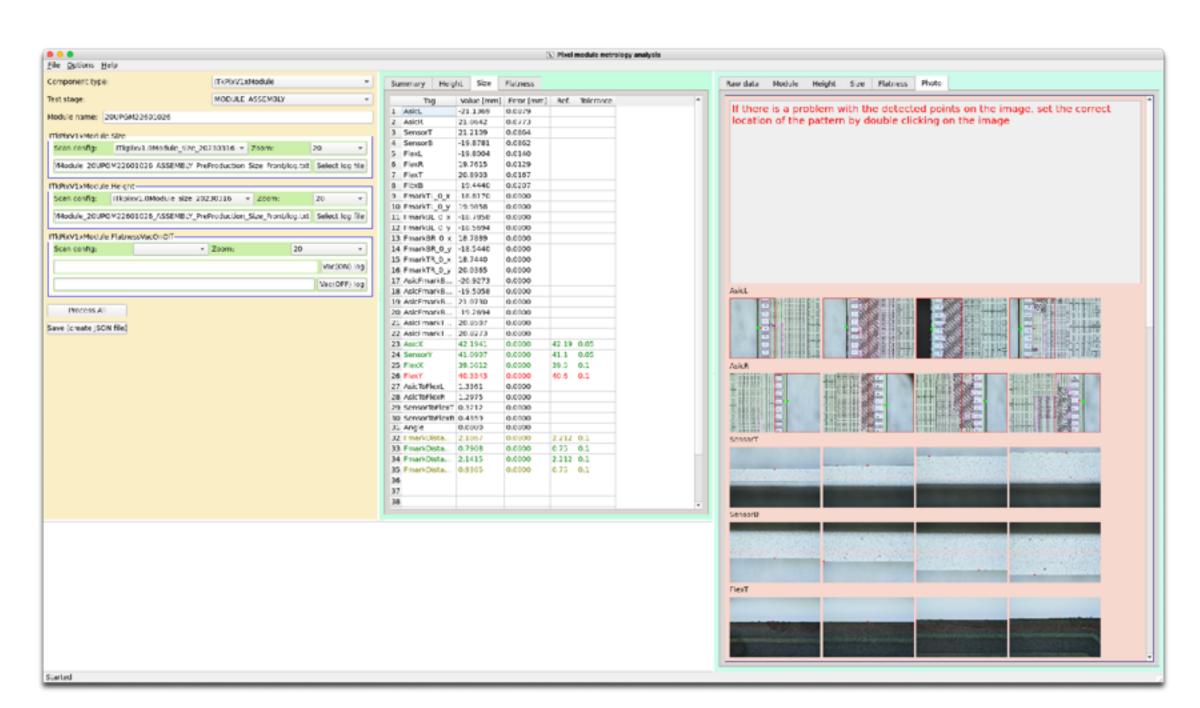

Metrology GUI

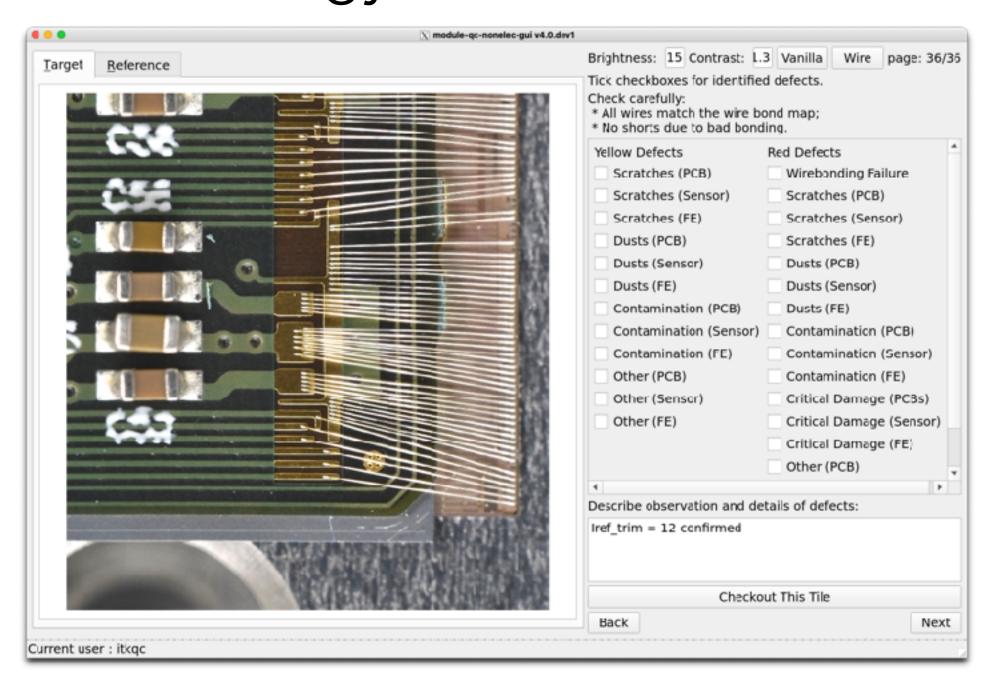

# Visual Inspection

- OpenCVで自動識別されたmoduleの画像を36分割し、傷やゴミ、欠けなどがあった場合左のcheckboxに記入してlocalDBにuploadする。

- Wirebond前やmodule裏面でも同様 にInspectionが行われる。

Visual Inspection GUI

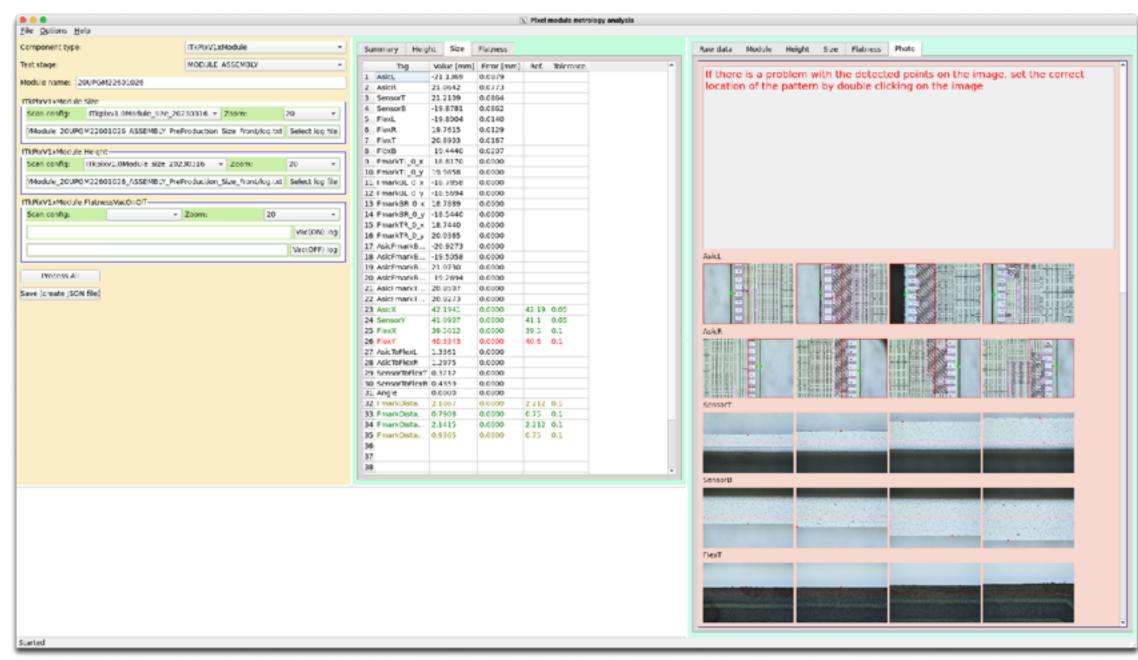

# Metrology

- Assembled moduleのsize scan dataからmoduleの高さを測定

- 同様にsize scanの写真からASICと PCBの大きさ、Fiducial markの距離 を測定

- ・ASICのedgeはまだ検出できないので 手動で指定する必要がある(要改善)

Metrology GUI

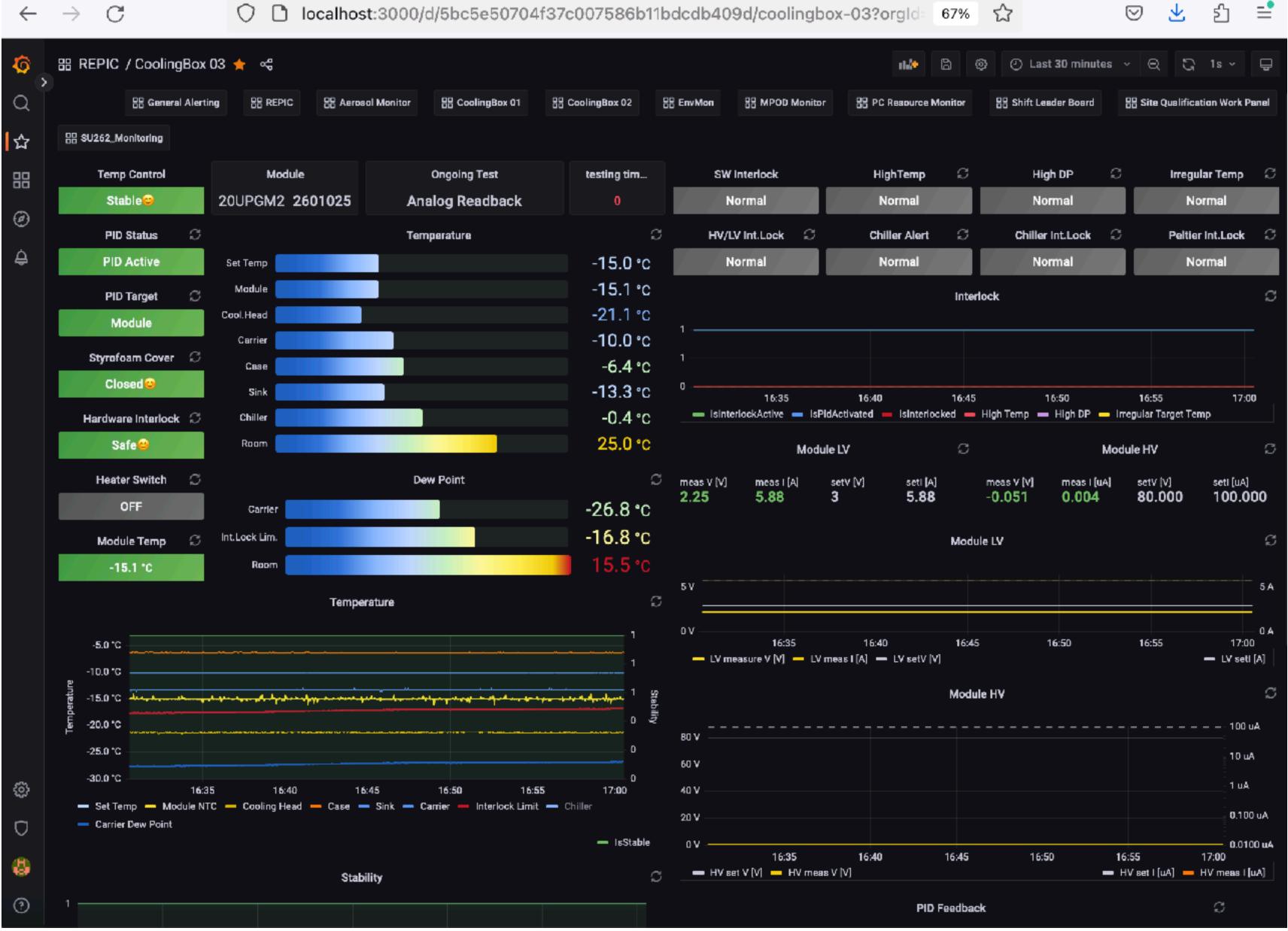

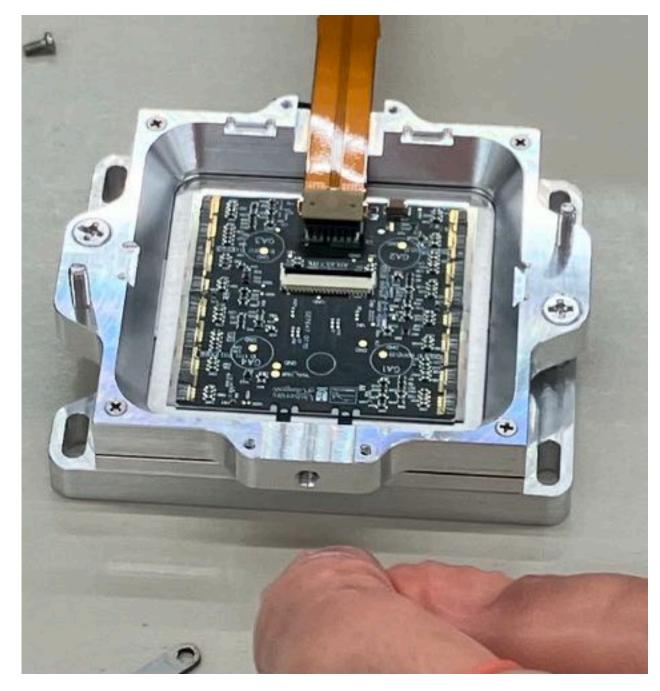

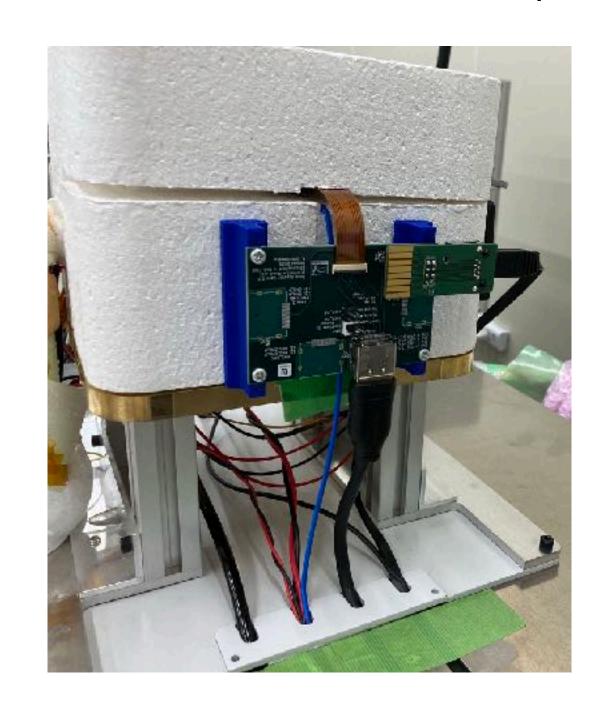

### Electrical test

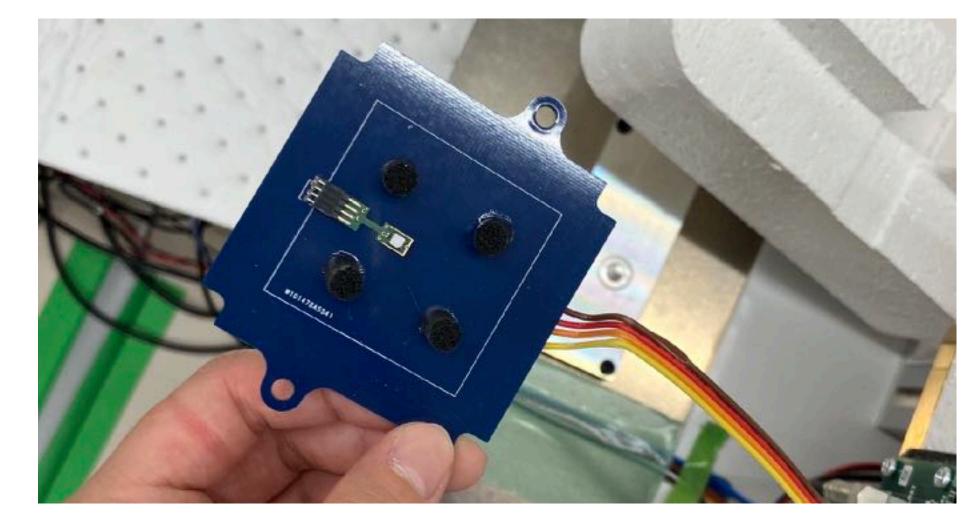

Wirebond moduleのMetrology後 moduleをキャリアに

moduleをcooling boxに入れてtest

2種類の温度でtest それぞれにconfigが 別に存在

- 1. warm 20°C

- 2. cold -15°C

キャリアに入ったmodule

cooling box

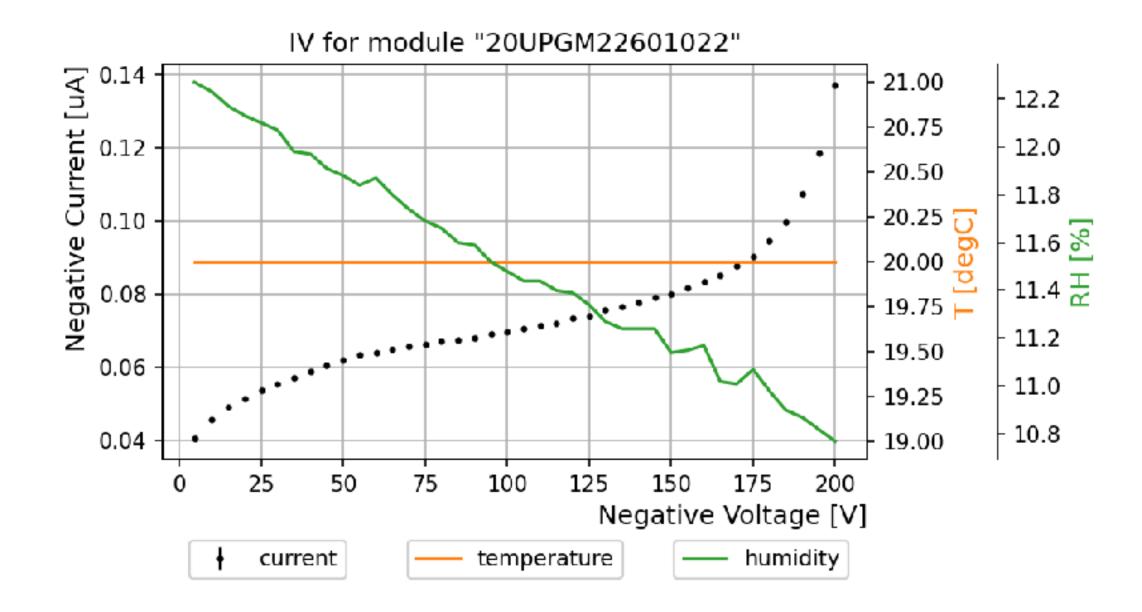

#### IV test

- moduleのsensor IVを測定

- Baremodule IVと同様5V step 0~200V

- moduleのマルチプレクサから測定

localDBから閲覧できるplot

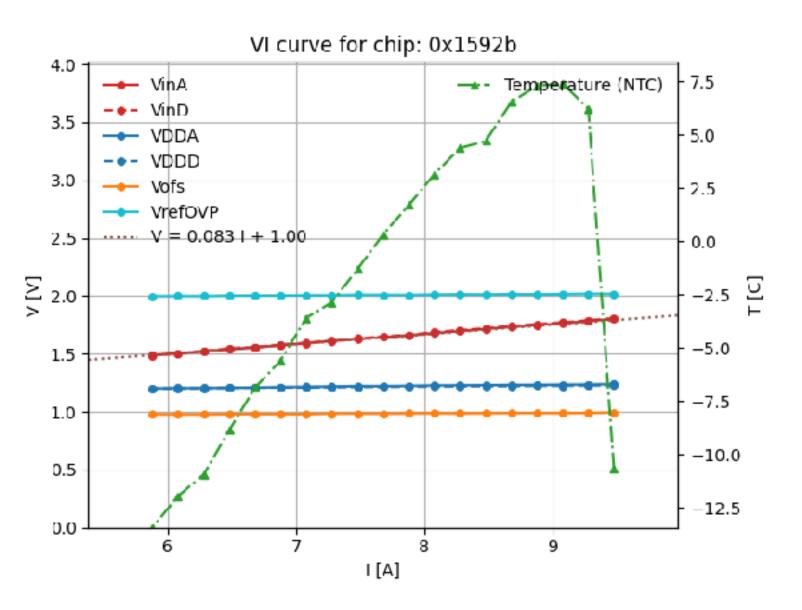

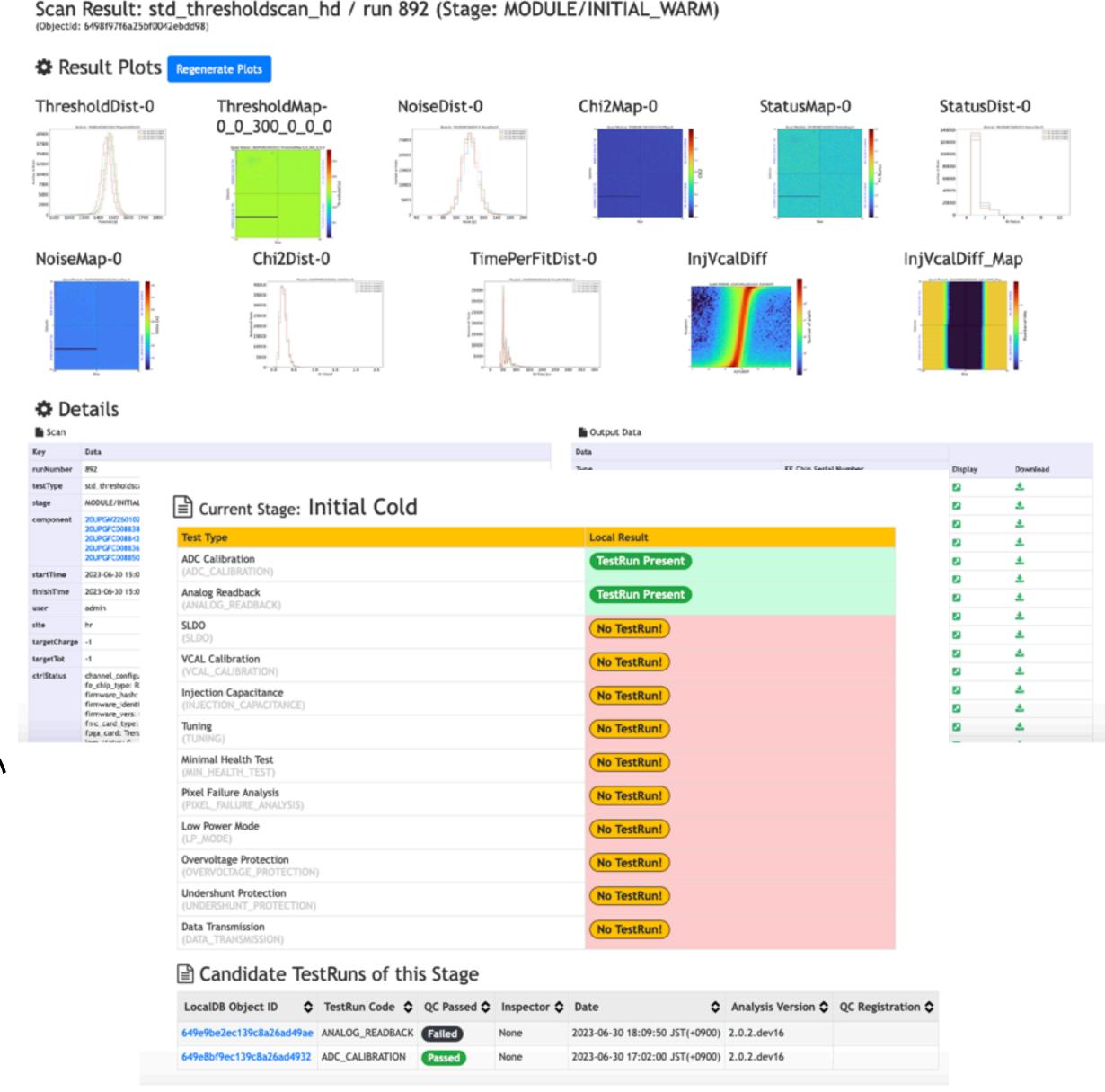

# Simple scan

#### 測定項目

- ADC calibration

- Analog readback

- SLDO

- VCAL\_CALIBRATION

- INJECTION\_CAPASITANCE

moduleの電源周りのscanを行っている

全部のscanにかかる時間:約2時間

Analog readback scanはよくscanが失敗する 1chipごとにscanしているのになぜ?

CCを変えた時にかかるVoltageの変化

失敗したscanの例

### Minimum Health Test

#### 測定項目

- Digital scan

- Analog scan

- Threshold scan

- Tot scan

tune前のmoduleのreadout scanが正常にできるかどうかを調べる

ここで正常にreadoutできない場合 cooling box占有できる状態であれば 解消に向けて対処する

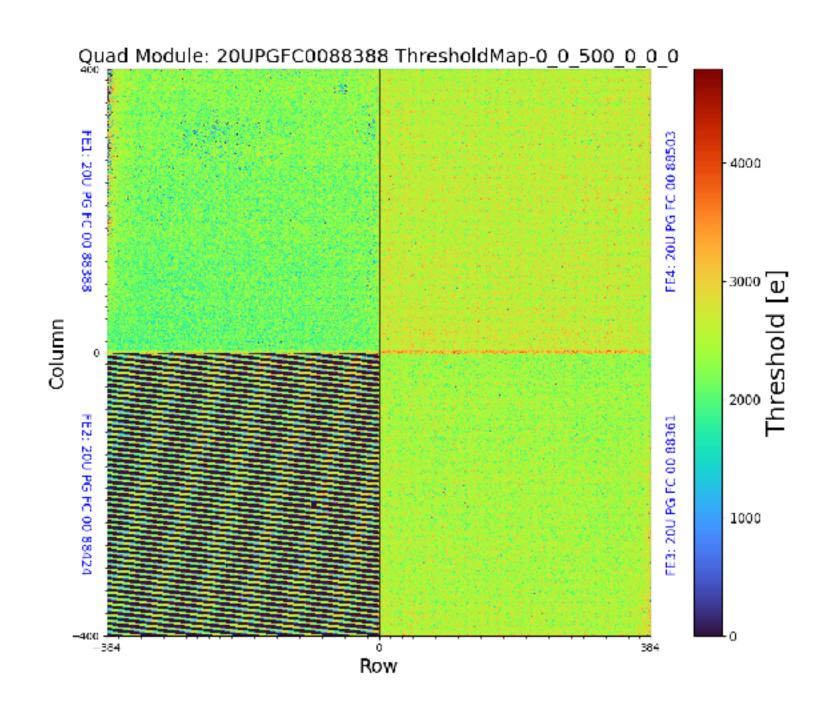

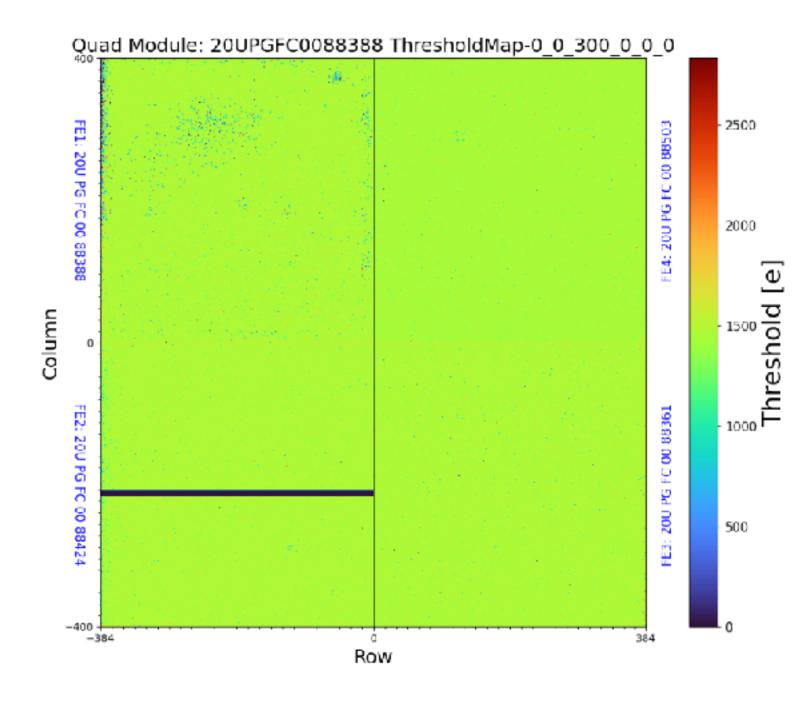

tune前のthreshold scan結果

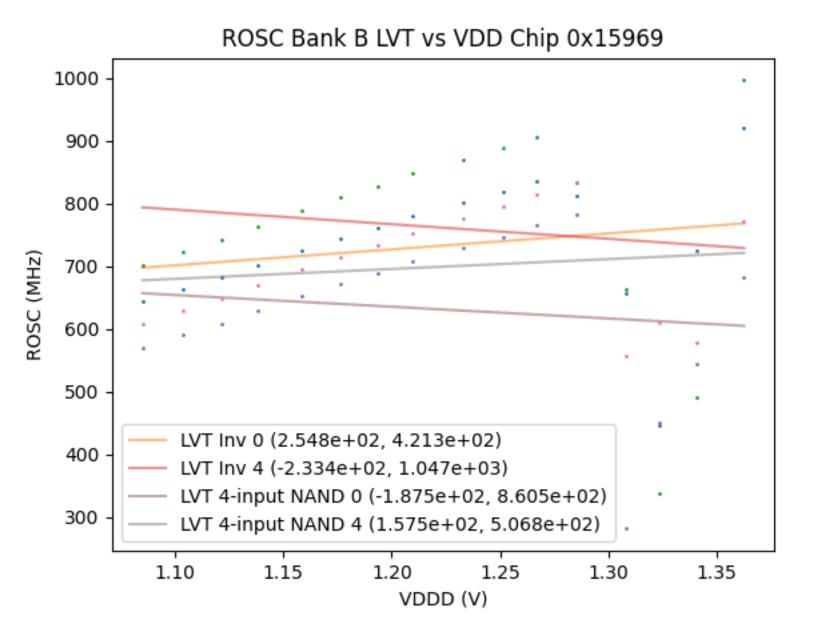

## Tuning, Pixel Failure Analysis

- Tuning

- 測定項目

- Ostd\_tune\_globalthreshold.json -t 2000

- ostd\_thresholdscan\_hr

- Ostd\_totscan

- Ostd\_tune\_globalthreshold.json -t 2500

- Ostd\_tune\_pixelthreshold.json -t 2000

- Ostd\_retune\_globalthreshold.json -t 1500

- Ostd\_retune\_pixelthreshold.json -t 1500

- ostd\_thresholdscan\_hd.json

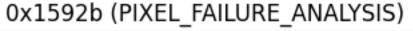

- Pixel Failure Analysis (PFA)

- Digital Scan with clear mask

- Analog Scan

- Threshold Scan (high res, low range)

- Noise Scan (10M trigger)

- ToT Scan

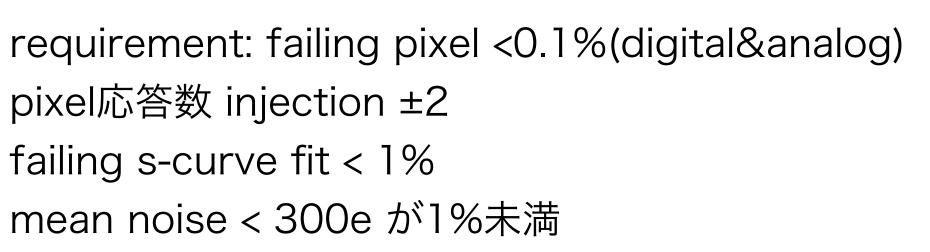

PFAはdigital,analogでのbad pixel tune failure pixelを数え上げ, requirementを満たしているかcheck

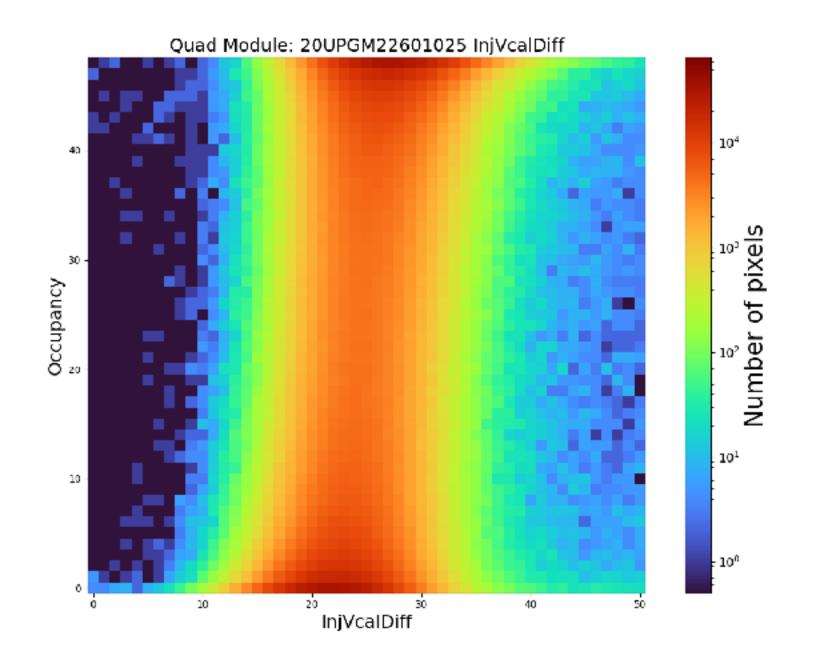

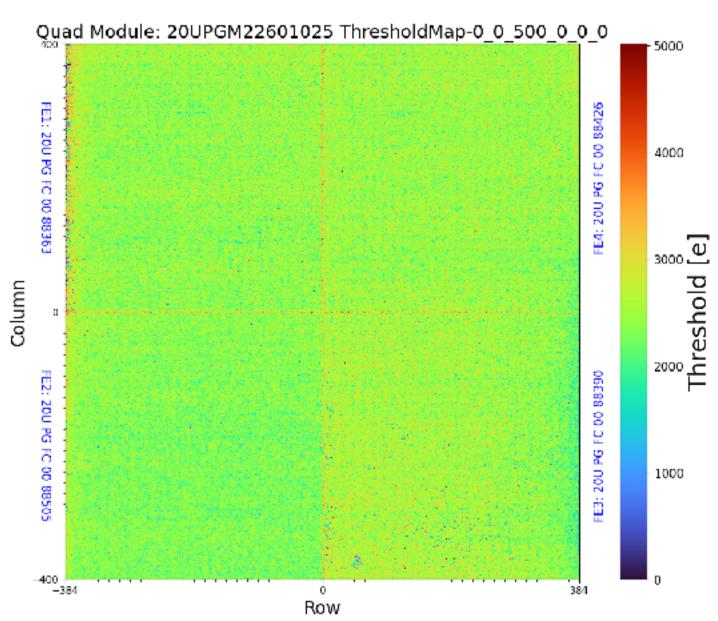

#### PIXEL\_FAILURE\_ANALYSIS for 0x1592b

| Parameter           | Analysis result | QC criteria | Pass  |

|---------------------|-----------------|-------------|-------|

| ELECTRICALLY_FAILED | 3737            | [0, 153.6]  | False |

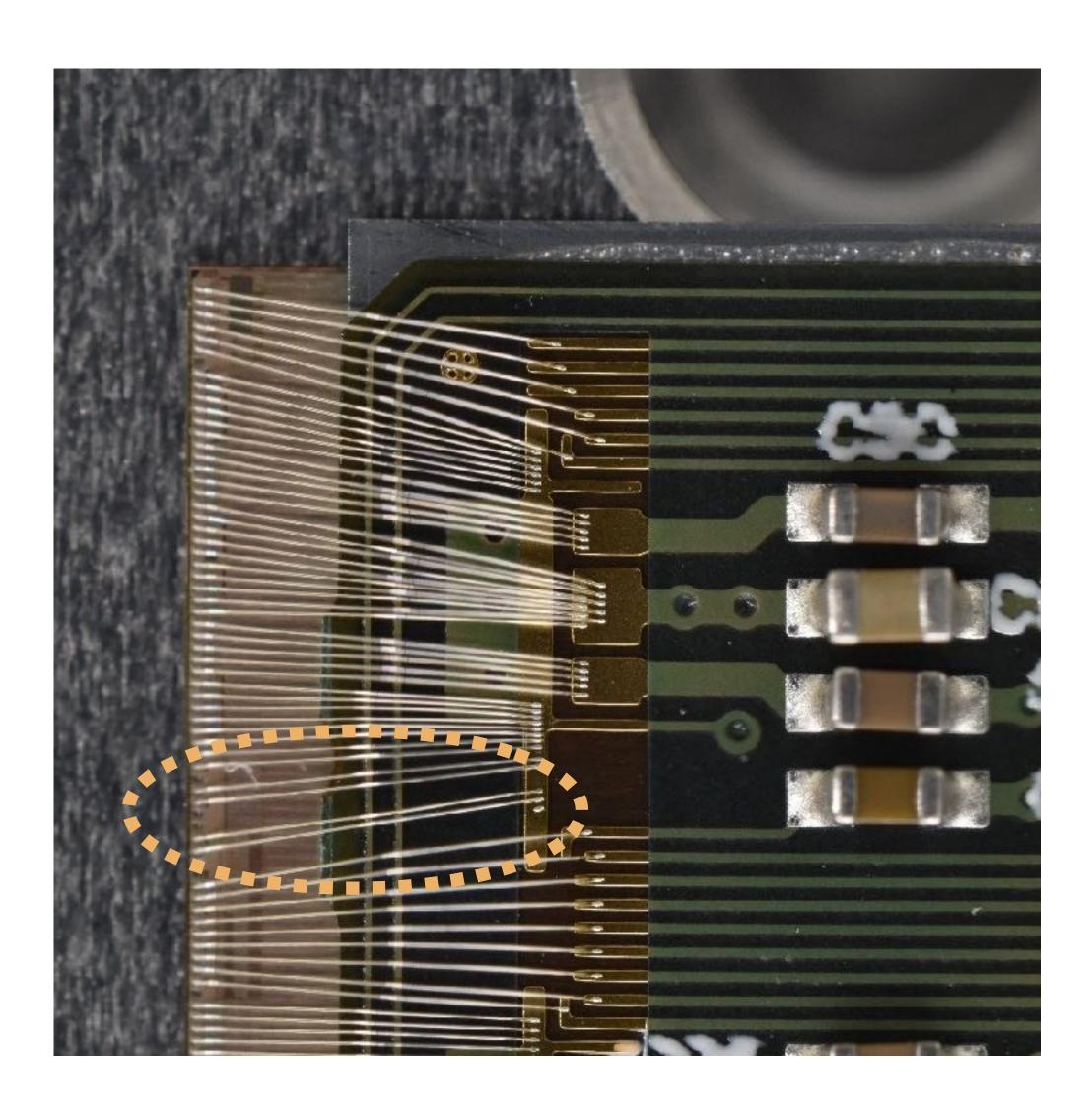

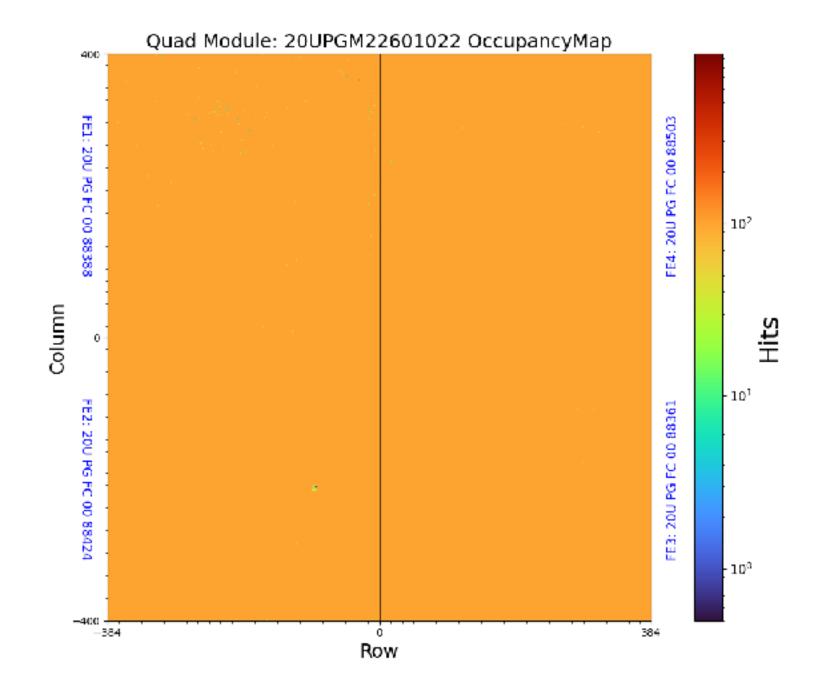

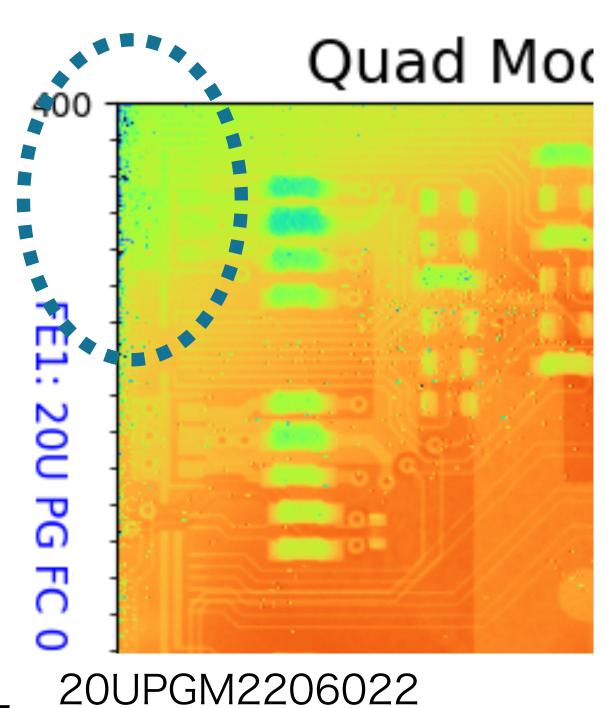

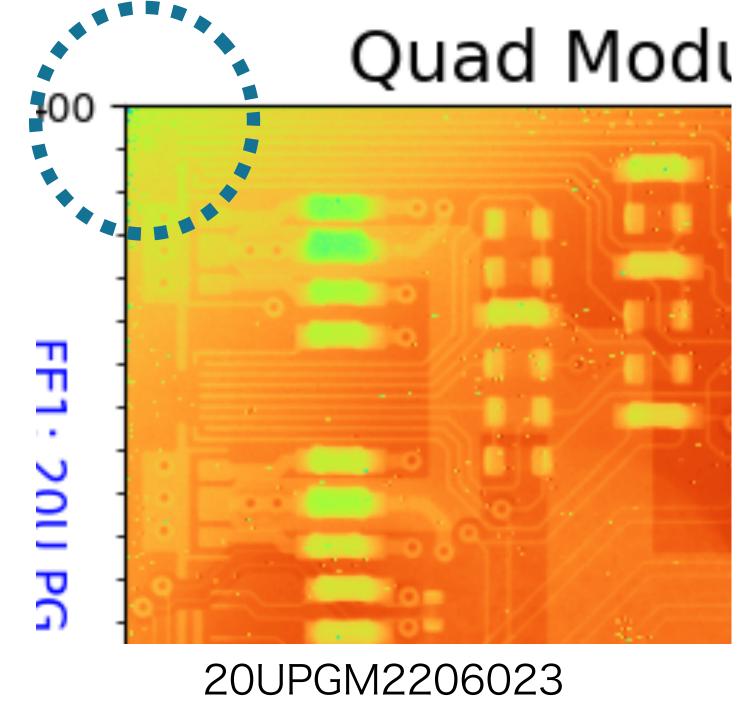

### Disconnected bump scan

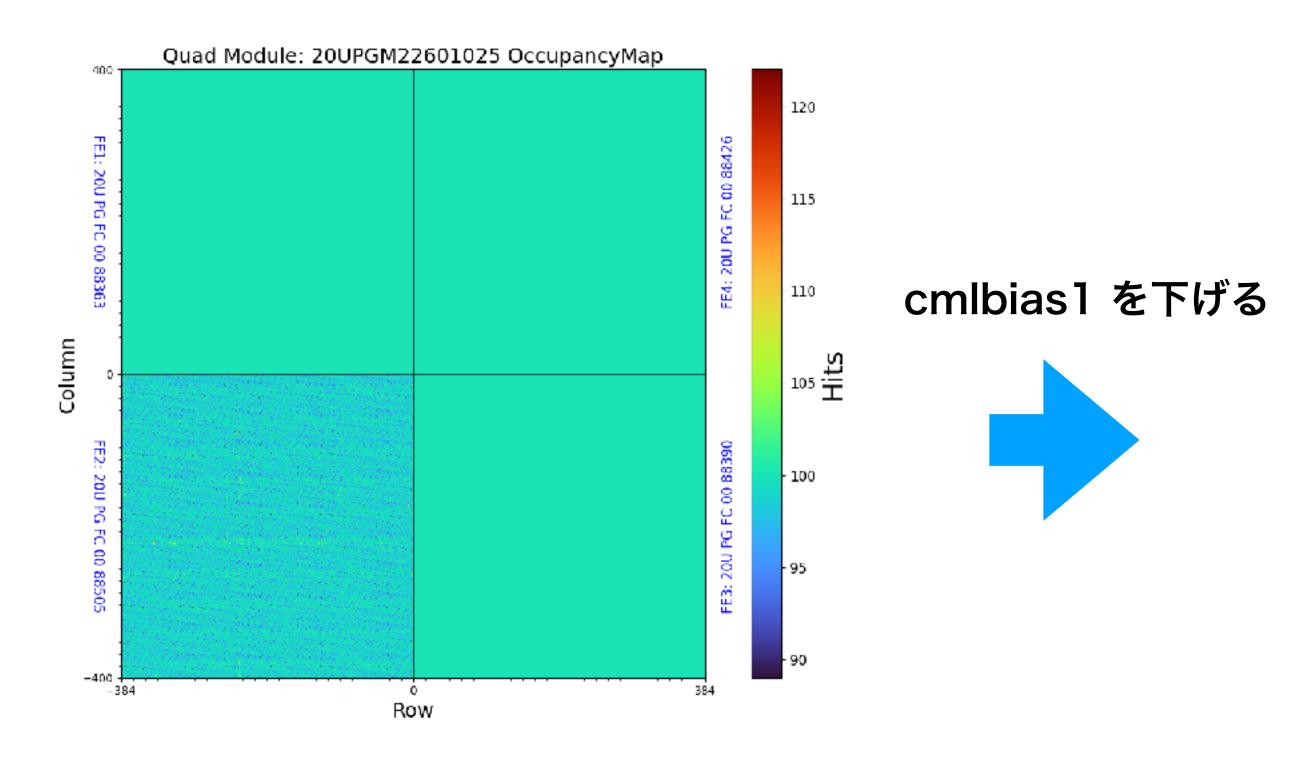

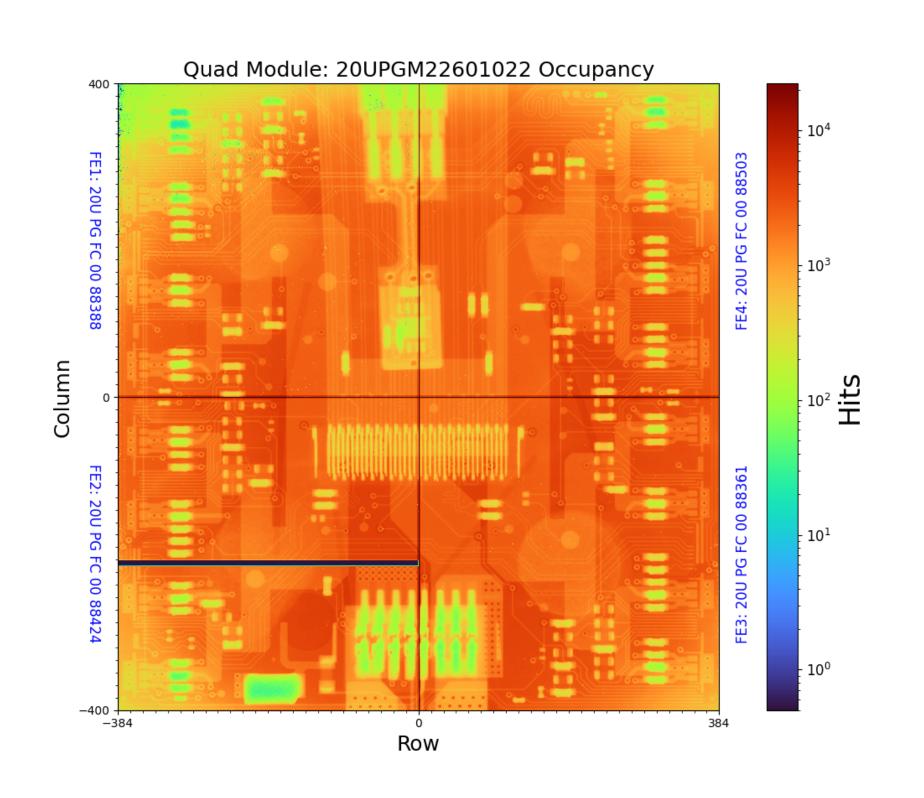

- bump剥がれの有無を調べる

- ・複数のmoduleでchip1の端に剥がれ?のようなものが見つかる

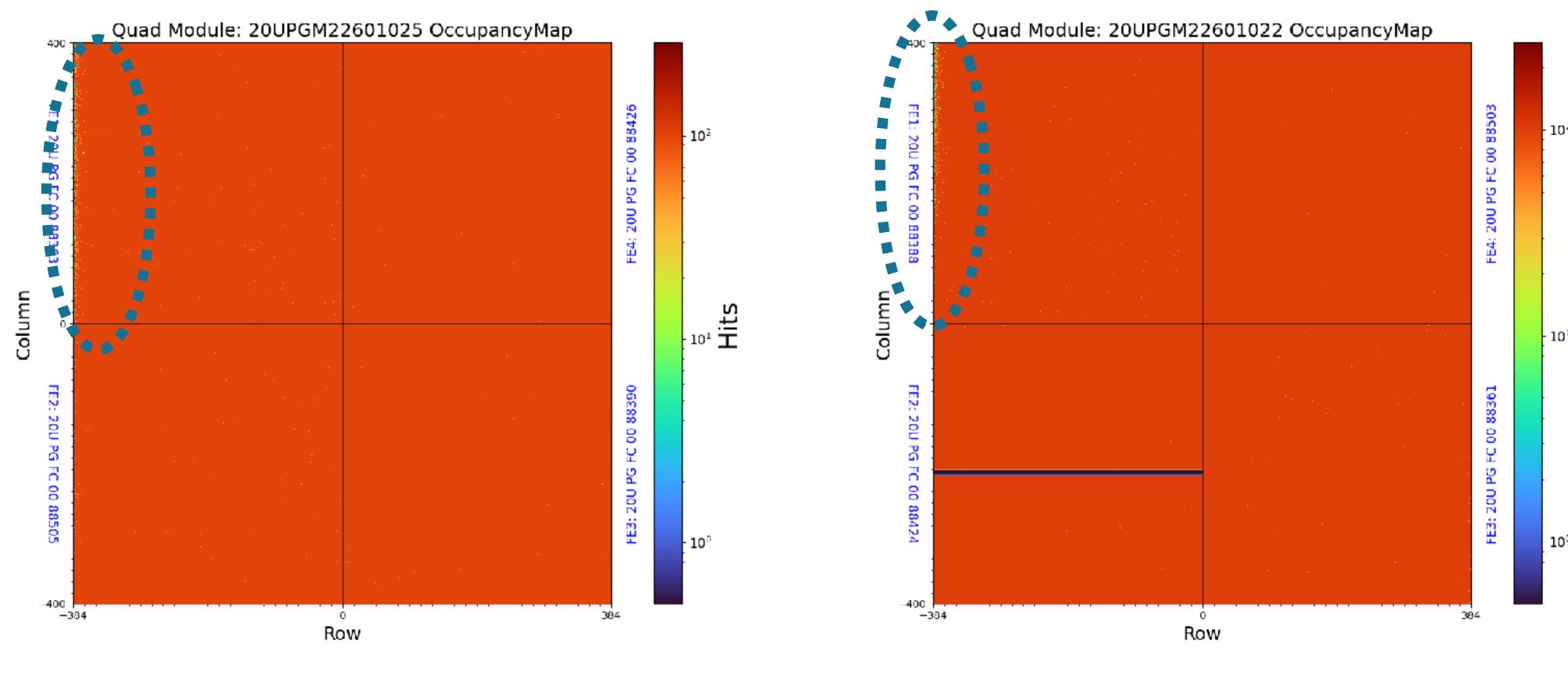

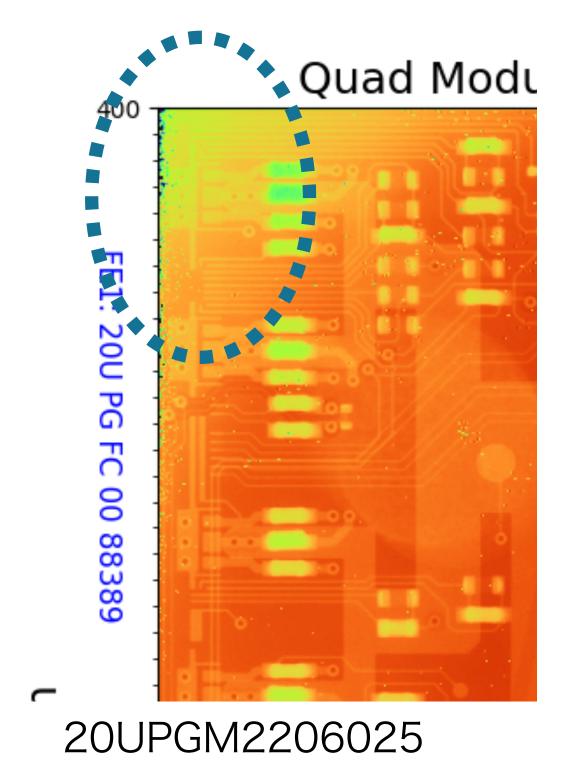

20UPGM22601025

20UPGM22601022

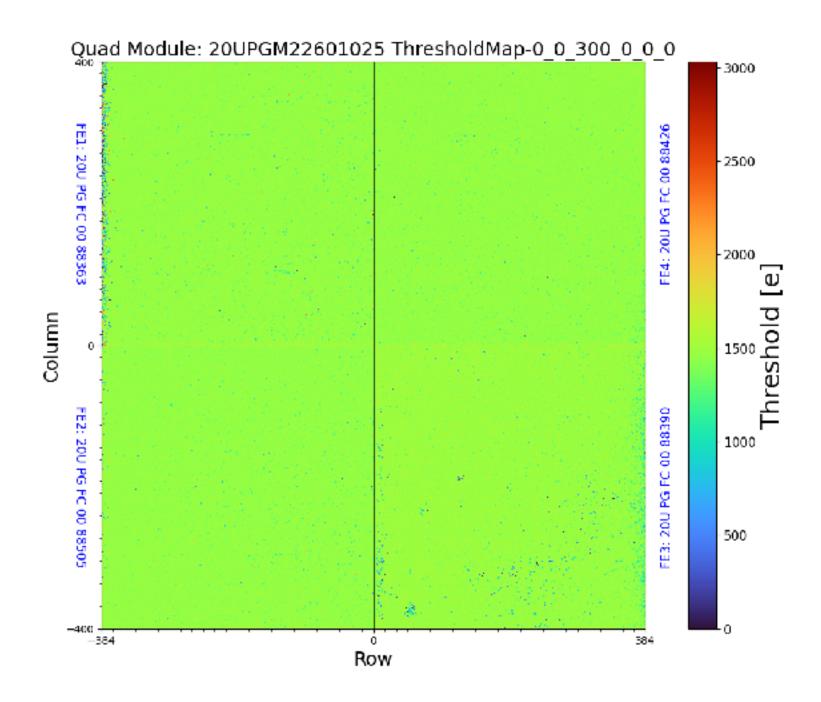

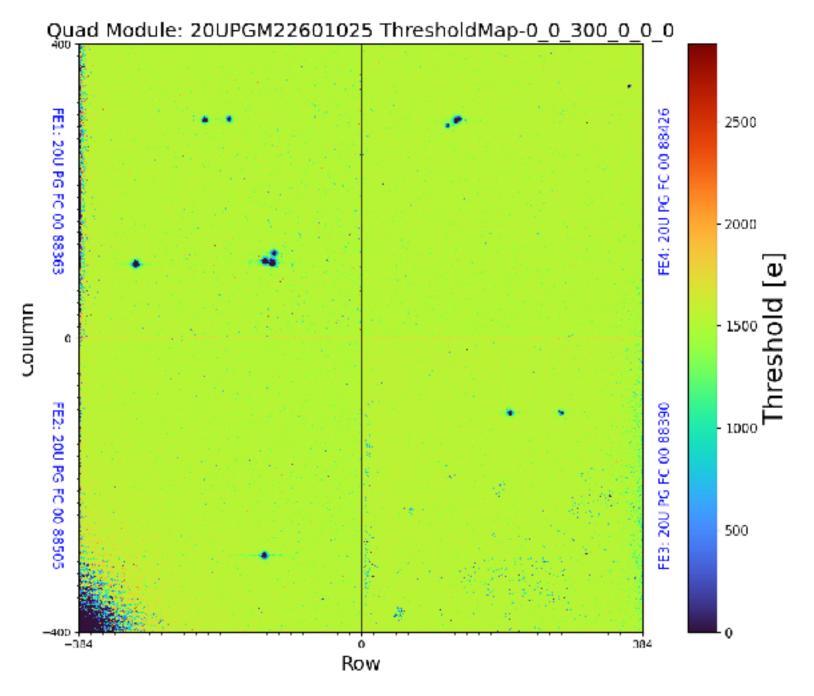

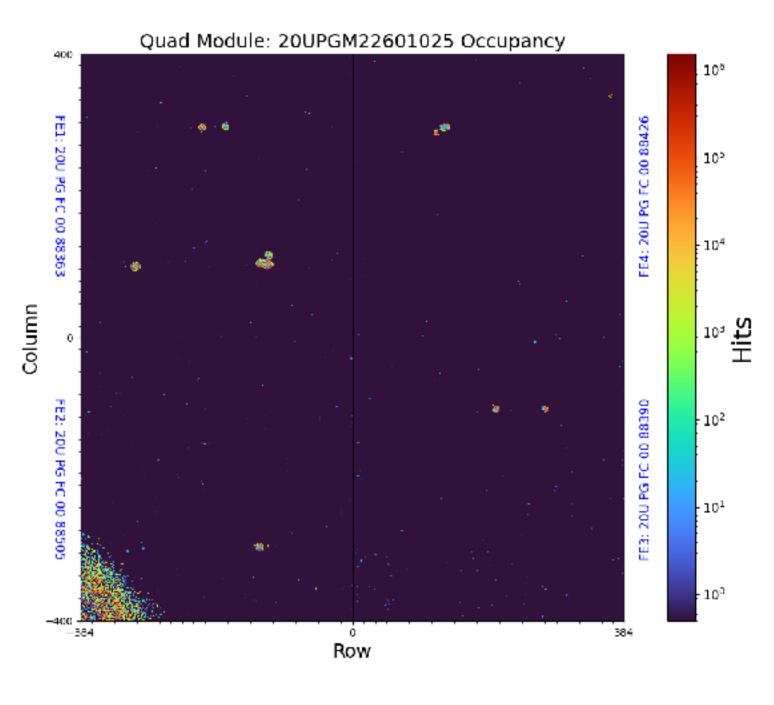

## Threshold scan w/o bias

- ・ bias voltage(HV)をかけずに同じconfigでthreshold scan

- HVonだとみられないspotが存在noise scanで調べたところHVをかけない時のみnoisyなpixelが悪さをしている

Threshold scan (HV on) 2023/07/07

Threshold scan (HV off)

noise scan (HV off)

## xray scan

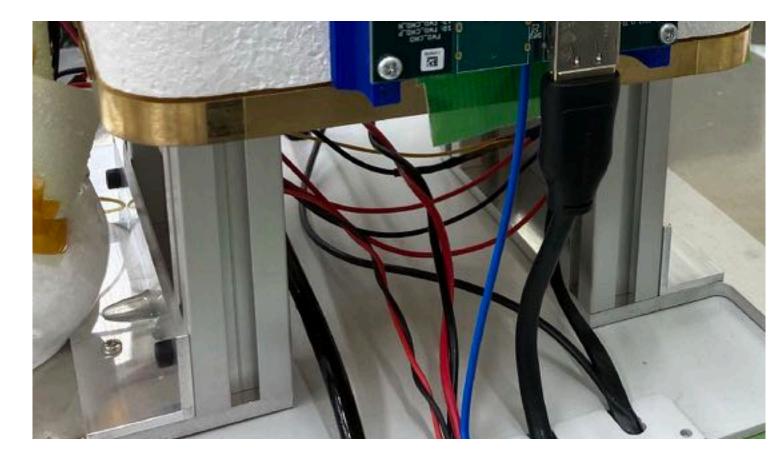

- 写真のようなx線照射装置を用いてscan

- cooling boxに被せる形

- ・ 運搬時は水平に保つ必要があり、2人がかりで行う

- ・x線装置を扱う際にガラスバッジ等は不要だが 装置が動いている間はできるだけ近づかないこと

- ・ scanは2分間

- ・x線を出さない時は常に鍵をoffにしておくこと

x線照射装置

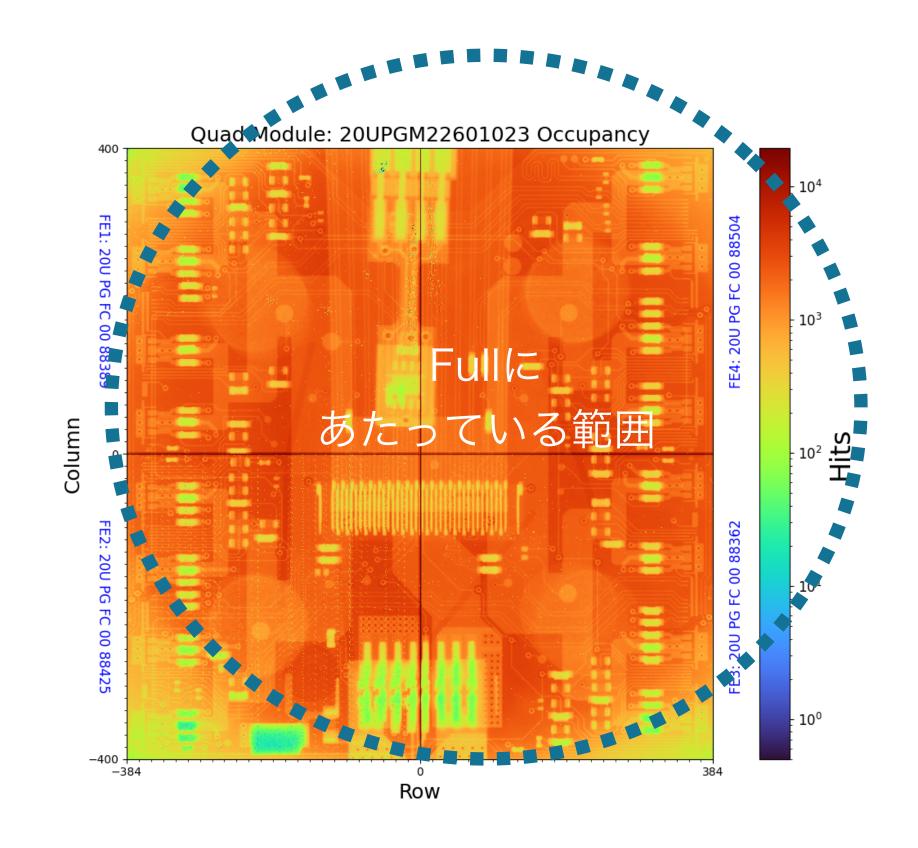

## xray scan

- 2分間x線を照射し、sensorからのdataを読み出せるかをtest

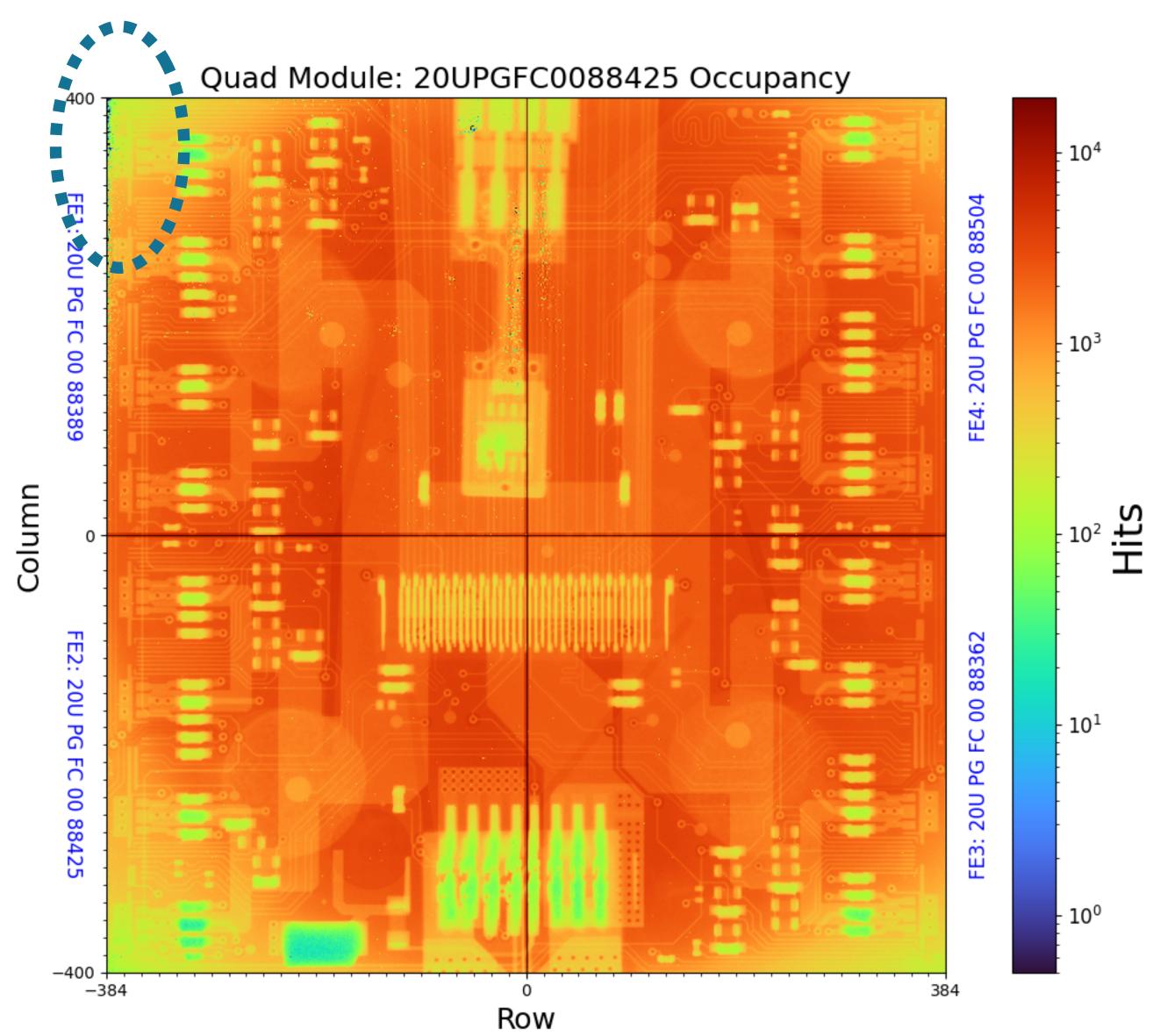

- bump剥がれがあるpixelなどは 図のようにhitが返ってこない

- QC testの結果をまとめている。

- dataをuploadするとsite上で結果のplot等を 閲覧できる。

- 各QC Testが終わった際にdataをuploadして sign offする必要がある

- 閲覧にはrepicのlocalDB pcのアカウントが必要 廣瀬さん(阪大)にメールで申請するともらえる

- ・詳しい使い方はここ→(<u>link</u>)

#### yarr scanの結果

各QC testの進捗状況とtestの合否

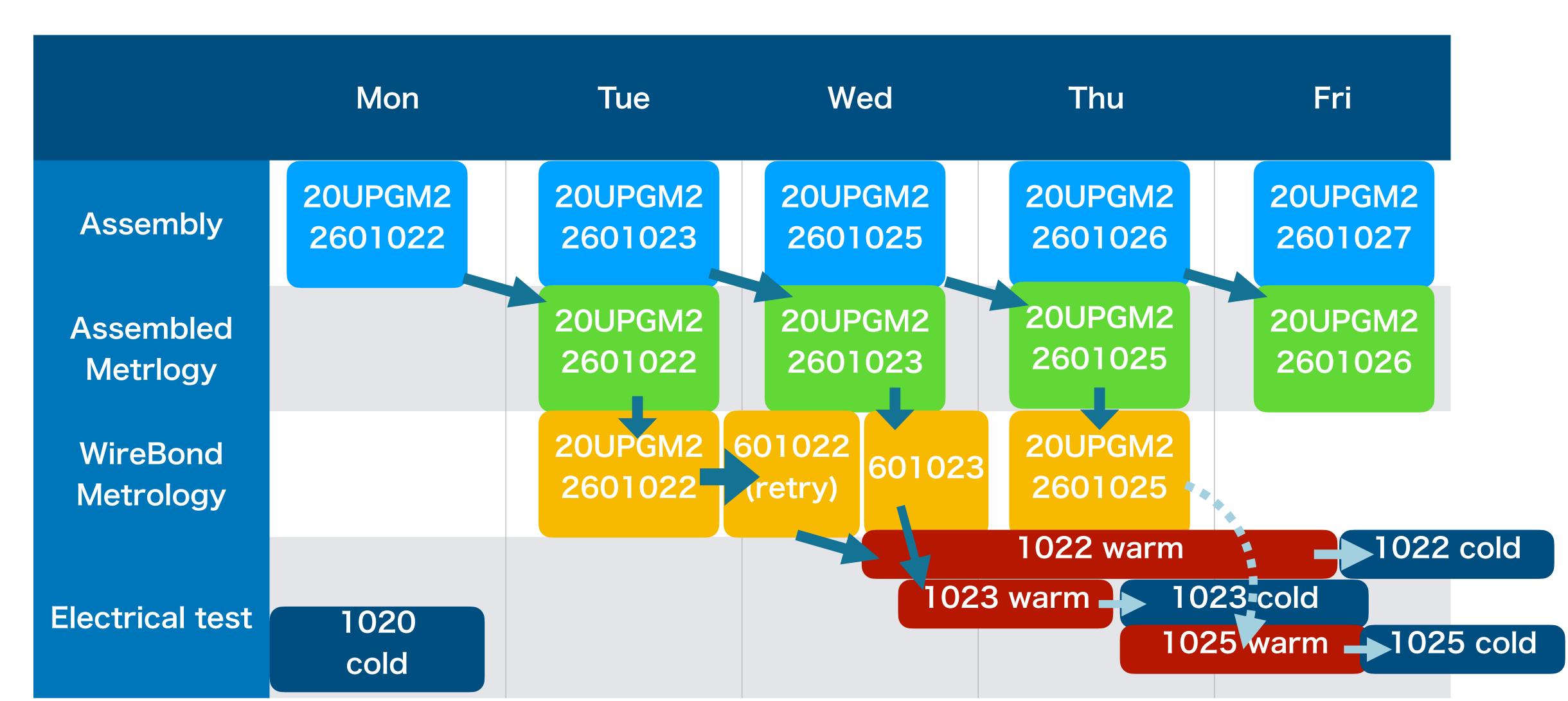

### 一週間のschedule

## QC passed module

- ・Assembly 5台done! 20UPGM22601022 chip ID miss(というか伝達miss) 20UPGM22601027 PCB rotate→Wirebondは次週以降

- Metrology

Assembled 4台done!

Wirebonded 3台done!

- Electrical test

- ・20UPGM22601022 Chip2のthreshold scanが回ら ない→Encorecolでnoisyな pixelの領域をmaskして解決

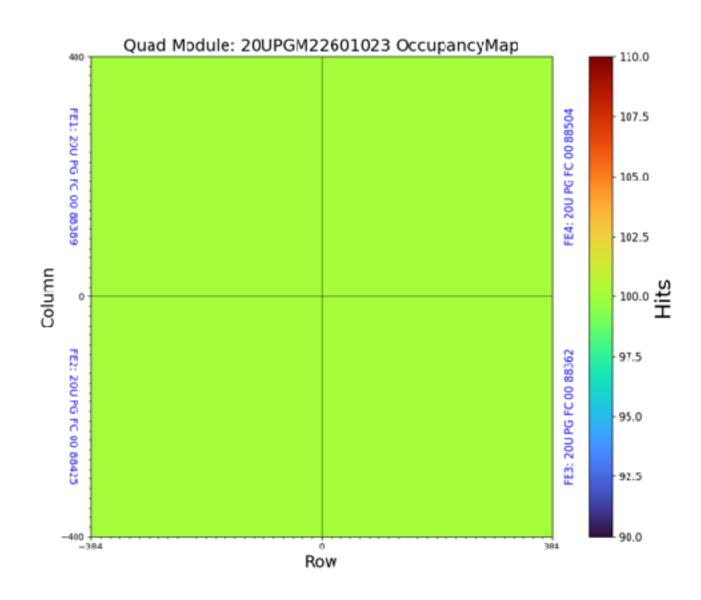

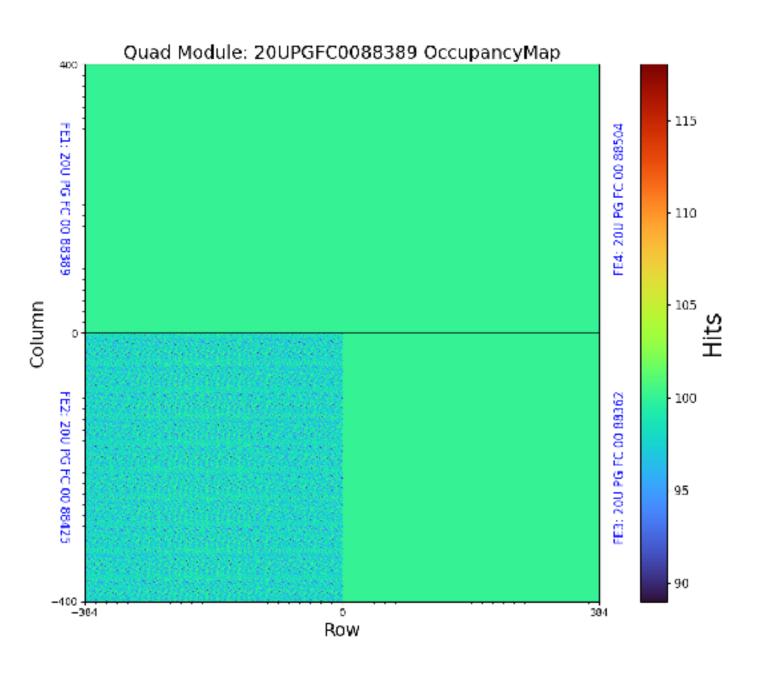

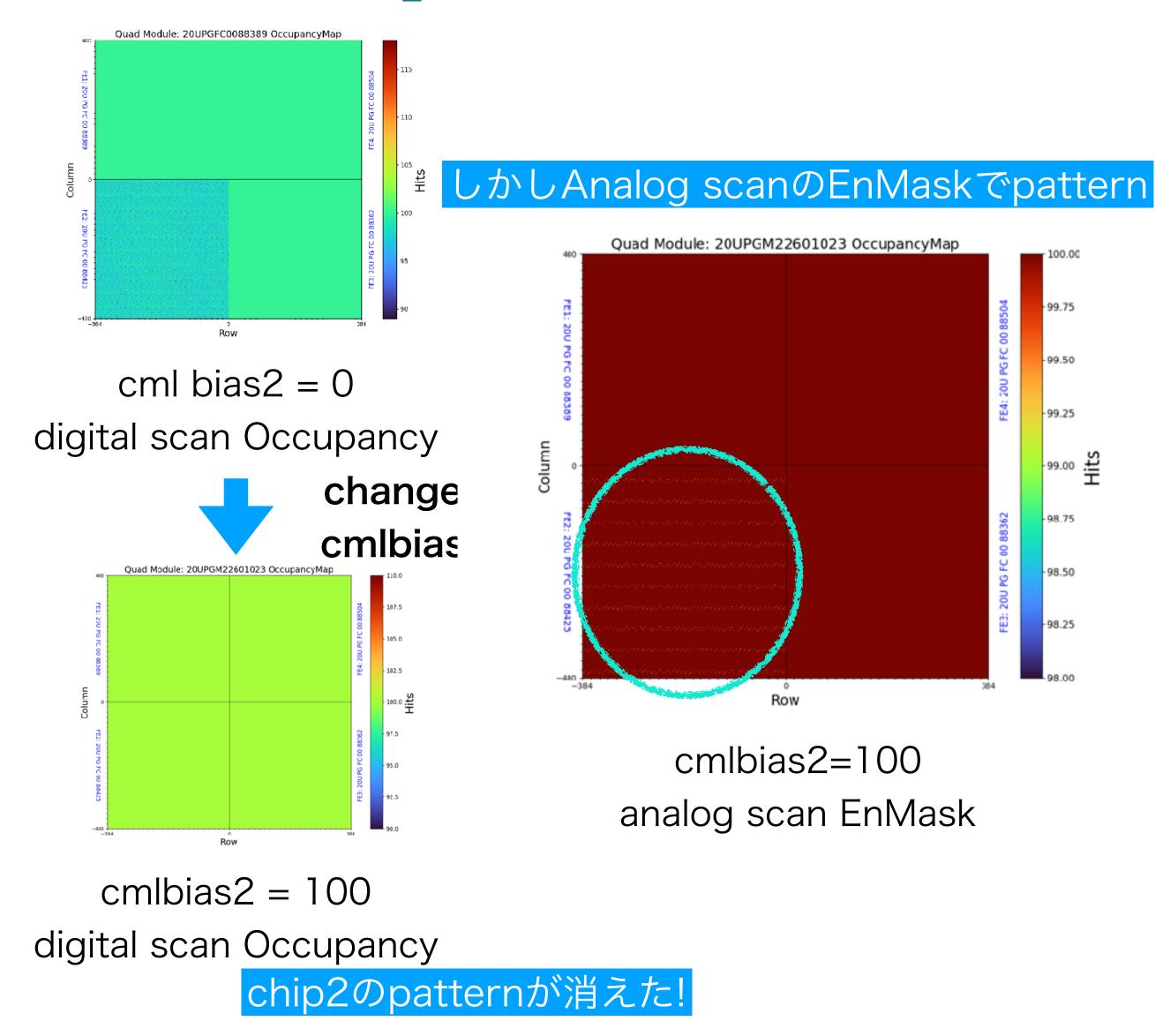

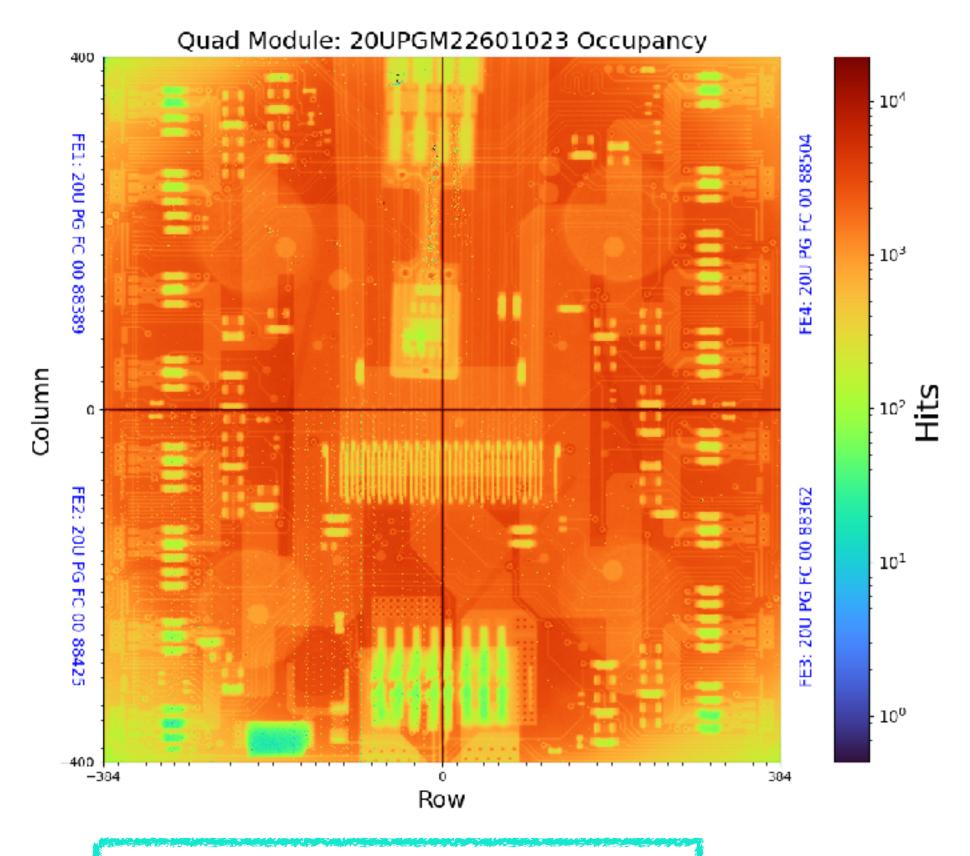

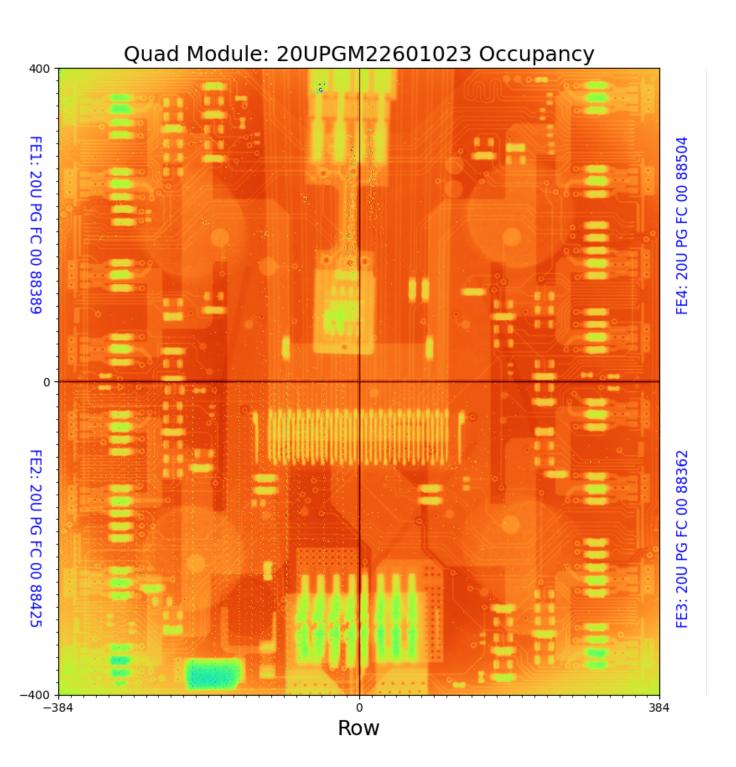

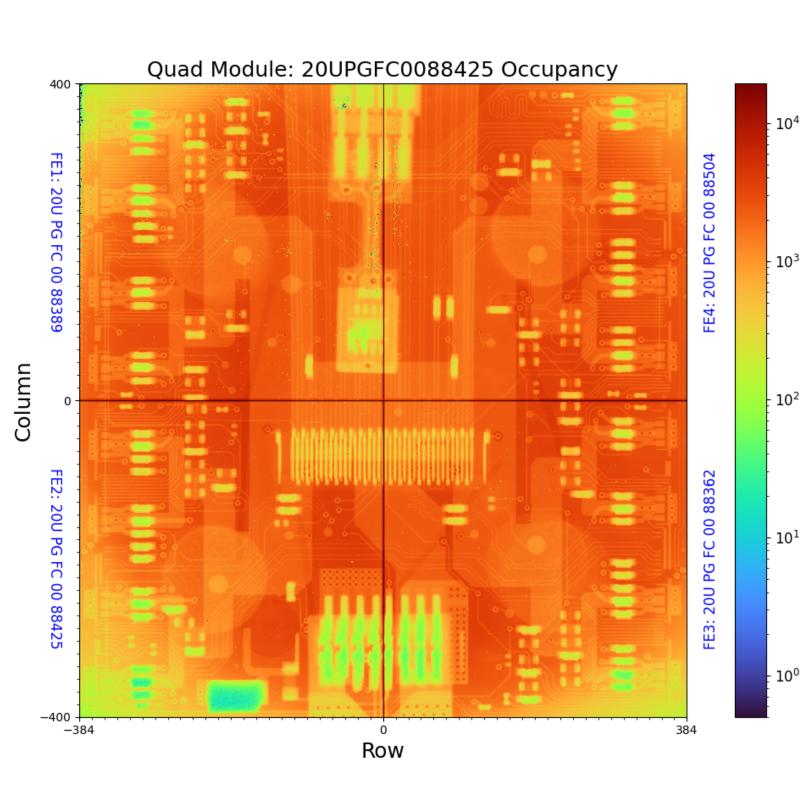

- 20UPGM22601023

cold chip2 digital scanで

pattarn

cold xray scan pattarn

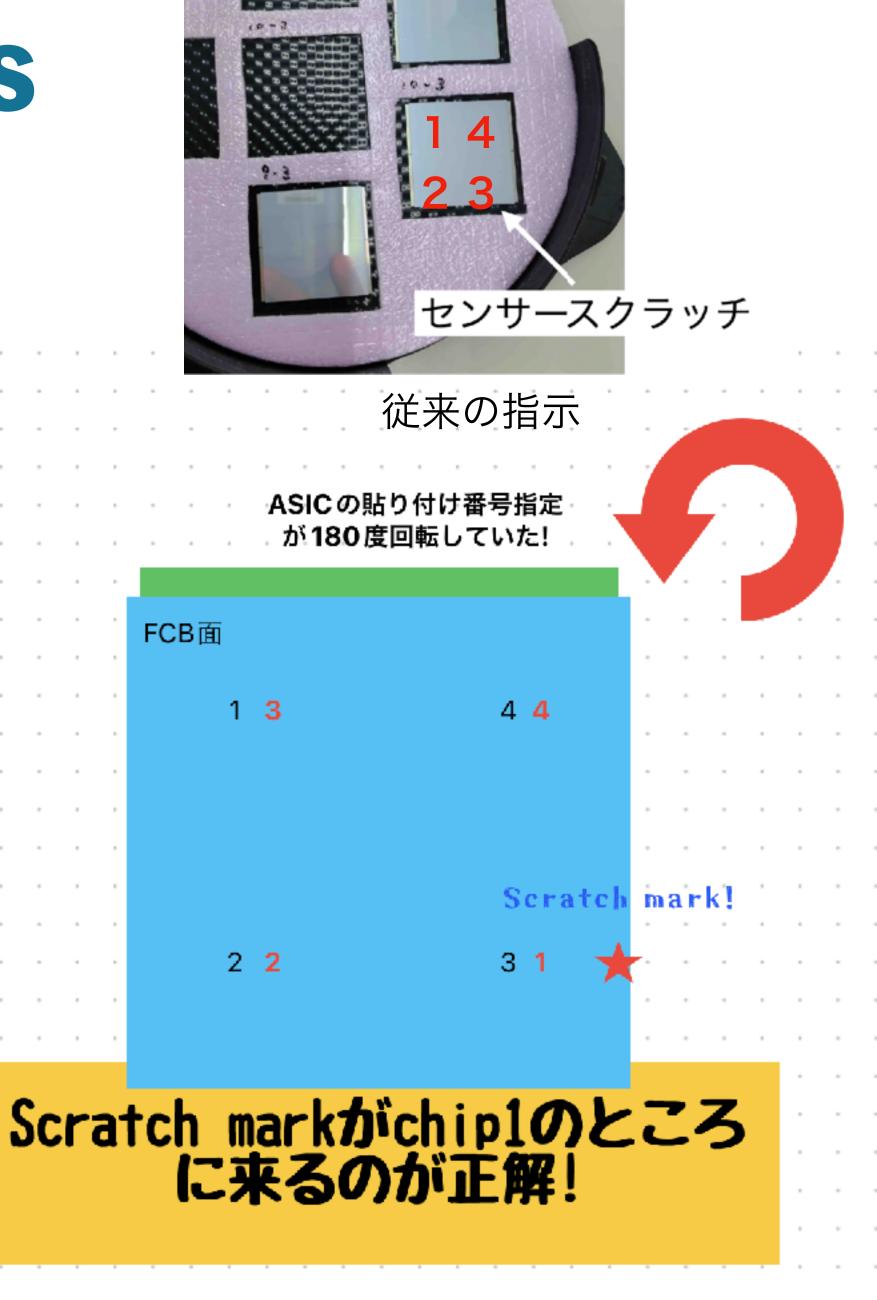

## Scratch mark position miss

- ・20UPGM22601022 にてe-fuse error →ITkProductionDataBaseのconfigが 間違っている!?

- 以前chip3の位置にあると考えていた scratch markはchip1の場所にあるとして configが定義されていた

- 今後はscratch markがchip1の場所に来るようにAssembly(20UPG2206025以降)

#### scratch mark miss

- chip IDの修正に伴い、Iref\_trimも 修正

- 全chipで修正されていることを確認 (Visual Inspection)

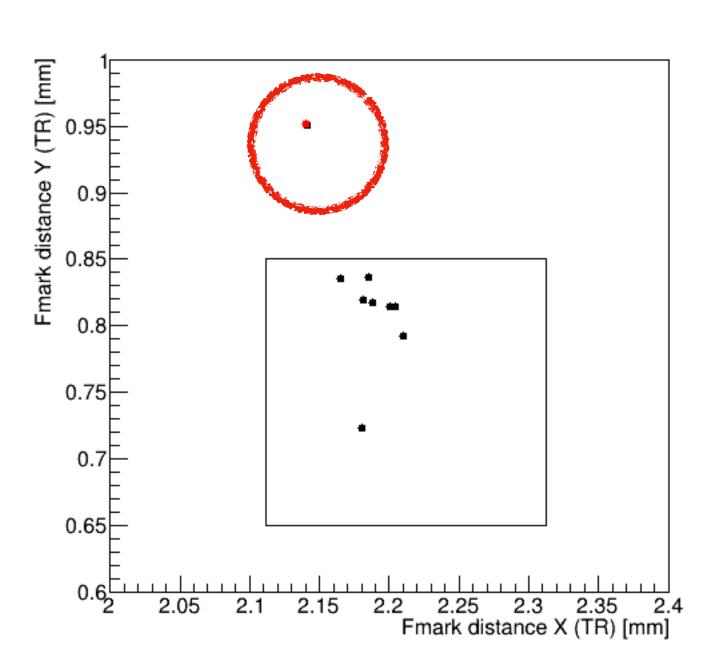

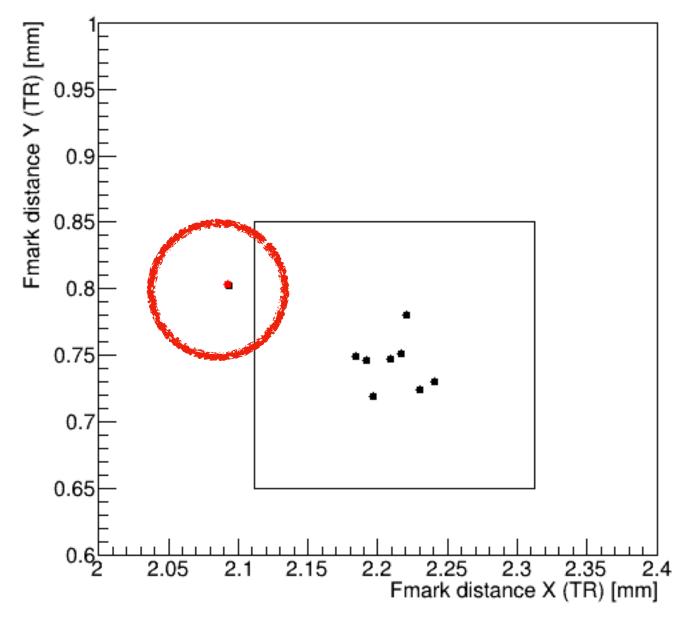

### PCB rotation

- ・木曜にAssembleした20UPGM22601026のPCBが回転していた!

- アセンブリの際のアライメントのずれによって発生したと考えられる。

- rotateしたmoduleのみ ASIC,PCB間

Fiducial markの距離が 要求を満たさず

- ・ stitched imageにgridをつけて 簡単にPCBの回転度合いを確かめられる ようにしたい→To do

#### 20UPGM2206022 threshold scan

- ・20UPGM2206023のchip2のthreshold scanが回らない

- ・Analog scanで正常にhitを返さないpixelをmask(by EncoreCol)→Threshold scanが回るように!

threshold scan Occupancy map

Analog scan Occupancy

Threshold scan Occupancy EnCoreCol Masked

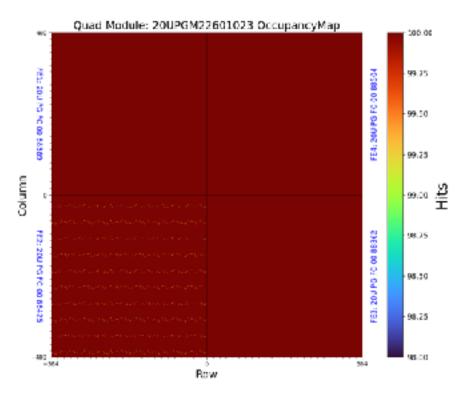

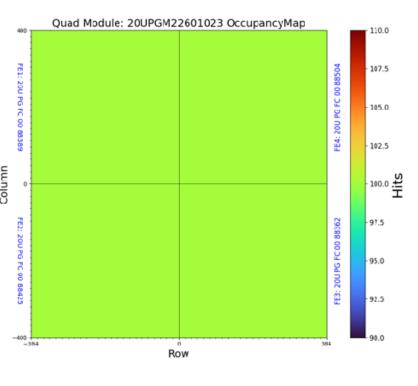

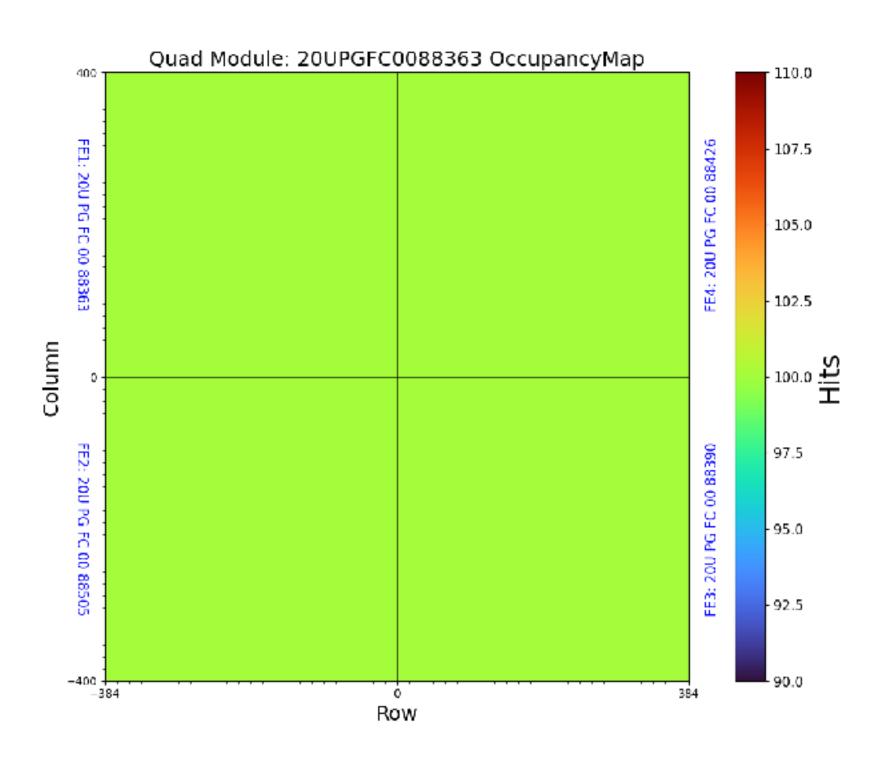

# 20UPGM2206023 Digital scan

- ・warm (20°C)で良好なchipがcold(-15°C)でchip2にパターンが見えるようになる

- ・0℃では2回scanを回すと良好に。再び-15℃に下げるとパターンが再現

- LVDS signalの強度の問題?cml biasを変えてみる

- 25のwarm digital scanでも同様のpattern

warm 20°C digital scan

0°C first scan

0°C second scan

cold(-15°C) digital scan

## scan pattern

- · 20UPGM2206023

- $temp = -15^{\circ}C$

xray scanでも

patternが見えるが

EnMaskとは一致せず

data line の問題?

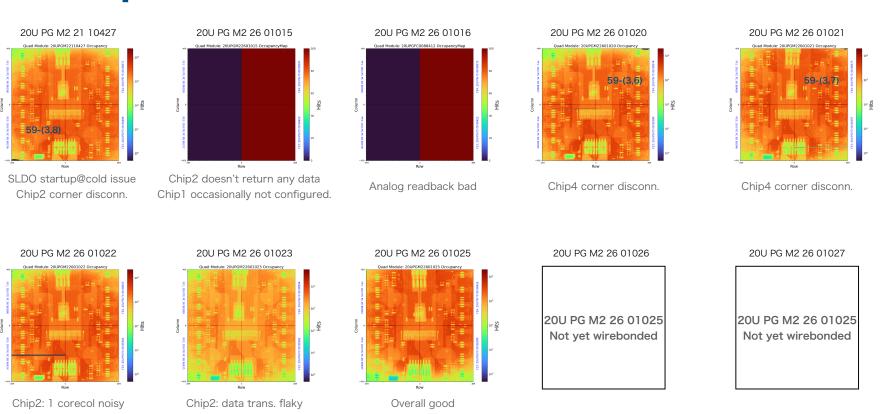

## disconnected bump?

- chiplのedge部分が剥がれのような挙動

- ・今回読み出しした3moduleで共通→製造過程に問題? しかしKEKでアセンブリしたmoduleにこのような傾向は見られない 他のmoduleでははっきりとした剥がれが確認(not chip1)

#### Pre-production: First 10 modules

2023/07/05 QAQC MT 生出さんのスライドより

・ repicでのアセンブリor readout systemの問題? or moduleの問題?

2023/07/07

**28**

### 問題点·改善点

- ・xray scanのアライメント cooling boxと支柱がネジで繋がっていてアクセスできない位置にあるので緩んだ時に修理できない

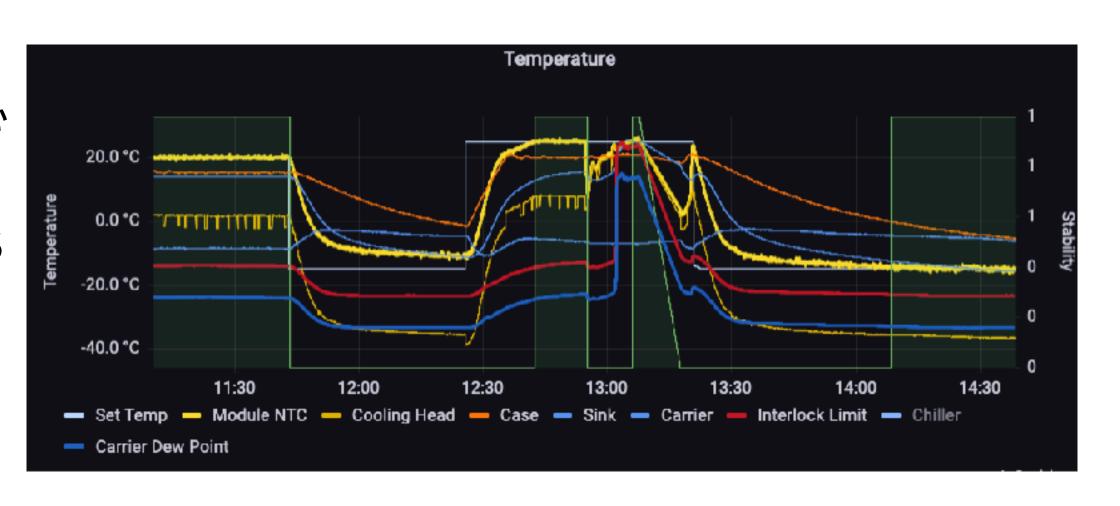

- ・温度が冷えにくい、module 吸着問題例:  $-15^{\circ}$ Cに冷やそうとした時に $-10^{\circ}$ Cまでしか冷えない(数回起こる)その度に $25^{\circ}$ Cまで上げてboxを開けてmoduleのalignmentをやり直さないといけない

- ・現在のcooling boxではmoduleを真空吸着しておらず空気を吸い込み露点が上昇boxと蓋のクッションによってcooling headに吸着させている(吸着が不十分)

- Metrology Machine GUI

- ・scan終了時に音で知らせる→done!

- ・missしたscanを選択して実行できるように

- ・Size scanのAF成功率の改善

- stitched imageにgridを重ねてPCBのrotateなどが一目でわかるように

# xray scan alignment

- x線照射装置とcooling boxのアライメントが不十分100%あたってない範囲がある

- cooling boxの支柱のネジの緩みが原因 設計上すぐにアクセスできない箇所にある

→改善するには治具を作り直す必要あり

支柱部分

## module吸着問題

- ・ moduleと冷却ヘッドは蓋のクッションで接触

- ・そのため-15°Cまで冷却できない時が多い →冷却できない時は一旦温度を25°Cまで上げ てmoduleを付け直す、30分以上のtime loss

- ・生出さん曰く真空吸着すると現在のcooling boxの露点が上がるらしい…

moduleの蓋

## まとめ

- 6/26-30 ハヤシレピック館山工場でITk Pix module量産作業を行なった

- systemがかなり自動化されていて非常にスムーズに作業できた

scan script,localDBが非常に便利!

- Scratch IDの位置ミス、20UPGM2206025以降修正

- ・20UPGM2206026にPCB rotate

- ・electrical test

20UPGM2206023,25のdigital scan patternはcmlbiasを変化させて解消

3moduleともchip1のedgeでbump剥がれのような応答

20UPGM2206023 cold xray scanでchip2にpattern→analog Enmaskのpatternとは一致せずdatalineの問題?

- xray alignment, 冷却に課題あり

## 参考リンク

• ITk Pix module QC document Japan

• ELOG

・ くらもちの個人的なlog(pass等は墨入れしてます)

# Back up

# 20UPGM2206025 digital scan

warm digital scan cml bias 1 = 400

warm digital scan cmlbias1 = 200

## xray scan

graphana