#### **MPG HLL Status**

- ▶ MPG HLL is working on the installation of a process line for

- → Post processing of up to 200 mm CMOS wafers

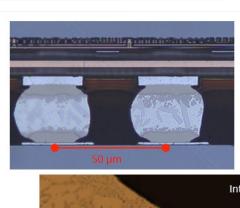

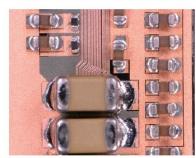

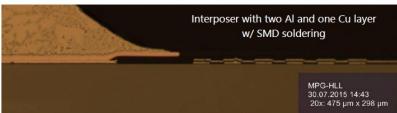

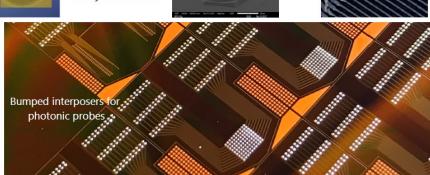

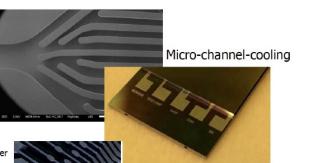

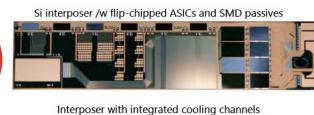

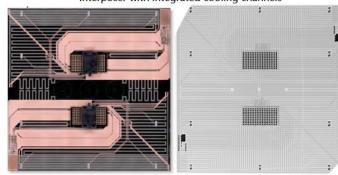

- → Fabrication of actively cooled interposers with micro-channels and TSVs

- → Hybrid bonding of post-processed CMOS wafers or single CMOS chips to sensors wafers

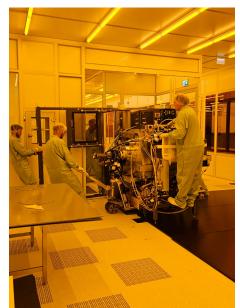

#### Current status

- → The clean room of MPG HLL was relocated to a new and larger building

- → Tests with equipment manufacturer finished, tool configuration done, purchasing in progress

- → Relocated equipment currently in the hook-up phase, qualification to follow

## Planned technology extension

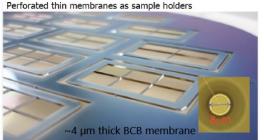

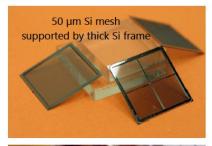

### Towards post-processing, micro-machining, vertical integration, and advanced heat management

- Deep reactive Ion etching for TSVs, micro-channels

- → **Ordered**, to be installed summer 2024

- Chemical mechanical polishing (prep for planarization and wafer bonding)

- → **Ordered**, to be installed autumn 2024

- > Low temperature direct wafer bonding line

- → Plasma activation, cleaning, bonding, metrology

- → Process defined, pre-tests accomplished, tendering in progress

- Hybrid bonding tool

- → W2W, C2W aligned bonding (bumpless fine pitch interconnect)

- → Process defined, tendering in progress

- → Lead time about 12 months

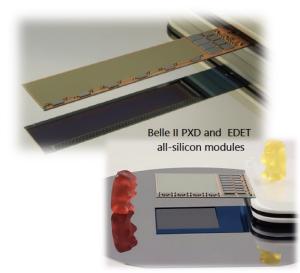

# A few few pictures from past projects – more to come!