# Cäribou: A Versatile Data Acquisition System for Silicon Pixel Detectors

M. Benoit (ORNL), E. Buschmann (BNL), Hucheng Chen (BNL), D. Dannheim (CERN), R. Palomo (Sevilla), Y. Otarid (CERN), M. Pijacki (Carleton), S. Spannagel (DESY), T. Vanat (DESY).

AIDAinnova 3rd Annual Meeting – 20.03.2024

# A particular solution to a particular need

Most silicon pixel detectors share the same power, control and readout concepts (different voltage levels, number of channels, protocols ...)

Every new detector drives the development of a new DAQ system or modification of an exisiting one (time consuming, not very innovative)

#### Why not a common versatile DAQ system?

(Common hardware, firmware and software cores, keeping the focus on detector integration)

#### Collaborating towards the open

Open source hardware, firmware and software for laboratory and beam tests

**DOI** 10.1088/1748-0221/12/01/P01008 **DOI** https://doi.org/10.22323/1.370.0100 **DOI** 10.1088/1748-0221/18/02/C02005

Maintained by a collective effort of hardware, firmware and software developers

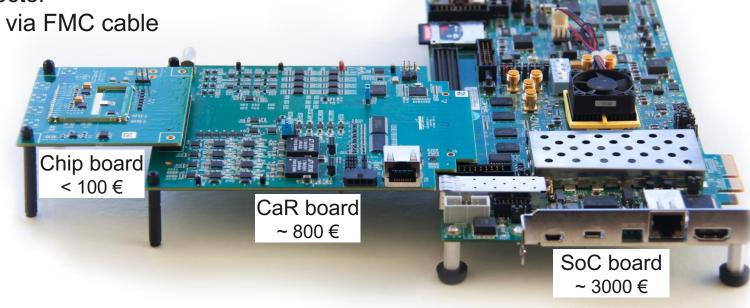

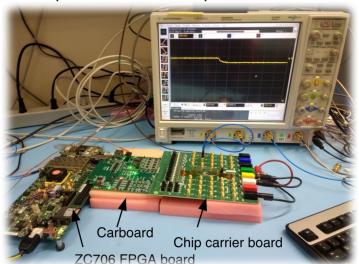

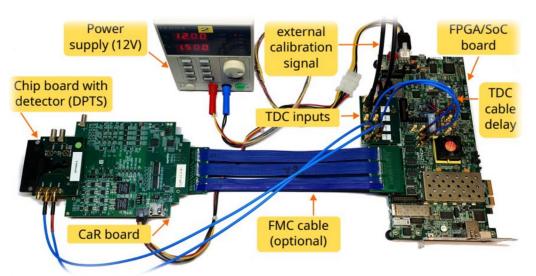

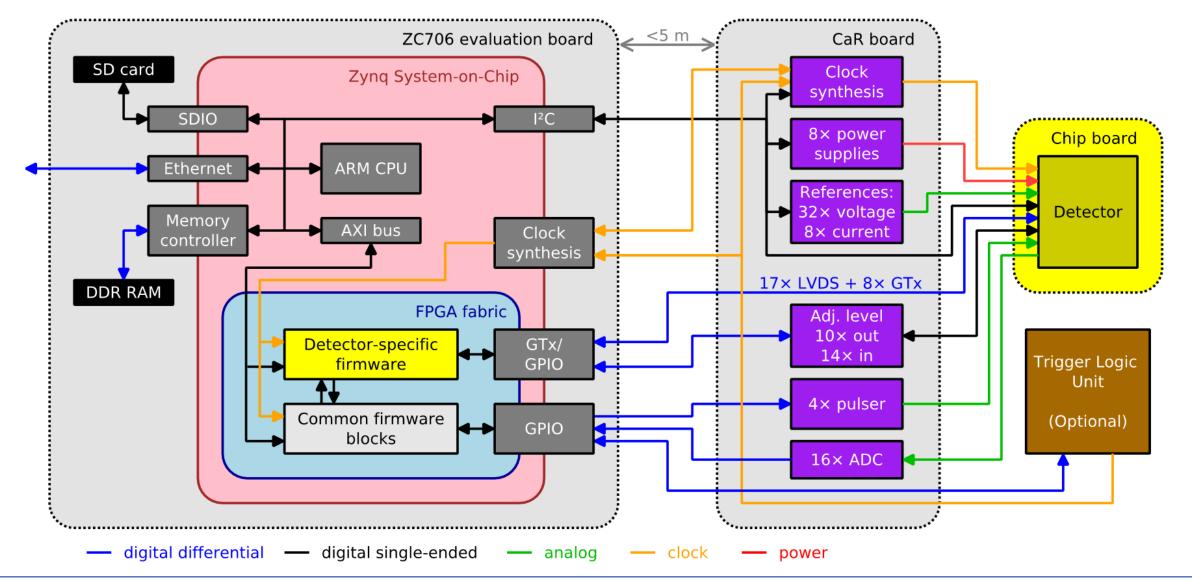

#### Caribou hardware architecture

- System-on-Chip (SoC) board

- ie: Xilinx ZC706 evaluation board

- Embedded CPU runs DAQ and control software

- FPGA runs custom firmware for detector control and readout

- Control and Readout (CaR) interface board

- Physical interface from SoC to detector

- CaR SoC connection extendable via FMC cable

- Detector (chip) carrier board

- Custom low-cost PCB

# System-on-Chip board

#### Xilinx ZC706 evaluation board

Zynq-7000 XC7Z045-2FFG900C SoC

#### **Processing System (PS)**

2 x ARM Cortex-A9 MPCore CPUs Yocto-based Linux Network/ssh control interface Caribou DAQ software (Peary)

**Programmable Logic (PL)**

Kintex-7 FPGA

AXI control interface

Caribou firmware

https://www.xilinx.com/products/boards-and-kits/ek-z7-zc706-g.html

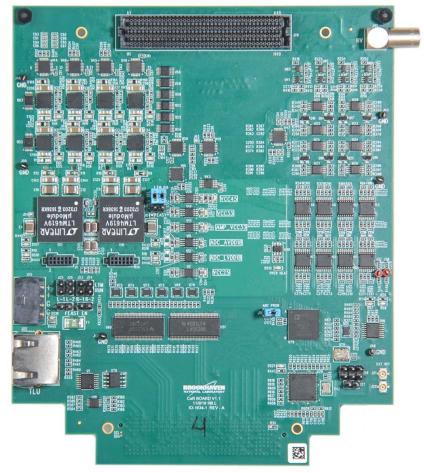

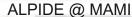

# Control and Readout (CaR) board

| Feature                           | Description                                  |

|-----------------------------------|----------------------------------------------|

| Adjustable Power Supplies         | 8 units, 0.8 – 3.6 V, 3 A                    |

| Adjustable Voltage References     | 32 units, 0 – 4 V                            |

| Adjustable Current References     | 8 units, 0 – 1 mA                            |

| Voltage Inputs to Slow ADC        | 8 channels, 50 kSPS, 12-bit, 0 – 4 V         |

| Analog Inputs to Fast ADC         | 16 channels, 65 MSPS, 14-bit, 0 – 1 V        |

| Programmable Injection Pulsers    | 4 units                                      |

| Full-Duplex High-Speed GTx Links  | 8 links, <12 Gbps                            |

| LVDS Links                        | 17 bidirectional links                       |

| Input/Output Links                | 10 output links, 14 input links, 0.8 – 3.6 V |

| Programmable Clock Generator      | Included                                     |

| External TLU Clock Reference      | Included                                     |

| External High-Voltage (HV) Input  | Included                                     |

| FEAST Module Compatibility        | Supported                                    |

| FMC Interface to FPGA             | Included                                     |

| SEARAY Interface to Detector Chip | 320-pin connector                            |

Resources for various target applications

**20 CaR boards v1.4** produced and distributed within RD50 common project

https://gitlab.cern.ch/Caribou/hardware/carboard

# **Detector carrier board (chip board)**

- **Detector-specific**

- Physical hardware hosting the detector

- Only provide passives and detector-specific components

H2M

RD50-MPW2

**ATLASpix**

RD50-MPW3

CLICpix2

**APTS**

CLICTD

**DPTS**

**FASTPIX**

dSiPM

H35Demo/FEI4

MLR1

RD50-MPW1

**CoRDIA**

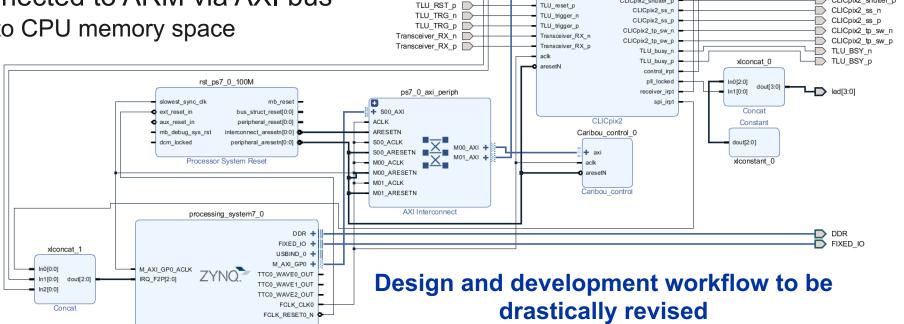

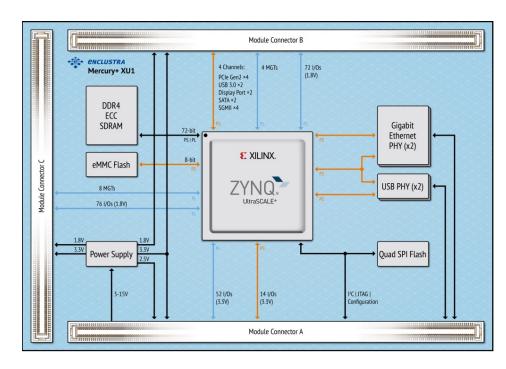

#### Caribou FPGA firmware

- Combination of custom and Xilinx IP cores

- Common logic

Development and integration of detector-specific blocks

ZYNQ7 Processing System

Detector control and readout

Firmware blocks connected to ARM via AXI bus

Registers mapped to CPU memory space

SI5345 CLK OUT8 📄

CLICpix2\_miso\_n

CLICpix2\_miso\_p

TLU RST n

Transceiver refClk

CLICpix2 0

C3PD\_reset\_p

CLICpix2\_mosi\_ CLICpix2\_mosi\_ CLICpix2\_pwr\_pulse\_

CLICpix2\_pwr\_pulse\_

CLICpix2\_reset

CLICpix2 shutter p

CLICpix2 reset r

CLICpix2 reset p

CLICpix2\_shutter\_r

CLICpix2 shutter p

#### Caribou software – OS – Linux

- Yocto-based Linux distribution

- OpenEmbedded build system

- Yocto reference embedded distribution: Poky

- Standard Linux packages (ssh, python, git, NTP, ...)

- Community-developed layer for Xilinx ZC706 (<u>meta-xilinx</u>)

- Custom layers with user-specific software and recipes (<u>meta-caribou</u>)

- OS boot from SD card

- Boot partition with bitstream and boot configuration (ie: MAC address)

- Linux partition with root filesystem

- Gitlab CI-based nightly build

- Preserved build cache (~50 GB) and single recipie rebuild

- DAQ software included

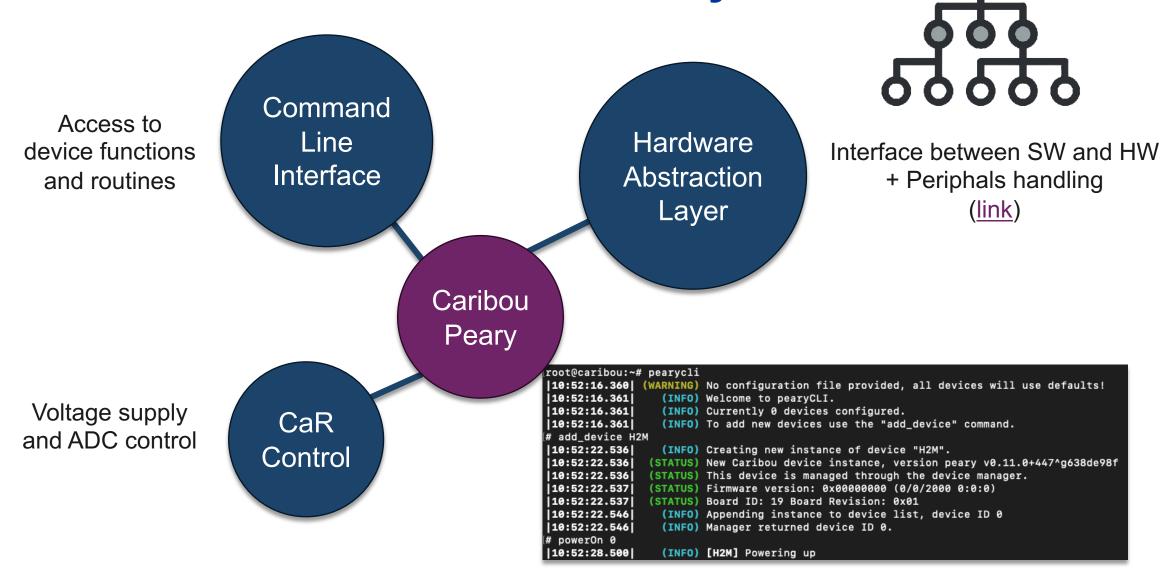

# Caribou software - DAQ - Peary

#### Some recent extensions

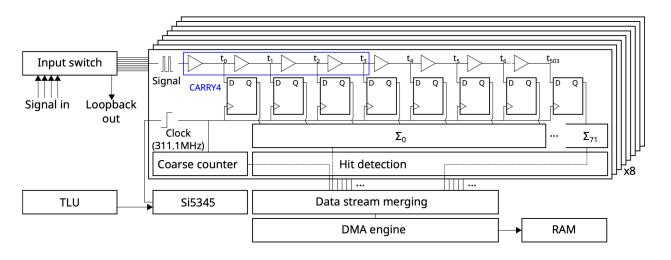

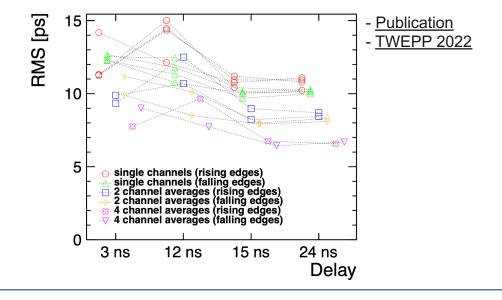

#### Focus on picosecond timing applications

- Motivation: support of waveform sampling and timing of digital pulses (FASTPIX, APTS, DPTS)

- Oscilloscope readout support in Peary software

- For both lab measurement and test-beams

- 8-channel TDC with picosecond resolution

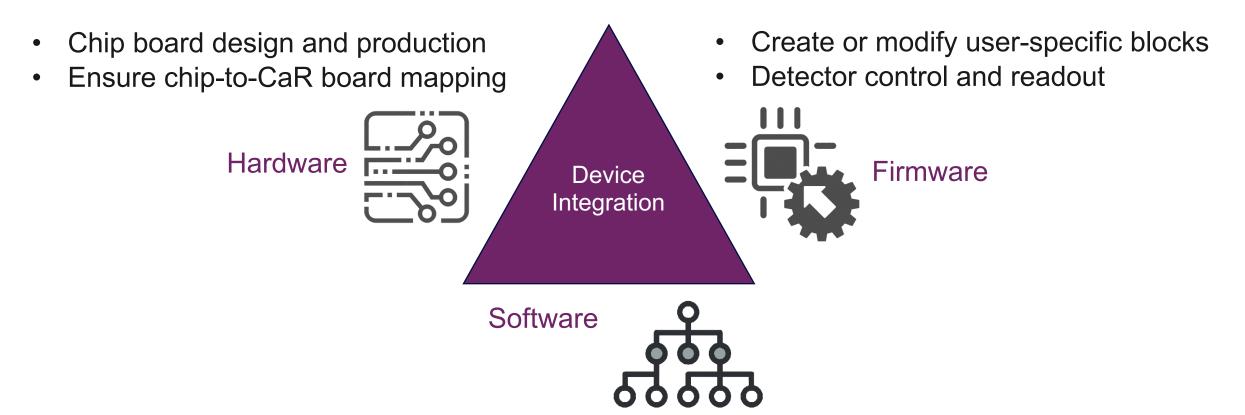

# **Device integration workflow**

- Define CaR board peripherals and firmware registers mapping

- Create detector-specific class with custom functions

# **Application examples**

- Support for various readout schemes

- Digital interface via GTx or LVDS

- Analogue waveforms (ADC or oscilloscope)

- Integration in beam telescope setups

- FEI4, Timepix3, Mimosa, ALPIDE

FASTpix with oscilloscope readout

DPTS with TDC in FPGA readout

Telescope integration

MIMOSA @ DESY

# Future plans – Caribou V1.5 respin

- Carboard v1.5 respin as an intermediate step

- List of obsolete components and subsitutes finalized

- Layout and BOM finalised by BNL

- Pre-production launched:

- 1. First few board assembled by end of February

- 2. Board testing at BNL

- 3. Launch of ~20 boards production

- (RD50 common project)

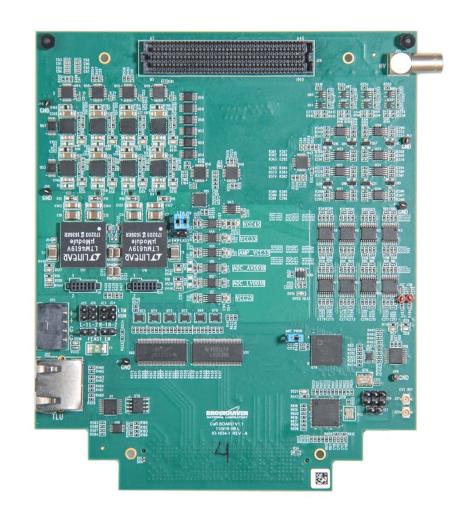

# Future plans – Caribou 2.0

- Based on commercial System-on-Module (SoM)

- Optimize system cost, increase flexibility and performance (GbEth, SFP+, configurable bias polarity, mutli-device support ...)

- Mercury+ XU1 System-on-Chip

- ZYNQ Ultrascale+ MPSoC

- More resources and processing power

- Merging Zynq and CaR boards into a compact and modular CaR board

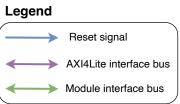

#### Firmware revision - Boreal

#### Top Module

#### **Boreal firmware (link):**

Unified, modular and configurable architecture

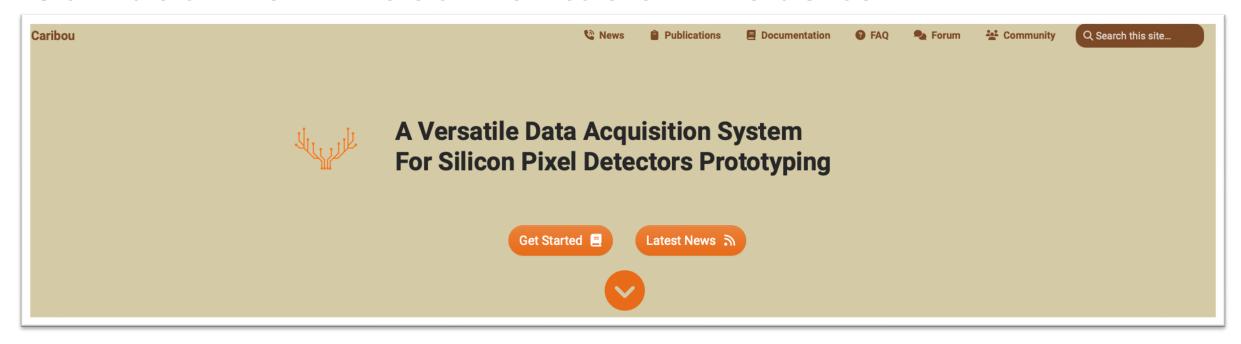

#### CI/CD:

linting, simulation, building, deployment

#### Caribou 2.0 – Documentation website

#### Project website (<u>link</u>)

- Documentation

- Mattermost channel

- Publications

- Forum

- ...

#### Automatic documentation builds and website deployments

# **Summary**

- Open source, Linux-based, standalone

- Proving excellent operation on many detector prototypes

- Ongoing upgrade phase with many improvements to come

20 March 2024

# Thank you

# CERN

home.cern

#### Contact

CERN

Younes Otarid

EP R&D

younes.otarid@cern.ch

# Caribou system architecture

#### Caribou 2.0 – CaR board prototyping

- CaR board 2.0 schematics/layout still under development

- Enclustra Mercury+ XU1 SoC module and Mercury+ ST1 base board for protoyping

- Core development plan:

- Finalise CaR board design

- Firmware structure revision

- Migrate Yocto build and Peary software to the Zynq UltraScale+ SoC