AGH UNIVERSITY OF SCIENCE AND TECHNOLOGY

### Update from AGH activities in WP11.3 – CMOS 28 nm

**Marek Idzik for AGH-UST**

AIDAinnova 3rd Annual meeting, 18-21 March 2024, Catania, Italy

# Design of fast ultra-low power 10-bit SAR ADC in CMOS 28nm

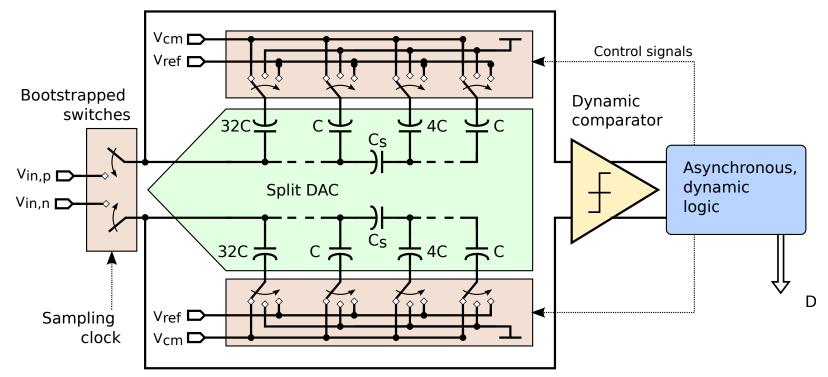

- SAR architecture already verified in CMOS 130/65 nm

- Fully differential, MCS switching, dynamic comparator, asynchronous logic

• The goal  $\rightarrow$  the ultra-low power and the highest sampling rate

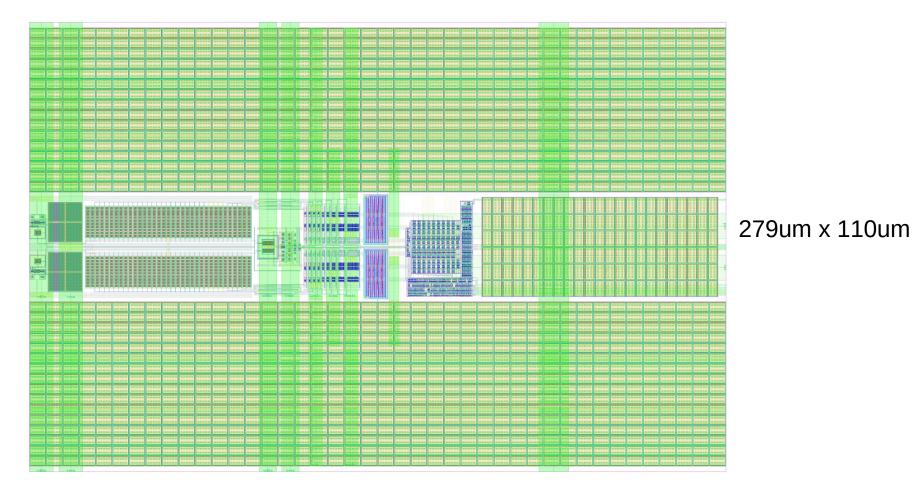

### Fast ultra-low power 10-bit SAR ADC in 28nm Status of ADC integration

• Layout ready, extracted, post-layout simulations done

## Simulation results of 10-bit SAR ADC Comparison to ADC prototypes in 130/65 nm

| CMOS<br>[nm] | Verification           | Power<br>@40MHz<br>[uW] | Max<br>fsample<br>[MHz] |                                            |

|--------------|------------------------|-------------------------|-------------------------|--------------------------------------------|

| 130          | Prototype<br>ASIC      | 680                     | 50                      | M. Firlej et al.<br>JINST 18 P11013 (2023) |

| 65           | Prototype<br>ASIC      | 440                     | 50-60                   | M. Firlej et al.<br>JINST 19 P01029 (2024) |

| 65           | Prototype<br>ASIC      | ~550                    | 80-90                   | M. Firlej et al.<br>JINST 19 P01029 (2024) |

| 28           | Post-layout simulation | <150 ?                  | ~180 ?                  |                                            |

- Post-layout simulations show a great improvement in power consumption and sampling frequency, compared to 130/65 nm

- How realistic the post-layout simulations are ?

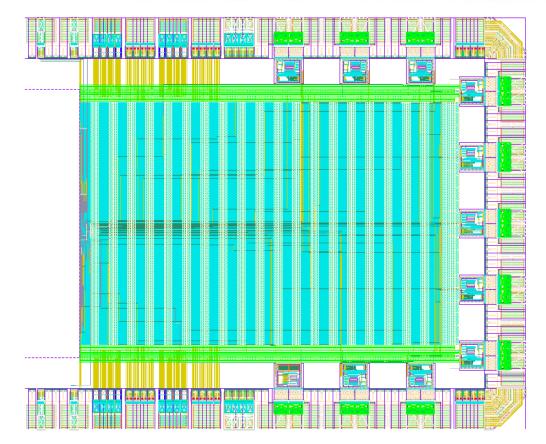

#### Fast ultra-low power 10-bit SAR ADC in 28nm Status of digital part

- Supply delivered also to ADC digital circuitry via digital grid

- Data outputs in SLVS standard

- Digital part is pad-limited

- No show stoppers, but few issues to solve

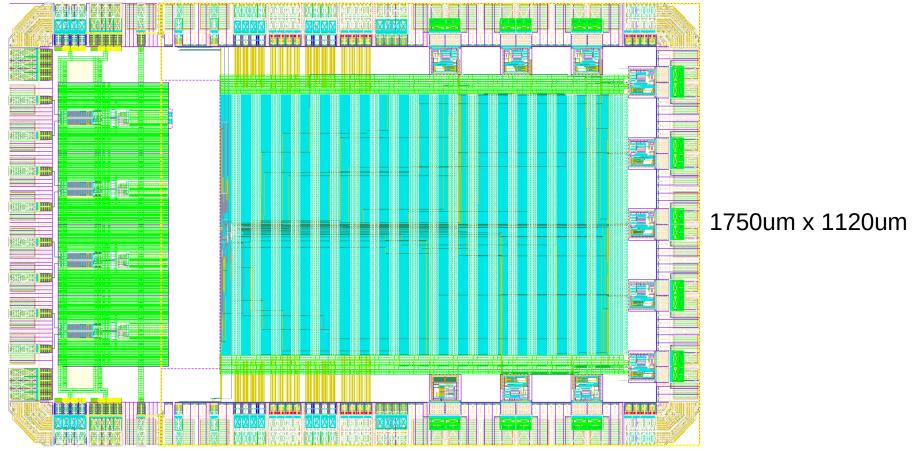

#### Fast ultra-low power 10-bit SAR ADC in 28nm Status of chip integration

- Integration of 4-channel ADC ASIC in progress

- Should be ready for submission in 1-2 months