# A 20-b accelerometer-based front-end for instrumentation

Enrico Sentieri – STMicroelectronics Andrea Baschirotto – Univ. Milan-Bicocca

> Microelectronics Users eXchange MUX-2011 CERN, June, 9<sup>th</sup>, 2011

# Introduction

#### Introduction

- Design Objectives

- Noise Budget Partitioning

- Architecture

- ADC Architecture

#### **Sensor Accelerometers (1)**

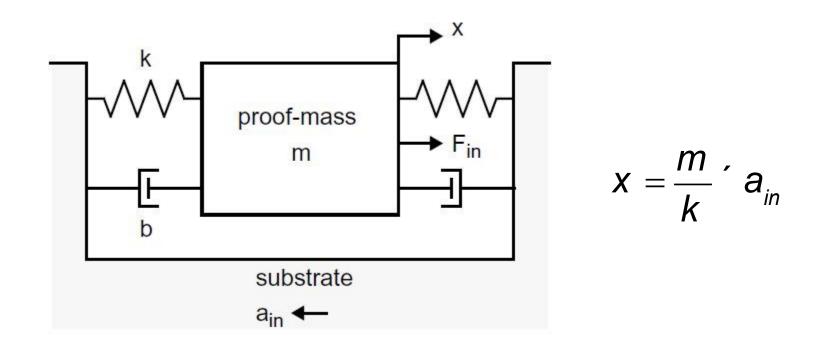

Displacement accelerometers measure the displacement (x) of a suspended proof mass (m) in response to an input acceleration (a)

#### **Sensor Accelerometers (2)**

- **Displacement capacitive** sensors are widely used in several systems

- Accelerometers

- Pressure sensors

- Microphone

- etc...

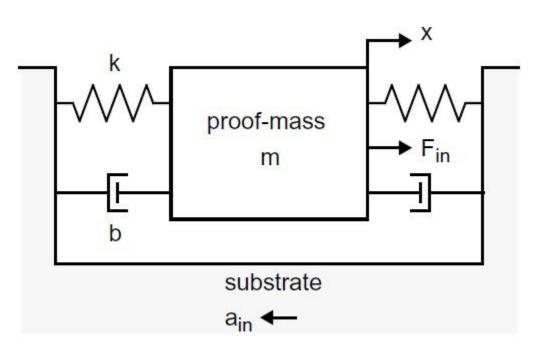

### **Sensor Accelerometer (3)**

- Most popular technique to measure the proof mass displacement

- → Capacitive Position Sensing

- Different Sensor-Capacitive-Bridge topologies

- Example:

- Two nominally equal-sized capacitor are formed between the electrically conductive proof mass and stationary electrodes

- When the substrate undergoes acceleration

- → the proof mass displaces from the nominal position

- → capacitive half-bridge unbalacement

# **Sensor Accelerometer Interface (1)**

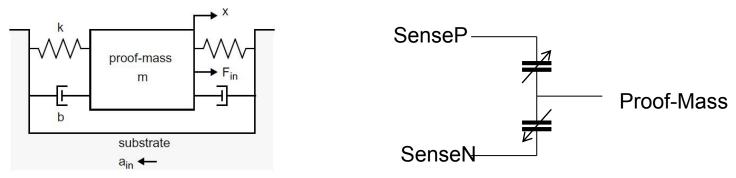

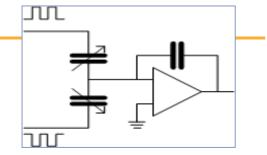

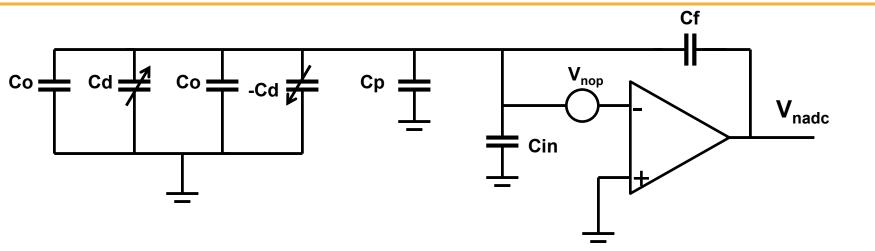

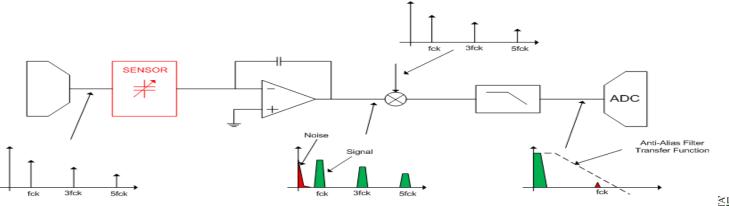

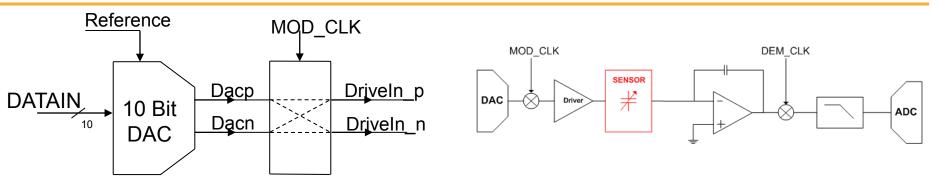

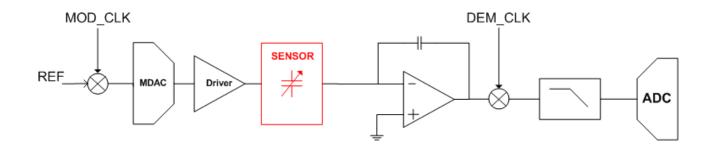

- Capacitors sense AC signals

- → AC modulation sources for capacitive sensing

- The sensed signal is an Amplitude Modul. Signal

- The acceleration signal modulates a HF carrier

- To extract the envelopment

- → The sensed signal need to be demodulated or sampled

- Accelerometer sensitivity  $\approx$  modulation carrier amplitude

## **Sensor Accelerometer Interface (2)**

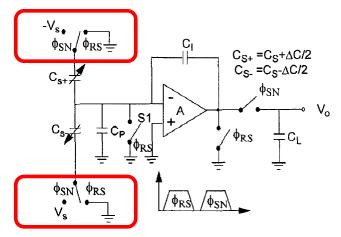

SC Architectures are very popular

- MOS switches to connect the sensor and the circuit input.

- The thermal noise of MOS switches (kT/C noise)

- SC circuits are sample data systems

- It is not possible to insert an Anti-Alias filter between reading circuit and sensor

- the input wide band noise is folded in base band

- SC have much higher noise

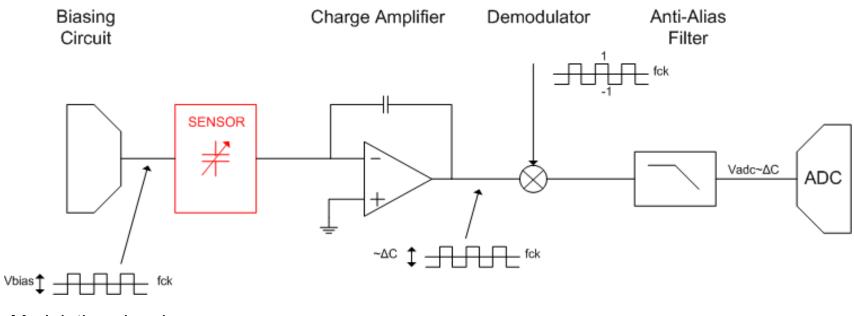

#### **Modulation/Demodulation**

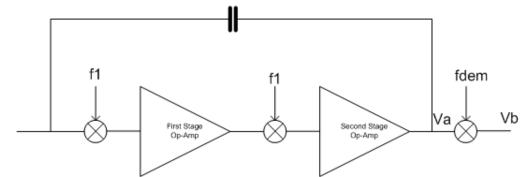

#### **Time Domain Signal Processing**

Modulating signal

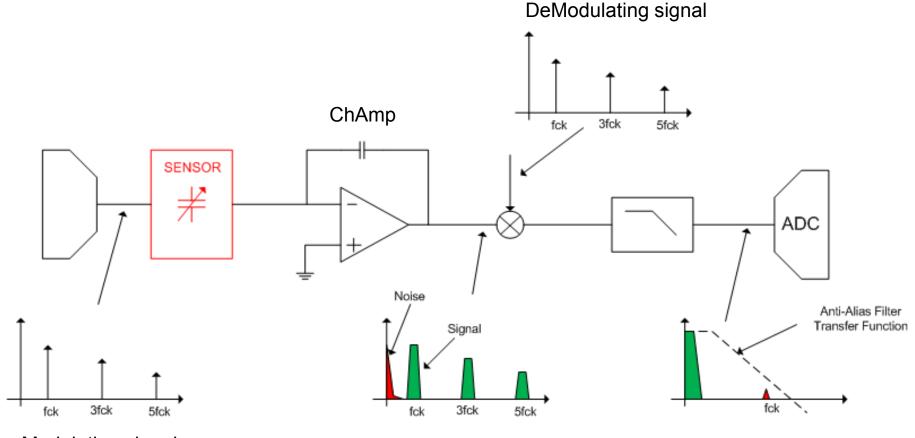

#### **Modulation/Demodulation**

Frequency Domain Signal Processing

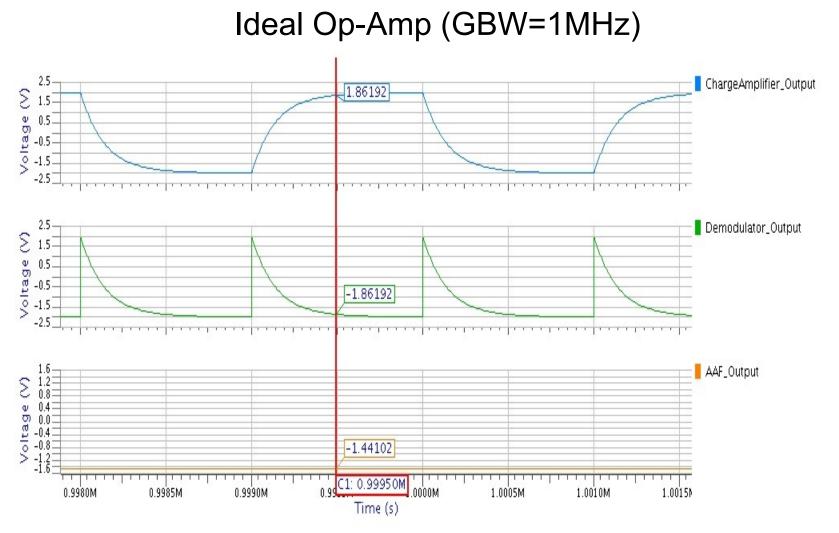

#### Gain Error due to Op-Amp band limited (1)

Modulation

The acceleration is transposed to the odd harmonics frequencies of the Modulation signal

$$X_{2'k+1} = \frac{4'V_0}{\pi}' \frac{1}{2'k+1}$$

- The ChAmp transfer-function shapes the modulated signal frequency spectrum

- High-frequency component attenuation

- The Demodulated signal amplitude is affected by ChAmp Bandwidth

- → Gain Error

- Gain error depends on process and temperature variations

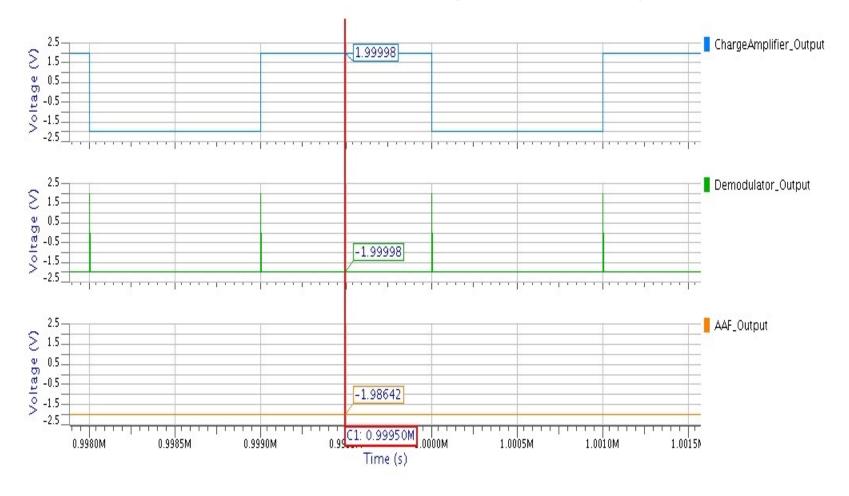

#### Gain Error due to opamp limited band (2)

#### Ideal Op-Amp (GBW=1GHz)

#### Gain Error due to opamp limited band (3)

#### **Mod/Dem-Freq vs. Power Consumption**

- Higher Mod/Dem-Freq

- In CMOS circuit, the electronics low frequency *flicker-noise* which often extends to low MHz

- Barger opamp Gain-Bandwidth

- Higher Power Consumption

- Trade-off between performances and power consumption

- Typically the Mod/Dem-Freq (f<sub>m</sub>) is from some tens of kHz to MHz

- $\rightarrow f_{\rm m} = 100 \rm kHz$

# **Design Objectives**

- Introduction

- Design Objectives

- Noise Budget Partitioning

- Architecture

- ADC Architecture

## **Design Objectives (1)**

- Design a digitizing accelerometer interface that uses the full bandwidth and dynamic range of the sensor

- ➡ The Sensor Signal Full-Scale is ±2G

- $\rightarrow$  The total equivalent acceleration noise < 2.5µG

- sensor + electronic

SNR = 20 '

$$\log_{10}(\frac{2G}{\sqrt{2}} + \frac{1}{2.5\mu G}) = 115 dB$$

# **Design Objectives (2)**

- Low power consumption

- Architecture choice

- Open-Loop Capacitive sensor Interface

- Interface Topology

- Charge Sensitive Amplifier with modulated input and synchronously demodulated output

- The capacitive bridge is driven (modulated) by a squared wave voltage

- Gain error (due to Sensor and Integrated Circuit process variation) has to be compensated

- Bias Voltage Amplitude → 10b resolution programmable

MUX-2011

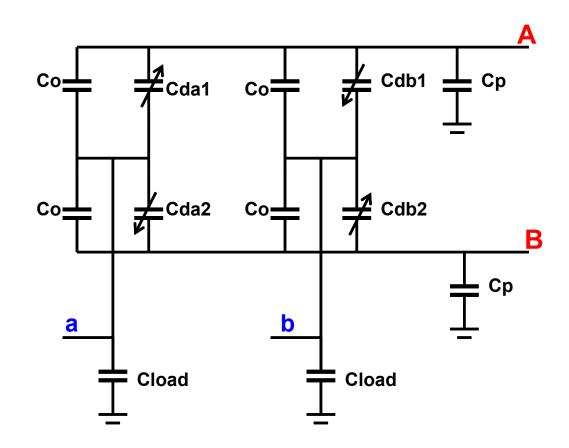

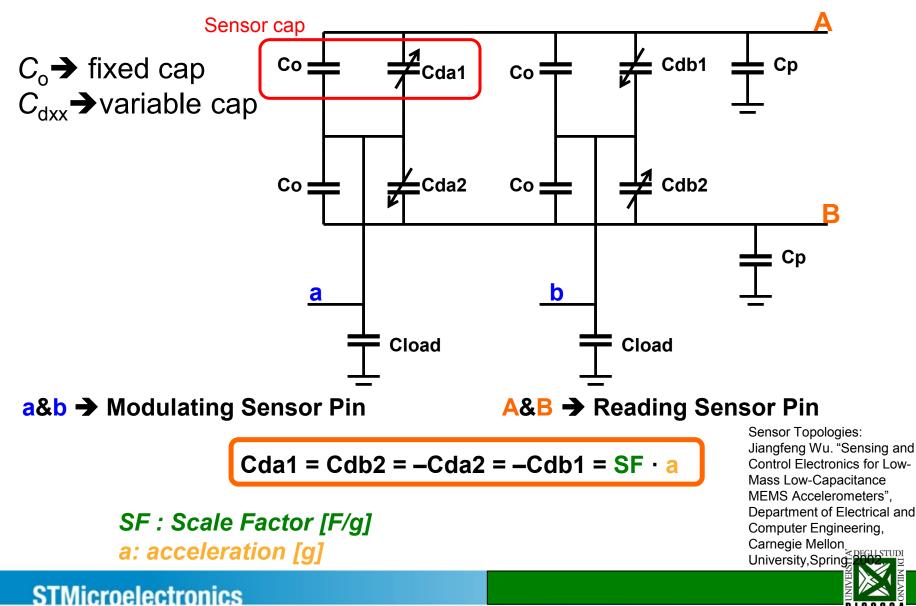

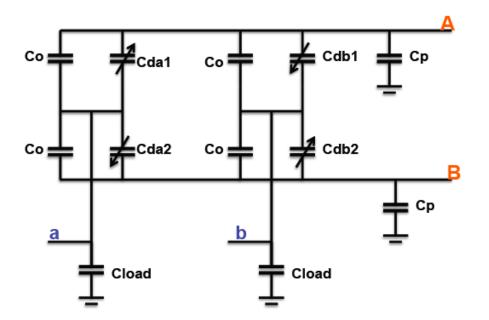

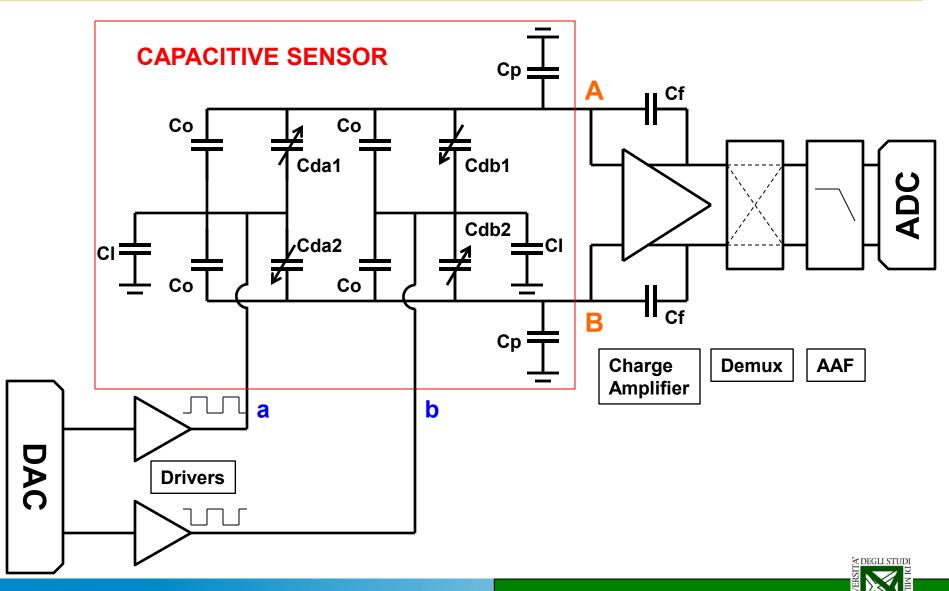

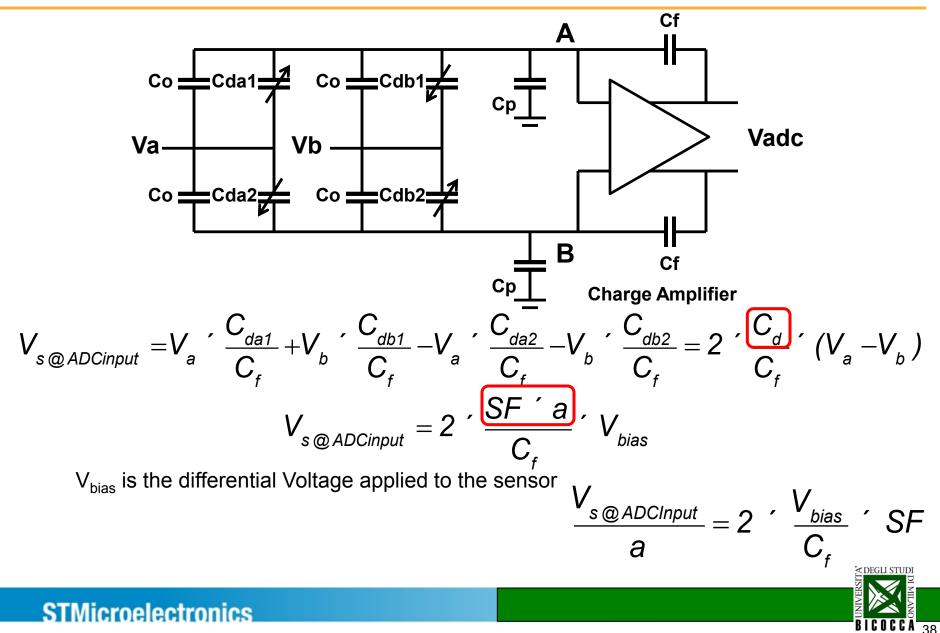

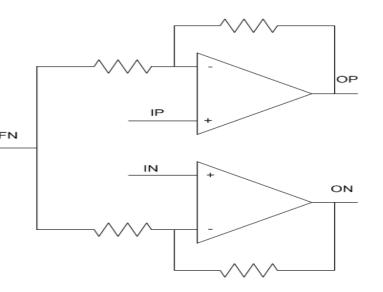

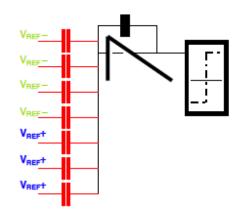

### **Capacitive Sensor**

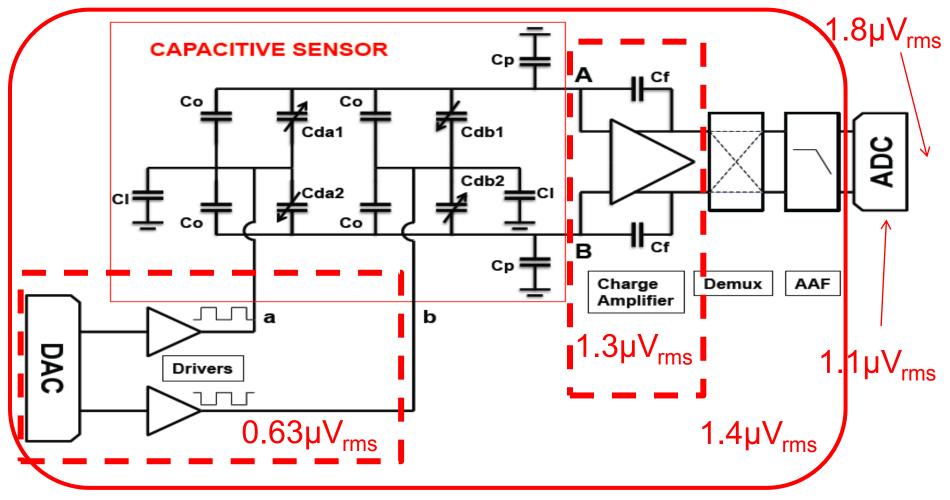

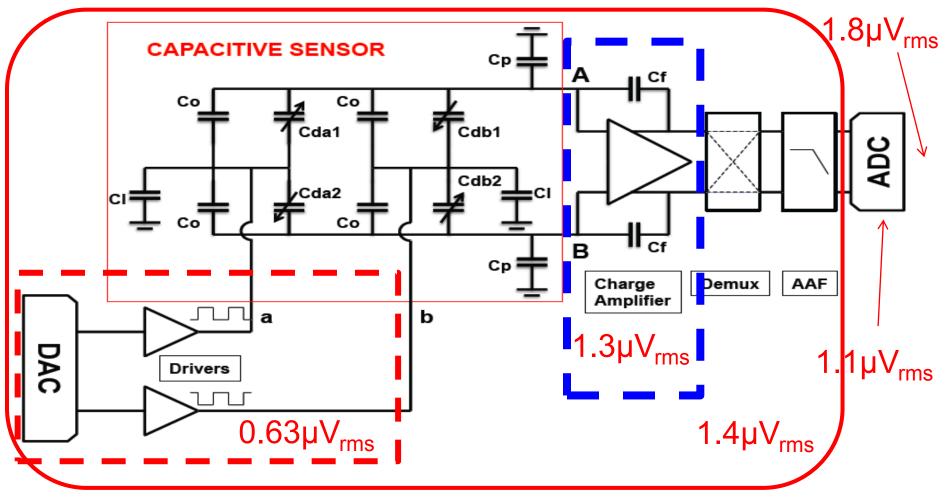

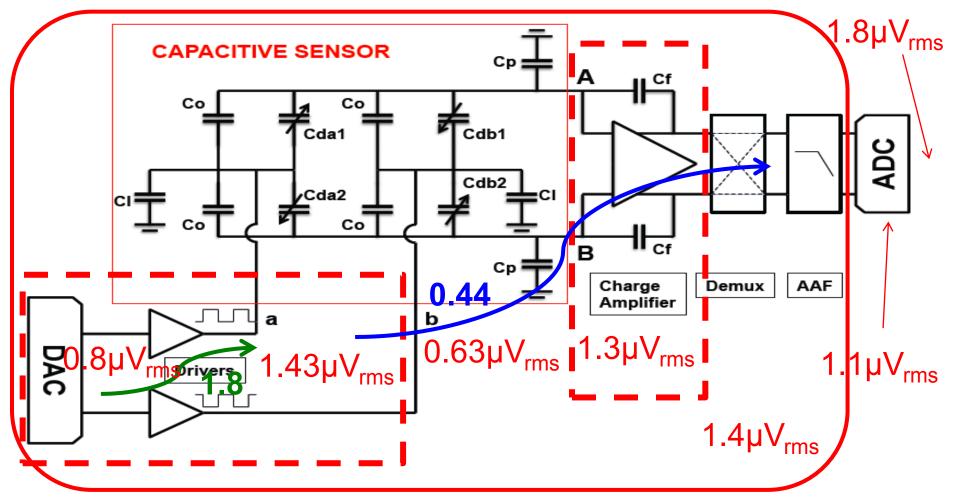

- The Capacitive sensor

- → fully-differential

- The bridge is driven by a differential signal a & b

- With an acceleration

the capacitive

bridge is unbalanced

a differential

charge is injected in

the pins A & B

Differential charge ≈ acceleration

#### **Capacitive Sensor Equivalent electrical Model**

**UUA** 18

## **Capacitive Sensor Parameters**

- Sensor Input and Interconnection Capacitance

- $\rightarrow$  C<sub>p</sub>=12pF

- C<sub>load</sub>=20pF

- Sensor cap

- C<sub>o</sub>=1pF

- Scale Factor

- SF = 300fF/G

- Sensor Dynamic Range

- → ±2G → S=2G

- Sensor Noise Density

- → a<sub>sn</sub>=100nG/sqrt(Hz)

- Sensor Bandwidth

- → BW=300Hz

BICOCCA 20

#### **Ideal Sensor Accelerometer Interface**

# **Technology Choice(1)**

- The technology choice driven by:

- Performance

- Cost

- Process Maturity

- Analog Option Required

## **Technology Choice (2)**

- Standard CMOS technology with double thick oxide

- A rough system analysis

- → more than 90% device area is used for analog blocks

- ► → No need to use technology with high level of integration density

- → The technology choice is driven by analog requirement

- A Mature technology with two different thick oxide MOS has been selected:

- 70Å (3.3V gate, 0.350µm minimum channel length)

- 120Å (5.0V gate, 0.500µm minimum channel length)

- The 5.0V MOS slower and noisier than 3.3V MOS

- Two power supply domains (5.0V & 3.3V) are available

# **Technology Choice (3)**

- Resistors

- Linear Resistor (Doped-Poly resistor)

- Diffused Resistor

- poor linearity

- no flicker noise compared to the poly resistor

- HIPO (High resistance poly) resistor

- higher sheet resistance compared to poly resistor.

- extra mask → higher cost

- Capacitor

- High-linearity caps required for the Charge Amplifier feedback capacitor and ADC (Switched Capacitor) → Metal to metal capacitor is the best choice

- MIM (Metal Insulator Metal)

- Thin oxide → High density level

- Extra Masks → Higher Cost

- Fringed Capacitor

- Lower density

- No extra mask

# **Noise Budget Partitioning**

- Introduction

- Design Objectives

- Noise Budget Partitioning

- Architecture

- ADC Architecture

# **Noise Budget Partitioning (1)**

- Starting from high level specifications

- define the specification for each blocks of the system

- → identify critical blocks

- roughly definition of a suitable architecture of each block

- Simplifications

- This preliminary analysis should be done not considering mod/dem effects

# **Noise Budget Partitioning (2)**

- The **Noise Budget partitioning** is an iterative design process

- Some design specifications are defined based on preliminary analysis/assumptions

- the required performances for each block are evaluated

in case of any issue, the assumptions will be modified

- It's quite impossible, at the first run, to identify all the critical design parameter

# **Noise Budget Partitioning (3)**

- Target: Total noise  $\rightarrow a_{n_rms}$ = 2.5µG

- Two different main Noise contributors:

- Sensor Noise (Brownian Noise) → a<sub>sn rms</sub>

- Electronic Noise  $\rightarrow a_{en_rms}$

- Quantization Noise, Thermal Noise, & Flicker Noise

• Sensor Noise

$$(a_{sn\_rms})$$

:

$a_{sn\_rms} = a_{sn} \land \sqrt{BW} = 100 nG / \sqrt{Hz} \land \sqrt{300 Hz} = 1.73 \mu G$

Electronic Noise → Equivalent Acceleration noise is evaluated to match the design Objectives:

$$a_{en_{rms}} = \sqrt{a_{n_{rms}}^2 - a_{sn_{rms}}^2} = 1.81 \mu G$$

# **Noise Budget Partitioning**

Assuming no-noise sensor

# **Noise Budget Partitioning (4)**

SNR due to the only electronic Noise evaluated at Sensor level:

$$SNR_{e} = 20 \text{ '} \log_{10}(\frac{S}{\sqrt{2}} \text{ '} \frac{1}{a_{en_{rms}}}) = 117.9 dB$$

- ➡ First design specification,

- the SNR @ADC-output > 117.9dB

- ► → ADC resolution has to be:

$$ENOB_{ADC} > \frac{SNR_{e} - 1.76}{6.02} = 19.3bit$$

# **ADC Performances (1)**

- ADC resolution >19.3 bit

- SC- $\Sigma\Delta$  Architecture

- the only one to satisfy this challenging design specifications.

- Oversampled ADC architecture

Relaxed the Anti-Alias Filer requirements specification

- The small signal bandwidth

- Critical opamp flicker-noise

- the ADC with Correlated Double Sampling or Chopper Stabilization technique

### **ADC Performances (2)**

- Which Power Supply?

- ADC under 5V supply domain

- → higher reference voltage compared to 3.3V supply domain

- Sample capacitor reduction (less area) and/or reduce the Oversampling Ratio (smaller opamp bandwidth)

$$V_{signal} \propto V_{ref}$$

$V_{noise} \propto \sqrt{\frac{K_b T}{C_s OR}}$

V<sub>ref</sub>: ADC reference Voltage K<sub>b</sub>: Boltzmann Constant T: Temperature C<sub>s</sub>: Sampling Capacitor OR: Oversampling Ratio

# **ADC Performances (3)**

- Which Power Supply?

- 5.0V MOS have higher 1/f noise than 3.3V MOS

- Increased oxide thickness → Increased trap number in the silicon oxide interface.

- If the ADC is designed under 5.0V domain

- The Charge-Amplifier to be designed under the same supply domain to use all the available ADC dynamic range

Both solutions have some advantages (larger signal @5V) and some drawbacks (larger 1/f noise @5V)

The best compromise performance vs. power consumption has been achieved supplying the ADC and Charge Amplifier at 3.3V

# **ADC Performances (5)**

Assumptions:

- ADC Differential Reference Voltage → 2.5V<sub>peak</sub>

- Possible under 3.3V domain

- Maximum ADC Input signal → 2.0V<sub>peak</sub>

- To avoid Modulator Saturation issue

- ~2dB of margin

- ADC resolution required 20 bit

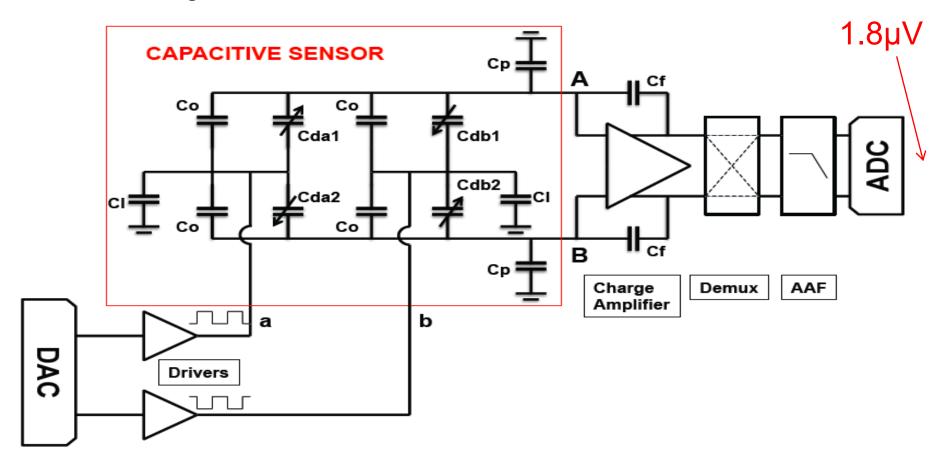

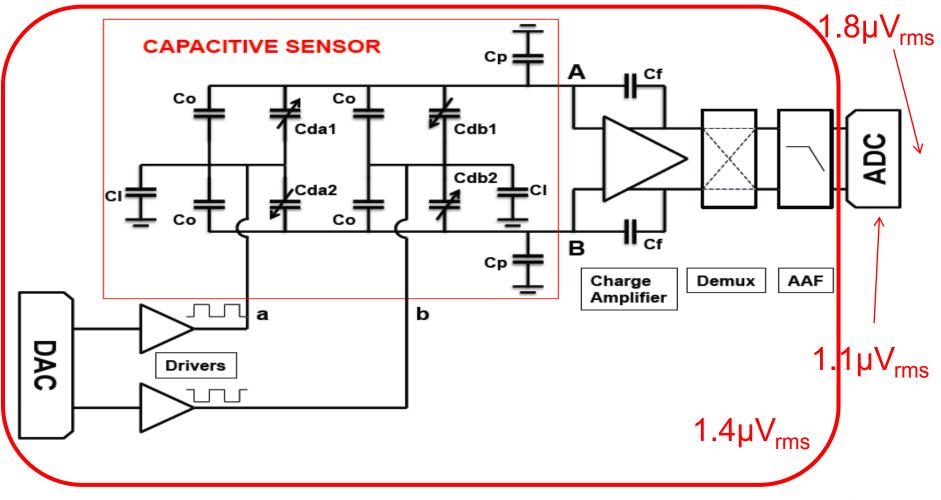

## **ADC Performances (6)**

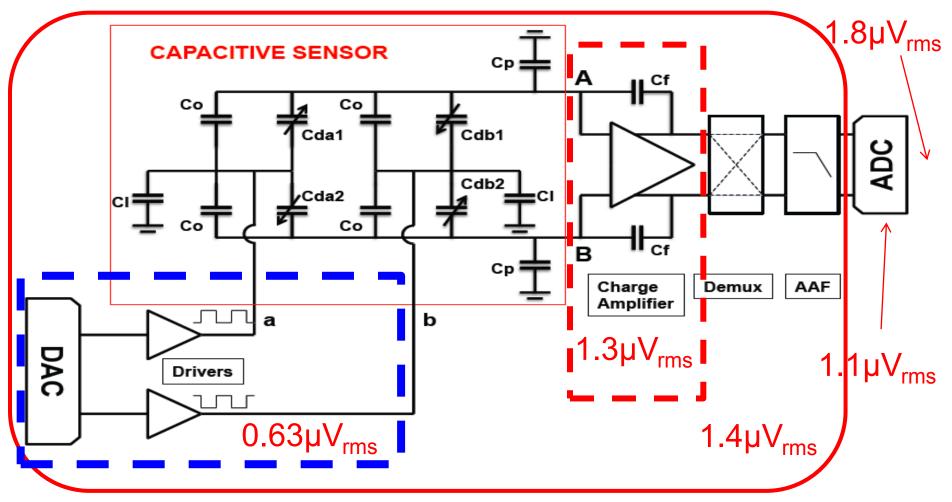

#### Total Noise at ADC output

$$V_{n_{@ADCoutput}} = \frac{S_{in\_ADC_{max}}}{\sqrt{2}} \cdot 10^{-\frac{SNR_{e}}{20}} = \frac{2}{\sqrt{2}} \cdot 10^{-\frac{117.9}{20}} = 1.8 \,\mu V$$

#### ADC Noise

Assuming dominant quantization noise

$$V_{nADC} = \frac{LSB}{\sqrt{12}} = \frac{V_{in\_ADC_{max}}}{2^{(nbit-1)}}, \quad \frac{1}{\sqrt{12}} = \frac{2}{2^{19}}, \quad \frac{1}{\sqrt{12}} = 1.1 \ \mu V$$

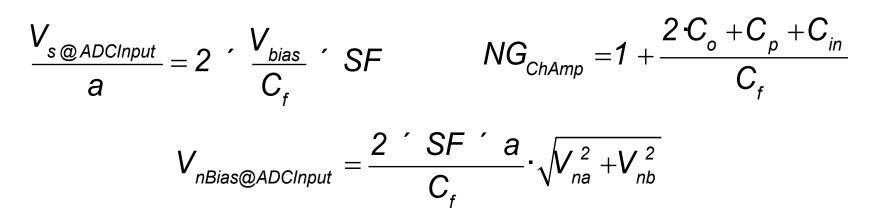

#### **Biasing and Reading Noise partitioning**

$$V_{nBiasRead} = \sqrt{V_{n\_@ADCout}^2 - V_{nADC}^2} = 1.42 \,\mu V$$

The system is divided in to two different macro blocks:

- Reading (Charge Amplifier and AAF)

- Biasing (DAC and Driver)

|                                     | Noise Biasing/Noise Reading |        |     |        |        |

|-------------------------------------|-----------------------------|--------|-----|--------|--------|

|                                     | 3/1                         | 2/1    | 1/1 | 1/2    | 1/3    |

| Noise Biasing<br>V <sub>nBias</sub> | 1.35µV                      | 1.27µV | 1µV | 0.63µV | 0.45µV |

| Noise Reading<br>V <sub>nRead</sub> | 0.45µV                      | 0.63µV | 1µV | 1.27µV | 1.35µV |

### **Noise Budget Partitioning**

Assuming no-noise sensor

#### **Sensor Transfer Function**

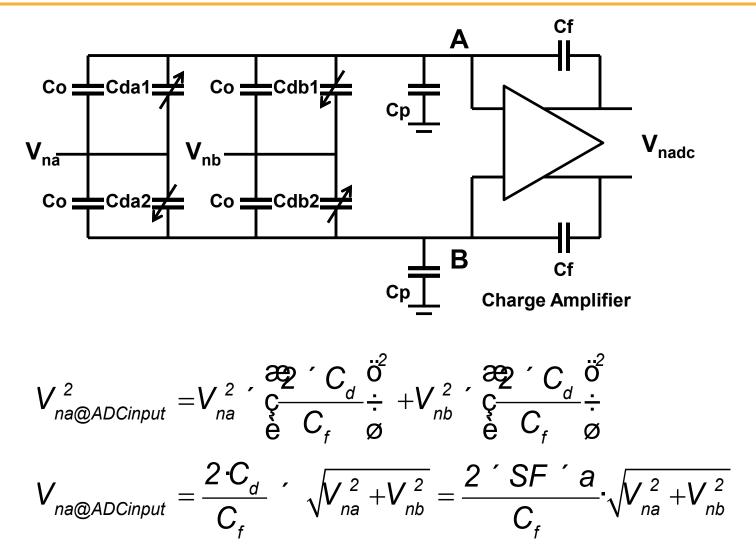

#### **Biasing Noise Gain**

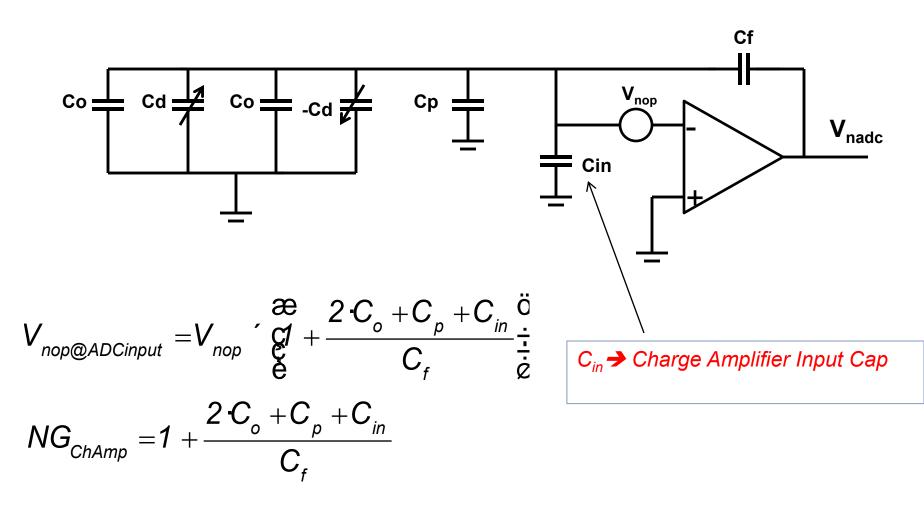

#### **Charge Amplifier Noise Gain**

### **Biasing Voltage (1)**

- To maximize the ADC input → two possibilities:

- Increase the Bias Voltage

- Decrease the ChAmp feedback cap (C<sub>f</sub>)

- Increase the Charge Amplifier Gain

- $C_f \checkmark \Rightarrow$  the (ChAmp & BiasCircuit ) ADC input noise

- ► → No effect on the overall SNR

## **Biasing Voltage (2)**

- To optimize SNR

- $\rightarrow$  V<sub>bias</sub> has to be maximized

- The Sensor Drivers has to be realized under 5.0V Supply Domain

- Considering Supply Variation & Driver Output MOS headroom

$$\rightarrow V_{\text{bias}} = 4.5 V$$

#### **Charge Amplifier Feedback capacitor**

•  $\rightarrow$  V<sub>bias</sub>=4.5V

• The feedback cap  $(C_f)$  is evaluated to maximize ADC DR when the maximum acceleration  $(a_{max})$  is applied to the sensor

$$V_{ADC} = 2 \stackrel{\cdot}{,} \frac{SF \stackrel{\cdot}{,} a}{C_{f}} \stackrel{\cdot}{,} V_{bias}$$

$$C_{f} = 2 \stackrel{\cdot}{,} SF \stackrel{\cdot}{,} a_{max} \stackrel{\cdot}{,} \frac{V_{bias}}{V_{ADCmax}} = 2 \stackrel{\cdot}{,} 300 fF/G \stackrel{\cdot}{,} 2G \stackrel{\cdot}{,} \frac{4.5V}{2V} = 2.7 pF$$

#### **Biasing and Reading Noise partitioning (2)**

■ Read-out noise → Charge Amplifier noise

$$NG_{ChAmp} = 1 + \frac{2 C_{o} + C_{p} + C_{in}}{C_{f}} > 1 + \frac{2 C_{o} + C_{p}}{C_{f}} = 1 + \frac{2 + 12}{2.7} = 6.2$$

The Charge Amplifier Input Noise is amplified

Bias Noise Gain

$$NG_{Biasmax} = \frac{\Delta C_{max}}{C_f} = \frac{2 \times SF \times a_{max}}{C_f} = \frac{2 \times 300 fF/G \times 2G}{2.7 pF} = 0.44$$

The Bias Input Noise is amplified

43µ\

45

#### **Biasing and Reading Noise partitioning (3)**

- Reading Noise is more critical than Biasing Noise due to Charge Amplifier Noise Gain

- Strategy: Increasing the Reading Noise Budget compared to the Biasing Noise Budget

- 1/2 may be the best compromise to increase the reading Noise Budget

- 1/3 small improvement for Reading and bigger worsening for the Biasing Noise Budget

|                                                                                                          |                                     | Noise Biasing/Noise Reading |        |     |        |        |

|----------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------------|--------|-----|--------|--------|

|                                                                                                          |                                     | 3/1                         | 2/1    |     |        | 1/3    |

|                                                                                                          | Noise Biasing<br>V <sub>nBias</sub> | 1.35µV                      | 1.27µV | 1µV | 0.63µV | 0.45µV |

|                                                                                                          | Noise Reading<br>V <sub>nRead</sub> | 0.45µV                      | 0.63µV | 1µV | 1.27µV | 1.35µV |

| $V_{n\text{Read}@ADCInput} = 1.27 \mu V$                                                                 |                                     |                             |        |     |        |        |

| $V_{nBias@ADCInput} = 0.63 \mu V$ $\triangleright$ $V_{nBias@DriverOutput} = \frac{0.63 \mu V}{0.44} = $ |                                     |                             |        |     |        |        |

### **Noise Budget Partitioning**

Assuming no-noise sensor

#### **Noise Budget Partitioning Conclusion**

- Starting from the high level system specifications

- A preliminary noise breakdown

- To descend the hierarchy, it is necessary to define the architecture of each block

- → Next step → defining the circuits architecture and their noise budget

- It is mandatory to take into account the mod/dem effects

# Architecture

- Introduction

- Design Objectives

- Noise Budget Partitioning

- Architecture

- ADC Architecture

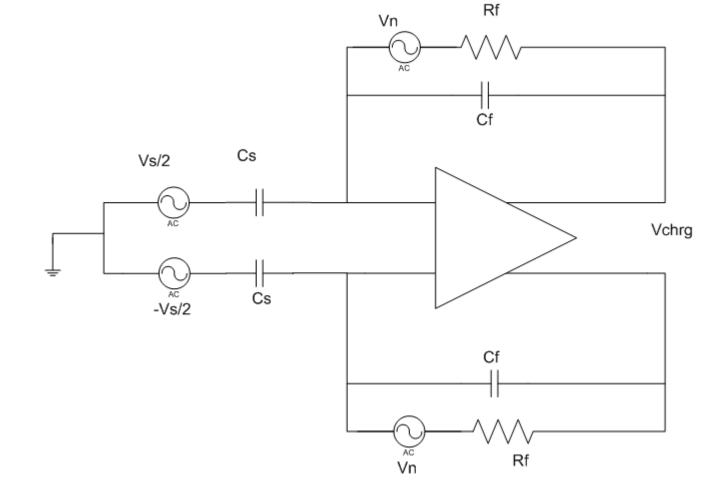

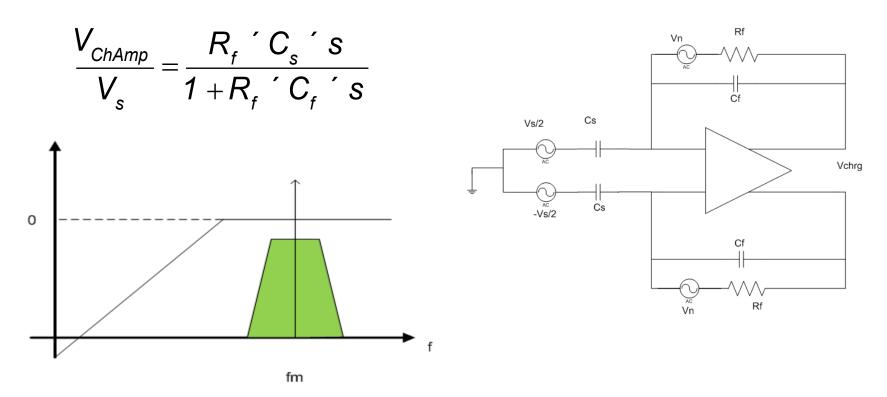

#### **Charge Amplifier**

Assuming no-noise sensor

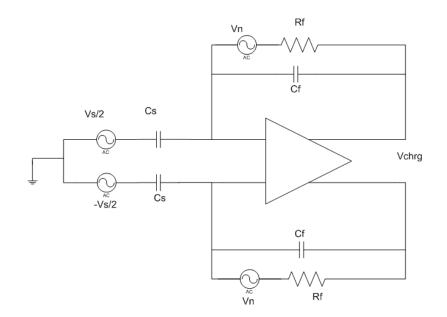

### **Charge Amplifier (1)**

Charge Amplifier needs a opamp input DC polarization

## **Charge Amplifier (2)**

- The Charge Amplifier Signal is Amplitude Modulated

- Carrier frequency  $\rightarrow f_m$

- To reduce the Charge Amplifier gain error

- The pole frequency has to be lower than modulation frequency

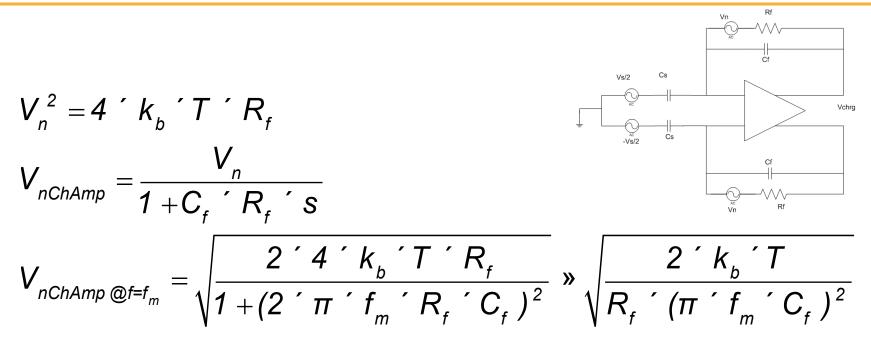

#### **Charge Amplifier (3)**

R<sub>f</sub>  $\uparrow$   $\rightarrow$  Output Noise density (due to R<sub>f</sub>)  $\checkmark$

## **Charge Amplifier (4)**

- The noise spec  $\rightarrow V_{nRead} = 1.27 \mu V$

- Assumption:

- *R*<sub>f</sub>-Noise ≈ 1/3 of the to Total Noise (negligible effect in the noise power budget)

- The ChAmp Output Noise density due to feedback resistor is:

$$\frac{1.27\,\mu N}{3\,\,'\,\sqrt{300}} = 24nV\,\,/\,\sqrt{Hz}$$

Assumption: Modulation frequency f<sub>m</sub>=100kHz

$$R_{f}^{3} \frac{2 \operatorname{k}' T}{V_{n\_ChAmp@f=f_{m}}^{2} \operatorname{(}\pi \operatorname{f}_{m}^{\prime} C_{f}^{\prime} \operatorname{)}^{2}} = 20M\Omega$$

$$f_{pole} = \frac{1}{2 \operatorname{\pi}' R_{f}^{\prime} C_{f}} = 3kHz \ll f_{m}$$

#### **Charge Amplifier (5)**

- Large R<sub>f</sub>'s

- are difficult to be integrated in standard CMOS process

- require large Area

- Switched Capacitor

- MOS operating in triode

- Integrated Resistor

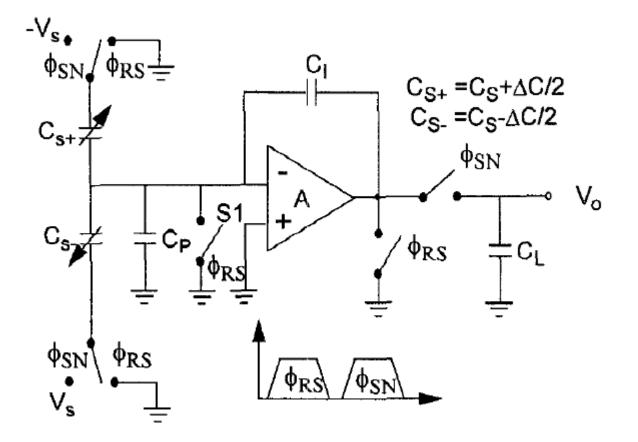

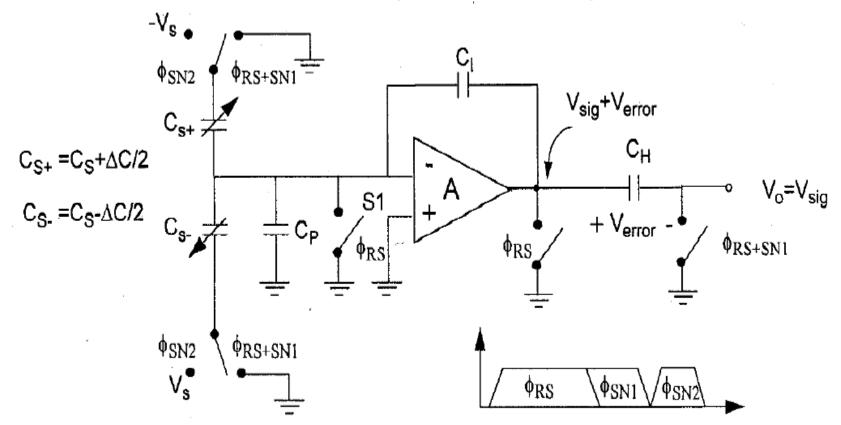

#### **Charge Amplifier (6)**

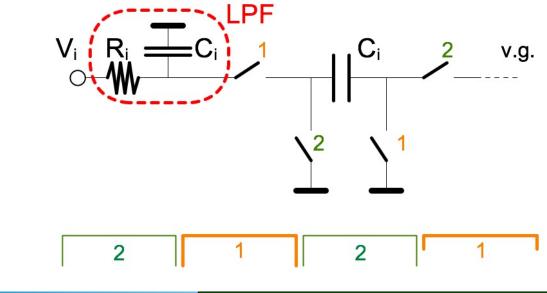

Switched Capacitor capacitance sensing

"Correlated Double Sampling in Capacitive Position Sensing Circuits for Micromachined Applications" Wongkomet, N.; Boser, B.E.;1998

## **Charge Amplifier (7)**

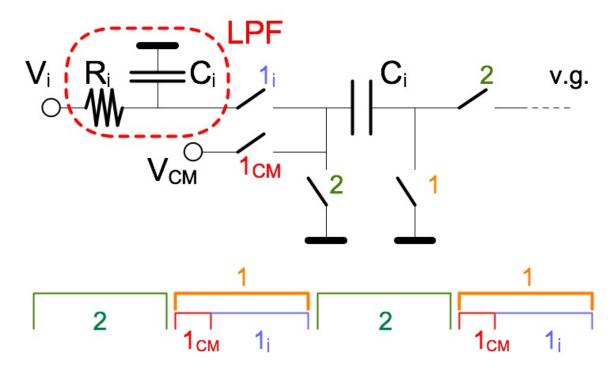

Switched Capacitor capacitance sensing with CDS

"Correlated Double Sampling in Capacitive Position Sensing Circuits for Micromachined Applications" Wongkomet, N.; Boser, B.E.;1998

## **Charge Amplifier (8)**

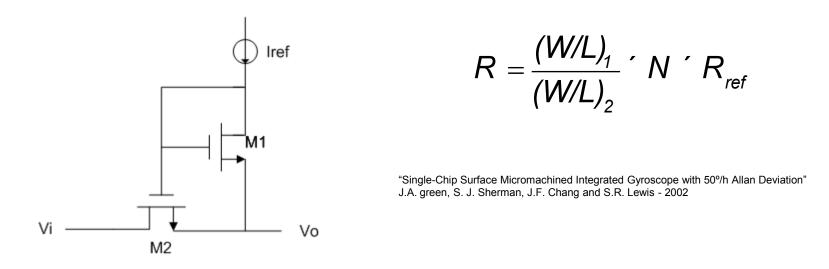

MOS operating in Triode region

- Good operation with small (V<sub>o</sub>-V<sub>i</sub>) to keep M2 in triode

- Same ChAmp Input and Output

- This solution is mainly used when a pre-Amplifier is inserted after the Charge Amplifier

#### **Charge Amplifier (9)**

- Integrated Resistor

- ONO Noise Folding

- Better Linearity/No dynamic limitation

- Better Noise Performance

- Beneficial States Area increments

- Roughly Area Estimation

- **Doped Poly Typical**  $Rs(\Omega/sq)=300 \rightarrow area for 2x 20M\Omega \& W=1\mu m$

$$A = \frac{2 \, \hat{} \, 20M\Omega}{300} = 0.13mm^2$$

HIPO Rs(Ω/sq)=1000 → area for 2x 20MΩ & W=1µm

$$A = \frac{2 \, \hat{} \, 20M\Omega}{1000} = 0.04mm^2$$

### **Charge Amplifier (10)**

- Diffused Resistor have Rs higher or equal to HIPO resistor

- Standard process (no extra mask)

- B Linearity Issue

- B Junction Leakage at the high Impedance Input of the Charge Amplifier

## **Charge Amplifier (11)**

- The choice between HIPO and doped Poly depends on cost evaluation (mask/process vs. area)

- The real area used for the feedback resistor is higher than first roughly estimation

- Distance between modules

- Active area density

## **Charge Amplifier (12)**

- ChAmp opamp

- Output swing & Anti-Alias Filter Resistive Load

- Two-Stage topology

- High current during the carrier rising/falling edge

- Class-AB output stage

- Overall gain error reduction

- $\rightarrow$  Closed-Loop gain-gandwidth > 10x  $f_{\rm m}$

- ChAmp feedback factor ≈ 1/NG<sub>ChAmp</sub> = 1/6

- Opamp noise is chopped

- → Thermal noise dominates

- Thermal noise reduction

- Large differential pairs and current generator MOS

- ➡ high parasitic capacitor

- ► → stability Issue

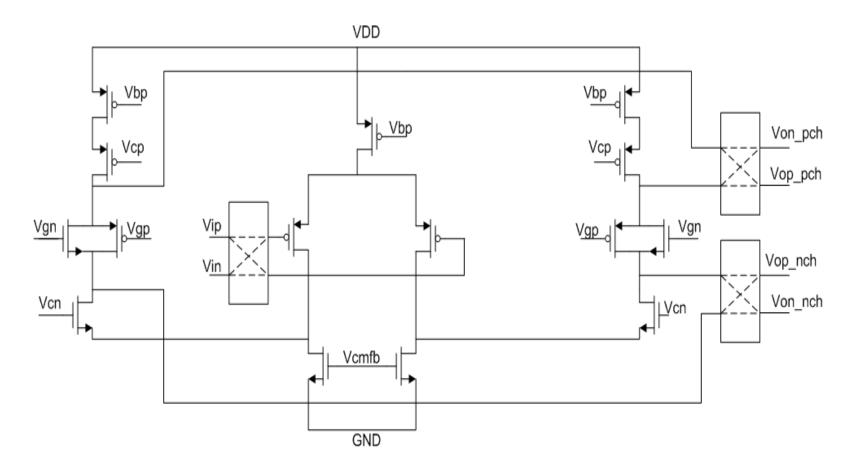

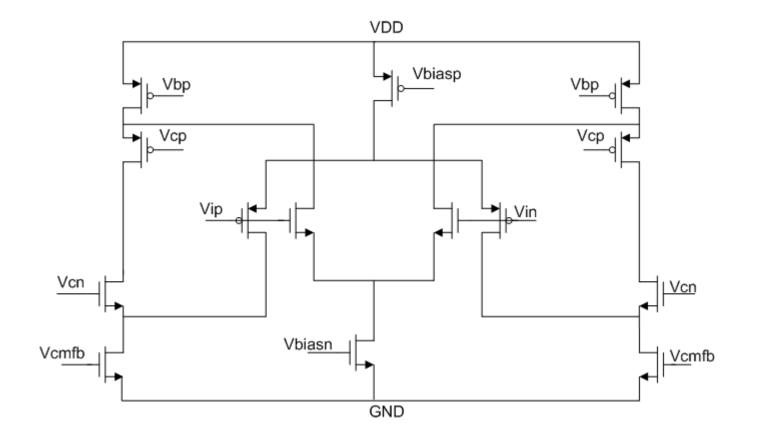

## **Charge Amplifier (13)**

- Recent technologies have small difference between P-Ch and N-Ch flicker noise

Op-Amp with N-Ch differential pair can achieve better Noise performance

- The advantages of N-Ch differential pairs:

- Higher  $g_m \rightarrow$  Lower thermal noise

- Higher rejection of the P-Ch current generator Noise.

- Opamp noise is choppered

## **Charge Amplifier (14)**

- Low Noise circuits design

- Iarge transistor

- ► → large channel width and MOS area

- thermal and 1/f noise reduction

- In case of capacitive sensing

$$NG_{ChAmp} = 1 + \frac{2 C_{o} + C_{p} + C_{in}}{C_{f}}$$

- Large Transistor

- ► → Large gate capacitance

- Increased Charge Amplifier Noise Gain

## **Charge Amplifier (15)**

- For dominant thermal noise (chopper)

- Minimum noise for  $C_{in} \leq C_{sensor} + C_{interconnect}$

$$NG_{ChAmp} = 1 + \frac{2 \cdot C_o + C_p}{C_f} = 6.2$$

$$\frac{V_{nRead@ADCInput}}{NG_{ChAmp}} \cdot \sqrt{BW} = \frac{1.27\mu V}{6.2 \cdot \sqrt{300Hz}} \approx 11nV / \sqrt{Hz}$$

#### **Charge Amplifier (16)**

- This rough result is useful only to understand the challenge of the Charge Amplifier opamp design

- $\rightarrow$  11nV/ $\sqrt{Hz}$  is an aggressive input noise target

- To reduce the noise

- Sol1 → mod/dem frequency  $(f_m)$  increase

- $\rightarrow f_m$  > opamp flicker corner frequency

- higher power consumption (the Mod/Dem frequency effects all the circuits specifications)

- Complexity in circuits Implementation

- Sol2 → chopper opamp

66

## **Charge Amplifier (17)**

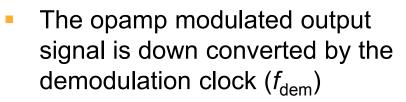

The opamp 1/f noise is modulated by the Choppered square wave at frequency f<sub>1</sub> (Odd harmonics)

*F*<sub>1</sub> defined avoid that its odd harmonics are down converted in base band by the demodulation square wave

#### **Charge Amplifier (18)**

#### First Stage of the Chopper Charge Amplifier Op-Amp

## **Charge Amplifier (19)**

- Both solutions (Choppered and CT) have been designed and compared.

- CT solution performs the best results with the in term of:

- Power consumption

- Performances

- Linearity

- Development time

- Op-Amp specification:

- GBW ≈ 10MHz

- Input referred Noise ≈  $11nV/\sqrt{Hz}$

- Current Consumption ≈ 2.2mA → 7.3mW@3.3V

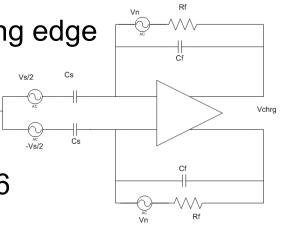

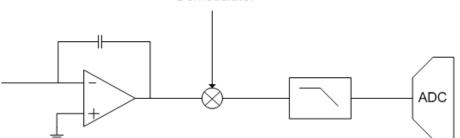

## **Anti-Alias Filter (1)**

- Large ADC Over Sampling Ratio

- One single pole Filter is enough to reduce the folding noise issue

- The Reading Block Noise budget is mainly used by the Charge Amplifier (High Complexity).

- If active solution is implemented the AAF Op-Amp needs Chopper Stabilization technique in order to remove the flicker Noise

Passive Filter with external capacitor solution is widely used in very high performance standalone ADC.

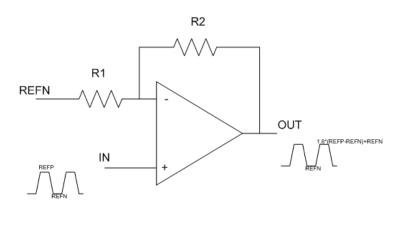

#### **Anti-Alias Filter (2)**

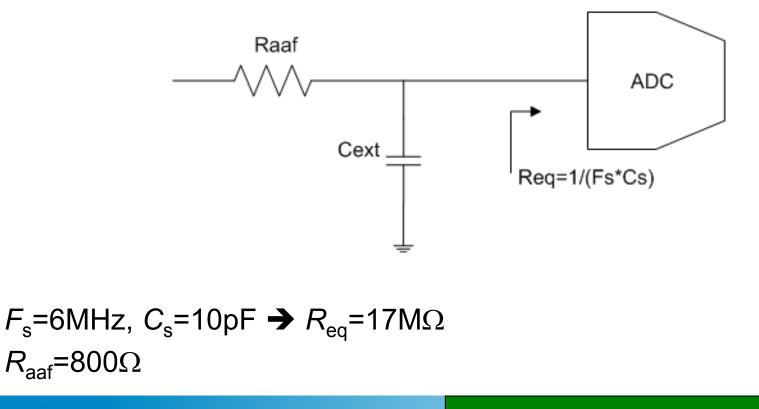

The value of the AAF resistor is designed in order to have an attenuation of 0.4dB between the Dem. output and the ADC Input

#### **Anti-Alias Filter (3)**

The AAF noise voltage:

$$V_{n_{R_{aaf}}} = \sqrt{4 \, \check{} \, k_b \, \check{} \, T \, \check{} \, R_{aaf} \, \check{} \, BW} = 65nV$$

Negligible

$$C_{ext}$$

=20nF >>  $C_s$

Cut-Off frequency: 10kHz < Modulation frequency

Attenuation at the ADC sampling frequency: -56dB

#### **Anti-Alias Filter (4)**

#### **Passive Anti-Alias Filter solution**

- Simple

- Second States Compared With Active Solution

- Oliseless

- Over consumption

- 8 Requires external capacitors

- Bain Error

### **Bias Circuit**

Assuming no-noise sensor

### **Bias Circuits**

- Low Power/Low Noise Application → Reduce no. of circuits

- The Biasing circuit is divided in two blocks

- DAC that is used to set the amplitude of the Carrier

- Driver feeds the Sensor and Buffer the DAC output

- High Impedance input Driver

- Two possible Implementations:

- DAC dynamic Range 4.5V

- - Rail-to-Rail Input Stage Op-Amp

- DAC dynamic Range 2.5V (as ADC)

- - B The DAC and Driver Input Noises are amplified

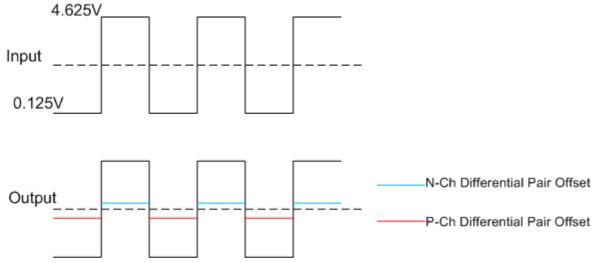

### Bias circuit / Rail-to-Rail Input Stage (1)

# Bias circuit / Rail-to-Rail Input Stage (2)

Rail-to-Rail Input stage critical point

distortion due to different offset of the P-ch and N-ch diff-pairs

- A squared wave is added to the carrier, its amplitude is equal to the difference between the N-ch and P-Ch differential pairs Offset.

- The carrier amplitude is effected by Offset Issue and it depends on DAC setting → equivalent to an INL issue

### Bias circuit / Rail-to-Rail Input Stage (3)

- INL problem reduced increasing the MOS sizes to be < DAC INL</p>

- Additional problem → <u>the diff-pair differential Flicker Noise is</u> <u>modulated</u>

- The power of the modulated Flicker Noise is equal to the sum of P-Ch and N-Ch differential pairs Flicker Noise power

- The Driver Modulated Flicker Noise is demodulated in base band by the Demodulator and so it appears at ADC output

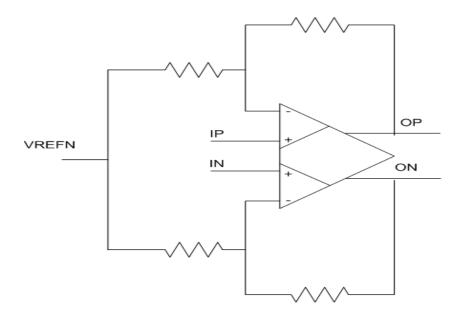

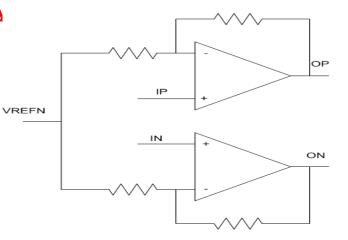

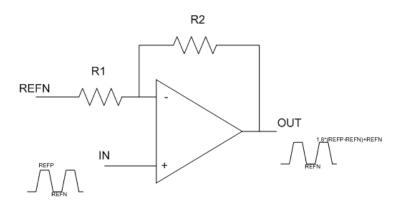

### **Bias circuit / Non Inverting Amplifier (1)**

### Fully Differential Difference Amplifier

- So extra Pole due to current generator

- Good CMRR

- 8 More design Complexity

- 8 Needs Common Mode Feedback Circuit

# **Bias circuit / Non-Inverting Amplifier (2)**

- Single Ended opamp

- Simple Architecture

- Use power (No CMFB)

- Extra pole due to differential to Single-Ended MOS diode

- No Common Mode Rejection (the Common Mode and Differential signals are Amplified)

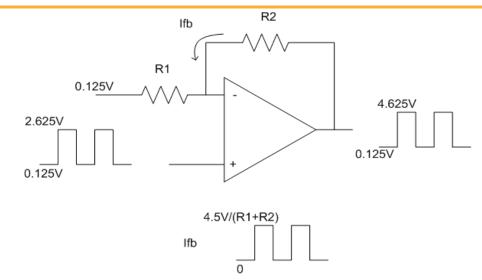

# **Bias circuit / DAC Architecture**

- Differential DAC inserted before the Modulator

- Static DAC.

- BAC noise is not Choppered (Inserted before Modulator).

- Two possible topologies:

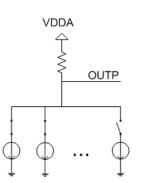

- Current Steering

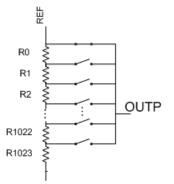

Resistive DAC Array (Poly Resistor)

Poly Resistor Flicker Noise is lower than MOS flicker Noise

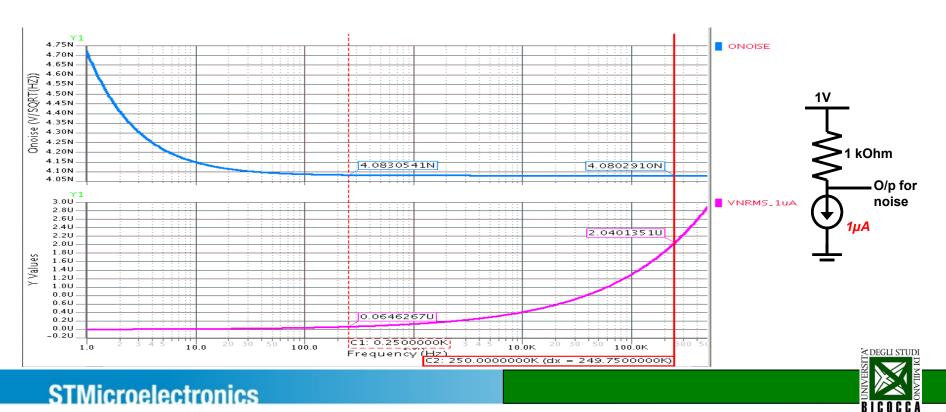

### Rp1pp (p+poly res) Flicker/Thermal Noise evaluation (1)

- Flicker noise (pink noise) is present in polysilicon resistor with thermal noise.

- It depends on bias voltage, area and frequency as shown below:

- $Vn^2 \propto V_{bias}^2 / (W.L.f) \rightarrow flicker noise increases as bias voltage increases$

- Ideal thermal noise for  $1k\Omega \rightarrow \sqrt{[4*1.38e-23\cdot300\cdot10^3]} = 4.07nV/\sqrt{Hz}$

- Total noise simulation graph of  $1k\Omega$ , Rp1pp resistor with  $1uA (\rightarrow \Delta V = 1mv)$

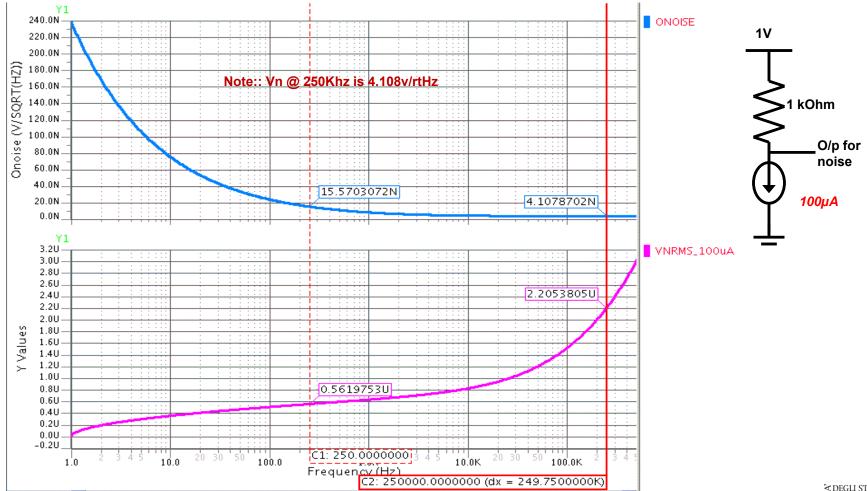

### Rp1pp (p+poly res) Flicker/Thermal Noise evaluation (2)

• Total noise simulation of 1k $\Omega$ , Rp1pp resistor with 100uA ( $\rightarrow \Delta V=0.1V$ )

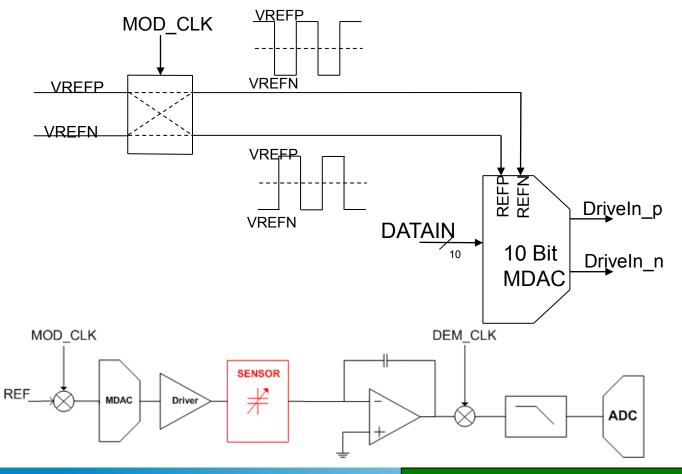

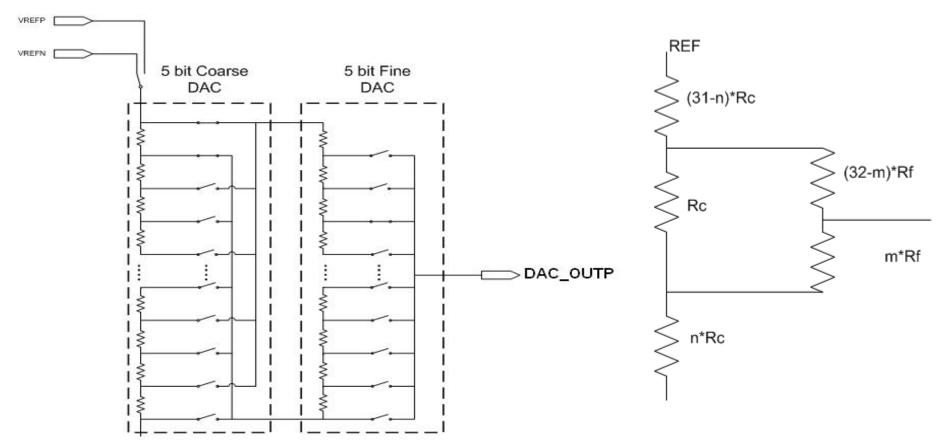

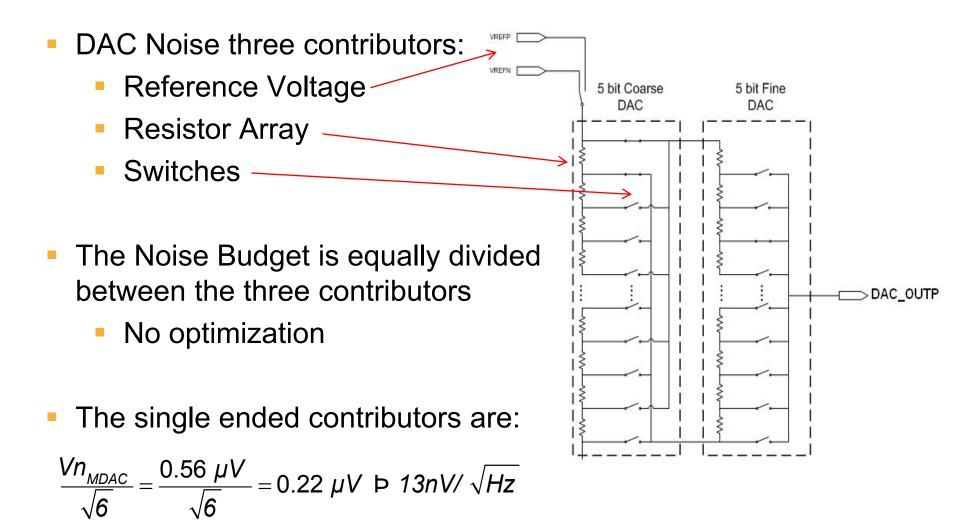

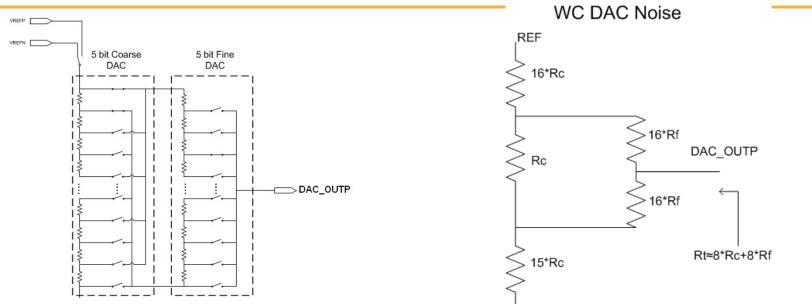

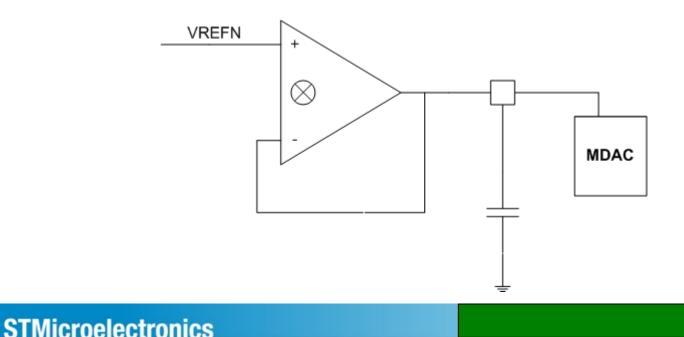

### **MDAC Architecture**

#### DAC Flicker Noise Reduction

- Ø Increase the dimension of the Resistor (Huge Impact on device area)

- ③ Move the Modulation before the DAC → MDAC Architecture

# **MDAC topology (1)**

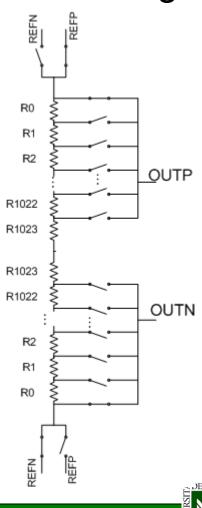

- 10 Bit Differential MDAC Single Resistor String solution:

- 2\*1024 resistors

- 2\*1024 switches

- Good linearity

- B Too Small value of the Resistor Module

- Best States States Best States Best States Best States States

- Area

- Parasitic Capacitor

# **MDAC topology (2)**

# 10 Bit Differential MDAC Double resistors (Segmented)String Array

# **MDAC topology (3)**

- 10 Bit Differential MDAC Double Resistor String Array solution:

- 2\*64 resistor

- 2\*64 switches

- B Worse linearity

- Bigger Resistor Module

- Seduced Number of switches

### **Driver Feedback resistor (1)**

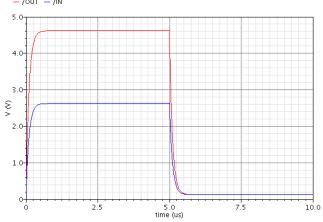

- The squared wave current flowing in the feedback resistor modulates the flicker Noise of the P-Poly resistance

- The resistor flicker noise is folded in base band by the demodulator

### **Driver Feedback resistor (2)**

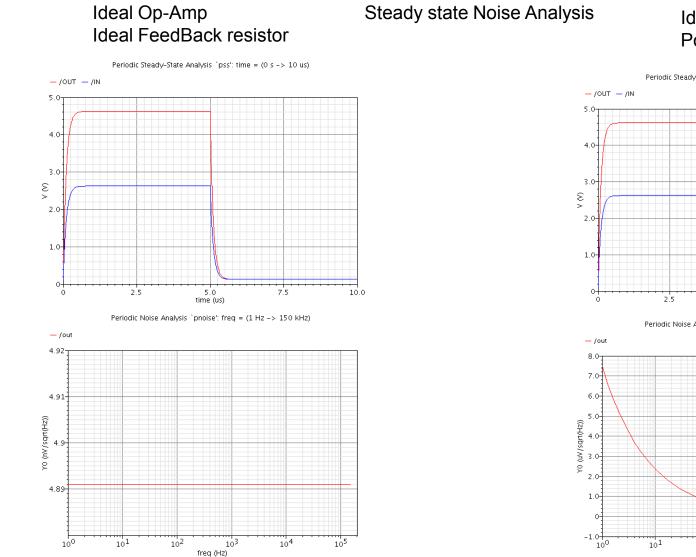

#### Ideal Op-Amp Poly Resistor

Periodic Steady-State Analysis `pss': time = (0 s -> 10 us)

Periodic Noise Analysis `phoise': freq = (1 Hz -> 150 kHz)

### **Driver Feedback resistor (3)**

- Solutions

- Increase the value of the feedback resistor

- → maximum current reduction

- thermal noise increase

- Increase the feedback resistor area

- flicker noise reduction

- → parasitic capacitor increase

- stability issue and/or reduced closed loop bandwidth

- Use Diffused resistor, with negligible flicker noise

- ► → Linearity Issue

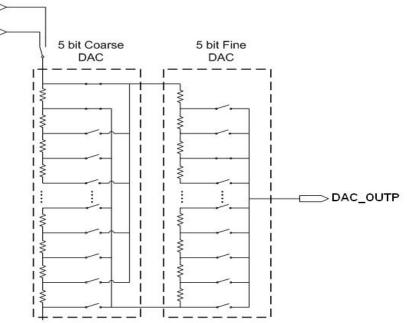

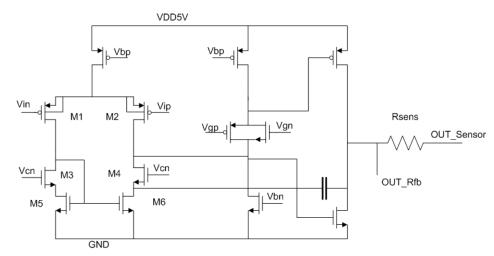

### **Driver Operational Amplifier (1)**

- Output Dynamic range and Resistive feedback

- Two stage operational Amplifier

- Low power

- Class AB Output Stage

- Input Voltage Range [125mV-to-2.625V]

- ► → P-Ch Input stage and supplied under 5V domain

- Output Voltage Range [125mV-to-4.625V]

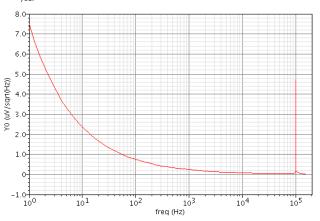

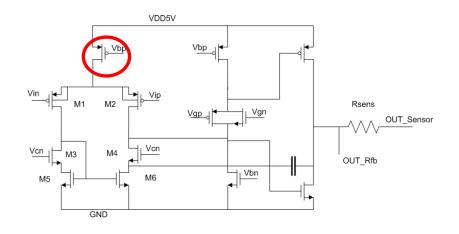

### **Driver Operational Amplifier (2)**

### **Driver Operational Amplifier (3)**

- The Input Voltage Range is compatible with 3.3V MOS

- 3VMOS better noise performance than 5VMOS

- ► → (M1, M2, M3, M4, M5 and M6 are 3.3V MOS)

- Ahuja compensation

- → move the output pole at higher frequency

- Output series resistor to Sensor Capacitive load adds a zero that help stability

### **Noise Budget Partitioning**

Assuming no-noise sensor

### **Biasing Circuit Design (1)**

• Driver Gain  $G_{\text{Driver}} = 4.5 \text{V}/2.5 \text{V} = 1.8$

$$V_{nBias@DriverOutput} = \frac{0.63\mu V}{0.44} = 1.43 \ \mu V_{rms}$$

$$V_{nBias@DriverOutput} = \frac{V_{nBias@DriverOutput}}{G_{Driver}} = \frac{1.43 \ \mu V_{rms}}{1.8} = 0.79 \ \mu V_{rms}$$

The noise budget is equally divided between MDAC & Drivers

$$V_{nMDAC} = V_{nDrivers} = \frac{V_{nBias@DriverInput}}{\sqrt{2}} = 0.56 \ \mu V_{rms}$$

Two equal single-ended drivers are used

$$V_{nDriver} = \frac{V_{nDrivers}}{\sqrt{2}} = 0.4 \ \mu V_{rms}$$

95

# **Biasing Circuit Design (2)**

- Driver Noise Contributors

- Opamp

- Feedback resistor

- The Driver Noise budget is equally divided between opamp and Feedback resistor contributors (No optimization)

$$Vn_{D_{-}OP} = Vn_{D_{-}RFB} = \frac{Vn_{Driver}}{\sqrt{2}} = \frac{0.4 \ \mu V}{\sqrt{2}} = 0.28 \ \mu V \qquad \text{Only thermal noise}$$

$$\frac{Vn_{D_{-}OP}}{\sqrt{BW}} = \frac{Vn_{D_{-}RFB}}{\sqrt{BW}} = \frac{0.28 \ \mu V}{\sqrt{300}} = 16nV \ / \sqrt{Hz}$$

$$\frac{\partial Vn_{D_{-}RFB}}{\partial W} = \frac{\partial^{2} (1 - V)}{\partial W}$$

$$\frac{\partial Vn_{D_{-}RFB}}{\partial W} = \frac{\partial^{2} (1 - V)}{\partial W}$$

$$\frac{\partial Vn_{D_{-}RFB}}{\partial W} = \frac{\partial^{2} (1 - V)}{\partial W} = \frac{\partial^{2} (1$$

### **Biasing Circuit Design (3)**

- Opamp design is mainly driven by gain bandwidth requirement

- GBW=4MHz

- Input referred Noise density=  $28 \text{nV}/\sqrt{\text{Hz}}$

- Driver Current Consumption =300uA

- Total Driver Current consumption

- I<sub>tot</sub>=300µA+300µA+72µA=672µA

- P<sub>tot</sub>=3.4mW

# **Biasing Circuit Design (4)**

### **Biasing Circuit Design (5)**

- The relationship between Coarse and Fine resistor depends on DAC Linearity requirements

- Ex.:  $R_f = 4 \cdot R_c$   $\begin{pmatrix} 13n V' \sqrt{Hz} \end{pmatrix}^2 = 4 \times K_b \times T \times 8 \times (R_c + R_f) \\ R_c = 255\Omega$   $R_f = 1020\Omega$  $I_{DAC} = \frac{V_{ref}}{32 \times R_c \times 2} = 153 \mu A$

### **Biasing Circuit Design (6)**

- Power consumption reduction

- $\rightarrow$  two external caps filter the noise coming from V<sub>REF</sub>

- The DAC reference opamp is choppered

- Static opamp

- $\rightarrow$  Low power consumption (<100µA per-buffers)

|                   | Current<br>Consumption<br>[ µA ] | Supply Voltage<br>[ V ] | Power<br>Consumption<br>[ mW ] |

|-------------------|----------------------------------|-------------------------|--------------------------------|

| Charge Amplifier  | 2200                             | 3.3                     | 7.3                            |

| Anti-Alias Filter | 0                                | 3.3                     | 0                              |

| Drivers           | 672                              | 5.0                     | 3.4                            |

| Differential MDAC | 353                              | 3.3                     | 1.16                           |

### **Driver Noise vs. DAC Output Slope (1)**

• Output steps would have to be as more ideal as possible

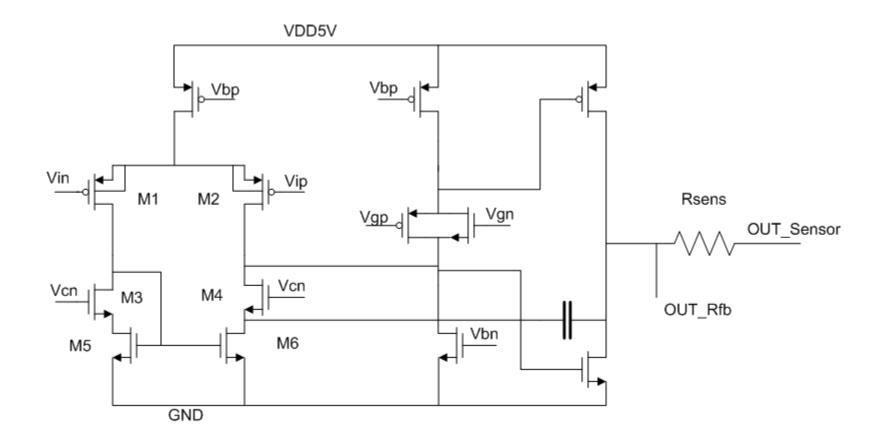

# **Driver Noise vs. DAC Output Slope (2)**

Tal current generator noise is modulated by the diff-pair unbalancement in slew-rate conditions

Periodic Steady-State Analysis `pss': time = (0 s -> 20 us)

Additional noise

3.0-71 2.5 2.0- $\underset{>}{\overset{\odot}{\Sigma}}_{1.5}$ 1.0-.5-5.0-170UT 4.0 €<sup>3.0-</sup> ><sub>2.0</sub>-1.0-0-5.0 10.0 15.0 20.0 time (us)

### **Driver Noise vs. DAC Output Slope (3)**

- Tail current generator modulated noise reduction

- Sol1 J Increase Op-Amp Gain Bandwidth

- ► → Increase power consumption

- Sol2→ Decrease DAC Output Signal Slope

- Increase Gain error (The effect is equivalent to reduce the Carrier Amplitude)

- To match the maximum ADC dynamic range the Charge Amplifier gain has to be increased

- Trade off GBW vs. Slope → Power vs. Noise

# **ADC Architecture**

- Introduction

- Design Objectives

- Noise Budget Partitioning

- Architecture

- ADC Architecture

### 20b 250Hz ADC

- Sigma-Delta is the only possible 20b ADC solution

- No matching requirement

- Oversampling requirement (easy to be performed at small signal bandwidth)

### 20b 250Hz Sigma-Delta ADC

- Overall Specs

- ADC Resolution:

- THD

- Bandwidth

- Output rate

- Anti Aliasing Filter

- Supply Voltage

- Area

- > 20 bit (SNR >123 dB)

- < -90 dB

- 1Hz-250Hz

- 500 Sps

- External

- 3.3V

- < 3.5 mm^2

### 20b 250Hz Sigma-Delta ADC

- Noise Budget calculation

- Reference Voltage: 2.5V

- Input Amplitude: 4V<sub>pp</sub> (1.4V<sub>rms</sub>)

### For 125dB-SNR → Total Noise ≈ 700 fV<sup>2</sup>

### 20b 250Hz Sigma-Delta ADC

| Noise Budget calculation          |                     |

|-----------------------------------|---------------------|

| For 125dB-SNR 	→ Total Noise ≈    | 700 fV <sup>2</sup> |

| Noise Budget                      |                     |

| Opamp Noise after chopper         | 150 fV <sup>2</sup> |

| kT/C Noise                        | 250 fV <sup>2</sup> |

| 250 fV <sup>2</sup> < kT/(Cs·OSR) |                     |

| Reference Noise                   | 200 fV <sup>2</sup> |

| Q <sub>noise</sub> + Other noise  | < 50fV <sup>2</sup> |

- → Equivalent SNR (considering only Q<sub>noise</sub>) = 136 dB

- → MATLAB SNR requirement > 136 dB

kΤ

$N_{inband} = \frac{C_s}{OSR} = \frac{2 \cdot F_b}{F} \stackrel{\cdot}{\longleftrightarrow} \frac{kT}{C}$

### 20b 250Hz Sigma-Delta ADC

- Sampling frequency choice

- Low sampling frequency

- Quantization noise

- Low OSR low resolution

- High order

- Q<sub>N</sub> is not the key limitation !!!

- Thermal noise

- Low OSR → large in-band noise

- For a given DR → Larger  $C_S$  → higher Power

- High sampling frequency

- Smaller sampling period

- Larger opamp bandwidth spec

higher power

- Larger slew-rate → higher power

#### 20b 250Hz Sigma-Delta ADC

- Sampling frequency choice

- Trade-off choice

- → OSR= 8.192

- ► → Fs = 250 x 2 x 8.192 = 4.096 MHz

- $\rightarrow$  N<sub>inband</sub><sup>2</sup>=(kT/C<sub>S</sub>)/OSR

- $\rightarrow$  C<sub>S</sub> = kT / (N<sub>inband</sub><sup>2</sup>·OSR) = 10pF

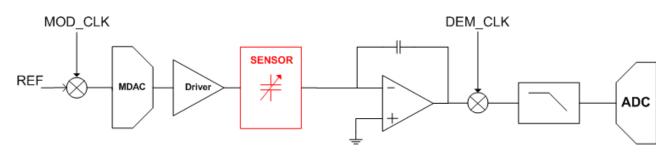

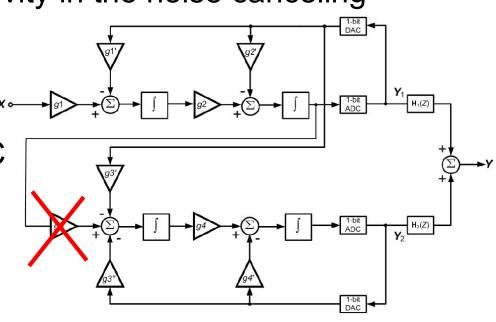

## 20b 250Hz Sigma-Delta ADC – Topology Choice

- Single-bit 2+2-MASH

- OND DAC cap mismatch sensitivity

- B Cap mismatch sensitivity in the noise canceling network

- Earge Slew-rate requirements

- Simple feedback DAC network

- Stability !!!

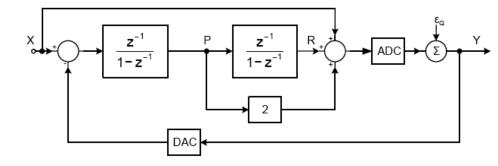

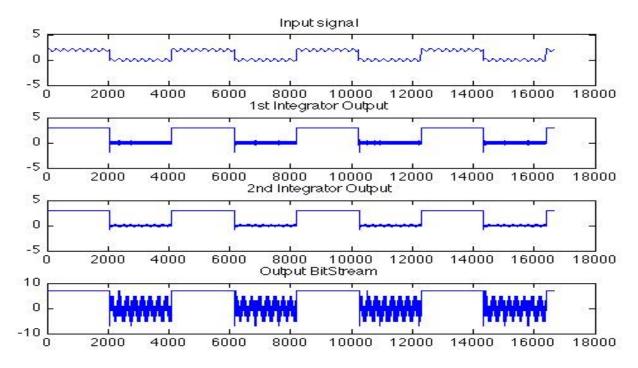

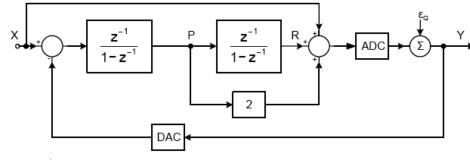

### 2<sup>nd</sup>-order FeedForward single-loop

# No signal in P & R

- Maximum opamp output swing

Quantizer LSB

- Useful for multi-bit quantizer

- → Small integrator output swing

**G A**113

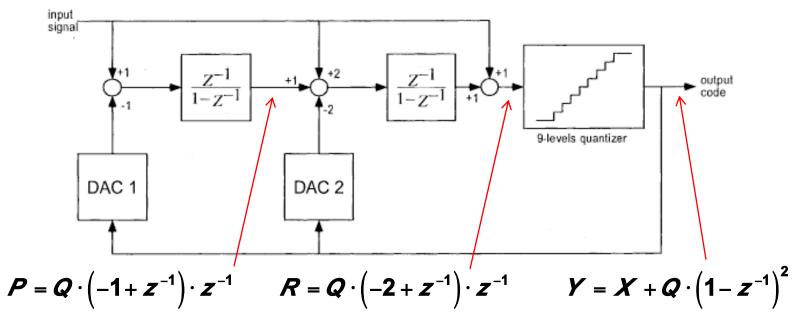

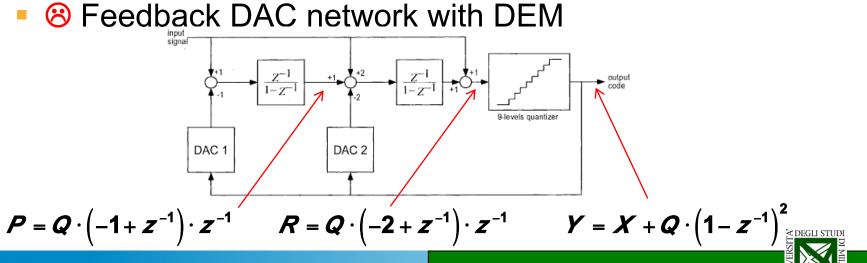

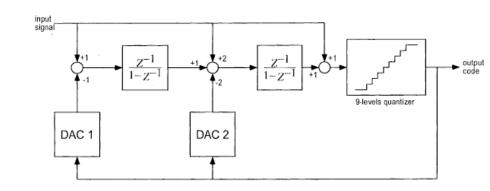

## 20b 250Hz Sigma-Delta ADC – Topology Choice

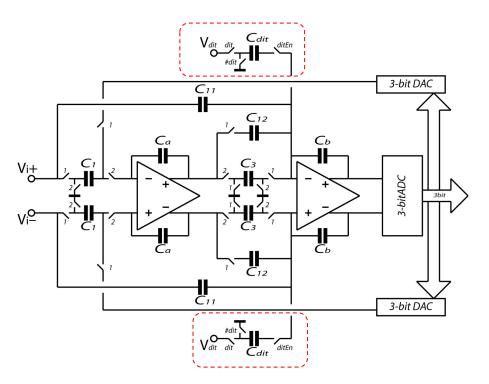

- 3-bit 2<sup>nd</sup>-order FeedForward single-loop

- BAC cap mismatch sensitivity

- One of the sensitivity of the sensitivity in the sensitivity is sensitive.

- One of the sensitivity of the sensitivity in the sensitivity is sensitivity in the sensitivity in the sensitivity in the sensitivity is sensitivity in the sensitivity in the sensitivity in the sensitivity is sensitivity is sensitivity in the sensitivity is sensitivity i

- Seduced Slew-rate requirements

- Over the second seco

- Lower load for the previous stage

- Single DAC

$$\boldsymbol{P} = \boldsymbol{Q} \cdot \left(-1 + \boldsymbol{z}^{-1}\right) \cdot \boldsymbol{z}^{-1} \qquad \boldsymbol{R} = \boldsymbol{Q} \cdot \left(-2 + \boldsymbol{z}^{-1}\right) \cdot \boldsymbol{z}^{-1} \qquad \boldsymbol{Y} = \boldsymbol{X} + \boldsymbol{Q} \cdot \left(1 - \boldsymbol{z}^{-1}\right)^2$$

- Nys's Topology

- B Three input branches

- Higher load for the previous stage

- B Two DACs

FF Topology

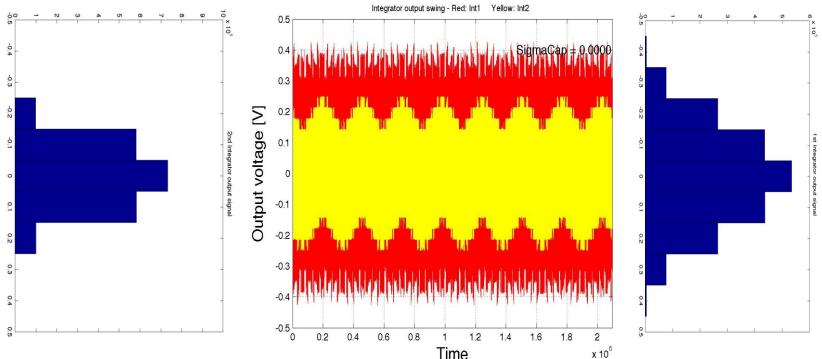

# Amplitude swing @ Integrator outputs

- Output swing  $< V_{FS}/2 \rightarrow$  relaxed opamp output swing

- Low Power Consumption

ADEGLI STUDI MILANO BICOCCA 115

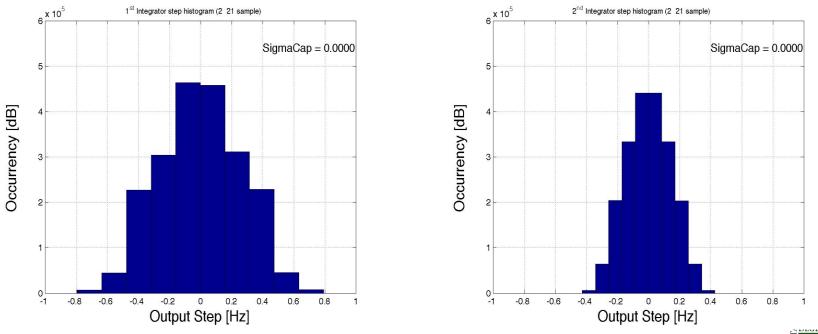

FF Topology

**STMicroelectronics**

- Integrator output step histogram

- SR is still important

BICOCCA 116

####

- Input overload signal

- The structure recovers from overload

- No reset circuit is need

EGLI STUD

**BICOCCA**118

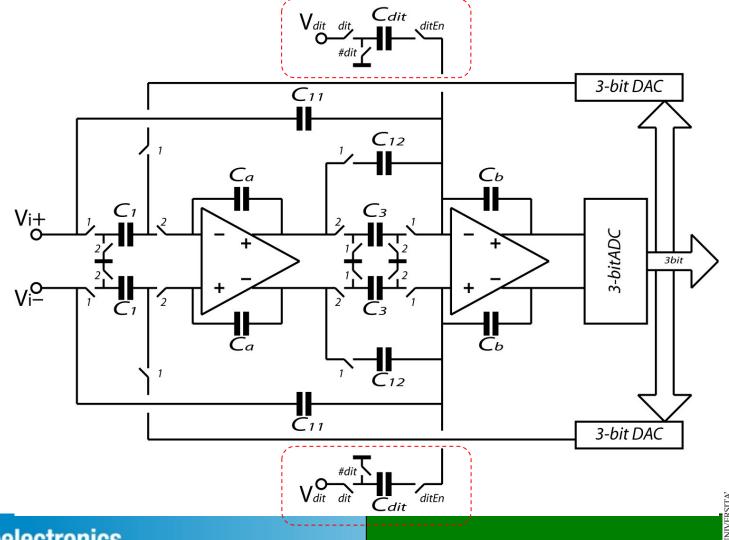

## 20b 250Hz Sigma-Delta ADC – Topology Choice

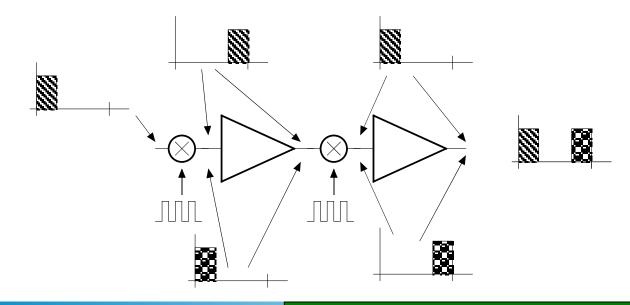

#### FFSDM – SC Implementation

# FFSDM Architecture development

- Q<sub>noise</sub>

- DAC non-linearity (Cap mismatch)

- Instability / Recovery time

- Idle tones

- Quantizer V<sub>TH</sub> Error

- FF Adder Gain Error

- Circuit design development

- Opamp performance effects

- Gain, Bandwidth, Slew-Rate

- Sampling Jitter

- Thermal noise

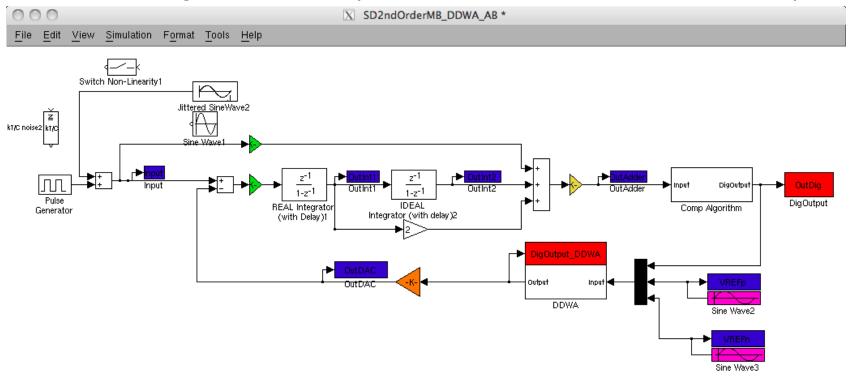

#### Simulink model

- Transient effects (SR, QN, Jitter, mismatch)

- Small signal effects (Thermal&1/f, Gain&Bandwidth)

### 20b 250Hz Sigma-Delta ADC – Topology Choice

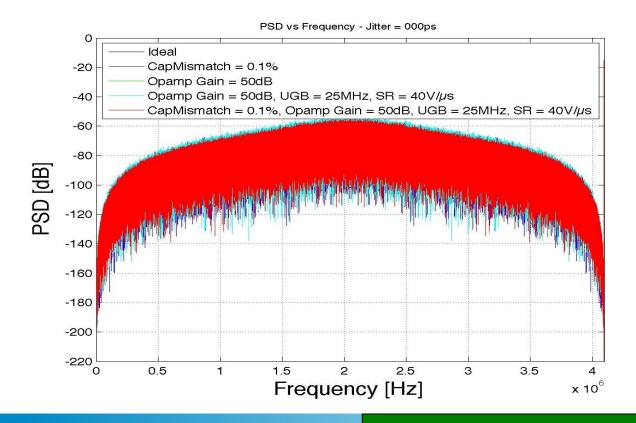

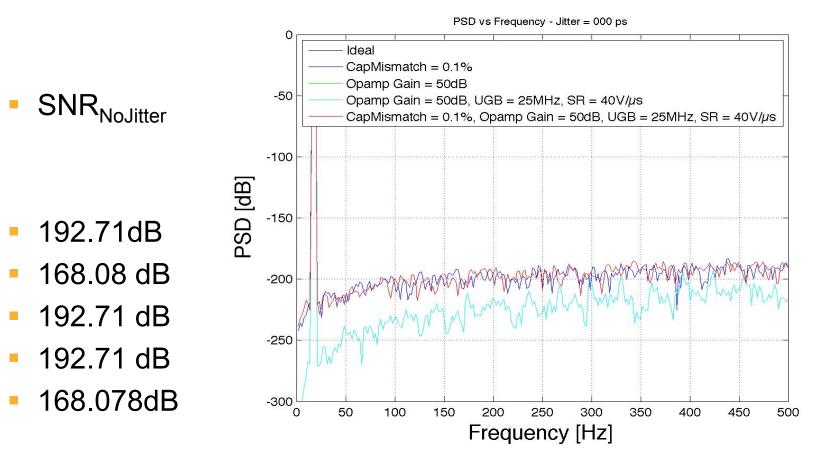

- FFSDM Real opamp performance

- Gain = 50dB, UGB = 25MHz, SR = 40V/μs

- Poor opamp gain requirement → LowPowerCons

FFSDM - Real opamp performance

## 20b 250Hz Sigma-Delta ADC – Topology Choice

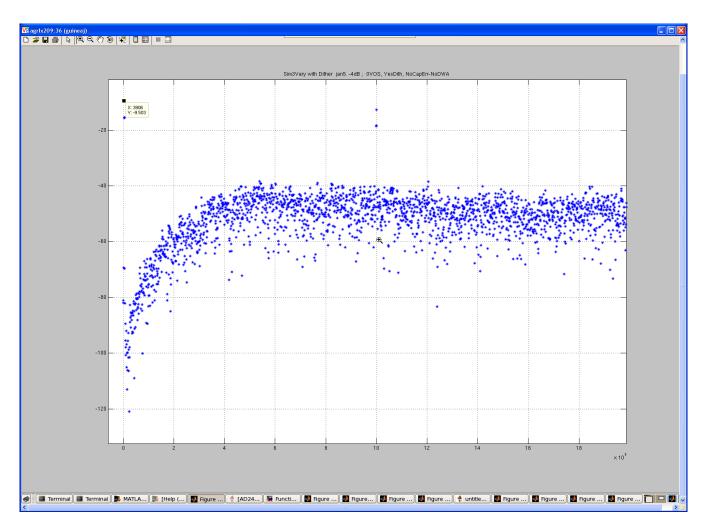

- Dither Avoids Spurious\_Tone generation at low signal-level

- @ Low-Level Multibit ADC behaves like a single-bit ADC

- Dither is implemented with an SC branch

- C<sub>dit</sub> = 1/10 Cb

- connected at the 2<sup>nd</sup>-opamp input

- dith frequency = Fs/4

- → input tones at Fs/4, i.e. far from the signal band

- can be disabled (dithEn signal)

### **20b 250Hz Sigma-Delta ADC – Implementation**

- Input noise reduction

- The aggressive AAF reduces input noise bandwidth

- It reduces settling time of the sampling operation

- The final sampled value depends on charging starting point

- Sampling error depends on signal amplitude

THD

### **20b 250Hz Sigma-Delta ADC – Implementation**

#### Input noise reduction - Solution

- The sampling capacitor is reset at the beginning of the sampling phase

- ► The signal-dependent error is canceled

## **20b 250Hz Sigma-Delta ADC – Implementation**

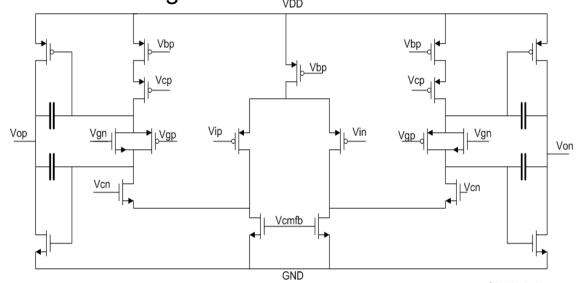

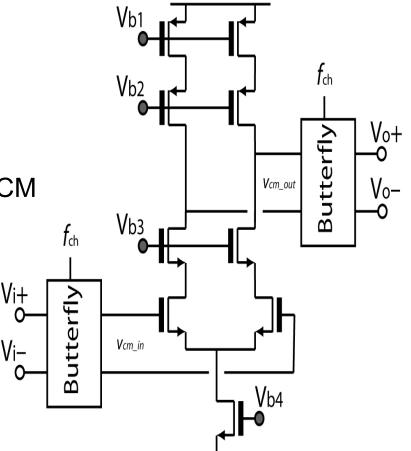

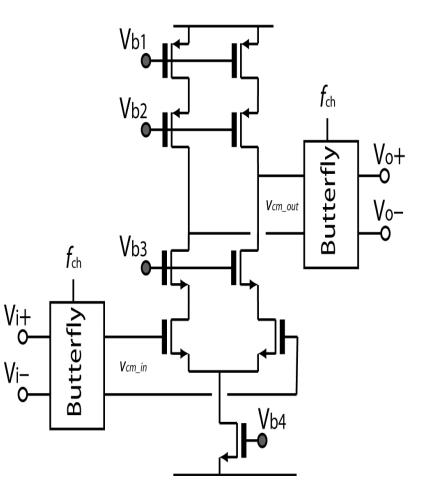

- 1<sup>st</sup>-opamp design

- I/f Noise → Chopper

- FFSDM

- Reduce swing

- →Telescopic cascode

- Different input.vs.output CM compensated in the SC structure

## **20b 250Hz Sigma-Delta ADC – Implementation**

- Chopper concept

- Chopper frequency choice: Trade-off motivation

- Low chopping frequency → Larger in-band noise folding

- High chopping frequency

→ Large-&-frequent opamp output steps

- Chopper frequency choice  $\rightarrow$  F<sub>s</sub>/8

# 20b 250Hz Sigma-Delta ADC – Implementation

- Chopper concept

- In a two-stage opamp only the 1<sup>st</sup>-stage in chopped

- Negligible 2<sup>nd</sup>-stage 1/f noise

- Smaller 1<sup>st</sup>-stage output swing

- In a single-stage opamp

- ► The full opamp is chopped

- ➡ Significant output swing

- III BUT in FF-SDM

- Small 1<sup>st</sup>-opamp output swing

- Chopper is not critical

129

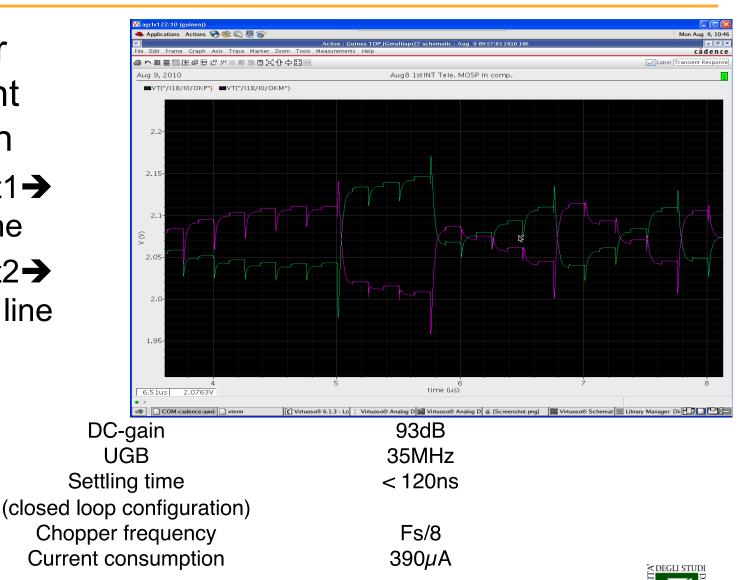

## 20b 250Hz Sigma-Delta ADC – Implementation

- Chopper Transient evolution

- Output1 → pink line

- Output2→

Green line

### **20b 250Hz Sigma-Delta ADC – Implementation**

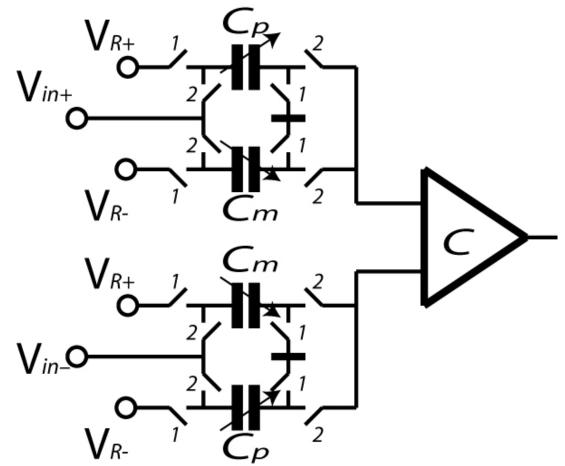

V

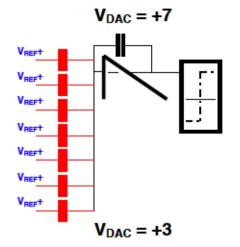

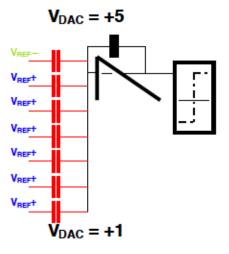

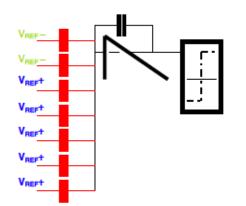

- Multibit ADC

- ADC Threshold voltage generation

- Passive SC solution in the comparator (single-ended version)

- Charge balance

$$V_{c}(2) = V_{in} - \frac{C_{p}}{C_{p} + C_{m}} \mathscr{H}_{R}$$

$$V_{R} \xrightarrow{1}_{2} \xrightarrow{C_{P}}_{2} \xrightarrow{2}_{1} \xrightarrow{V_{c}}_{1} \xrightarrow{V_{$$

- $V_{TH} = 7 \rightarrow C_p = 7 \cdot C \& C_m = 1 \cdot C$

- $V_{TH} = 5 \rightarrow C_p = 5 \cdot C \& C_m = 3 \cdot C$

- $V_{TH} = 3 \Rightarrow C_p = 3 \cdot C \& C_m = 7 \cdot C$

$$V_{c}(2) = V_{in} - \frac{C_{p} * V_{R+} + C_{m} * V_{R-}}{C_{p} + C_{m}} = V_{in} - \frac{C_{p} - C_{m}}{C_{p} + C_{m}} * V_{R+}$$

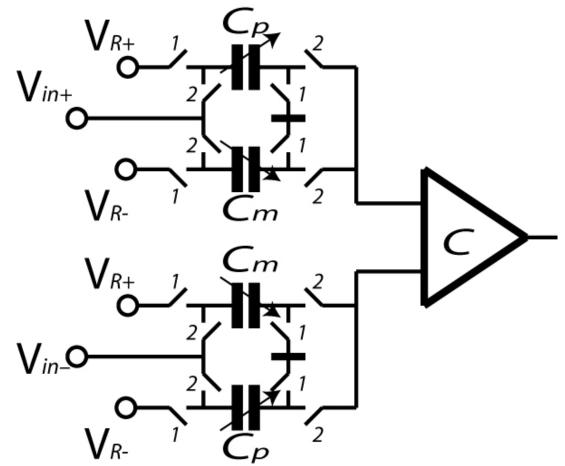

### **20b 250Hz Sigma-Delta ADC – Implementation**

- Multibit ADC

- Fully-differential scheme

### **20b 250Hz Sigma-Delta ADC – Implementation**

- Multibit ADC

- Fully-differential scheme

## **20b 250Hz Sigma-Delta ADC – Implementation**

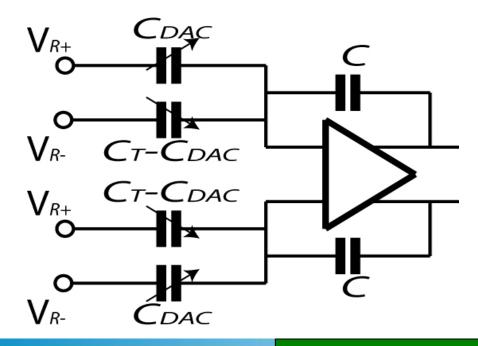

- Multibit DAC

- Fixed total opamp input capacitance

- Independent on the input data

- Fixed total load for V<sub>R+</sub> & V<sub>R-</sub>

- Independent on the input data

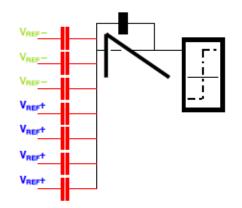

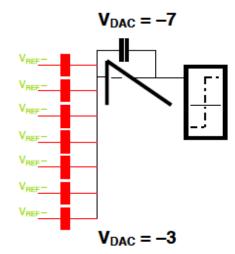

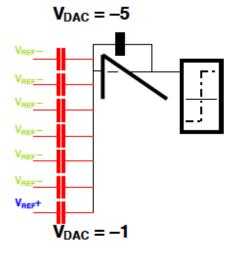

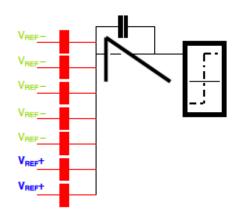

### **20b 250Hz Sigma-Delta ADC – Implementation**

Multibit DAC: 3bit operation example

### **20b 250Hz Sigma-Delta ADC – Implementation**

Multibit DAC: 3bit operation example

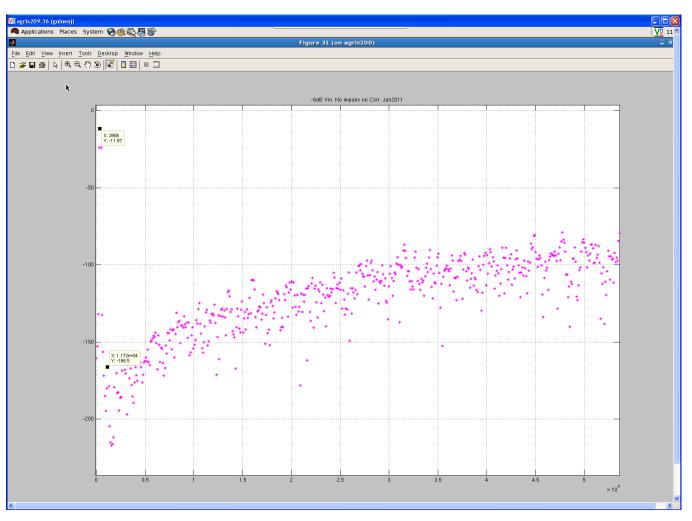

### **20b 250Hz Sigma-Delta ADC – Simulation**

A<sub>in</sub>=-4dB<sub>FS</sub>, Dither=NO

#### **20b 250Hz Sigma-Delta ADC – Simulation**

A<sub>in</sub>=-4dB<sub>FS</sub>, Dither=YES

### **Overall System Power Consumption**

|                   | Current<br>Consumption<br>[ µA ] | Supply Voltage<br>[ V ] | Power<br>Consumption<br>[ mW ] |

|-------------------|----------------------------------|-------------------------|--------------------------------|

| Charge Amplifier  | 2200                             | 3.3                     | 7.3                            |

| Anti-Alias Filter | 0                                | 3.3                     | 0                              |

| Drivers           | 672                              | 5.0                     | 3.4                            |

| Differential MDAC | 353                              | 3.3                     | 1.16                           |

| ADC               | 890                              | 3.3                     | 3                              |